Изобретение относится к области вычислительной техники, а именно к вычислительным системам на основе универсальных микропроцессоров.

Известен блок в системном контроллере для работы с внешней памятью (ОЗУ), находящийся в составе гибридного микропроцессора, включающего центральный процессор, системный контроллер, внешнюю память, двухуровневую кэш-память (патент RU 2359315, кл. G06F 9/30, опублик. 20.06.2009).

Недостатком описанного блока является его низкая производительность при обращениях во внешнюю память.

Наиболее близким по технической сути и достигаемому техническому результату является механизм буферизации потоков данных, считываемых из ОЗУ и пересылаемых между двумя интерфейсами, представляющих собой шины данных ОЗУ и ЦПУ соответственно и содержащее буфер, выполненный на памяти или регистрах и накапливающий данные для их передачи по запросу с второго интерфейса без обращения за ними в первый (Патент US 7581072 В2, кл. G06F 12/00, опублик. 14.12.2006).

Недостатком описанного устройства буферизации является низкая эффективность работы. Кроме того, устройство не имеет отслеживания адреса, по которому происходит запись в память, потому при его работе возможна ситуация, когда хранящиеся в буфере данные потеряют актуальность в связи с новой записью в ОЗУ по данному адресу.

Ожидаемый технический результат от использования данного изобретения состоит в повышении производительности подсистемы памяти, заключающейся в уменьшении задержек получения запрошенных ЦПУ данных, повышении гибкости применения и хранения одновременно нескольких потоков запросов данных из памяти и увеличения пропускной способности шины данных ОЗУ за счет уменьшения на нее нагрузки.

Указанный технический результат достигается тем, что в устройстве буферизации потоков данных, пересылаемых между двумя интерфейсами, представляющими собой шины данных ОЗУ и ЦПУ соответственно, содержащем буфер, выполненный на памяти или регистрах и накапливающий данные для их передачи по запросу со второго интерфейса без обращения за ними в первый, оно содержит дополнительные буферы, тэг-контроллер и выходной мультиплексор, причем тэг-контроллер связан с мультиплексором, буфером, выполненным на памяти или регистрах, и дополнительными буферами для отслеживания актуальности хранящихся в них данных, а входы буферов устройства подключены к ОЗУ.

Уменьшение задержки получения данных возникает в результате того, что данные были заранее считаны в буфер до того, как процессор их затребовал, несколько буферов позволяют накапливать данные по четырем независимым адресам, а то, что данные передаются во второй интерфейс без обращения в первый (то есть ОЗУ), позволяет разгрузить шину данных.

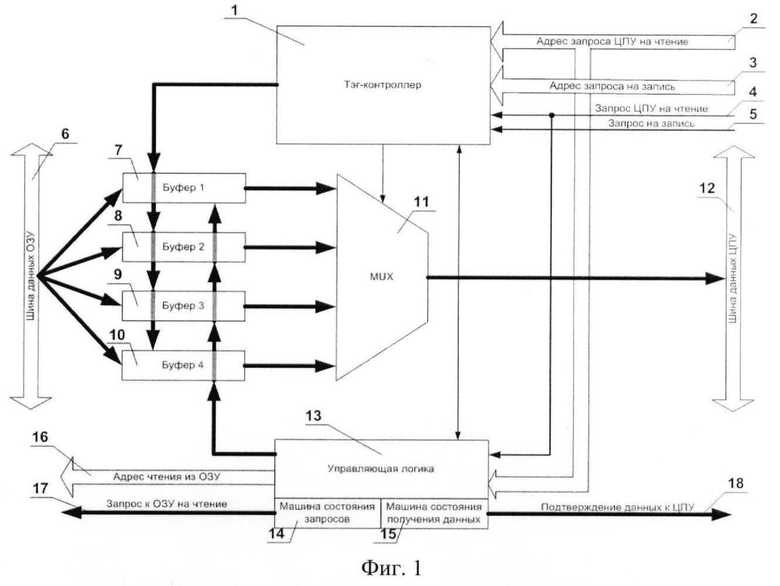

Изобретение поясняется чертежами, где на фиг.1 представлена блок-схема устройства буферизации потоков данных, считываемых из ОЗУ.

Механизм буферизации потоков данных, считываемых из ОЗУ, состоит из тэг-контроллера 1, шины адреса чтения 2, шины адреса записи 3, стробов 4 и 5 подтверждения действительности адресов чтения и записи, шины данных ОЗУ 6, буферов 7, 8, 9 и 10, мультиплексора переключения выходов буферов 11. Также содержит шину данных ЦПУ 12, управляющую запросами к памяти и ответу ЦПУ логику 13 с машинами состояний подтверждения 14 и запроса 15, шины адреса чтения из ОЗУ 16 со стробом запроса к контроллеру ОЗУ 17 и строб 18 подтверждения данных для ЦПУ.

Устройство работает следующим образом. После сброса тэг-контроллер 1 выставляет на сигнал выбора буфера разрешение записи в буфер 7. Выход буфера 10 через мультиплексор 11 оказывается скоммутирован на шину данных ЦПУ по сигналу выбора выхода буфера от тег-контроллера 1. Когда от процессора приходит запрос 4 на чтение по адресу 2, он направляется как на тэг-контроллер 1, так и на управляющую логику 13. Тэг-контроллер 1, не обнаружив, что данные по этому адресу находятся в буфере, сигнализирует об этом по внутренней служебной шине управляющей логике, и та, с помощью машины состояния запросов 14, формирует запрос к ОЗУ на чтение 17 по адресу 16. Полученные данные заполняются в буфер 7, при этом, в зависимости от соотношения частоты шины памяти и шины ЦПУ, начинается выдача данных от мультиплексора 11 на шину 12 и формирование сигнала подтверждения 18 с помощью машины состояния получения данных 15 до того момента, как данные считаются полностью. По мере пакетной выдачи данных получение новых данных от ОЗУ завершается, и нужное количество пересылается в ЦПУ. Однако запись в буфер 7 на этом не останавливается, а продолжается, пока он не заполнится. По окончании записи машина состояния запросов 14 переходит в режим ожидания, а управляющая логика 13 выставляет сигнал окончания загрузки данных тэг-контроллеру 1, который снимает разрешение записи с буфера 7 и переводит его на буфер 8. Таким образом, в случае следующего запроса по адресу, не совпадающему с тем, по которому были записаны данные в предыдущий раз, вышеприведенный алгоритм работы повторится для буфера 8, данные в буфере 7 сохранятся для возможного будущего запроса.

В случае, если обращение на чтение со стороны процессора было по адресу, по которому уже было произведено чтение, тэг-контроллер 1 сообщает о совпадении адресов управляющей логике 13, одновременно переключая мультиплексор 11 на получение данных из того буфера, в котором хранятся нужные данные. Управляющая логика 13 формирует адрес 16, по которому будет идти чтение из буфера, на основе адреса запроса ЦПУ на чтение 2. Далее управляющая логика 13 формирует с помощью машины состояния получения данных 15 сигнал подтверждения данных для ЦПУ, и данные направляются на шину данных ЦПУ 12. Если затем в какой-либо момент последует следующий запрос на чтение 5, и адрес окажется последовательным относительно предыдущего запроса, то буфер (в данном примере буфер 8) окажется опустошен наполовину, и одновременно с выдачей данных ЦПУ с помощью машины состояния получения данных 15 машина состояния запросов 8 сформирует запрос на чтение 17 по последовательно относительно адреса запроса ЦПУ идущему адресу 16 для того, чтобы буфер 8 вновь стал полон.

Отдельной задачей тег-контроллера является наблюдение за адресом 4, по которому центральным процессором или внешними устройствами по запросу 5 происходит запись в ОЗУ, так как возможна ситуация, что данные, которые сохранены в буферах, уже не будут актуальными, так как по соответствующему адресу в ОЗУ была произведена запись. В этом случае тэг-контроллер 1 выставляет признак, что данные в буфере не актуальны.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ДОСТУПА К ПАМЯТИ В КЛАСТЕРНОЙ МАШИНЕ ШИРОКОГО ИСПОЛНЕНИЯ | 2013 |

|

RU2662394C2 |

| ПРИНУДИТЕЛЬНОЕ ПРИМЕНЕНИЕ СТРОГО УПОРЯДОЧЕННЫХ ЗАПРОСОВ В СИСТЕМЕ СЛАБО УПОРЯДОЧЕННОЙ ОБРАБОТКИ | 2006 |

|

RU2405194C2 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| ГИБРИДНЫЙ МИКРОПРОЦЕССОР | 2014 |

|

RU2556364C1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| УСТРОЙСТВО ДЛЯ СБОРА И ОБРАБОТКИ ДАННЫХ | 2002 |

|

RU2218597C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ УСТАНОВКИ ПОЛИТИКИ КЭШИРОВАНИЯ В ПРОЦЕССОРЕ | 2008 |

|

RU2427892C2 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении производительности подсистемы памяти, заключающейся в уменьшении задержек получения запрошенных ЦПУ данных, повышении гибкости применения и увеличении пропускной способности шины данных ОЗУ. Устройство буферизации потоков данных, пересылаемых между двумя интерфейсами, представляющими собой шины данных ОЗУ и ЦПУ соответственно, содержащее буфер, выполненный на памяти или регистрах и накапливающий данные для их передачи по запросу со второго интерфейса без обращения за ними в первый, причем устройство содержит дополнительные буферы, тэг-контроллер и выходной мультиплексор, причем тэг-контроллер связан с мультиплексором, буфером, выполненным на памяти или регистрах, и дополнительными буферами для отслеживания актуальности хранящихся в них данных, а входы буферов устройства подключены к ОЗУ. 1 ил.

Устройство буферизации потоков данных, пересылаемых между двумя интерфейсами, представляющими собой шины данных ОЗУ и ЦПУ соответственно, содержащее буфер, выполненный на памяти или регистрах и накапливающий данные для их передачи по запросу со второго интерфейса без обращения за ними в первый, отличающееся тем, что устройство содержит дополнительные буферы, тэг-контроллер и выходной мультиплексор, причем тэг-контроллер связан с мультиплексором, буфером, выполненным на памяти или регистрах, и дополнительными буферами для отслеживания актуальности хранящихся в них данных, а входы буферов устройства подключены к ОЗУ.

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| EP 0793178 A2, 03.09.1997 | |||

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2017211C1 |

| ИНТЕРФЕЙС С ВЫСОКОЙ СКОРОСТЬЮ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2371872C2 |

Авторы

Даты

2013-02-20—Публикация

2011-12-08—Подача