Изобретение относится к области вычислительной техники, а именно к подсистеме памяти современных микропроцессоров.

Известен способ заполнения кэш-памяти команд и выдачи команд на выполнение и устройство для его осуществления, включающее массив памяти и блок выбора секции для записи, поступившей из основной памяти строки. Выбор осуществляют вне зависимости от аналогичного выбора секции для записи предыдущих строк (патент US 005774685, кл. G06F 9/30, опубл. 2009).

Известен способ заполнения кэш-памяти команд и выдачи команд на выполнение и устройство для его осуществления, включающее в себя центральный процессор, буфер команд, блок управления памятью, двухуровневую кэш-память, содержащую кэш-память команд первого уровня, кэш-память данных первого уровня и объединенную кэш-память второго уровня, системный контроллер и внешнюю память. Способ включает разделение массива кэш-памяти на N секций, каждую строку перемещают из основной памяти в кэш-память и помещают в определенную строку любой из секций, которую определяют посредством блока выбора секций (БВС). Разрядность запоминающих устройств не превышает половины длины строки кэш-памяти (патент RU №2359315, кл. G06F 9/30, опубл. 2008).

Значительная часть исполняемого программного кода организована по линейному принципу, то есть при выполнении команды по адресу A велика вероятность, что следующей будет выполнена команда по адресу A+1. Большинство современных буферов команд осуществляют так называемую упреждающую выборку: запрашивают команды по адресам, следующим за исполняемым адресом, не дожидаясь инкрементации программного счетчика. Таким образом, большинство запросов, поступающих в кэш-память команд, имеют линейно возрастающие адреса. Недостатком описанных устройств является то, что следующие друг за другом строки регулярно помещаются в одну и ту же секцию кэш-памяти, что исключает их одновременное считывание и ограничивает таким образом производительность кэш-памяти (скорость выдачи инструкций буферу команд).

Технический результат от использования изобретения состоит в повышении производительности путем увеличения скорости выдачи инструкций без увеличения разрядности запоминающих устройств

Увеличение скорости может достигать двукратного (при выполнении линейных участков кода) по сравнению с известными способами и подсистемами памяти, что особенно важно для многопотоковых процессоров.

Описываемые способ и устройство заполнения кэш-памяти команд и выдачи команд на выполнение позволяет осуществлять параллельное считывание строк по линейно возрастающим адресам, что позволит повысить производительность кэш-памяти.

Указанный технический результат достигается тем, что в способе заполнения кэш-памяти команд и выдачи команд на выполнение, включающем заполнение кэш-памяти команд и выдачу команд на выполнение, разделение массива кэш-памяти на N секций, перемещение каждой строки из основной памяти в кэш-память и размещение в определенной строке секции, которую определяют посредством блока выбора секций, согласно изобретению заполнение кэш-памяти производят размещением строки в секцию, следующую за секцией, в которую была размещена предыдущая строка, при этом последующие строки размещают в циклической последовательности, а выдачу команд на выполнение осуществляют из двух соседних секций одновременно.

Описанный способ осуществляется устройством, включающим центральный процессор, буфер команд, блок управления памятью, двухуровневую кэш-память, содержащую кэш-память команд первого уровня, кэш-память данных первого уровня, содержащую секции запоминающих устройств, входной регистр, входной демультиплексор, блок выбора секций, блок анализа промаха/попадания, выходной мультиплексор и выходной регистр, объединенную кэш-память второго уровня, системный контроллер и внешнюю память, согласно изобретению кэш-память команд первого уровня содержит дополнительный выходной мультиплексор, связанный с буфером команд и выходным регистром, и блок выбора секций, состоящий из связанных между собой запоминающего устройства кодов секций, преобразователя кода, представляющего собой алгоритм замещения элемента с наиболее длительным интервалом отсутствия обращения к нему, регистра хранения предыдущего кода выбора секции, сдвигового регистра и мультиплексора, при этом блок выбора секций связан с входным демультиплексором и секциями запоминающих устройств.

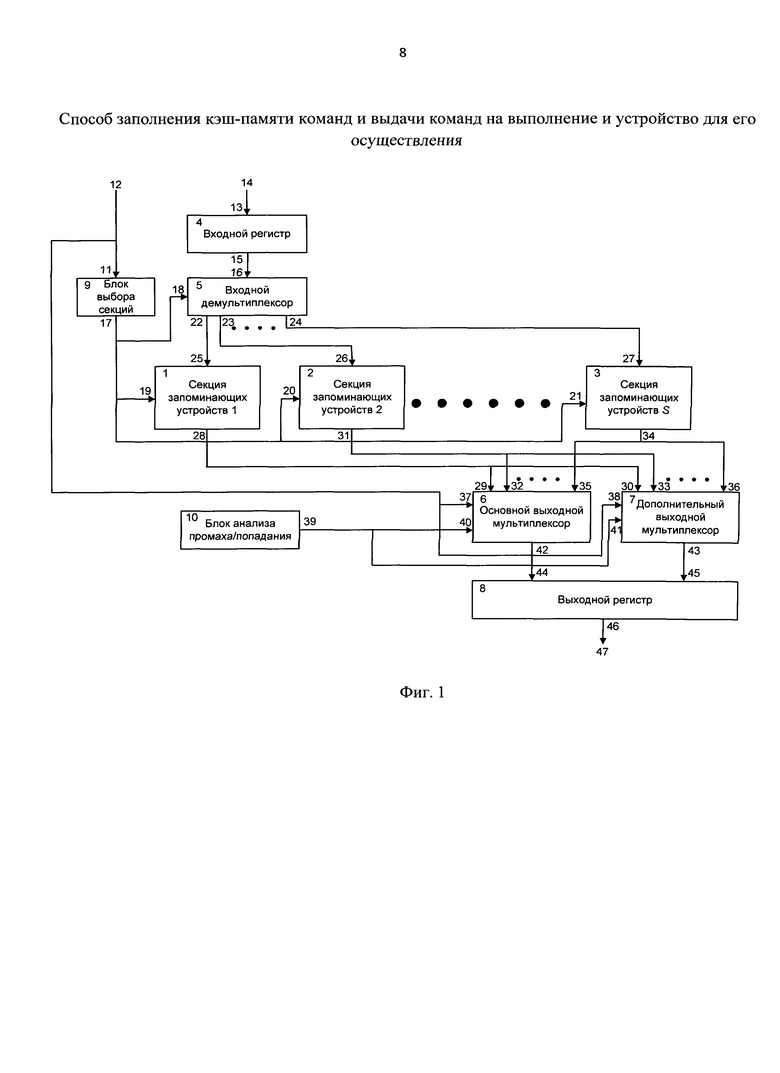

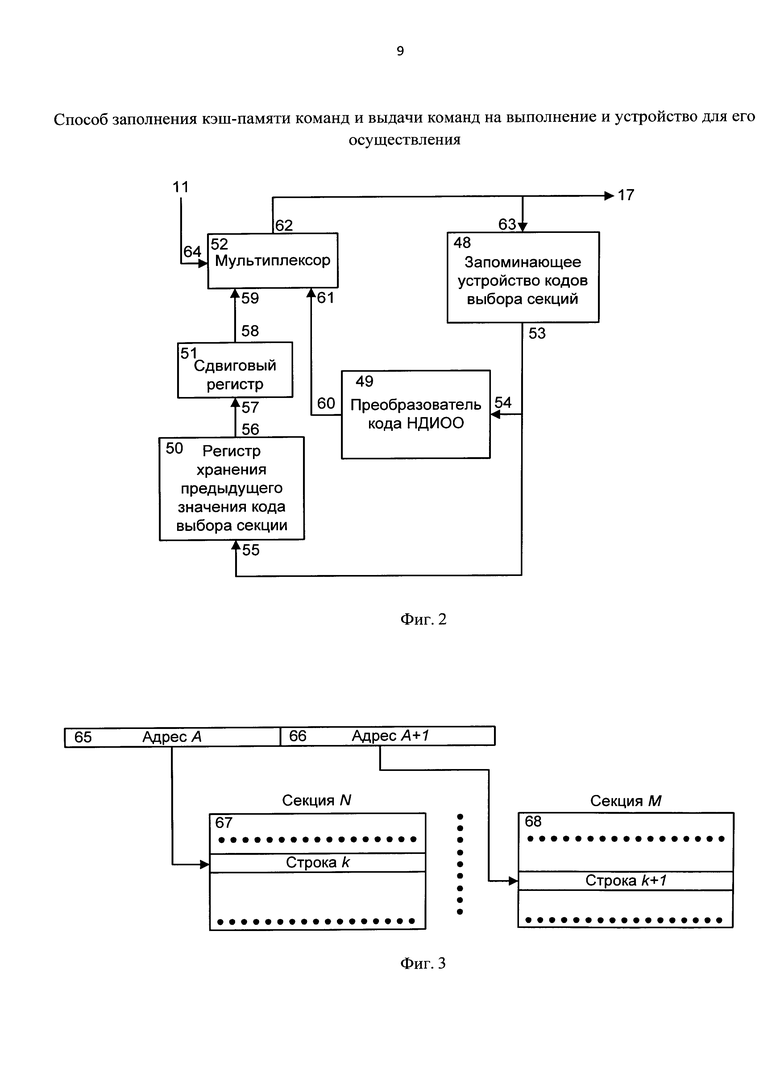

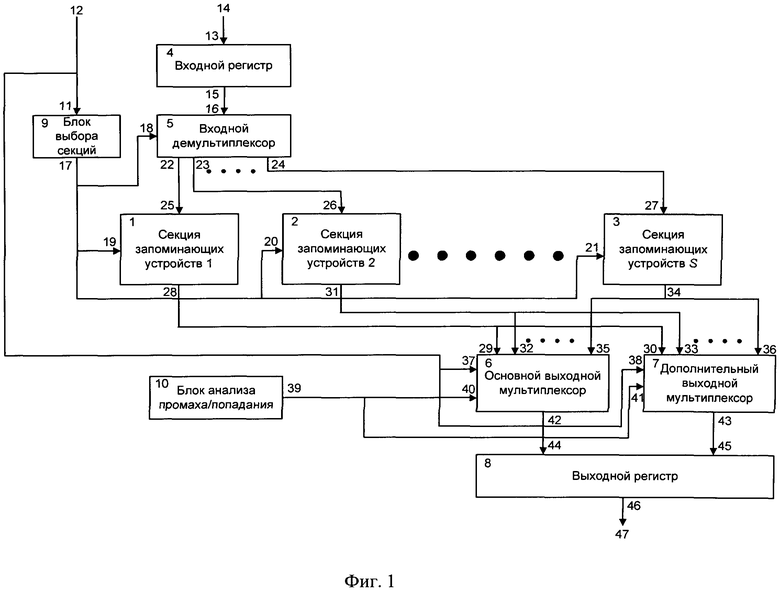

Изобретение поясняется чертежами, где на фиг. 1 изображена схема устройства заполнения кэш-памяти и выдачи инструкций буферу команд на выполнение, на фиг. 2 - схема блока выбора секций, на фиг. 3 - схема размещения строк с линейно возрастающими адресами в секциях кэш-памяти команд.

Устройство состоит из запоминающих устройств кэш-памяти команд (S секций) 1, 2 и 3, входного регистра 4, входного демультиплексора 5, основного 6 и дополнительного 7 выходных мультиплексоров, выходного регистра 8, блока выбора секций (БВС) 9 и блока анализа промаха/попадания в кэш-память 10. Вход 11 БВС 9 связан с выводом 12, на который от буфера команд поступает сигнал ADINC. Вход входного регистра 13 связан с выводом 14, на который от системного контроллера или кэш-памяти второго уровня поступают входные данные. Выход 15 входного регистра 4 связан с информационным входом 16 входного демультиплексора 5. Выход 17 БВС 9 связан с управляющим входом 18 входного демультиплексора 5, с управляющими входами (разрешение записи) 19, 20 и 21 секций запоминающих устройств 1, 2 и 3 соответственно. Информационные выходы 22, 23 и 24 входного демультиплексора 5 связаны с информационными входами 25, 26 и 27 секций запоминающих устройств 1, 2 и 3 соответственно. Информационный выход 28 секции запоминающих устройств 1 связан с информационными входами 29 и 30 основного выходного мультиплексора 6 и дополнительного выходного мультиплексора 7 соответственно. Информационный выход 31 секции запоминающих устройств 2 связан с информационными входами 32 и 33 основного выходного мультиплексора 6 и дополнительного выходного мультиплексора 7 соответственно. Информационный выход 34 секции запоминающих устройств 3 связан с информационными входами 35 и 36 основного выходного мультиплексора 6 и дополнительного выходного мультиплексора 7 соответственно. Вывод 12 связан с управляющими входами 37 и 38 основного выходного мультиплексора 6 и дополнительного выходного мультиплексора 7 соответственно. Выход 39 блока анализа промаха/попадания в кэш-память 10 связан с управляющими входами 40 и 41 основного выходного мультиплексора 6 и дополнительного выходного мультиплексора 7 соответственно. Выходы 42 и 43 основного выходного мультиплексора 6 и дополнительного выходного мультиплексора 7 связаны с входами 44 и 45 выходного регистра 8 соответственно. Выход 46 выходного регистра 8 связан с выводом 47, данные с которого поступают на буфер команд. Особенность предлагаемого устройства заключается в применении модернизированного БВС, состоящего из запоминающего устройства кодов выбора секций 48, известного преобразователя кода выбора секций по алгоритму замещения элемента с наиболее длительным интервалом отсутствия обращения к нему алгоритма замещения элемента с наиболее длительным интервалом отсутствия обращения к нему (НДИОО) 49, регистра хранения предыдущего значения кода выбора секций 50, сдвигового регистра 51 и мультиплексора 52. Выход 53 запоминающего устройства кодов выбора секций 48 связан с входом 54 преобразователя кода по алгоритму НДИОО 49. Выход 53 запоминающего устройства кодов выбора секций 48 связан с входом 55 регистра хранения предыдущего значения кода выбора секций 50. Выход 56 регистра хранения предыдущего значения кода выбора секции 50 связан с входом 57 сдвигового регистра 51. Выход 58 сдвигового регистра 51 связан с информационным входом 59 мультиплексора 52. Выход 60 преобразователя кода выбора секций 49 связан с информационным входом 61 мультиплексора 52. Выход 62 мультиплексора 52 связан с входом 63 запоминающего устройства кодов выбора секций 48 и выходом 17 блока выбора секций. Вход 11 блока выбора секций связан с управляющим входом 64 мультиплексора 52.

Особенностью устройства так же является включение в состав БВС регистра хранения предыдущего значения кода выбора секции и сдвигового регистра. Способ заполнения кэш-памяти команд и выдачи команд на выполнение состоит в использовании следующей схемы размещения строк с линейно возрастающими адресами в кэш-памяти. В тот период времени, когда происходит выполнение линейного участка кода, буфер команд выставляет кэш-памяти сигнал AD_INC. Строки, помещаемые в кэш-память команд при отсутствии сигнала AD_INC, помещаются в секции, выбираемые в соответствии с известным алгоритмом замещения элемента с наиболее длительным интервалом отсутствия обращения к нему (алгоритм НДИОО). Обозначим адрес строки 65, помещенной в кэш-память команд последней перед выставлением сигнала AD_INC, как А. Пусть она помещена в строку к (к однозначно определяется адресом А) секции N (66) кэш-памяти с числом секций S, при этом N определена алгоритмом замещения элемента с наиболее длительным интервалом отсутствия обращения к нему (НДИОО). В способе при следующем запросе БВС описанной конструкции обеспечит запись строки 67 по адресу A+1 в строку k+1 секции М (68), где М=N+1 при N<S и М=1 при N=S. При этом в строке секции устанавливается специальный флаг: бит AI. Обеспечить вышеописанную последовательность позволяют включенные в состав блока выбора секций регистр хранения предыдущего значения кода выбора секции и сдвиговый регистр.

Описанный способ осуществляется следующим образом

При заполнении кэш-памяти от внешнего источника инструкции, поступающие на вход 14 кэш-памяти, записываются во входной регистр 4. Выходные данные регистра 4 передаются на вход одной из секций запоминающих устройств через демультиплексор 5. Выбор нужной секции и управление демультиплексором осуществляются с выхода 17 блока выбора секций 9. Коды выбора секций хранятся в запоминающем устройстве 48. При выставлении адреса запроса на выход запоминающего устройства выдается текущий код. Он записывается в регистр 50. Преобразователем кода 49 осуществляется стандартное преобразование считанного кода по алгоритму замещения элемента с наиболее длительным интервалом отсутствия обращения к нему (НДИОО). Преобразованный код передается на выход 17 устройства выбора секций через мультиплексор 52 при условии пассивного уровня сигнала AD_INC на входе 11 устройства выбора секций. Отличительной особенностью предлагаемого метода является то, что в случае выставления сигнала AD_INC на входе 11 на активный уровень на выход 17 устройства выбора секций поступает преобразованное стандартным сдвиговым регистром 51 предыдущее значение кода выбора секций, хранимое в регистре 50 от предыдущего запроса. В соответствующей строке выбранной секции при этом устанавливается бит AI.

При выдаче инструкций из кэш-памяти буферу команд при поступлении запроса на выдачу строки по адресу A осуществляется считывание данных из всех секций запоминающих устройств 1, 2, 3. При условии попадания в секцию N, данные из секции N пересылаются обычным образом через основной выходной мультиплексор 6, управляемый выходным сигналом 39 блока анализа промаха/попадания 10, в младшую часть выходного регистра 8. Отличительной особенностью предлагаемого метода является то, что при условии активного уровня сигнала AD_INC на входе 12 устройства осуществляется одновременная пересылка через дополнительный выходной мультиплексор 7 данных строки k+1 из секции М в старшую часть выходного регистра 8 в том случае, если в строке k+1 секции М установлен бит AI. Таким образом, достигается увеличение скорости выдачи инструкций буферу команд без увеличения разрядности запоминающих устройств кэш-памяти команд первого уровня.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство КЭШ-памяти | 1988 |

|

SU1675881A1 |

| ПОЛУПРОВОДНИКОВАЯ ПАМЯТЬ | 1993 |

|

RU2156506C2 |

| СПОСОБ КОПИРОВАНИЯ ДАННЫХ В КЭШ-ПАМЯТИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2012 |

|

RU2504000C1 |

| ПОДСИСТЕМА ПАМЯТИ ЯДРА МИКРОПРОЦЕССОРА | 2011 |

|

RU2475822C1 |

| ЗАЩИТА ДОСТУПА К ПАМЯТИ | 1998 |

|

RU2215321C2 |

| ЦИФРОВОЙ КОМПЬЮТЕР С ВОЗМОЖНОСТЬЮ ПАРАЛЛЕЛЬНОГО ВЫПОЛНЕНИЯ ДВУХ И БОЛЕЕ КОМАНД | 1991 |

|

RU2109333C1 |

| ГРАФИЧЕСКАЯ СИСТЕМА С КОНФИГУРИРУЕМЫМИ КЭШАМИ | 2007 |

|

RU2412469C2 |

| УСТРОЙСТВО ЧТЕНИЯ ИЗ КЭШ-ПАМЯТИ | 2005 |

|

RU2290706C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ДОСТУПА К ПАМЯТИ В КЛАСТЕРНОЙ МАШИНЕ ШИРОКОГО ИСПОЛНЕНИЯ | 2013 |

|

RU2662394C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в повышении производительности кэш-памяти путем увеличения скорости выдачи инструкций без увеличения разрядности запоминающих устройств. Способ заполнения кэш-памяти команд и выдачи команд на выполнение включает заполнение кэш-памяти команд и выдачу команд на выполнение, разделение массива кэш-памяти на секции, перемещение каждой строки из основной памяти в кэш-память и размещение в определенной строке секции, которую определяют посредством блока выбора секций, причем заполнение кэш-памяти производят размещением строки в секцию, следующую за секцией, в которую была размещена предыдущая строка, при этом последующие строки размещают в циклической последовательности с установлением флага, а выдачу команд на выполнение осуществляют из двух секций одновременно при наличии указанного флага. 2 н.п. ф-лы, 3 ил.

1. Способ заполнения кэш-памяти команд и выдачи команд на выполнение, включающий заполнение кэш-памяти команд и выдачу команд на выполнение, разделение массива кэш-памяти на секции, перемещение каждой строки из основной памяти в кэш-память и размещение в определенной строке секции, которую определяют посредством блока выбора секций, отличающийся тем, что заполнение кэш-памяти производят размещением строки в секцию, следующую за секцией, в которую была размещена предыдущая строка, при этом последующие строки размещают в циклической последовательности с установлением флага, а выдачу команд на выполнение осуществляют из двух секций одновременно при наличии указанного флага.

2. Устройство заполнения кэш-памяти команд и выдачи команд на выполнение, включающее центральный процессор, буфер команд, блок управления памятью, двухуровневую кэш-память, содержащую кэш-память команд первого уровня, кэш-память данных первого уровня, содержащую секции запоминающих устройств, входной регистр, входной демультиплексор, блок выбора секций, блок анализа промаха/попадания, выходной мультиплексор и выходной регистр, объединенную кэш-память второго уровня, системный контроллер и внешнюю память, отличающееся тем, что кэш-память команд первого уровня содержит дополнительный выходной мультиплексор, связанный с буфером команд и выходным регистром, и блок выбора секций, состоящий из связанных между собой запоминающего устройства кодов выбора секций, преобразователя кода выбора секций по алгоритму замещения элемента с наиболее длительным интервалом отсутствия обращения к нему, регистра хранения предыдущего кода выбора секции, сдвигового регистра и мультиплексора, при этом блок выбора секций связан с входным демультиплексором и секциями запоминающих устройств.

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| СПОСОБ И СИСТЕМА ВЫЧИСЛЕНИЯ УКАЗАТЕЛЯ ДЛЯ МАСШТАБИРУЕМОГО ПРОГРАММИРУЕМОГО КОЛЬЦЕВОГО БУФЕРА | 2006 |

|

RU2395835C2 |

| US 7633827 B2, 15.12.2009 | |||

| US 6609189 B1,19.08.2003. | |||

Авторы

Даты

2016-07-20—Публикация

2014-07-24—Подача