Область техники, к которой относится изобретение

Настоящее изобретение в общем относится к электронной схеме, предназначенной для приёма колебательного сигнала и вывода выходного сигнала на частоте, имеющей частотное отношение к колебательному сигналу, определяемое с помощью коэффициента деления, схеме автоматической фазовой подстройки частоты, схемы приёмопередатчика, а также радиостанции, содержащей такую электронную схему и способ частотного разделения.

Уровень техники

Поскольку радиосхемы становятся более сложными, а также проектируются для работы при всё более высоких частотах, элементы таких цепей имеют тенденцию потреблять всё большую мощность. Делители частоты являются важными элементами радиосхем и используются, например, для синтезирования сигналов с желаемой частотой и фазой. Например, многополосные радиосхемы основываются на способности генерировать сигналы на различных контролируемых частотах. Другим примером применения технологии формирования направленного сигнала является система, где на множество антенн подаются сигналы с контролируемой фазой, в этой системе расположение множества антенн обеспечивает желаемую направленную характеристику.

Прогнозируется, что сотовые системы радиосвязи могут использовать миллиметровые волны. Частоты в этих случаях могут находиться приблизительно в диапазоне от 15 до 60 ГГц. Для того чтобы использовать систему вне помещения, может использоваться более длинный циклический префикс по сравнению с домашними системами на 60 ГГц. Для этого может быть предпочтительным меньшее разнесение поднесущих частот при модуляции в мультиплексировании с ортогональным частотным разделением, однако в этом случае появляются более жёсткие требования к шуму из-за нестабильности фазы. В то же самое время технология формирования направленного сигнала, предпочтительно, поддерживается для увеличения диапазона и ёмкости системы. В этом случае используется большое количество элементов антенны. Сигнал на каждом элементе будет иметь индивидуальное смещение фазы, которое управляет направлением диаграммы направленности антенны. Одним из ключевых альтернативных вариантов использования является наложение фазовых смещений в гетеродинном сигнале. Частота гетеродина в таких случаях, предпочтительно, является программируемой, чтобы можно было выполнять операции на различных каналах и на различных диапазонах частот.

Вариант использования схематики для генерирования гетеродина, предпочтительно, стремится к достижению низкого фазового шума, индивидуально программируемой фазе, программируемой частоте, и/или распределению сигналов на все приёмопередатчики в системе формирования направленного сигнала, причём всё это осуществляется без потребления излишней энергии.

Поэтому желательно обеспечивать подход для электронной схемы, обеспечивающий один или более из упоминавшихся выше желательных признаков при умеренном потреблении энергии.

Сущность изобретения

В соответствии с первым аспектом изобретения, обеспечивается электронная схема, выполненная с возможностью принимать колебательный сигнал и выводить выходной сигнал на частоте, имеющей частотное отношение к колебательному сигналу, определяемое с помощью коэффициента деления. Электронная схема содержит первый делитель частоты, выполненный с возможностью принимать колебательный сигнал и выводить N сигналов, разделённых по частоте с различными фазами, второй делитель частоты, выполненный с возможностью принимать один из N сигналов, при этом разделение частоты принятого сигнала производится с помощью значения, заданного с помощью первого управляющего сигнала, обеспечиваемого для второго делителя частоты, N триггерных запирающих схем, каждая из которых выполнена с возможностью принимать соответствующий один из N сигналов на синхронизируемый вход соответствующей триггерной запирающей схемы и принимать выходной сигнал второго частотного делителя на входе соответствующей триггерной запирающей схемы, схему мультиплексора, выполненную с возможностью принимать выходные сигналы N триггерных запирающих схем и выводить сигнал, на котором основывается выходной сигнал, выбранный из принятых сигналов на основе второго управляющего сигнала, обеспеченного для схемы мультиплексора, и управляющая схема, выполненная с возможностью обеспечивать первый управляющий сигнал и второй управляющий сигнал на основе коэффициента разделения.

Сигнал, выходящий из схемы мультиплексора, может быть выходным сигналом электронной схемы.

Электронная схема может содержать выходную триггерную запирающую схему, выполненную с возможностью принимать колебательный сигнал на синхронизируемом входе выходной триггерной запирающей схемы, принимать сигнал, выходящий из схемы мультиплексора на входе выходной триггерной запирающей схемы, и выводить выходной сигнал электронной схемы.

Управляющая схема может быть машиной состояний, выполненной с возможностью обеспечивать первый и второй управляющие сигналы для каждого цикла выходного сигнала электронной схемы, основываясь на коэффициенте разделения и выбранной фазы с помощью схемы мультиплексора для предшествующего цикла выходного сигнала. Управляющая схема может содержать схему целочисленного делителя, выполненную с возможностью делить коэффициент деления на М и обеспечивать целочисленное значение результата деления и целочисленное значение остатка, счётчик по модулю М (modulo-M-counter), выполненный с возможностью принимать значение остатка в качестве входного и выходного сигнала, как синхронизированный вход, а также выводить значение счётчика и значение переноса, и суммирующую схему, выполненную с возможностью суммировать значение результата деления и значение переноса, чтобы формировать первый управляющий сигнал, при этом второй управляющий сигнал основывается на значении счётчика. Управляющая схема может содержать триггерную запирающую схему, выполненную с возможностью принимать значение счётчика в качестве входного, а один из выходов N триггерных запирающих схем в качестве синхронизирующего сигнала, при этом выходной сигнал из триггерной запирающей схемы является вторым управляющим сигналом.

В соответствии со вторым аспектом изобретения, обеспечивается схема автоматической фазовой подстройки частоты, содержащая делитель частоты, включающий в себя электронную схему согласно первому аспекту.

В соответствии с третьим аспектом, обеспечивается схема приёмопередатчика, содержащая схему автоматической фазовой подстройки частоты согласно второму аспекту.

В соответствии с четвёртым аспектом, обеспечивается радиостанция, содержащая схему приёмопередатчика согласно третьему аспекту, и антенное устройство, присоединённое к схеме приёмопередатчика.

В соответствии с пятым аспектом изобретения, обеспечивается способ частотного разделения колебательного сигнала. Способ содержит формирование М сигналов с различными фазами с помощью первого делителя частоты из колебательного сигнала, в котором каждый из М сигналов имеет частоту в отношении 1/М от колебательного сигнала, частотное разделение одного из М сигналов с помощью второго делителя частоты со значением, заданным с помощью первого управляющего сигнала, обеспеченного для второго делителя частоты, синхронизация М триггерных запирающих схем с соответствующим одним из М сигналов, чтобы обеспечивать соответствующий запирающийся выходной сигнал с выхода второго делителя частоты, отбор сигнала на основе второго управляющего сигнала из числа запирающихся выходных сигналов, на котором основывается выходной сигнал частотного разделения, обеспечение первого управляющего сигнала и второго управляющего сигнала на основе коэффициента деления, и вывод выходного сигнала на частоте, имеющей частотное соотношение с колебательным сигналом, определяемое с помощью коэффициента деления.

Выбранный запирающийся выходной сигнал может быть выходным сигналом.

Способ может содержать синхронизацию выходной триггерной запирающей схемы с колебательным сигналом, чтобы обеспечивать выходной сигнал из выбранного запирающегося выходного сигнала.

Обеспечение первого и второго управляющих сигналов может выполняться для каждого цикла выходного сигнала с помощью машины состояний, основываясь на коэффициенте деления, и выборе сигнала для предшествующего цикла выходного сигнала. Обеспечение первого и второго управляющих сигналов может содержать деление коэффициента деления на М с помощью целочисленного делителя, чтобы обеспечивать целочисленное значение результата деления и целочисленное значение остатка, счётчик по модулю М значения остатка, использующий выходной сигнал для синхронизирования, чтобы обеспечивать значение счётчика и значение переноса, и суммирование значения результата деления и значения переноса, чтобы формировать первый управляющий сигнал, при этом второй управляющий сигнал основывается на значении счётчика. Второй управляющий сигнал может быть сформирован как запирающееся значение для значения счётчика, синхронизированного с помощью выходного сигнала.

Другие задачи, признаки и преимущества настоящего изобретения будут понятны из последующего подробного описания, из прикреплённых зависимых пунктов формулы изобретения, а также из чертежей. В общем все термины, используемые в формуле изобретения, должны интерпретироваться в соответствии с их обычными значениями в данной технической области, до тех пор, пока это недвусмысленно не определяется в этом описании иным образом. Все ссылки на “a/an/the [element, device, component, means, step, etc]” (элемент, устройство, компонент, средство, этап, и т.д.) должны интерпретироваться открыто, как ссылка на, по меньшей мере, один пример из упоминавшихся элемента, устройства, компонента, средства, этапа и т.д., до тех пор, пока это недвусмысленно не определяется иным образом. Этапы любого раскрываемого здесь способа не должны выполняться в точно раскрываемом порядке, до тех пор, пока это недвусмысленно не определяется.

Краткое описание чертежей

Приведённая выше часть описания, а также дополнительные задачи, признаки и преимущества настоящего изобретения будут более понятны с помощью последующего иллюстративного и неограничивающего подробного описания предпочтительных вариантов осуществления настоящего изобретения со ссылками на прилагаемые чертежи.

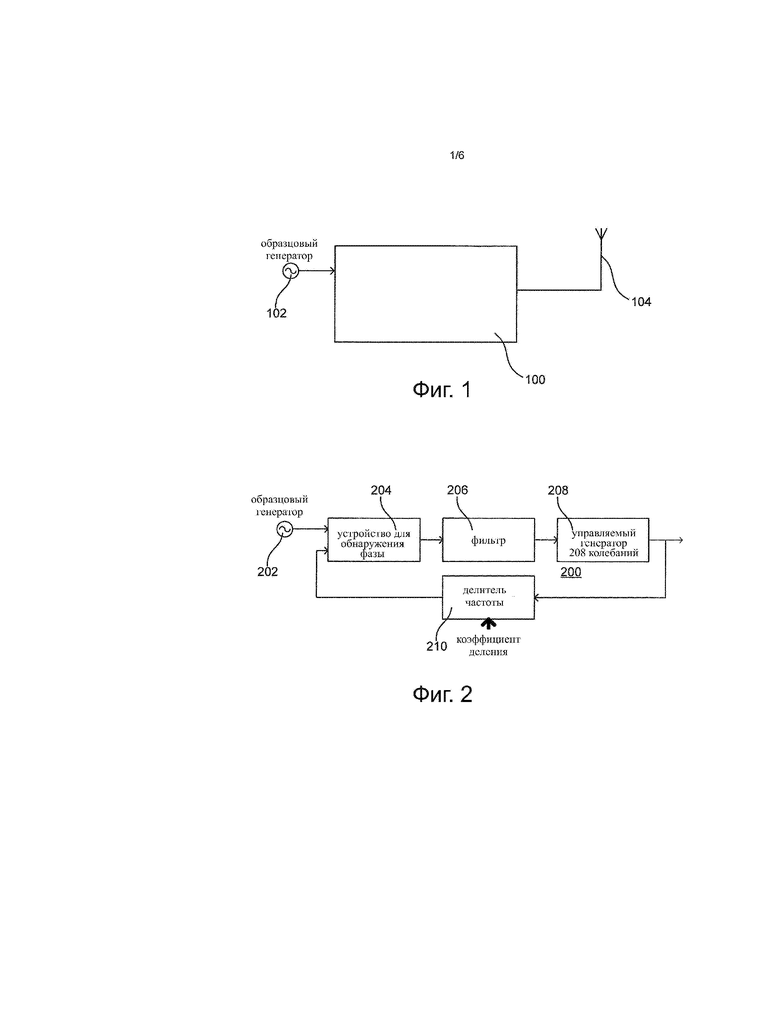

Фиг. 1 иллюстрирует приёмник, передатчик или приёмопередатчик, который обеспечивается опорным сигналом на точно определённой частоте от образцового генератора, чтобы они могли передавать/принимать сигналы на желаемой частоте с помощью антенны.

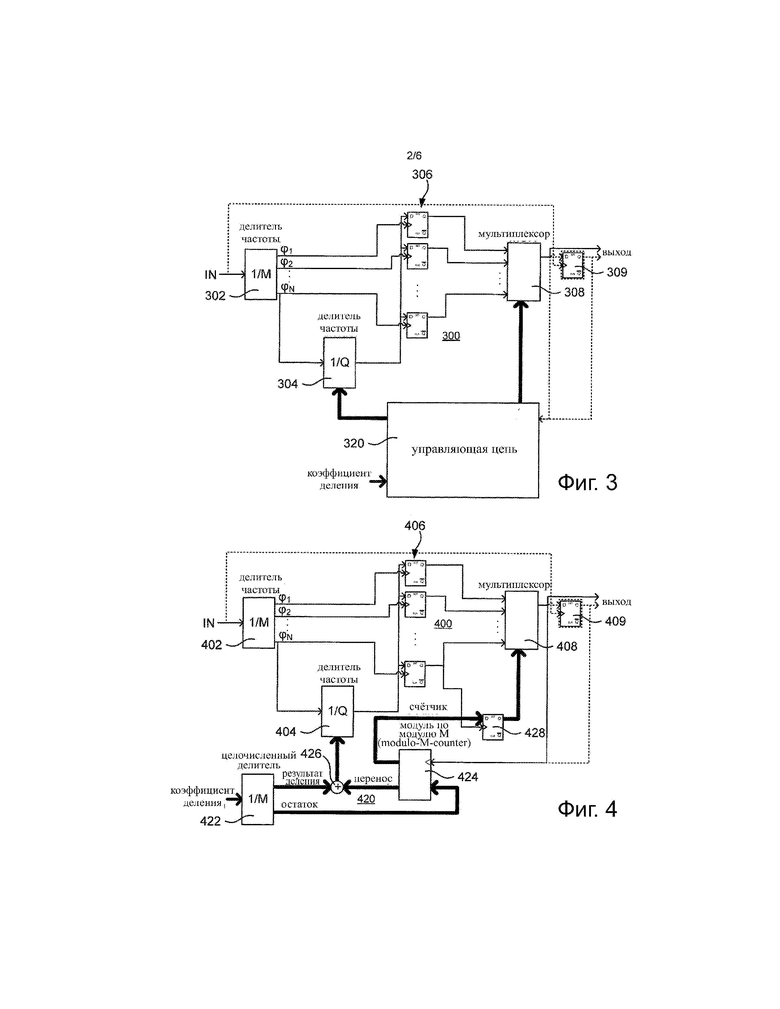

Фиг. 2 схематически иллюстрирует контур фазовой синхронизации.

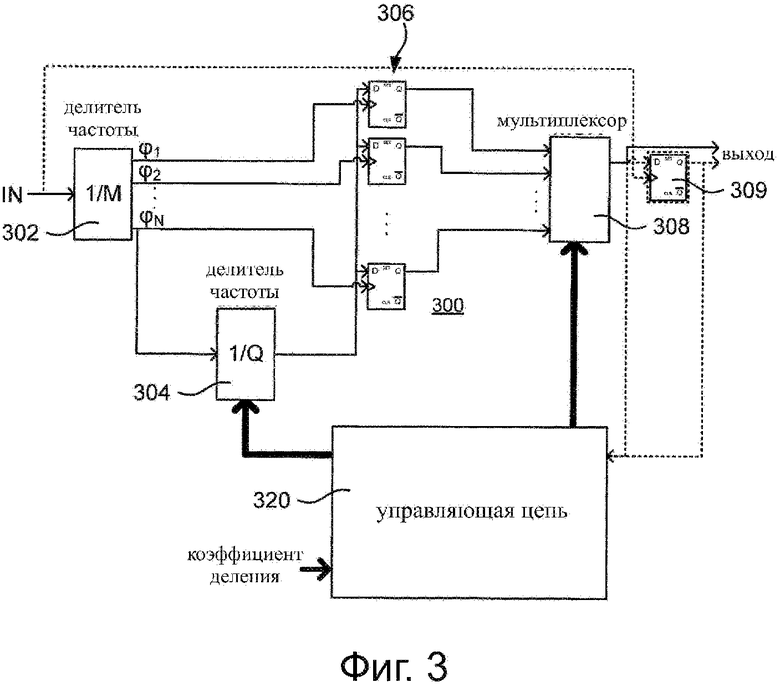

Фиг. 3 схематически иллюстрирует схему делителя частоты, в соответствии с вариантом осуществления изобретения.

Фиг. 4 схематически иллюстрирует схему делителя частоты, в соответствии с вариантом осуществления изобретения.

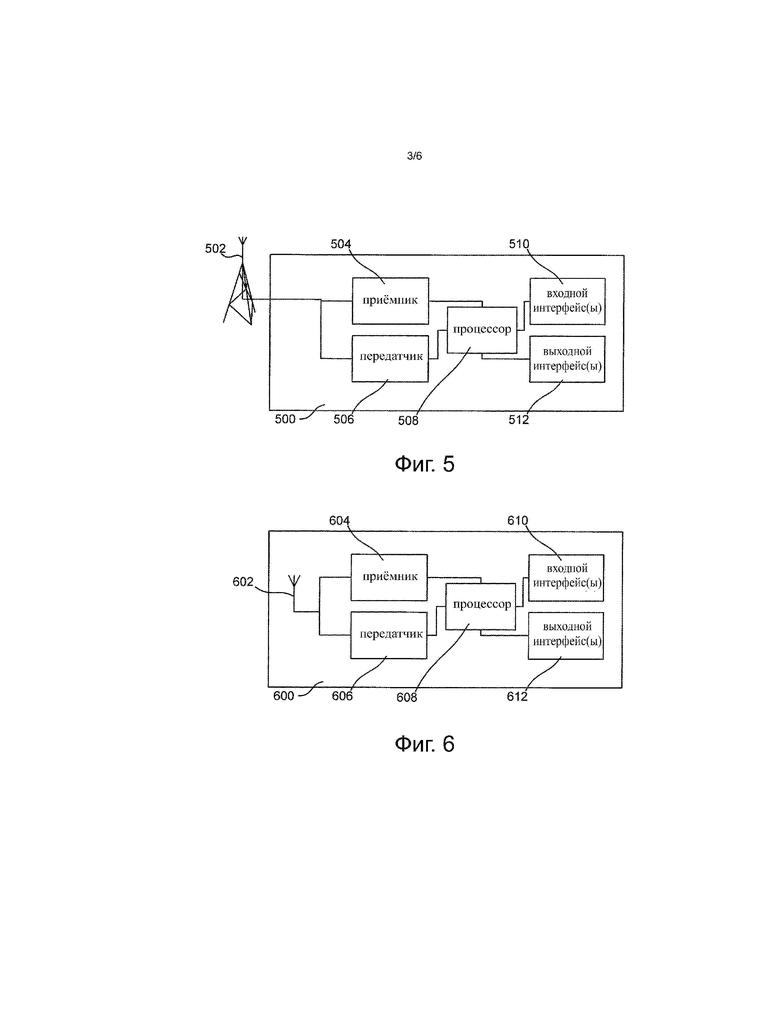

Фиг. 5 схематически иллюстрирует такой узел сети, в соответствии с вариантом осуществления изобретения.

Фиг. 6 схематически иллюстрирует такое оконечное устройство беспроводной сети связи, в соответствии с вариантом осуществления изобретения.

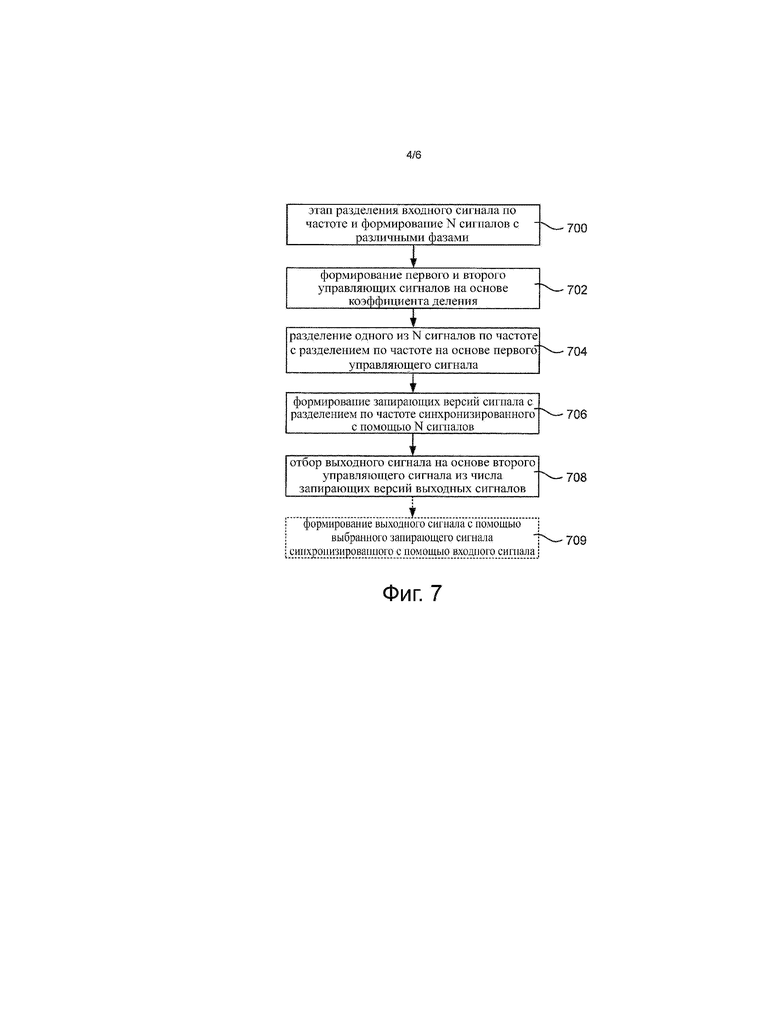

Фиг. 7 является блок-схемой последовательности процесса, иллюстрирующей способ частотного разделения, в соответствии с вариантом осуществления изобретения.

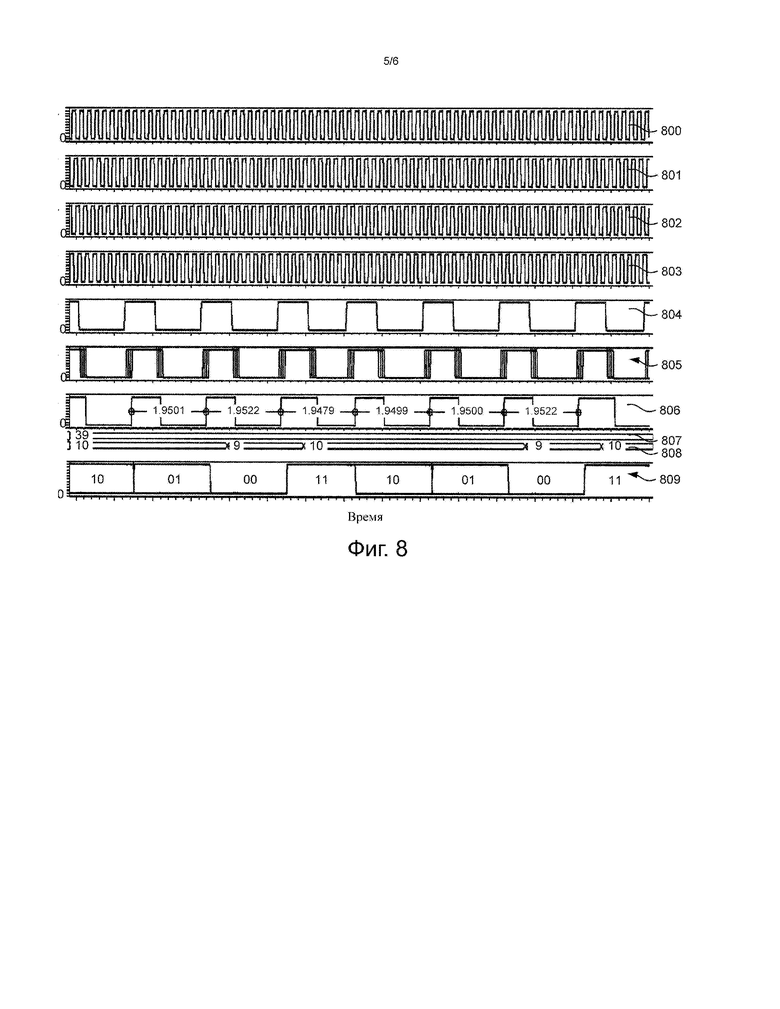

Фиг. 8 является диаграммой сигналов.

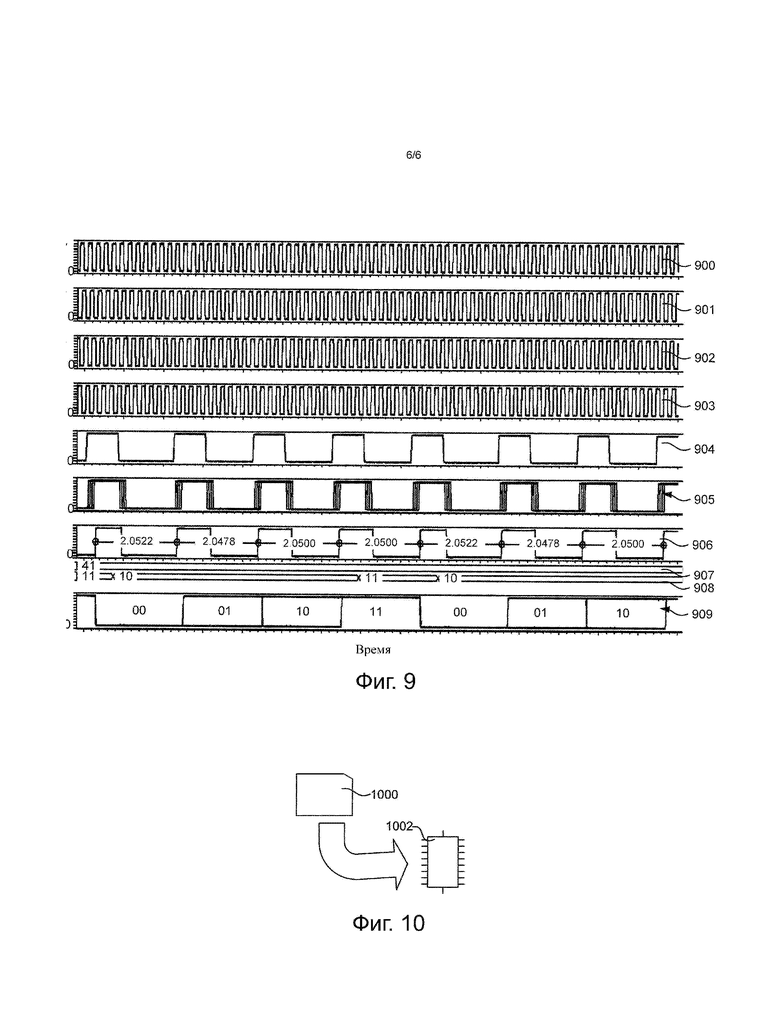

Фиг. 9 является диаграммой сигналов.

Фиг. 10 схематически иллюстрирует считываемую компьютером среду и процессор, выполненный с возможностью выполнять программный код, сохраняемый в считываемой компьютером среде.

Подробное описание

Фиг. 1 схематически иллюстрирует приёмник, передатчик или приёмопередатчик 100, который обеспечивается опорным сигналом на точно определённой частоте от образцового генератора 102, чтобы они могли передавать/принимать сигналы на желаемой частоте с помощью антенны 104. Образцовый генератор 102 обычно обеспечивает фиксированную частоту. Чтобы позволить отправление/передачу на желаемой частоте, частота синтезируется на основе опорного сигнала. Для этой цели может использоваться контур фазовой синхронизации (PLL). Для более сложных задач приёмника/ передатчика/ приёмопередатчика, например, для технологии формирования направленного сигнала, как уже обсуждалось в разделе «уровень техники», может использоваться не только частота желаемого сигнала; также это относится к правильной фазе.

Фиг. 2 схематически иллюстрирует контур фазовой синхронизации PLL 200. PLL принимает опорный сигнал от образцового генератора 202. PLL 200 содержит устройство 204 для обнаружения фазы, фильтр 206, управляемый генератор 208 колебаний и делитель частоты. Устройство 204 для обнаружения фазы сравнивает фазы опорного сигнала и копии разделённой частоты выходного сигнала управляемого генератора 208. Таким образом, устройство 204 для обнаружения фазы выводит сигнал, показывающий разницу фаз между сигналами. Выходной сигнал устройства 204 для обнаружения фазы фильтруется с помощью фильтра 206, чтобы обеспечивать надлежащий управляющий сигнал для управляемого генератора 206, который, в свою очередь, выводит колебательный сигнал, основываясь на этом управляющем сигнале. Управляемый генератор 208 может быть генератором, управляемым с помощью напряжения, в котором управляющий сигнал определяется с помощью напряжения. Также могут использоваться другие типы управляемых генераторов, например, генераторы, с цифровым управлением, в которых управляющий сигнал является цифровым значением. Колебательный сигнал, который выводится с помощью управляемого генератора 208, является выходным сигналом контура фазовой синхронизации PLL 200, и с помощью обратной связи выходного сигнала через делитель 210 частоты, контур PLL будет стремиться к заблокированному состоянию, где возвращённый с учётом обратной связи и разделённый сигнал по частоте становится равным опорному сигналу. Это подразумевает, что отношение между выходным сигналом контура фазовой синхронизации PLL 200 и опорным сигналом будет определяться с помощью делителя 210 частоты. Т.е. возвращённый разделённый сигнал с учётом обратной связи по частоте и опорный сигнал становятся равными в среднем по фазе и частоте с помощью устройства 204 для обнаружения фазы, обеспечивающего сигнал, показывающий разницу фаз, причём этот сигнал затем оказывает воздействие через структуру, которая иллюстрировалась ранее, на управляемый генератор 208. Таким образом, выражение «равный» в данном случае не должно истолковываться таким образом, что упоминавшиеся выше сигналы всё время являются точно такими же, а должно истолковываться таким образом, что возвращённый разделённый сигнал с учётом обратной связи по частоте является регулируемым с ограничениями, связанными с практическим вариантом применения, чтобы находиться по возможности как можно ближе по фазе и частоте к опорному сигналу. С помощью управления делителем 210 частоты посредством коэффициента деления, могут быть достигнуты желаемые свойства выходного сигнала контура фазовой синхронизации PLL 200. Грубо говоря, посредством возможности получения любого значения коэффициента деления, могут быть достигнуты любые свойства выходного сигнала для контура PLL 200. Варианты осуществления изобретения делителей частоты, иллюстрируемые в дальнейшем со ссылками на фиг. 3 и 4, предусматривают возможность использования множества коэффициентов деления, которые традиционно были труднодостижимыми.

Для работы с радиоканалом такого типа, как иллюстрировалось выше, желательно использование генерирования сигналов гетеродина с фазовым управлением. Эта тема обсуждалась, например, в работе “A PLL based 12 GHz LO generator with digital phase control in 90 nm CMOS” («Генератор LO (гетеродина) с частотой 12 ГГц на основе контура фазовой синхронизации PLL с цифровым фазовым управлением в комплементарном металлооксидном полупроводнике 90 нм»), авторы A. Axholt и H. Sjöland в Analog Integrated Circuits and Signal Processing (аналоговые интегральные микросхемы и обработка сигнала), том 67, № 3, стр. 309-318, 2011 г. и “A 60 GHz receiver front-end with PLL based phase controlled LO generation for phased-arrays” (Входные каскады приёмника на 60 ГГц с генерированием LO (гетеродина) с фазовым управлением на основе контура фазовой синхронизации PLL), авторы A. Axholt и H. Sjöland в Analog Integrated Circuits and Signal Processing (аналоговые интегральные микросхемы и обработка сигнала), том 80, № 1, стр. 23-32, 2014 г. Для осуществления технологии формирования направленного сигнала каждый элемент антенны присоединяется к приёмопередатчику, а каждый приёмопередатчик принимает сигналы гетеродина (LO) от контура фазовой синхронизации (PLL) с фазовым управлением. Все контуры PLL принимают общий опорный сигнал пониженной частоты, например, в низком гигагерцовом диапазоне. В этом способе достаточно распределить опорный сигнал по всему радиочипу, который может быть выполнен при намного более низкой мощности, чем непосредственное распределение сигнала гетеродина (LO). Затем контуры PLL будут локально увеличивать опорный сигнал до более высокой частоты и генерировать сдвиг на 90 градусов сигналов гетеродина (LO). Посредством использования общего опорного сигнала выходные сигналы контуров фазовой синхронизации (PLL) будут фиксированными по частоте и фазе. Управляемые цифровым способом источники тока могут использоваться для добавления тока в контурный фильтр PLL, что будет осуществлять очень точно управляемое смещение линейной фазовой характеристики выходного сигнала.

Чтобы сделать частоту программируемой с высоким разрешением, а также чтобы можно было использовать высокую опорную частоту кристалла, которая является желательной для достижения низкого шума, применяется так называемый N-дробный частотный синтез с дробным коэффициентом деления. В устройстве для частотного фрагментирования эффективное частотное разделение в схемы обратной связи не является целым числом. Этот процесс выполняется при наличии переменного модуля делителя, т.е. он чередует разделение посредством различных чисел. Это выполняется таким способом, что среднее число деления равно целевому значению. Анализируя частотный спектр последовательностей чисел деления, среднее значение будет создавать правильное значение постоянного тока (DC), сопровождаемое шумом квантования. В зависимости от того, каким образом выполнено изменение, шум квантования будет принимать различные спектральные формы. В классической схемы делитель модулируется периодически, создавая прочные тоны, называемые дробными паразитными составляющими. В настоящее время в цепях вместо этого является популярным использование дельта-сигма-модуляторов, которые вместо паразитных составляющих генерируют высокочастотный шум определённой формы. Наличие такого высокочастотного шума определённой формы является полезным, поскольку контур фазовой синхронизации PLL имеет низкочастотную характеристику, которая в этом случае подавляет его. Однако некоторые конструктивные ограничения на ширину полосы пропускания контура и характеристика фильтра должны соответствовать шуму квантования, которые должен подавляться до уровня ниже других источников шума. Для каждого элемента антенны приёмопередатчика в этом случае необходим очень быстрый делитель частоты с программируемым модулем.

При использовании делителя с фиксированным числом делений для самых высоких частот, который, например, может делить на два или четыре с помощью предварительного делителя частоты, подразумевается, что схематика является менее сложной. Деление на два или четыре также является выгодной, поскольку оно может создать квадратурный сигнал, необходимый для приёмопередатчика. Также выгодно сохранять эту первую схематику для разделения частоты настолько простой, насколько это возможно, посредством использования фиксированного числа для деления. Однако, проблема вытекает из этого частотного разрешения. Если последующие делители могут только делиться на целочисленные значения, разрешение становится равным М входных периодов синхронизирующих импульсов, где М является числом деления предварительного делителя частоты, которое равно двум или четырём в упоминавшемся выше примере. С помощью использования сдвига делителей на 90° и переключения между выходными фазами, где разница фаз между последующими фазами равна циклу генератора, управляемого напряжением (VCO), может быть восстановлено полное разрешение, например, таким образом, как обсуждается в работе “Sub-Integer Frequency Synthesis Using Phase-Rotating Frequency Dividers” (Синтез частоты Sub-Integer, с использованием делителей частоты с вращающейся фазой), автор - Brian A. Floyd в IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS (институт инженеров по электротехнике и радиоэлектронике, научные труды по теме цепей и систем I: официальные документы), том 55, №. 7, август 2008.

Один из способов работы мультимодульных делителей с вращением фаз является смещение между фазами непосредственно на выходе мультифазного делителя. При использовании только четырёх фаз, относительное смещение фаз достигает 90 градусов, что означает небольшое пересечение между импульсами с различными фазами. Это делает проблематичным переключение в мультигигагерцовом диапазоне. Если переключение не сделано в нужный момент времени, т.е. когда импульсы из последовательных фаз накладываются друг на друга, выходной сигнал имеет тенденцию содержать кратковременные импульсные помехи, которые возможно будут приводить к ошибкам на последующих этапах работы делителя. Одним из способов облегчения операции вращения фаз является дополнительное разделение и создание даже большего количества фаз, как например, обсуждается в работе “A 2.4-GHz Monolithic Fractional-N Frequency Synthesizer With Robust Phase-Switching Prescaler and Loop Capacitance Multiplier” (Монолитный N-дробный частотный синтезатор на 2,4 ГГц с помехоустойчивым предварительным делителем частоты с переключением частот и умножитель с ёмкостным контуром), написанной Keliu Shu, и др. в IEEE JOURNAL OF SOLID-STATE CIRCUITS (журнал института инженеров по электротехнике и радиоэлектронике по полупроводниковым интегральным схемам), том 38, № 6, июнь 2003. Разница фаз становится меньше, например, в описанной выше работе авторов Keliu Shu, и др., на 45 градусов, а смещение фаз между последовательными фазами является менее чувствительным к точности по времени. Недостатки этого решения состоят в том, что дерево делителя растёт, вызывая чрезмерное потребление энергии, а также в том, что параллельные делители могут запуститься в двух различных состояниях, с различным порядком фаз. Таким образом, необходимо действительное состояние, которое должно быть обнаружено и скорректировано.

Даже в том случае, если разница фаз сделана более меньше, ещё не даёт хорошую вероятность того, что возможно переключать между другими фазами, не являющимися соседними. По естественным причинам будет трудно переключать между фазой 0 и фазой 4 в фазовом вращателе с 8 равномерно разнесёнными фазами, покрывающими полный период. Общий способ достижения последовательных коэффициентов деления, с использованием (N+1)/N предварительных делителей частоты, должен применить так называемый счётчик “swallow counter”. Фазовый делитель-вращатель следует за двумя счётчиками, где S-счётчик, т.е. счётчик “swallow counter”, отсчитывает количество циклов с вращением, а Р-счётчик отсчитывает полное количество циклов с вращением и без него. При использовании фазового вращателя с 8 фазами, выходной сигнал или делится на 8, или делится на 9. Проблема с таким подходом состоит в том, что существует минимальный общий коэффициент деления, достижимый для полного покрытия коэффициентов деления. Это может звучать невероятно, но это подтверждается следующим примером: во-первых, при подсчёте 3 выходных импульса с вращением и затем 2 без вращения, общий выход составляет 8•3 + 9•2 = 42. Изменяем на 8•2 + 9•3 = 43 выходов последующих коэффициентов деления и так далее вплоть до 8•0 + 9•5 = 45. С P=6, минимальный коэффициент деления составляет 8•6 + 9•0 = 48. То есть, с делителем 8/9, 46-47 не являются действительными коэффициентами деления. Это предполагает требование на самую высокую возможную опорную частоту. Рассмотрим, например, опорную частоту ≈ 500 МГц, которая будет проблематичной с частотой, управляемой с помощью напряжения, составляющей 20 Гц, когда 7 или более последующих коэффициентов деления являются общими для использования в схемах автоматической фазовой подстройки частоты (PLL) с дельта-сигма N-дробной модуляцией.

Фиг. 3 схематически иллюстрирует схему 300 делителя частоты, действующей как фазовый вращатель, который использует другой способ мультиплексирования сигналов. Первый конфигурируемый делитель 302 частоты работающий на 1/М, например, на ¼ от входной частоты, предпринимает грубое разбиение и повторную тактовую синхронизацию, произведённую с помощью N фаз φ1, φ2, …, φN даёт хорошее разрешение. Например, N может быть равно четырём, как используется в примере, иллюстрируемом ниже, но может составлять, например, 2P, где P является целым числом, или N может быть любым другим целым числом, подходящим для этого варианта.

В последующем примере, M выбирается равным 4 и N выбирается равным 4. Преимущество такого подхода состоит в том, что различия по фазе между выходными импульсами после первоначального деления на 4 (0°, 90°, 180°, 270°) разделяются с помощью значения Q деления во втором делителе 304 частоты. Т.е. относительная разница по фазе между фазами, идущими в мультиплексор, уменьшается до 0°, (90/Q)°, (180/Q)°, (270/Q)°. Следовательно, например, с Q>4 возможно делать смещения по фазе между не последовательными фазами. Это позволяет использовать только один конфигурируемый делитель и мультиплексор 308.

N сформированных версий сигнала, разделённого по частоте с различными фазами, используются, соответственно, для тактовой синхронизации триггерных запирающих схем 306. Это позволяет обеспечивать входной сигнал к триггерным запирающим схемам 306, с соответствующим фазовым смещением. В качестве входного сигнала к триггерным запирающим схемам 306 используется выходной сигнал из второго делителя 304 частоты. Второй делитель 304 частоты является конфигурируемым и обеспечивает деление частоты на Q, где Q определяется с помощью первого управляющего сигнала. Выходные сигналы триггерных запирающих схем 306 обеспечиваются для мультиплексора, где выходной сигнал схемы 300 делителя частоты выбирается на основе второго управляющего сигнала.

Сигнал, обеспечиваемый из мультиплексора 308, может в этом случае заново синхронизироваться с входным сигналом, например, с помощью триггерной запирающей схемы 309, причём эта синхронизация будет улучшать характеристики в отношении кратковременных внезапных изменений амплитуды или фазы сигнала выходного сигнала схемы делителя частоты.

Цифровое управление числа деления применяется на входе второго делителя 304 и на управляющем входе мультиплексора 308. Управление может обеспечиваться с помощью управляющей схемы 320. Управление может привлекать использование машины состояний, которая сохраняет дорожку выбранной в настоящее время фазы, в зависимости от которой назначаются последующие коэффициенты деления, выбирается следующее значение Q, выходная фаза и момент переключения. Хотя частота является относительно низкой и фазы пересекаются, может быть гарантировано переключение фаз без кратковременных внезапных изменений амплитуды или фазы сигнала. Пример сценария с фиксированным коэффициентом деления, равным 41, будет требовать следующую структуру: (Q, MUX): (10,1), (10,2), (10,3), (11,0), (10,1), (10,2), (10,3), (11,0), …

Фиг. 4 схематически иллюстрирует схему 400 делителя частоты, действующую как фазовый вращатель, которая аналогична схемы, проиллюстрированной на фиг. 3, при этом она содержит первый делитель 402 частоты, второй делитель 404 частоты, N триггерных запирающих схем 406, и мультиплексор 408, а также по дополнительному выбору содержит триггерную запирающую схему 409 выходного сигнала. Управляющая логика, генерирующая управление для первого делителя 402 частоты и мультиплексора 408, может использоваться таким образом, как схематически иллюстрируется на фиг. 4. В зависимости от варианта применения второго делителя частоты, может быть необходима дополнительная схематика для управления моментом переключения для двух управляющих сигналов. Если следовать приведённому выше примеру, использующему вышеуказанный коэффициент деления, становится ясно, что управляющая логика может генерировать последовательность. Может обеспечиваться элемент 428 задержки для управляющего сигнала мультиплексора, поскольку второй делитель 404 частоты обычно нуждается в коэффициенте деления перед запуском нового выходного цикла. Элемент 428 задержки может быть триггером, синхронизированным с помощью одного из сигналов со смещённой фазой, обеспечиваемого для мультиплексора 408. Предпочтительно, один из сигналов со смещённой фазой с самым большим смещением по фазе выбирается для синхронизации, чтобы обеспечить работу без кратковременных внезапных изменений амплитуды или фазы сигнала.

Прикладываемый коэффициент деления, например, равный 41, как в упоминавшемся выше примере, обеспечивается для целочисленного делителя 422, который обеспечивает значение результата деления и значение остатка на основе коэффициента М деления, прикладываемого с помощью делителя 402 частоты. Значение остатка обеспечивается для счётчика 424 по модулю М (modulo-M-counter), который синхронизируется с помощью выходного сигнала схемы 400 делителя частоты. Счётчик по модулю М обеспечивает значение счётчика и значение переноса. Значение переноса обеспечивается для суммирующего устройства 426, которое добавляет значение переноса к значению результата деления, чтобы обеспечивать управляющий сигнал для второго делителя частоты, которое управляется таким образом, чтобы выполнять частотное разделение на основе управляющего сигнала, т.е. частоту деления с помощью добавленного значения. Счётчик по модулю М обеспечивает значение счётчика для элемента 428 задержки, который выводит значения счётчика, основываясь на согласовании по времени, когда все входы к мультиплексору 408 установлены, как управляющий сигнал для мультиплексора 408, который выбирает один из сигналов со смещённой фазой, соответственно, к выходу. Этот механизм машины состояний, содержащий целочисленный делитель 422, счётчик 424 по модулю М, суммирующее устройство 426, и элемент 428 задержки, таким образом даёт возможность схемы 400 делителя частоты обеспечивать разделение частоты, в соответствии с желаемым коэффициентом деления, как обсуждалось выше. Фиг. 8 и 9 являются диаграммами, иллюстрирующими, соответственно, примеры для коэффициентов 39 и 41 деления, где может использоваться этот механизм. Эти коэффициенты деления являются выбранными примерами для иллюстрации, поскольку они являются примерами для коэффициентов деления, которые обычно являются сложными для достижения.

Вариант осуществления изобретения, проиллюстрированный со ссылкой на фиг. 4, иллюстрирует механизм машины состояний, основанной на нескольких стандартных операционных элементах, взаимодействующих особым способом, для того чтобы реализовать схему управления. Она обеспечивает надёжное и требующее малой мощности функционирование также при очень высоких частотах. Управляющая схема может также быть реализована другими способами, например, смешанным решением, с использованием программных и аппаратных средств, обеспечивающим последовательность средств управления в отношении второго делителя частоты и мультиплексора. Такое решение может, например, использовать таблицы преобразования для обеспечения последовательности для различных коэффициентов деления.

Как показано на фиг.1, приёмник/передатчик/приёмопередатчик могут использовать один или более контуров PLL, включающих в себя делитель частоты, как иллюстрировалось выше, и применяться в узле беспроводной коммуникационной сети, например, в таком узле сети, как базовая станция сотовой сети или точка доступа коммуникационной сети малой дальности, и т.д. Фиг. 5 схематически иллюстрирует такой узел 500 сети согласно варианту осуществления изобретения. Узел 500 сети, который становится частью сети доступа системы, в которой он функционирует, содержит антенное устройство 502, содержащее одну или более антенн, один или более приёмников 504 и один или более передатчиков 506. Узел 500 сети может также содержать процессор 508, выполненный с возможностью управлять приёмником 504 и/или передатчиком 506. Узел 500 сети может также содержать один или более входных интерфейсов 510 и/или выходных интерфейсов 512. Здесь интерфейсы 510, 512 могут содержать интерфейсы сигнализации, интерфейсы оператора и т.д.

Возвращаясь снова к фиг. 1, приёмник/передатчик/приёмопередатчик могут использовать один или более контуров PLL, включающих в себя делитель частоты, как иллюстрировалось выше, и применяться в оконечном устройстве беспроводной коммуникационной сети, например в телефоне, модеме, коммуникационной плате и т.д., которое может быть выполнено с возможностью функционирования в сотовой сети и/или коммуникационной сети малой дальности и т.д. Фиг. 6 схематически иллюстрирует такое оконечное устройство 600 согласно варианту осуществления изобретения. Оконечное устройство 600 содержит антенное устройство 602, содержащее одну или более антенн, один или более приёмников 604, и один или более передатчиков 606. Оконечное устройство 600 может также содержать процессор 608, выполненный с возможностью управлять приёмником 604 и/или передатчиком 606. Оконечное устройство 600 может также содержать один или более входных интерфейсов 610 и/или выходных интерфейсов 612. Здесь интерфейсы 510, 512 могут содержать интерфейсы сигнализации, интерфейсы пользователя и т.д.

Фиг. 7 является блок-схемой последовательности процесса, иллюстрирующей способ частотного разделения, в соответствии с вариантом осуществления изобретения. Входной сигнал на этапе 700 разделяется по частоте с помощью делителя М таким образом, что формируется N сигналов с различными фазами. Основываясь на желаемом коэффициенте разделения, на этапе 702 формируются первый управляющий сигнал и второй управляющий сигнал. Управляющие сигналы могут, например, формироваться с помощью механизма машины состояний, как иллюстрировалось выше. Один из N сигналов используется для разделения частоты с помощью делителя Q разделения частоты, основываясь на первом управляющем сигнале. Запирающие сигналы формируются на этапе 706 посредством синхронизации триггеров, соответственно, с N сигналами где запирающие сигналы основываются на частоте сигнала, разделённой посредством делителя Q. Среди этих запирающих сигналов один из них выбирается на этапе 708, основываясь на втором управляющем сигнале для формирования выходного сигнала разделения частоты. По необязательному выбору, выходной сигнал может запираться на этапе 709, во время которого синхронизация может быть выполнена посредством входного сигнала делителя частоты.

В данном случае управляющие сигналы обеспечиваются в качестве управляющих последовательностей, основываясь на коэффициенте разделения для разделения частоты. Управляющие последовательности могут быть заранее рассчитаны и быть доступны из памяти, например, регистра сдвига. В качестве альтернативы, управляющие последовательности обеспечиваются с помощью машины состояний. Машина состояний может быть реализована посредством целочисленного деления коэффициента разделения на М, при этом целочисленное деление обеспечивает величину остатка для использования в качестве счётчика по модулю М, в котором второй управляющий сигнал основывается на значении счёта, т.е. значение второго управляющего сигнала является значением счёта и обеспечивается, когда всегда запирающие сигналы были сформированы на этапе 706. Значение переноса счётчика по модулю М добавляется к значению результата целочисленного деления, чтобы сформировать значение Q первого управляющего сигнала.

Фиг. 8 является диаграммой сигналов, иллюстрирующей несколько сигналов, которые обсуждались выше. Сигналы 800-803 иллюстрируют сформированные N сигналов, в данном примере - в количестве 4, с различными фазами, обеспеченными первым делителем 302, 402 частоты. Сигнал 804 иллюстрирует выход со второго делителя 304, 404 частоты. Сигналы 805 иллюстрируют версии сигналов, обеспеченных соответствующей триггерной запирающей схемой 306, 406, т.е. доступных на входах мультиплексора 308, 408 и, таким образом, для выбора. Сигнал 806 иллюстрирует выбранный выходной сигнал схемы 300, 400 делителя частоты. Сигнал 807 иллюстрирует управляющий сигнал, обеспеченный для схемы делителя частоты, позволяющий использовать коэффициент деления. В примере, проиллюстрированном на фиг. 8, этот коэффициент равен 39. Сигнал 808 иллюстрирует первый управляющий сигнал, обеспеченный для второго делителя 304, 404 частоты, который здесь показывается таким образом, что он переключается между 9 и 10, и последовательность может быть видна в изменении цикла сигналов 804 и 805. Сигналы 809 иллюстрируют второй управляющий сигнал, обеспеченный для мультиплексора 308, 408 с целью выбора выходного сигнала 806.

Фиг. 9 является диаграммой сигналов, аналогичной фиг. 8, иллюстрирующей некоторые из сигналов, которые обсуждались выше, но для другого коэффициента разделения, т.е. 41. Сигналы 800-903 иллюстрируют сформированные N сигналов, в данном случае в количестве 4, с различными фазами, обеспеченными первым делителем 302, 402 частоты. Сигнал 904 иллюстрирует выход со второго делителя 304, 404 частоты. Сигналы 905 иллюстрируют версии сигналов, обеспеченных соответствующей триггерной запирающей схемой 306, 406, т.е. доступные на входах мультиплексора 308, 408 и, таким образом, для выбора. Сигнал 906 иллюстрирует выбранный выходной сигнал схемы 300, 400 делителя частоты. Сигнал 907 иллюстрирует управляющий сигнал, обеспеченный для схемы делителя частоты, позволяющий использовать коэффициент деления. В примере, проиллюстрированном на фиг. 9, этот коэффициент равен 41. Сигнал 908 иллюстрирует первый управляющий сигнал, обеспеченный для второго делителя 304, 404 частоты, который здесь показывается таким образом, что он переключается между 10 и 11, и последовательность может быть видна в изменении цикла сигналов 904 и 905. Сигналы 909 иллюстрируют второй управляющий сигнал, обеспеченный для мультиплексора 308, 408 для выбора выходного сигнала 906.

Способы, выполненные в соответствии с настоящим изобретением, для некоторых вариантов осуществления изобретения могут быть подходящими для реализации с помощью средства обработки данных, такого как компьютеры и/или процессоры, особенно для случая, когда последовательность для первого управляющего сигнала и второго управляющего сигнала обеспечивается посредством решения с использованием программных и аппаратных средств, как обсуждалось выше. Следовательно, обеспечиваются компьютерные программы, содержащие инструкции, выполненные с возможностью вызывать выполнение средством обработки данных, процессором или компьютером этапов любого из способов, согласно любому из вариантов осуществления изобретения, описанных со ссылкой на фиг. 7. Компьютерные программы предпочтительно содержат программный код, который хранится в машиночитаемом носителе 1000, как иллюстрируется на фиг. 10, который может загружаться и исполняться с помощью средства обработки данных, процессора или компьютера 1002, для того чтобы вызывать выполнение способов, соответственно, согласно вариантам осуществления настоящего изобретения, предпочтительно согласно любому из вариантов осуществления изобретения, описанных со ссылкой на фиг. 7. Компьютер 1002 и компьютерный программный продукт 1000 могут быть выполнены с возможностью исполнять программный код последовательно, когда действия любого из способов выполняются поэтапно. Средство обработки данных, процессор или компьютер 1002, предпочтительно, что является обычным, рассматриваются как встроенная система. Таким образом, изображённые на фиг. 10 машиночитаемый носитель 1000 и компьютер 1002 следует истолковывать как средства, приведённые только для иллюстративных целей, чтобы обеспечивать понимание принципа, и не следует истолковывать как любую прямую иллюстрацию элементов.

Изобретение описано выше в основном со ссылками на некоторые варианты осуществления изобретения. Однако, как легко поймут специалисты в данной области техники, другие варианты осуществления изобретения, отличные от раскрытых выше, в равной степени возможны в пределах объёма изобретения, что определяется прилагаемой формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНТЕЗАТОР ДРОБНЫХ КОГЕРЕНТНЫХ ЧАСТОТ С ФАЗОВОЙ СИНХРОНИЗАЦИЕЙ | 1998 |

|

RU2208904C2 |

| СИНТЕЗАТОР ЧАСТОТ | 2010 |

|

RU2434322C1 |

| АДАПТИВНЫЙ СИНТЕЗАТОР ЧАСТОТ С КОММУТАЦИЕЙ ЭЛЕМЕНТОВ КОЛЬЦА ФАЗОВОЙ АВТОПОДСТРОЙКИ | 2010 |

|

RU2419201C1 |

| ЦИФРОВОЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2021 |

|

RU2766442C1 |

| УСТРОЙСТВА И СПОСОБЫ ПОДСТРОЙКИ ЧАСТОТЫ В СИНТЕЗАТОРЕ ЧАСТОТ С МНОЖЕСТВОМ ВЫХОДОВ | 2008 |

|

RU2476990C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ УМЕНЬШЕНИЯ ФАЗОВЫХ СКАЧКОВ ПРИ ПЕРЕКЛЮЧЕНИИ ИСТОЧНИКОВ СИНХРОНИЗАЦИИ | 2002 |

|

RU2288543C2 |

| Широкодиапазонный генератор импульсов с кратно дробной автоподстройкой частоты | 2019 |

|

RU2716222C1 |

| СИНТЕЗАТОР С ИЗМЕНЯЕМОЙ ЧАСТОТОЙ, СПОСОБ СИНТЕЗА ЧАСТОТЫ СИГНАЛА В СИНТЕЗАТОРЕ И РАДИОТЕЛЕФОН | 1992 |

|

RU2153223C2 |

| СПОСОБЫ И УСТРОЙСТВО ДЛЯ ДИНАМИЧЕСКОГО МАСШТАБИРОВАНИЯ ЧАСТОТЫ СХЕМЫ ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ ДЛЯ МИКРОПРОЦЕССОРОВ | 2008 |

|

RU2461961C2 |

| ФОРМИРОВАНИЕ СИГНАЛА ГЕНЕРАТОРА КОЛЕБАНИЙ С ПОДАВЛЕНИЕМ ПАРАЗИТНЫХ ПИКОВ В УСТРОЙСТВЕ БЕСПРОВОДНОЙ СВЯЗИ | 2008 |

|

RU2454792C2 |

Группа изобретений относится к вычислительной технике и может быть использована для приема колебательного сигнала и вывода выходного сигнала на частоте, имеющей частотное отношение к колебательному сигналу, определяемое с помощью коэффициента разделения. Техническим результатом является уменьшение потребляемой мощности. Устройство содержит первый делитель частоты, принимающий колебательный сигнал и выводящий N сигналов, разделённых по частоте с различными фазами, второй делитель частоты, принимающий один из N сигналов, при этом разделение частоты принятого сигнала с помощью значения, заданного с помощью первого управляющего сигнала, обеспечивается для второго делителя частоты, N триггерных запирающих схем, выполненных с возможностью принимать соответствующий один из N сигналов на синхронизируемый вход соответствующей триггерной запирающей схемы и принимать выходной сигнал второго делителя частоты на входе соответствующей триггерной запирающей схемы, схему мультиплексора и управляющую схему. 5 н. и 10 з.п. ф-лы, 10 ил.

1. Электронная схема (300, 400), выполненная с возможностью принимать колебательный сигнал и выводить выходной сигнал на частоте, имеющей частотное отношение к колебательному сигналу, определяемое с помощью коэффициента разделения, при этом электронная схема (300, 400) содержит

первый делитель (302, 402) частоты, выполненный с возможностью принимать колебательный сигнал и выводить N сигналов, разделённых по частоте с различными фазами (φ1, φ2, …, φN);

второй делитель (304, 404) частоты, выполненный с возможностью принимать один из N сигналов, при этом разделение частоты принятого сигнала с помощью значения, заданного с помощью первого управляющего сигнала, обеспечивается для второго делителя частоты;

N триггерных запирающих схем (306, 406), каждая из которых выполнена с возможностью принимать соответствующий один из N сигналов на синхронизируемый вход соответствующей триггерной запирающей схемы (306, 406) и принимать выходной сигнал второго делителя (304, 404) частоты на входе соответствующей триггерной запирающей схемы (306, 406);

схему (308, 408) мультиплексора, выполненную с возможностью принимать выходные сигналы N триггерных запирающих схем (306, 406) и выводить сигнал, на котором основывается выходной сигнал, выбранный из принятых сигналов на основе второго управляющего сигнала, обеспеченного для схемы (308, 408) мультиплексора; и

управляющую схему (320, 420), выполненную с возможностью обеспечивать первый управляющий сигнал и второй управляющий сигнал на основе коэффициента разделения.

2. Электронная схема (300, 400) по п. 1, в которой сигнал на выходе схемы мультиплексора является выходным сигналом электронной схемы.

3. Электронная схема (300, 400) по п. 1, содержащая выходную триггерную запирающую схему (309, 409), выполненную с возможностью принимать колебательный сигнал на синхронизируемом входе выходной триггерной запирающей схемы (309, 409), принимать сигнал, выходящий из схемы (308, 408) мультиплексора на входе выходной триггерной запирающей схемы (309, 409), и выводить выходной сигнал электронной схемы (300, 400).

4. Электронная схема (300, 400) по любому из пп. 1-3, в которой управляющая схема (320, 420) является машиной состояний, выполненной с возможностью обеспечивать первый и второй управляющие сигналы для каждого цикла выходного сигнала электронной схемы (300, 400), основываясь на коэффициенте разделения, и выбранной фазы с помощью схемы (308, 408) мультиплексора для предшествующего цикла выходного сигнала.

5. Электронная схема (400) по п. 4, в которой управляющая схема (420) содержит:

схему (422) целочисленного делителя, выполненную с возможностью делить коэффициент деления на М и обеспечивать целочисленное значение результата деления и целочисленное значение остатка;

счётчик (424) по модулю М, выполненный с возможностью принимать значение остатка в качестве входного и выходного сигнала, как синхронизируемый вход, а также выводить значение счётчика и значение переноса;

и схему (426) суммирующего устройства, выполненную с возможностью суммировать значение результата деления и значение переноса, чтобы формировать первый управляющий сигнал,

при этом второй управляющий сигнал основывается на значении счётчика.

6. Электронная схема (400) по п. 5, в которой управляющая схема (420) содержит триггерную запирающую схему (428), выполненную с возможностью принимать значение счётчика в качестве входного, а один из выходов N триггерных запирающих схем (406) в качестве синхронизирующего сигнала, при этом выходной сигнал из триггерной запирающей схемы (428) является вторым управляющим сигналом.

7. Схема автоматической фазовой подстройки частоты, содержащая делитель частоты, включающий в себя электронную схему (300, 400) по любому из пп. 1-6.

8. Схема (500, 600) приёмопередатчика, содержащая схему автоматической фазовой подстройки частоты по п. 7.

9. Радиостанция, содержащая

схему (500, 600) приёмопередатчика по п. 8 и

антенное устройство (502, 602), присоединённое к схеме (500, 600) приёмопередатчика.

10. Способ частотного разделения колебательного сигнала, содержащий:

формирование (700) М сигналов с различными фазами с помощью первого делителя частоты из колебательного сигнала, в котором каждый из М сигналов имеет частоту в отношении 1/М от колебательного сигнала;

частотное разделение (704) одного из М сигналов с помощью второго делителя частоты со значением, заданным с помощью первого управляющего сигнала, обеспеченного для второго делителя частоты;

синхронизацию (706) М триггерных запирающих схем с соответствующим одним из М сигналов, чтобы обеспечивать соответствующий запирающий выходной сигнал с выхода второго делителя частоты;

отбор (708) сигнала на основе второго управляющего сигнала из числа запирающих выходных сигналов, на котором основывается выходной сигнал частотного разделения;

обеспечение (702) первого управляющего сигнала и второго управляющего сигнала на основе коэффициента разделения и

вывод выходного сигнала на частоте, имеющей частотное соотношение с колебательным сигналом, определяемое с помощью коэффициента разделения.

11. Способ по п. 10, в котором выбранный запирающий выходной сигнал является выходным сигналом.

12. Способ по п. 10, содержащий синхронизацию (709) выходной триггерной запирающей схемы с колебательным сигналом, чтобы обеспечивать выходной сигнал от выбранного запирающего выходного сигнала.

13. Способ по любому из пп. 10-12, в котором обеспечение (702) первого и второго управляющих сигналов выполняется для каждого цикла выходного сигнала с помощью машины состояний, основываясь на коэффициенте разделения и выборе сигнала для предшествующего цикла выходного сигнала.

14. Способ по п. 13, в котором обеспечение (702) первого и второго управляющих сигналов содержит

деление коэффициента разделения на М с помощью целочисленного делителя, чтобы обеспечивать целочисленное значение результата деления и целочисленное значение остатка;

счётчик по модулю М значения остатка, использующий выходной сигнал для синхронизации, чтобы обеспечивать значение счётчика и значение переноса; и

суммирование значения результата деления и значения переноса, чтобы формировать первый управляющий сигнал,

при этом второй управляющий сигнал основывается на значении счётчика.

15. Способ по п. 14, в котором второй управляющий сигнал формируется как запирающее значение для значения счётчика, синхронизированного с помощью выходного сигнала.

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| US 6542013 B1, 01.04.2003 | |||

| RU 2058667 C1, 20.04.1996 | |||

| Устройство автоматической подстройки частоты | 1984 |

|

SU1259482A1 |

Авторы

Даты

2018-10-02—Публикация

2015-06-16—Подача