Изобретение относится к автоматике и аналоговой вычислительной технике и может быть использовано для построения функциональных узлов аналоговых вычислительных машин, средств автоматического регулирования и управления, аналоговых процессоров и др.

Известны ранговые селекторы (см., например, авт. св. СССР 1262531, кл. G06G 7/25, 1986 г.), которые выполняют селекцию сигнала только (n+1)-го ранга (наибольшего сигнала) из нескольких аналоговых сигналов x1,…,xn+1.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных ранговых селекторов, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется селекция сигнала любого заданного ранга r ∈ {1, …, n+1}.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип ранговый селектор (патент РФ 2338250, кл. G06G 7/25, 2008 г.), который содержит дифференциальные компараторы, элементы И, ключи, резисторы, RS-триггеры и выполняет селекцию из n+1 аналоговых сигналов сигнала любого заданного ранга r ∈ {1, …, n+1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся большие аппаратурные затраты.

Техническим результатом изобретения является уменьшение аппаратурных затрат при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в ранговом селекторе, содержащем n дифференциальных компараторов, n элементов И, n+1 резисторов, n+1 RS-триггеров и 4n+3 ключей, которые сгруппированы в n+1 групп так, что j-я  группа содержит первый, третий и второй ключи, выполненные соответственно замыкающими и размыкающим, а i-я

группа содержит первый, третий и второй ключи, выполненные соответственно замыкающими и размыкающим, а i-я  группа дополнительно содержит четвертый ключ, выполненный размыкающим, объединенные выходы первого, второго и объединенные выходы третьего, четвертого ключей k-й

группа дополнительно содержит четвертый ключ, выполненный размыкающим, объединенные выходы первого, второго и объединенные выходы третьего, четвертого ключей k-й  группы соединены соответственно с входом второго и входом четвертого ключей (k+1)-й группы, объединенные выходы первого, второго ключей n-й группы образуют информационный выход рангового селектора, выход третьего и объединенные выходы первого, второго ключей (n+1)-й группы соединены соответственно с входом четвертого и входом второго ключей первой группы, вход третьего ключа j-й группы соединен через j-й резистор с шиной нулевого потенциала, а вход первого и вход второго ключей i-й группы соединены соответственно с неинвертирующим и инвертирующим входами i-го дифференциального компаратора, подсоединенного выходом к первому входу i-го элемента И, выход и второй вход которого соединены соответственно с управляющим входом четырех ключей i-й группы и неинвертирующим выходом i-го RS-триггера, подсоединенного входом установки к первому настроечному входу рангового селектора и входу установки (n+1)-го RS-триггера, неинвертирующий выход которого соединен с управляющим входом трех ключей (n+1)-й группы, в которой второй ключ имеет вход, а вход первого ключа соединен с (n+1)-ым информационным входом рангового селектора, подсоединенного i-ым информационным входом к неинвертирующему входу i-го дифференциального компаратора, особенность заключается в том, что вход третьего ключа j-й группы и объединенные выходы третьего, четвертого ключей n-й группы соединены соответственно с входом сброса j-го RS-триггера и вторым настроечным входом рангового селектора.

группы соединены соответственно с входом второго и входом четвертого ключей (k+1)-й группы, объединенные выходы первого, второго ключей n-й группы образуют информационный выход рангового селектора, выход третьего и объединенные выходы первого, второго ключей (n+1)-й группы соединены соответственно с входом четвертого и входом второго ключей первой группы, вход третьего ключа j-й группы соединен через j-й резистор с шиной нулевого потенциала, а вход первого и вход второго ключей i-й группы соединены соответственно с неинвертирующим и инвертирующим входами i-го дифференциального компаратора, подсоединенного выходом к первому входу i-го элемента И, выход и второй вход которого соединены соответственно с управляющим входом четырех ключей i-й группы и неинвертирующим выходом i-го RS-триггера, подсоединенного входом установки к первому настроечному входу рангового селектора и входу установки (n+1)-го RS-триггера, неинвертирующий выход которого соединен с управляющим входом трех ключей (n+1)-й группы, в которой второй ключ имеет вход, а вход первого ключа соединен с (n+1)-ым информационным входом рангового селектора, подсоединенного i-ым информационным входом к неинвертирующему входу i-го дифференциального компаратора, особенность заключается в том, что вход третьего ключа j-й группы и объединенные выходы третьего, четвертого ключей n-й группы соединены соответственно с входом сброса j-го RS-триггера и вторым настроечным входом рангового селектора.

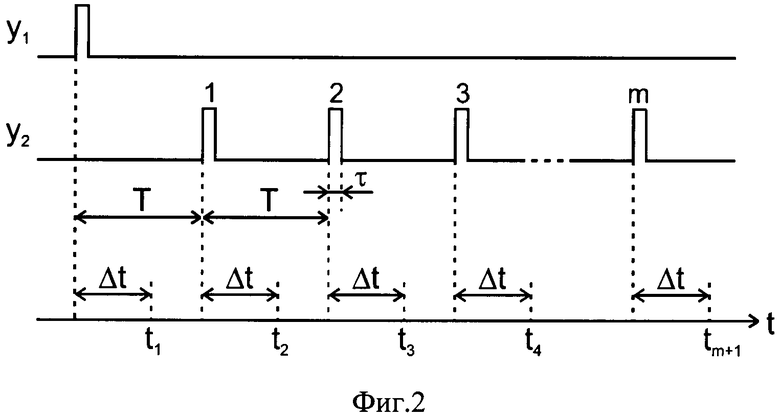

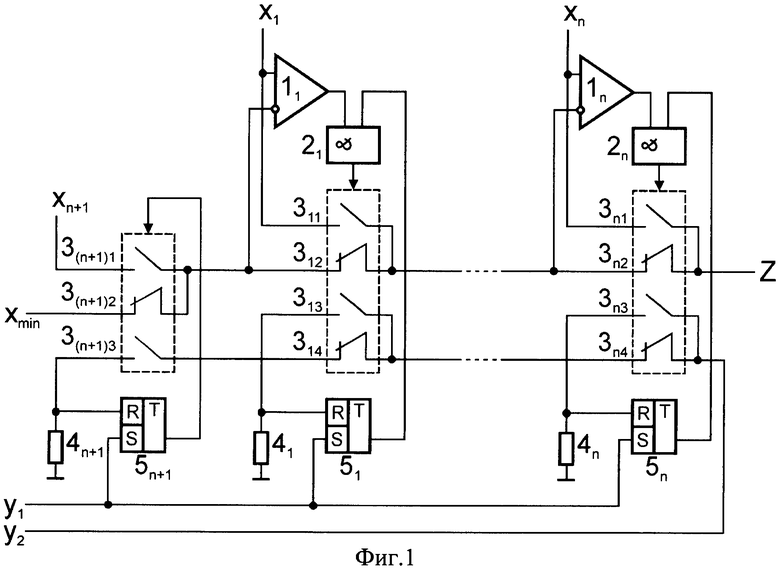

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого рангового селектора и временные диаграммы, поясняющие принцип его работы.

Ранговый селектор содержит n дифференциальных компараторов 11, …, 1n, n элементов И 21, …, 2n, 4n+3 ключей 311, …, 3(n+1)3, n+1 резисторов 41,…, 4n+1 и n+1 RS-триггеров 51,…,5n+1, причем все ключи сгруппированы в n+1 групп так, что j-я  группа содержит ключи 3j1, 3j3 и 3j2, выполненные соответственно замыкающими и размыкающими, а i-я

группа содержит ключи 3j1, 3j3 и 3j2, выполненные соответственно замыкающими и размыкающими, а i-я  группа дополнительно содержит ключ 3i4, выполненный размыкающим, объединенные выходы ключей 3k1, 3k2

группа дополнительно содержит ключ 3i4, выполненный размыкающим, объединенные выходы ключей 3k1, 3k2

и объединенные выходы ключей 3k3, 3k4 соединены соответственно с входами ключей 3(k+1)2 и 3(k+1)4, объединенные выходы ключей 3n1, 3n2 и объединенные выходы ключей 3n3, 3n4 образуют соответственно информационный выход и второй настроечный вход рангового селектора, выход ключа 3(n+1)3 и объединенные выходы ключей 3(n+1)1, 3(n+1)2 соединены соответственно с входом ключа 314 и входом ключа 312, вход ключа 3j3 соединен с входом сброса RS-триггера 5j, подсоединенным через резистор 4j к шине нулевого потенциала, а входы ключей 3i1 и 3i2 соединены соответственно с неинвертирующим и инвертирующим входами компаратора 1i, подсоединенного выходом к первому входу элемента 2i, выход и второй вход которого соединены соответственно с управляющим входом ключей 3i1,…,3i4 и неинвертирующим выходом RS-триггера 5i, подсоединенного входом установки к первому настроечному входу рангового селектора и входу установки RS-триггера 5n+1, неинвертирующий выход которого соединен с управляющим входом ключей 3(n+1)1,3(n+1)2,3(n+1)3, у которых ключ 3(n+1)2 имеет вход, а вход ключа 3(n+1)1 соединен с (n+1)-ым информационным входом рангового селектора, подсоединенного i-ым информационным входом к неинвертирующему входу компаратора 1i.

и объединенные выходы ключей 3k3, 3k4 соединены соответственно с входами ключей 3(k+1)2 и 3(k+1)4, объединенные выходы ключей 3n1, 3n2 и объединенные выходы ключей 3n3, 3n4 образуют соответственно информационный выход и второй настроечный вход рангового селектора, выход ключа 3(n+1)3 и объединенные выходы ключей 3(n+1)1, 3(n+1)2 соединены соответственно с входом ключа 314 и входом ключа 312, вход ключа 3j3 соединен с входом сброса RS-триггера 5j, подсоединенным через резистор 4j к шине нулевого потенциала, а входы ключей 3i1 и 3i2 соединены соответственно с неинвертирующим и инвертирующим входами компаратора 1i, подсоединенного выходом к первому входу элемента 2i, выход и второй вход которого соединены соответственно с управляющим входом ключей 3i1,…,3i4 и неинвертирующим выходом RS-триггера 5i, подсоединенного входом установки к первому настроечному входу рангового селектора и входу установки RS-триггера 5n+1, неинвертирующий выход которого соединен с управляющим входом ключей 3(n+1)1,3(n+1)2,3(n+1)3, у которых ключ 3(n+1)2 имеет вход, а вход ключа 3(n+1)1 соединен с (n+1)-ым информационным входом рангового селектора, подсоединенного i-ым информационным входом к неинвертирующему входу компаратора 1i.

Работа предлагаемого рангового селектора осуществляется следующим образом. На его первый, …, (n+1)-й информационные входы подаются соответственно аналоговые сигналы (напряжения) х1,…,xn+1, а на входе ключа 3(n+1)2 фиксируется опорное напряжение xmin<х1,…,xn+1. На первый, второй настроечные входы предлагаемого рангового селектора подаются соответственно импульсные сигналы у1,у2 ∈ {0,1} (фиг.2), причем период Т и длительность τ импульса сигнала у2 должны удовлетворять условиям T>Δt и τ<τТр+τИ+τКл, где Δt=(τК+τИ+τКл)n+τТр+τИ+τКл, а τИ, τТр, τКл и τК есть длительности задержек, вносимых элементом И, RS-триггером, ключом и дифференциальным компаратором. В j-й  группе замыкающие ключи замкнуты (разомкнуты), размыкающие ключи разомкнуты (замкнуты), когда на управляющем входе этой группы ключей присутствует логическая «1» (логический «0»). Если сигнал на неинвертирующем входе компаратора 1i

группе замыкающие ключи замкнуты (разомкнуты), размыкающие ключи разомкнуты (замкнуты), когда на управляющем входе этой группы ключей присутствует логическая «1» (логический «0»). Если сигнал на неинвертирующем входе компаратора 1i

больше (меньше) сигнала на его инвертирующем входе, то на выходе этого компаратора имеем логическую «1» (логический «0»). Импульс сигнала у1 устанавливает в «1» сигнал на неинвертирующем выходе всех RS-триггеров, при этом с учетом указанного выше принципа работы ключей и дифференциального компаратора на информационном выходе предлагаемого рангового селектора в момент времени t1 (см. фиг.2) имеем сигнал x(n+1) (n+1)-го ранга (наибольший из сигналов множества {x1, …, xn+1}), то есть

больше (меньше) сигнала на его инвертирующем входе, то на выходе этого компаратора имеем логическую «1» (логический «0»). Импульс сигнала у1 устанавливает в «1» сигнал на неинвертирующем выходе всех RS-триггеров, при этом с учетом указанного выше принципа работы ключей и дифференциального компаратора на информационном выходе предлагаемого рангового селектора в момент времени t1 (см. фиг.2) имеем сигнал x(n+1) (n+1)-го ранга (наибольший из сигналов множества {x1, …, xn+1}), то есть

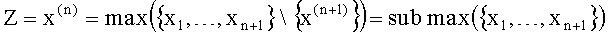

.

.

Первый импульс сигнала у2 сбрасывает в «0» сигнал на неинвертирующем выходе только того RS-триггера, номер j которого совпадает с номером сигнала х(n+1) (например, если х2=х(n+1), то j=2), при этом на информационном выходе предлагаемого рангового селектора в момент времени t2 имеем сигнал х(n) n-го ранга (наибольший из сигналов множества {x1, …, xn+1}\{x(n+1)}, где символом \ обозначена разность множеств), то есть

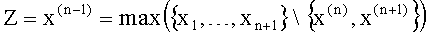

.

.

Второй импульс сигнала у2 сбрасывает в «0» сигнал на неинвертирующем выходе только того очередного RS-триггера, номер которого совпадает с номером сигнала х(n), при этом в момент времени t3 имеем

.

.

Наконец m-й (m∈{1, …, n}) импульс сигнала у2 сбрасывает в «0» сигнал на неинвертирующем выходе только того RS-триггера, номер которого совпадает с номером сигнала x(n+2-m), при этом в момент времени tm+1 имеем

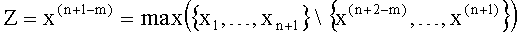

.

.

Таким образом, настройка предлагаемого рангового селектора на выполнение селекции сигнала x(r) ∈ {x1, …, xn+1} любого заданного ранга r ∈ {1, …, n+1} осуществляется с помощью импульса сигнала у1 и n+1-r импульсов сигнала у2.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый ранговый селектор обеспечивает выполнение селекции из n+1 аналоговых сигналов сигнала любого заданного ранга r ∈ {1, …, n+1} и обладает меньшими по сравнению с прототипом аппаратурными затратами, поскольку содержит на n+1 элементов И меньше, чем в аппаратурном составе прототипа.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАНГОВЫЙ СЕЛЕКТОР | 2007 |

|

RU2338250C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2003 |

|

RU2240597C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2003 |

|

RU2248042C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2000 |

|

RU2172980C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2002 |

|

RU2227932C1 |

| РАНГОВЫЙ ФИЛЬТР | 2006 |

|

RU2300143C1 |

| РАНГОВЫЙ СЕЛЕКТОР | 2004 |

|

RU2262740C1 |

| ИМПУЛЬСНЫЙ СЕЛЕКТОР | 2011 |

|

RU2469471C1 |

| ПРОЦЕССОР ДЛЯ АДРЕСНО-РАНГОВОЙ ИДЕНТИФИКАЦИИ И СЕЛЕКЦИИ АНАЛОГОВЫХ СИГНАЛОВ | 1994 |

|

RU2093888C1 |

| РАНГОВЫЙ ФИЛЬТР | 2002 |

|

RU2205449C1 |

Изобретение относится к автоматике и аналоговой вычислительной технике. Техническим результатом является уменьшение аппаратурных затрат при сохранении функциональных возможностей. Ранговый селектор содержит n дифференциальных компараторов (l1, …, ln), n элементов И (21, …, 2n), 4n+3 ключей (311, …, 3(n+1)3), n+1 резисторов (41,

…, 4n+1) и n+1 RS-триггеров (51, …, 5n+1). 2 ил.

Ранговый селектор, содержащий n дифференциальных компараторов, n элементов И, n+1 резисторов, n+1 RS-триггеров и 4n+3 ключей, которые сгруппированы в n+1 групп так, что j-я  группа содержит первый, третий и второй ключи, выполненные соответственно замыкающими и размыкающим, а i-я

группа содержит первый, третий и второй ключи, выполненные соответственно замыкающими и размыкающим, а i-я  группа дополнительно содержит четвертый ключ, выполненный размыкающим, причем объединенные выходы первого, второго и объединенные выходы третьего, четвертого ключей k-й

группа дополнительно содержит четвертый ключ, выполненный размыкающим, причем объединенные выходы первого, второго и объединенные выходы третьего, четвертого ключей k-й  группы соединены соответственно с входом второго и входом четвертого ключей (k+1)-й группы, объединенные выходы первого, второго ключей n-й группы образуют информационный выход рангового селектора, выход третьего и объединенные выходы первого, второго ключей (n+1)-й группы соединены соответственно с входом четвертого и входом второго ключей первой группы, вход третьего ключа j-й группы соединен через j-й резистор с шиной нулевого потенциала, а вход первого и вход второго ключей i-й группы соединены соответственно с неинвертирующим и инвертирующим входами i-го дифференциального компаратора, подсоединенного выходом к первому входу i-го элемента И, выход и второй вход которого соединены соответственно с управляющим входом четырех ключей i-й группы и неинвертирующим выходом i-го RS-триггера, подсоединенного входом установки к первому настроечному входу рангового селектора и входу установки (n+1)-го RS-триггера, неинвертирующий выход которого соединен с управляющим входом трех ключей (n+1)-й группы, в которой второй ключ имеет вход, а вход первого ключа соединен с (n+1)-м информационным входом рангового селектора, подсоединенного i-м информационным входом к неинвертирующему входу i-го дифференциального компаратора, отличающийся тем, что вход третьего ключа j-й группы и объединенные выходы третьего, четвертого ключей n-й группы соединены соответственно с входом сброса j-го RS-триггера и вторым настроечным входом рангового селектора.

группы соединены соответственно с входом второго и входом четвертого ключей (k+1)-й группы, объединенные выходы первого, второго ключей n-й группы образуют информационный выход рангового селектора, выход третьего и объединенные выходы первого, второго ключей (n+1)-й группы соединены соответственно с входом четвертого и входом второго ключей первой группы, вход третьего ключа j-й группы соединен через j-й резистор с шиной нулевого потенциала, а вход первого и вход второго ключей i-й группы соединены соответственно с неинвертирующим и инвертирующим входами i-го дифференциального компаратора, подсоединенного выходом к первому входу i-го элемента И, выход и второй вход которого соединены соответственно с управляющим входом четырех ключей i-й группы и неинвертирующим выходом i-го RS-триггера, подсоединенного входом установки к первому настроечному входу рангового селектора и входу установки (n+1)-го RS-триггера, неинвертирующий выход которого соединен с управляющим входом трех ключей (n+1)-й группы, в которой второй ключ имеет вход, а вход первого ключа соединен с (n+1)-м информационным входом рангового селектора, подсоединенного i-м информационным входом к неинвертирующему входу i-го дифференциального компаратора, отличающийся тем, что вход третьего ключа j-й группы и объединенные выходы третьего, четвертого ключей n-й группы соединены соответственно с входом сброса j-го RS-триггера и вторым настроечным входом рангового селектора.

| РАНГОВЫЙ СЕЛЕКТОР | 2007 |

|

RU2338250C1 |

| ИМПУЛЬСНЫЙ СЕЛЕКТОР | 2002 |

|

RU2219579C1 |

| US 6335641 В1, 01.01.2002. | |||

Авторы

Даты

2013-05-27—Публикация

2012-02-08—Подача