Изобретение относится к вычислительной технике и предназначено для построения быстродействующих многооперандных параллельно-конвейерных сумматоров, для обработки массивов целых положительных чисел.

Известен итерационный способ суммирования массива целых положительных чисел, при котором первое m-разрядное слагаемое суммируется со вторым m-разрядным слагаемым, затем полученная сумма суммируется с третьим m-разрядным слагаемым и так далее, пока не будет получена (m-поразрядная искомая сумма. Недостаток состоит в том, что, во-первых, при итерационном способе суммирования чисел выполняется n-1 операций суммирования, а с учетом последовательного способа последовательного способа переносов в старшие разряды - количество тактов суммирования равно (m-1)·n. Во-вторых, процесс формирования суммы является последовательным процессом.

Техническим результатом от использования способа организации вычислений суммы n m-разрядных чисел является повышение скорости вычисления за счет замены серии из n арифметических операций сложения m параллельно исполняемыми операциями подсчета количества единичных бит в разрядных срезах, формируемых из разрядов суммируемых чисел. На основании анализа и модификации полученных значений сумм количества единиц во всех разрядных срезах выполняется формирование значения двоичного числа, являющегося значением искомой суммы. В результате количество тактов необходимых для формирования значения суммы массива целых двоичных чисел будет равно (log2n)·m тактов. Таким образом, предлагаемый способ обеспечивает выполнение операции формирования суммы массива n m-разрядных чисел быстрее известного итерационного способа в ((m-1)·n)/((log2n)·m) раз, например, при m=100, n=64 вычисления будут выполняться в 8 раз быстрее.

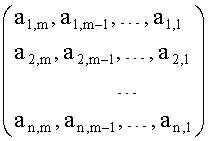

Описание работы устройства: каждое i-oe двоичное позиционное слагаемое можно представить в виде последовательности бит Ai(am, am-1, …, a2, a1), где m-разрядность числа, i∈[1, n]. Тогда n слагаемых можно представить в виде матрицы:

Способ организации конвейерных вычислений суммы n m-разрядных чисел заключается в параллельном подсчете количества единиц в m двоичных векторах, являющихся столбцами приведенной выше матрицы. В результате формируется m двоичных чисел bi - значений количества единиц в соответствующих n-разрядных векторах, где i∈[1, m].

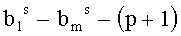

Младший разряд числа b1 является первым разрядом s1 искомой суммы, затем выполняется сдвиг первого двоичного числа b1 на один разряд вправо, после чего полученный результат суммируется с числом b2, младший разряд полученной суммы

Затем выполняется сдвиг двоичного числа

Затем выполняется сдвиг двоичного числа

Затем выполняется сдвиг двоичного числа

Затем выполняется сдвиг двоичного числа

если

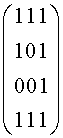

Пример: необходимо сложить четыре (m=4) трехбитных (n=3) операнда: a1=111, а2=101, а3=001, а4=111. Запишем их в виде матрицы с элементами ai,j

Параллельно подсчитывается число единиц в столбцах матрицы: b1=100, b2=010, b3=011. Так как младший бит b1 равен нулю, то бит результата s1=0.

Число b1 сдвигается на один разряд вправо и результат сдвига

Число

Число

Если принять за время суммирования пары n-разрядных чисел n тактов работы устройства, то время вычисления суммы в устройстве на базе описанного способа равно p-m тактов, где p=log2n, в то время как время суммирования итерационным способом равно m·n тактов. Таким образом, быстродействие устройства на базе описанного способа в n/(log2n) раз выше по сравнению с быстродействием устройства на базе известного итерационного способа суммирования.

Примером построения устройства на базе способа организации вычислений суммы n m-разрядных чисел может служить ее программирование на программируемых логических интегральных схемах (ПЛИС).

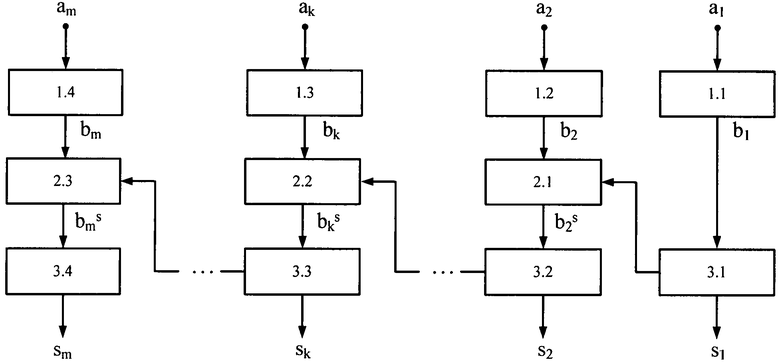

На фигуре представлен вариант структурной схемы устройства, реализующего способ организации вычислений суммы n m-разрядных чисел в общем виде, где 1 - счетчик единичный бит в двоичных векторах, 2 - p-разрядный двухплечевой сумматор, где p=log2n, 3 - сдвиговый p-разрядный регистр, a1-an - m-разрядные информационные входы схемы, s1-Sm - одноразрядные информационные выходы схемы, b1-bm - р-разрядные выходы счетчиков 1,

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих многооперандных параллельно-конвейерных сумматоров, для обработки массивов целых положительных чисел. Техническим результатом является повышение скорости вычисления. Способ содержит этапы, на которых параллельно подсчитывают количество единиц bi (i=1, m) в m n-разрядных двоичных векторах, сдвигают двоичное число b1 на один разряд вправо, суммируют с числом b2, полученную сумму

Способ суммирования n m-разрядных целых положительных двоичных чисел в позиционной системе счисления в суммирующем устройстве, заключающийся в том, что в суммирующем устройстве параллельно выполняется подсчет количества единиц в m n-разрядных двоичных векторах, составленных из первых разрядов n чисел, вторых разрядов n чисел, …, k-х разрядов n чисел, …, m-х разрядов n чисел; в результате параллельного подсчета количества единиц в m двоичных векторах формируется m двоичных чисел - значений количества единиц в соответствующих n-разрядных векторах, причем первое двоичное число b1 - значение количества единиц в первом n-разрядном векторе, второе двоичное число b2 - значение количества единиц во втором n-разрядном векторе, …, k-e двоичное число bk - значение количества единиц в k-м n-разрядном векторе, …, m-е двоичное число bm - значение количества единиц в m-м n-разрядном векторе; младший разряд числа b1 является первым разрядом s1 суммы n m-разрядных исходных чисел; затем выполняется сдвиг двоичного числа b1 на один разряд вправо, после чего полученный результат суммируется с числом b2, где младший разряд полученной суммы

| МНОГОУРОВНЕВАЯ M-МЕРНАЯ МАТРИЧНАЯ СУММИРУЮЩАЯ СТРУКТУРА ВЕРТИКАЛЬНОЙ АРИФМЕТИКИ В.М. ТАРАНУХИ | 2003 |

|

RU2246128C2 |

| ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2004 |

|

RU2284568C2 |

| Ассоциативное суммирующее устройство | 1986 |

|

SU1424011A1 |

| US 2004223580 A1, 11.11.2004 | |||

| US 5339447 A, 16.08.1994. | |||

Авторы

Даты

2013-08-27—Публикация

2011-12-05—Подача