ю

4

Изобретение относится к вычислительной технике и может быть исполь- зопаио 13 вычислительных устройствах для одновременного суммирования мно- птх чисел, представленных как в двоичной, так и в двоично-десятичной системе счисления.

Целью изобретения является повы- I lcinie быстродействия и упрощение кон- CTpyicumi устройства о

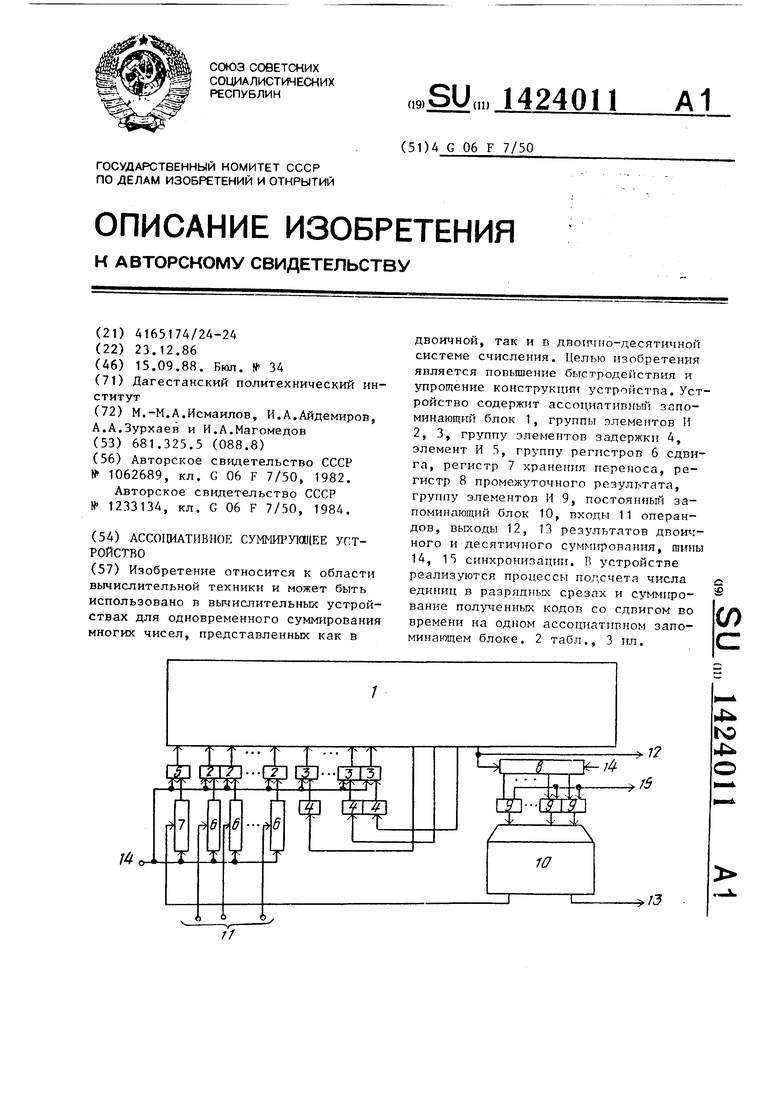

На чертеже представлена функциональная схема устройства.

Устройство содержит ассоциативный запоминающий блок 1, группы элементов И 2,3, группу элементов Д задержки, элемсмгг И 5, группу регистров 6 сдвига, регистр 7 хранения переноса, ре- гтютр 8 1тромсжуточного результата, группу элементов И 9, постоянньй за- )ш, блок 10, входы 11 операндом, ныход 12 результата двоичного суг широтияния, иыход 13 результата де- с. П и-.ного суммирования, шины l i,15 синхронизации.

У .гтройство работает следующим обpf IOI-1,

и. : v,o;tM 11 II засист-юсти от того я кпхом в,т,е подаются слагаемые (в дв(нмном или дпотгчио-дссятичиом), по- гтуп.яют и натесываются в регистры 6 г:л,чг,1емые полностью (в первом случае) или очередгтме тетрады всех слагаемых

(,Т)0

зтором ) ,

Р. ссмотрим работу устройства, когда счагаемче представлены в двоичной системе счисления (табл.1),

И ли гюд.аче тактового импульса на lUHijy 14 на перзые входы элементов И 2 подаются одноименные разряды слагаемых, Сформиронаиное слово является частью ассоциатипного признака, пода- ваомого па входы блока 1. Остальной частузго ассодиатчвного пригишка ется слово, считываемое из блока 1, которое Зс ик-ржипается на один такт при попову элементов 4 задеретси, В псрпом такте работы слово, считываемое 113 блока 1, равно 00...О (2). На пьглодп получается результат суммирования п последовательном коде, причем количество тактов, за которое вычи1гляется сумма, равно

Т п + logjN,

где Т - количество затрачиваемых

тактов, за которые вычисляется сумма;

0

5

0

5

0

5

0

5

0

5

П4 - разрядность двoIiчныx чисел, N - количество одновременно суммируемых чисел.

В двоично-десятичной системе счисления в коде 8-4-2-1 устройство работает следующим образом (табл.2).

Через входы 11 в регистры 6 поступают мпадшие тетрады всех слагаемых. Используя блоки, предназначенные для операции двоичного суммирования, а также шину 14, производим операцию двоичного сложения. Заметим при этом, что в регистре 7 содержатся нули. После обработки младших тетрад в регистре 8 (в исходном состоянии он содержит нули) формируется первичная двоичная сумма ) ,

При подаче первого тактового импульса на шину 15 происходит передача информации с регистра 8 через элементы И 9 на вход адреса постоянного запоминающего блока 10.

На вход блока 10 поступает информация с регистра В с учетом переноса из предыдущих тетрад (при сложении младших тетрад таких переносов нет), С выхода блока 10 по соответству ош,е- му адресу считывается слово, которое содержит два вида информации, а именно вьщеляет цифру результата в дво1-ш- но-десятичном коде и код переноса.

Полученная информация в двo rчнo- десятичном коде поступает на выход 13 и входы регистра 7 (количество переносов, которые необходимо учесть при суммкровакии вторых тетрад всех слагаемых), Регистр 7 является регистром сдвига. Обработка последующих тетрад всех слагаемых происходит аналогично.

Формула изобретения

Ассоциативное суммирующее устройство, содержащее ассоциативный запоминающий блок, три группы элементов И, элемент И, группу элементов задержки, регистр хранения переПоса, группу регистров сдвига, регистр проме- нсуточного результата и постоянный запоминающий блок, причем вход младшего разряда регистра промежуточного результата соединен с выходом результата ассоциативного запоминающего блока и с выходом результата двоичного суммирования устройства, выходы разрядов регистра промежуточного результата соединены с первыми входами

элементов И первой группы, выходы ко- торьж подключены к адресным входам постоянного запоминающего блока, первый выход которого соединен с выходом результата десятичного суммирования устройства, остальные выходы постоянного запоминающего блока соединены с входами разрядов регистра хранения переноса, выход которого подключен к первому входу элемента И, второй вход которого соединен с первой шиной синхронизации устройства и тактовыми входами регистров сдвига группы и регистра хранения переноса, входы раз- рядов каждого регистра сдвига группы соединены с входами разрядов соответствующего операнда устройства, выходы регистров сдвига группы соединены с первыми входами элементов И второй группы, вторые входы которых подключены к первой шине синхронизации устройства, вькоды ассоциативного запоминающего блока соединены через соответствующие элементы задержки группы с первыми входами элементов И третьей группы, выходы которых подключены к первым входам признака ассоциативного запоминающего блока, вторые входы элементов И первой группы соединены с второй шиной синхронизации устройства, отличающееся тем, что, с целью повьппения быстродействия и упрощения конструкции, выходы элементов И второй группы соединены с вторыми входами признака ассоциативного запоминающего блока, выход элемента И подключен к третьему входу признака ассоциативного запоминающего рлока, тактовый вход регистра проме- жуто ного результата соединен с первой шиной синхронизации устройства ,

Таблица 1

Таблица2

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Устройство для суммирования @ -разрядных чисел | 1985 |

|

SU1273917A1 |

| Суммирующее устройство | 1991 |

|

SU1807479A1 |

| Вычислительное устройство | 1990 |

|

SU1784969A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Суммирующее устройство | 1991 |

|

SU1803912A1 |

| Суммирующее устройство | 1990 |

|

SU1784970A1 |

| Генератор циклов | 1981 |

|

SU995289A1 |

| Суммирующее устройство | 1990 |

|

SU1775722A1 |

Изобретение относится к области вычислительной техники и может быть использовано в вычислительньк устройствах для одновременного суммирования многих чисел, представленных как в двоичной, так и в двотпю-десятичной системе счисления. Целью изобретения является повышение быстродействия и упрощение конструкцшт устройства. Устройство содержит ассоциативный запоминающий блок 1, группы элементов И 2, 3, группу элементов задержки 4, элемент И 5, группу регистров 6 сдвига, регистр 7 хранения пефеноса, регистр 8 промежуточного результата, группу элементов И 9, постояпньш запоминающий блок 10, входы 11 операндов, выходы 12, 13 результатов двоичного и десятичного сумм1фования, шины 14, 15 синхронизации. В устройстве реализуются процессы подсчета числа единиц в разрядных срезах и сумм1фо- вание полученных кодов со сдвигом во времени на одном ассоциативном запоминающем блоке. 2 табл., 3 ил. с (/)

С вых. На На вход эл-в вход РГ проме- ИЗ эл-в жуточного 4 результата 8

| Суммирующее устройство | 1982 |

|

SU1062689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Ассоциативное суммирующее устройство @ -разрядных двоичных и двоично-десятичных чисел | 1984 |

|

SU1233134A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-15—Публикация

1986-12-23—Подача