Изобретение относится к области цифровой обработки сигналов, к структурам вычислительных блоков микропроцессоров, а конкретно к параметризуемым однотактным умножителям двоичных чисел с фиксированной точкой в прямом и дополнительном коде, и может быть использовано для вычисления произведения чисел с фиксированной точкой в прямом и дополнительном коде.

Для решения задач цифровой обработки сигналов одной из ключевых операций является операция умножения. Наряду со сложением, это основная операция, необходимая для вычисления преобразований Фурье, фильтров и произведений матриц, что, в свою очередь, является основой решения задач коммуникации, обработки изображений и видео, а также свёрточных нейронных сетей. Таким образом, производительность операций умножения является основой быстрого решения важнейших задач цифровой обработки сигналов. Это относится к умножению как чисел с плавающей точкой, так и с фиксированной. При этом быстрое и эффективное умножение чисел с фиксированной точкой наиболее важно, поскольку в основе умножения чисел с плавающей точкой лежит умножение их мантисс, которые являются числами с фиксированной точкой в прямом коде.

Традиционный подход к разработке однотактных умножителей чисел с фиксированной точкой подразумевает использование массива одноразрядных умножителей, вычисляющих частичные произведения множителей, а также массива одноразрядных полных сумматоров и полусумматоров, расположенных каскадами и вычисляющих суммы частичных произведений. При этом традиционная схема рассчитана на умножение чисел в прямом коде. В случае, если один или оба множителя представлены в дополнительном коде, требуется коррекции множителей и/или результата, замедляющие выполнение операции умножения.

Известен умножитель, описанный в патенте RU2422881 (C1), который основан на массиве одноразрядных полных сумматоров и полусумматоров. Данная структура обладает низкой задержкой переноса, кроме того в ней существует возможность параметризации для множителей различной разрядности.

Недостатком данного умножителя является не достаточная универсальность, вследствие наличия возможности умножения только чисел в прямом коде.

В патентах US5313414 (A) и US5351206 (A) приведены структуры умножителей, основанные на массиве одноразрядных полных сумматоров и полусумматоров. Данные структуры обладают низкой задержкой переноса. В них существует возможность параметризации для множителей различной разрядности.

Недостатком данных умножителей является не достаточная универсальность, вследствие наличия возможности умножения только чисел в дополнительном коде и то, что один из множителей является константой.

Наиболее близким к заявленному изобретению является умножитель, описанный в патенте US5153850 (A), который позволяет умножать как числа в прямом коде, так и в дополнительном. Данный умножитель выбран в качестве прототипа заявленного изобретения.

Недостатками умножителя прототипа являются большие размеры по площади и низкое быстродействие, вследствие отсутствия параметризации и наличия дополнительных сумматоров для преобразования произведения.

Техническим результатом изобретения является создание параметризуемого однотактного умножителя двоичных чисел с фиксированной точкой в прямом и дополнительном коде, который обладает: повышенной универсальностью за счет того, что любой из множителей может быть представлен как в прямом, так и в дополнительном коде; улучшенной параметризуемостью, за счет возможности имплементации для множителей с любым количеством разрядов; меньшими размерами по площади и увеличенным быстродействием, за счет отсутствия дополнительных сумматоров для преобразования произведения и более простой топологии; повышенной универсальностью, вследствие возможности вывода результата в двухрядном коде, что позволяет использовать частичные произведения для дальнейших вычислений без задержки переноса на сумматоре приведения.

Поставленный технический результат достигнут путем создания параметризуемого однотактного умножителя двоичных чисел с фиксированной точкой в прямом и дополнительном коде, содержащего соединенные между собой:

- массив одноразрядных умножителей [1], выполненных с возможностью формирования частичных одноразрядных произведений входных множителей;

- логические блоки XOR [2], выполненные с возможностью модифицирования множителей с учётом их типа, а также с возможностью приема входных сигналов (tcA) и (tcB)

- массив одноразрядных полных сумматоров [3] и полусумматоров [4], расположенных каскадами со сдвигом и соединённых с возможностью сформирования конечного произведения, представленного двухрядным кодом в виде двух частичных произведений.

В предпочтительном варианте осуществления умножителя входными данными умножителя являются:

- первый множитель (a), представленный битовым вектором an–1,an–2,...,a1,a0, где n – размер вектора (n ≥ 1), an–1 – старший (знаковый) бит;

- второй множитель (b), представленный битовым вектором bm–1,bm–2,...,b1,b0, где m – размер вектора (m ≥ 1), bm–1 – старший (знаковый) бит;

- сигнал (tcA), выполненный с возможностью определения типа первого множителя (a): 0 – прямой код, 1 – дополнительный код;

- сигнал (tcB), выполненный с возможностью определения типа второго множителя (b): 0 – прямой код, 1 – дополнительный код;

выходными данными умножителя являются:

- первое частичное произведение (s) (сумма частичных произведений множителей), представленное битовым вектором sn+m–1,sn+m–2,...,s1,s0, где (n+m) – размер вектора, sn+m–1 – старший (знаковый) бит;

- второе частичное произведение (p) (вектор переносов), представленное битовым вектором pn+m–1,pn+m–2,...,p1,p0, где (n+m) – размер вектора, pn+m–1 – старший (знаковый) бит.

В предпочтительном варианте осуществления умножителя при n ≥ 4, m ≥ 4

- для любого из блоков одноразрядного умножителя [1], логического блока XOR [2], одноразрядного полного сумматора [3] и полусумматора [4] порядок входов не влияет на выходной результат, то есть входы этих блоков можно менять местами;

- сигнал (nA) на выходе логического блока XOR [2], входы которого соединены со входами умножителя (an–1) и (tcA);

- сигнал (nB) на выходе логического блока XOR [2], входы которого соединены со входами умножителя (bm–1) и (tcB);

- массив одноразрядных полных сумматоров [3] и полусумматоров [4] содержит (m–2) каскадов, которые пронумерованы при помощи индекса (i), где (i = 0,1,...,m–3;

- каскад одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 0) содержит (n) одноразрядных полных сумматоров [3] и полусумматоров [4], которые пронумерованы при помощи индекса (j), где (j = 0,1,...,n–1);

- каждый каскад одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 1, ..., m–3) содержит (n–1) одноразрядных полных сумматоров [3] и полусумматоров [4], которые пронумерованы при помощи индекса (j), где (j = 1,...,n–1);

- элементы каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 0) являются (n–1) одноразрядных полных сумматоров [3] с индексами (j = 1,...,n–1) и один одноразрядный полусумматор [4] с индексом (j = 0);

- элементами каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 1,...,m–4), при условии (m > 4), являются (n–2) одноразрядных полных сумматоров [3] с индексами (j = 2,...,n–1) и один одноразрядный полусумматор [4] с индексом (j = 1);

- элементами каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = m–3) являются (n–1) одноразрядных полных сумматоров [3] с индексами (j = 1,...,n–1);

- выход умножителя (p0) соединён с логическим нулём;

- выход умножителя (s0) соединён с выходом одноразрядного умножителя [1], входы которого соединены со входами умножителя (a0) и (b0);

- выход умножителя (p1) соединён с логическим нулём;

- выходы умножителя (s1) и (p2) соединены с выходами (s) и (co) соответственно одноразрядного полусумматора [4] с индексами (i = 0, j = 0), входы (a) и (b) которого соединены с выходами одноразрядных умножителей [1], входы первого из которых соединены со входами умножителя (a1) и (b0), а входы второго со входами умножителя (a0) и (b1);

- выходы умножителя (s2) и (p3) соединены с выходами (s) и (co) соответственно одноразрядного полного сумматора [3] с индексами (i = 0; j = 1), входы (a), (b) и (co) которого соединены с выходами одноразрядных умножителей [1], входы первого из которых соединены со входами умножителя (a2) и (b0), входы второго со входами умножителя (a1) и (b1), а входы третьего со входами умножителя (a0) и (b2);

- выходы умножителя (sk) и (pk+1), где (k = 3,...,m–2), при условии (m > 4), соединены с выходами (s) и (co) соответственно одноразрядных полусумматоров [4] с индексами (i = k–2; j = 1) соответственно;

- выходы умножителя (sk) и (pk+1), где (k = m–1,...,m+n–3), соединены с выходами (s) и (co) соответственно одноразрядных полных сумматоров [3] с индексами (i = m–3; j = k–m+2) соответственно;

- выход умножителя (sm+n–2) соединён с выходом логического блока XOR [2], вход (a) которого соединён с выходом одноразрядного умножителя [1], входы которого соединены со входами умножителя (an–1) и (bm–1), и вход (b) которого соединён с выходом логического блока XOR [2], входы которого соединены с сигналами (nA) и (nB);

- выход умножителя (pm+n–1) соединён с выходом логического блока XOR [2], входы которого соединены с сигналами (nA) и (nB);

- выход умножителя (sm+n–1) соединён с выходом одноразрядного умножителя [1], входы которого соединены с сигналами (nA) и (nB);

- входы (a) одноразрядных полных сумматоров [3] с индексами (i = 0,...,m–3; j = n–1), соединены с выходами логических блоков XOR [2], входы (a) которых соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj) и (bi+1) соответственно, и входы (b) которых соединены с сигналами (nA);

- входы (a) одноразрядных полных сумматоров [3] с индексами (i = 1,...,m–3; j = 2,...,n–2) соединены с выходами (s) одноразрядных полных сумматоров [3] с индексами (i–1; j+1) соответственно;

- вход (a) одноразрядного полного сумматора [3] с индексами (i = m–3; j = 1) соединён с выходом (s) одноразрядного полного сумматора [3] с индексами (i–1; j+1);

- входы (a) одноразрядных полусумматоров [4] с индексами (i = 1,...,m–4; j = 1), при условии (m > 4), соединены с выходами (s) одноразрядных полных сумматоров [3] с индексами (i–1; j+1).

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

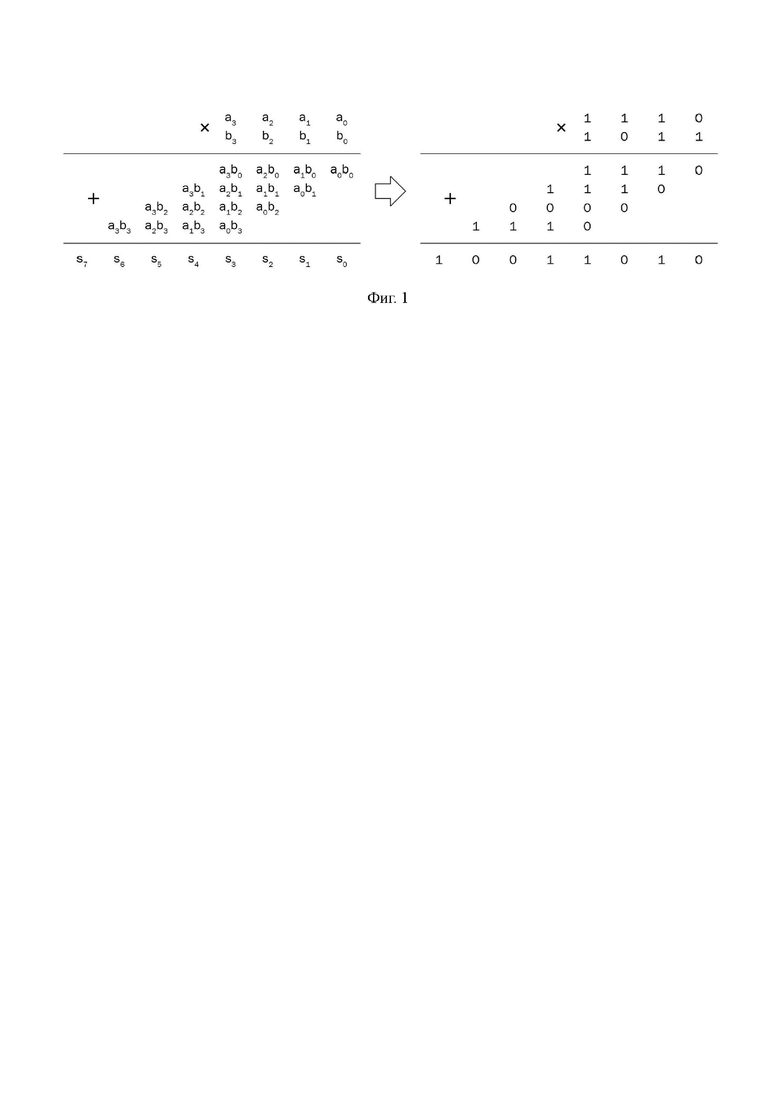

Фиг. 1. Схема работы умножения двоичных чисел в прямом коде, известного из уровня техники.

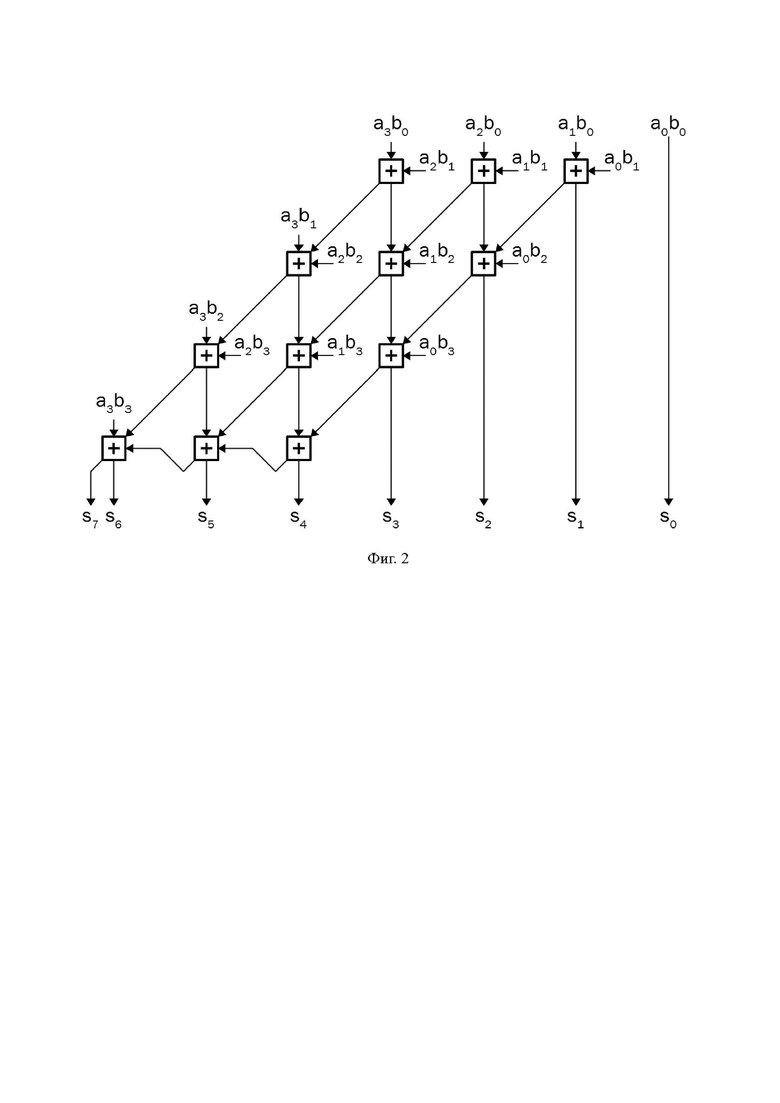

Фиг. 2. Схема матричного умножителя для множителей размером 4 разряда, известного из уровня техники.

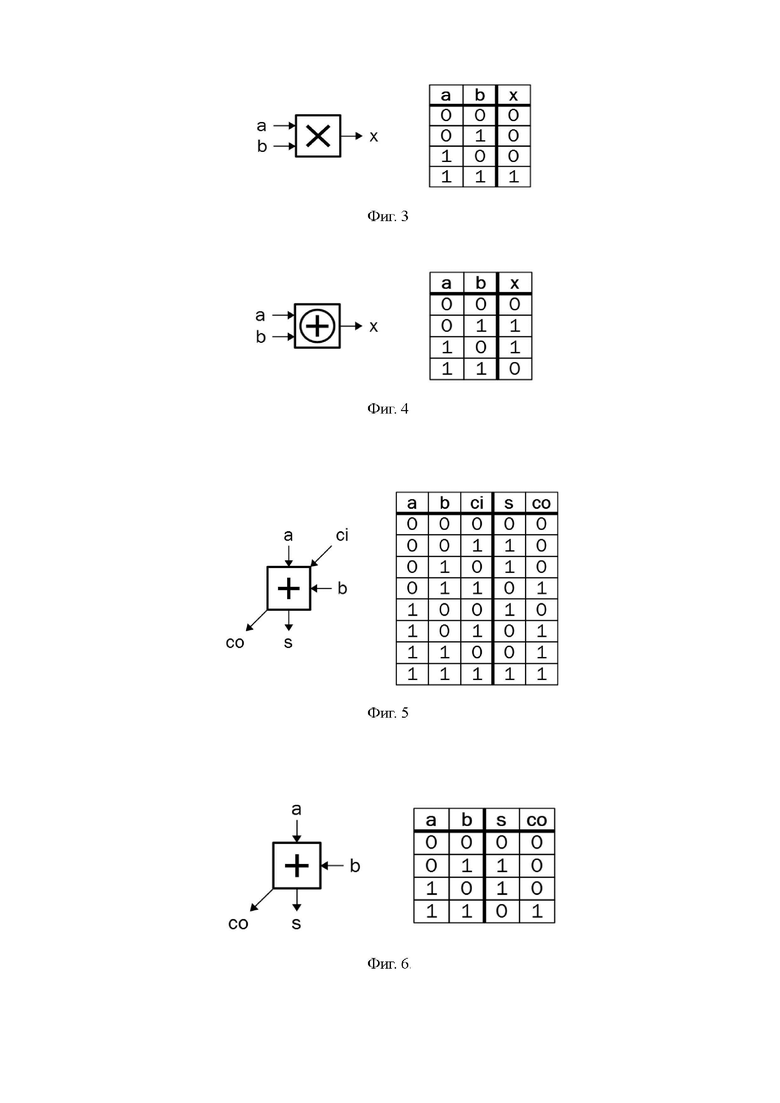

Фиг. 3. Обозначение и таблица истинности одноразрядного умножителя, известного из уровня техники.

Фиг. 4. Обозначение и таблица истинности логического блока XOR, известного из уровня техники.

Фиг. 5. Обозначение и таблица истинности одноразрядного полного сумматора, известного из уровня техники.

Фиг. 6. Обозначение и таблица истинности одноразрядного полусумматора, известного из уровня техники.

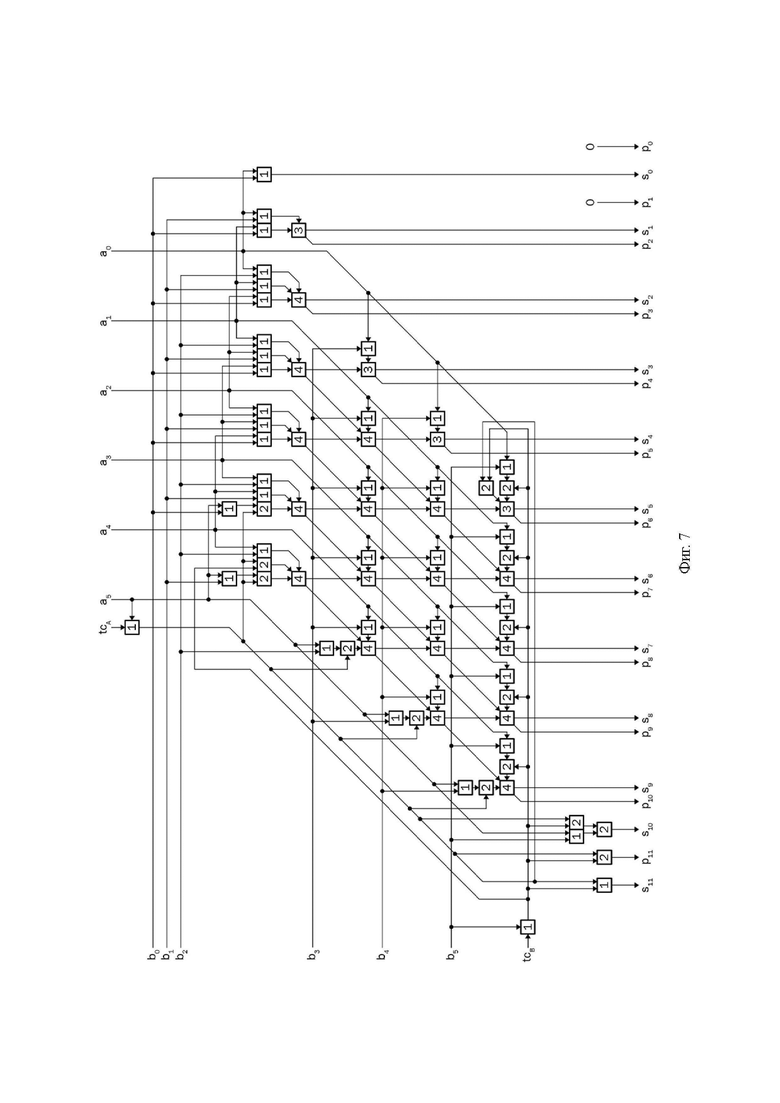

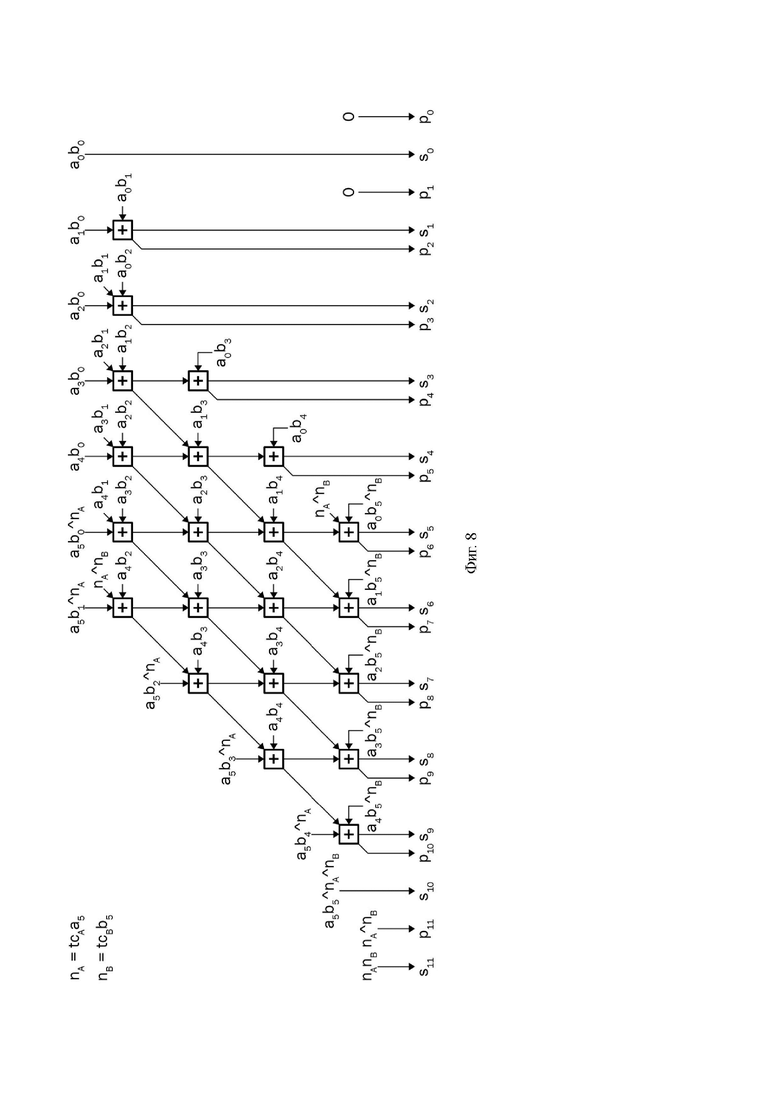

Фиг. 7. Схема параметризуемого однотактного умножителя двоичных чисел с фиксированной точкой в прямом и дополнительном коде для множителей размером 6 разрядов, выполненного согласно изобретению.

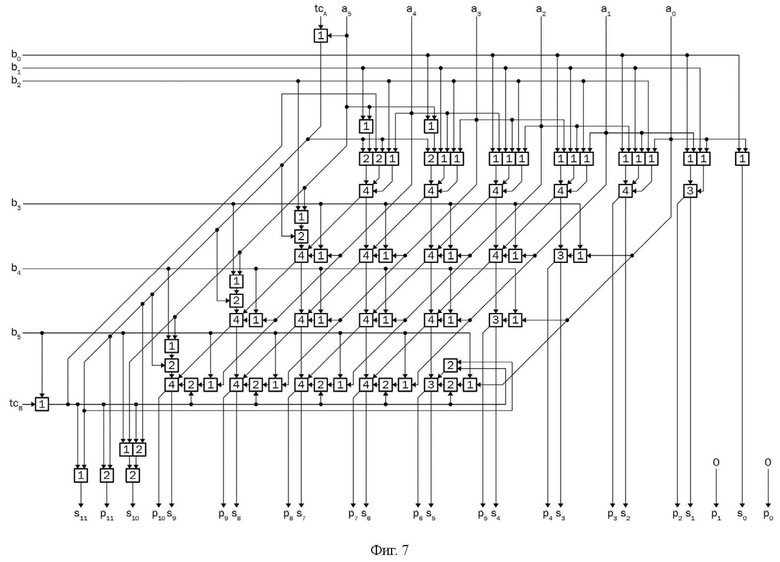

Фиг. 8. Упрощённая схема параметризуемого однотактного умножителя двоичных чисел с фиксированной точкой в прямом и дополнительном коде для множителей размером 6 разрядов, выполненного согласно изобретению, в которой графические обозначения одноразрядных умножителей и блоков XOR заменены логическими выражениями.

Рассмотрим более подробно функционирование заявленного параметризуемого однотактного умножителя двоичных чисел с фиксированной точкой в прямом и дополнительном коде (Фиг. 7 - 8).

Умножение многоразрядных двоичных чисел осуществляют аналогично умножению десятичных чисел: частичные произведения, полученные при поразрядном умножении цифр, составляющих каждое число, складывают с учётом веса и формируют итоговое произведение. На Фиг. 1 приведён пример умножения четырёхразрядных двоичных чисел в прямом коде.

В основе заявленного изобретения лежит традиционная структура двоичного матричного умножителя. Пример такой структуры для двух четырёхразрядных множителей в прямом коде приведён на Фиг. 2. Данная структура состоит из массива одноразрядных умножителей, формирующих частичные произведения, и массива одноразрядных полных сумматоров и полусумматоров, соединённых таким образом, чтобы выполнять последовательное сложение частичных произведений для формирования итогового произведения. Достоинствами данной структуры являются масштабируемость, то есть такую структуру легко составить для множителей любого размера и легко параметризовать, и простота разводки при разработке топологии ИС, что положительно сказывается на площади и быстродействии устройства. Недостатком данной структуры является то, что она не позволяет выполнить умножение чисел в дополнительном коде. Заявленное изобретение решает эту проблему с помощью введения коррекции частичных произведений, в которых участвуют старшие (знаковые) разряды множителей. Коррекцию осуществляют на основании флагов, указывающих на тип множителей (прямой или дополнительный код). При этом дополнительная задержка выполнения умножения отсутствует.

Аппаратной реализацией заявленного изобретения является IP-блок параметризуемого однотактного умножителя двоичных чисел с фиксированной точкой в прямом и дополнительном коде. Схема заявленного умножителя (вариант для множителей размером 6 разрядов) приведена на Фиг. 7.

В состав заявленного умножителя входят:

- одноразрядные умножители [1], формирующие частичные одноразрядные произведения входных множителей;

- логические блоки XOR [2], модифицирующие множители с учётом их типа, который определяется входными сигналами (tcA) и (tcB);

- массив одноразрядных полных сумматоров [3] и полусумматоров [4], расположенных каскадами со сдвигом и соединённых таким образом, чтобы сформировать конечное произведение, представленное двухрядным кодом (двумя частичными произведениями).

Входными данными умножителя являются:

- первый множитель (a), представленный битовым вектором an–1,an–2,...,a1,a0, где n – размер вектора (n ≥ 1), an–1 – старший (знаковый) бит;

- второй множитель (b), представленный битовым вектором bm–1,bm–2,...,b1,b0, где m – размер вектора (m ≥ 1), bm–1 – старший (знаковый) бит;

- сигнал (tcA), определяющий тип первого множителя (a) (0 – прямой код, 1 – дополнительный код).

- сигнал (tcB), определяющий тип второго множителя (b) (0 – прямой код, 1 – дополнительный код).

Выходными данными умножителя являются:

- первое частичное произведение (s) (сумма частичных произведений множителей), представленное битовым вектором sn+m–1,sn+m–2,...,s1,s0, где (n+m) – размер вектора, sn+m–1 – старший (знаковый) бит;

- второе частичное произведение (p) (вектор переносов), представленное битовым вектором pn+m–1,pn+m–2,...,p1,p0, где (n+m) – размер вектора, pn+m–1 – старший (знаковый) бит.

Рассмотрим вариант выполнения заявленного умножителя, в котором (n ≥ 4, m ≥ 4).

Варианты выполнения заявленного умножителя для случаев (n < 4) или (m < 4) не рассматриваются, однако могут быть осуществлены на основе формулы для случая (n ≥ 4, m ≥ 4).

Как следует из таблиц истинности одноразрядного умножителя [1], логического блока XOR [2], одноразрядного полного сумматора [3] и полусумматора [4], для любого из этих блоков порядок входов не влияет на выходной результат, то есть входы этих блоков можно менять местами.

Обозначим как сигнал (nA) выход логического блока XOR [2], входы которого соединены со входами умножителя (an–1) и (tcA).

Обозначим как сигнал (nB) выход логического блока XOR [2], входы которого соединены со входами умножителя (bm–1) и (tcB).

Массив одноразрядных полных сумматоров [3] и полусумматоров [4] содержит (m–2) каскадов, которые пронумерованы при помощи индекса (i), где (i = 0,1,...,m–3).

Каскад одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 0) содержит (n) одноразрядных полных сумматоров [3] и полусумматоров [4], которые пронумерованы при помощи индекса (j), где (j = 0,1,...,n–1).

Каждый каскад одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 1,...,m–3) содержит (n–1) одноразрядных полных сумматоров [3] и полусумматоров [4], которые пронумерованы при помощи индекса (j), где (j = 1,...,n–1).

Элементами каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 0) являются (n–1) одноразрядных полных сумматоров [3] с индексами (j = 1,...,n–1) и один одноразрядный полусумматор [4] с индексом (j = 0).

Элементами каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 1,...,m–4), при условии (m > 4), являются (n–2) одноразрядных полных сумматоров [3] с индексами (j = 2,...,n–1) и один одноразрядный полусумматор [4] с индексом (j = 1).

Элементами каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = m–3) являются (n–1) одноразрядных полных сумматоров [3] с индексами (j = 1,...,n–1).

Выход умножителя (p0) соединён с логическим нулём.

Выход умножителя (s0) соединён с выходом одноразрядного умножителя [1], входы которого соединены со входами умножителя (a0) и (b0).

Выход умножителя (p1) соединён с логическим нулём.

Выходы умножителя (s1) и (p2) соединены с выходами (s) и (co) соответственно одноразрядного полусумматора [4] с индексами (i = 0, j = 0), входы (a) и (b) которого соединены с выходами одноразрядных умножителей [1], входы первого из которых соединены со входами умножителя (a1) и (b0), а входы второго со входами умножителя (a0) и (b1).

Выходы умножителя (s2) и (p3) соединены с выходами (s) и (co) соответственно одноразрядного полного сумматора [3] с индексами (i = 0; j = 1), входы (a), (b) и (co) которого соединены с выходами одноразрядных умножителей [1], входы первого из которых соединены со входами умножителя (a2) и (b0), входы второго со входами умножителя (a1) и (b1), а входы третьего со входами умножителя (a0) и (b2).

Выходы умножителя (sk) и (pk+1), где (k = 3,...,m–2), при условии (m > 4), соединены с выходами (s) и (co) соответственно одноразрядных полусумматоров [4] с индексами (i = k–2; j = 1) соответственно.

Выходы умножителя (sk) и (pk+1), где (k = m–1,...,m+n–3), соединены с выходами (s) и (co) соответственно одноразрядных полных сумматоров [3] с индексами (i = m–3; j = k–m+2) соответственно.

Выход умножителя (sm+n–2) соединён с выходом логического блока XOR [2], вход (a) которого соединён с выходом одноразрядного умножителя [1], входы которого соединены со входами умножителя (an–1) и (bm–1), и вход (b) которого соединён с выходом логического блока XOR [2], входы которого соединены с сигналами (nA) и (nB).

Выход умножителя (pm+n–1) соединён с выходом логического блока XOR [2], входы которого соединены с сигналами (nA) и (nB).

Выход умножителя (sm+n–1) соединён с выходом одноразрядного умножителя [1], входы которого соединены с сигналами (nA) и (nB).

Входы (a) одноразрядных полных сумматоров [3] с индексами (i = 0,...,m–3; j = n–1), соединены с выходами логических блоков XOR [2], входы (a) которых соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj) и (bi+1) соответственно, и входы (b) которых соединены с сигналами (nA).

Входы (a) одноразрядных полных сумматоров [3] с индексами (i = 1,...,m–3; j = 2,...,n–2) соединены с выходами (s) одноразрядных полных сумматоров [3] с индексами (i–1; j+1) соответственно.

Вход (a) одноразрядного полного сумматора [3] с индексами (i = m–3; j = 1) соединён с выходом (s) одноразрядного полного сумматора [3] с индексами (i–1; j+1).

Входы (a) одноразрядных полусумматоров [4] с индексами (i = 1,...,m–4; j = 1), при условии (m > 4), соединены с выходами (s) одноразрядных полных сумматоров [3] с индексами (i–1; j+1) соответственно.

Входы (ci) одноразрядных полных сумматоров [3] с индексами (i = 1,...,m–3; j = 2,...,n–1) соединены с выходами (co) одноразрядных полных сумматоров [3] с индексами (i–1; j) соответственно.

Вход (ci) одноразрядного полного сумматора [3] с индексами (i = m–3; j = 1) соединён с выходом логического блока XOR [2], входы которого соединены с сигналами (nA) и (nB).

Входы (b) одноразрядных полных сумматоров [3] с индексами (i = m–3; j = 1,...,n–1), соединены с выходами логических блоков XOR [2], входы (a) которых соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj–1) и (bi+2) соответственно, и входы (b) которых соединены с сигналами (nB).

Входы (b) одноразрядных полных сумматоров [3] с индексами (i = 1,...,m–4; j = 2,...,n–1), при условии (m > 4), соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj–1) и (bi+2) соответственно.

Входы (b) одноразрядных полусумматоров [4] с индексами (i = 1,...,m–4; j = 1), при условии (m > 4), соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj–1) и (bi+2) соответственно.

Вход (ci) одноразрядного полного сумматора [3] с индексами (i = 0; j = n–1) соединён с выходом логического блока XOR [2], входы которого соединены с сигналами (nA) и (nB).

Вход (a) одноразрядного полного сумматора [3] с индексами (i = 0; j = n–2), соединён с выходами логического блока XOR [2], вход (a) которого соединён с выходом одноразрядного умножителя [1], входы которого соединены со входами умножителя (aj+1) и (bi), и вход (b) которого соединён с сигналом (nA).

Входы (a) одноразрядных полных сумматоров [3] с индексами (i = 0; j = 2,...,n–3), при условии (n > 4), соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj+1) и (bi) соответственно.

Входы (b) одноразрядных полных сумматоров [3] с индексами (i = 0; j = 2,...,n–1) соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj–1) и (bi+2) соответственно.

Входы (ci) одноразрядных полных сумматоров [3] с индексами (i = 0; j = 2,...,n–2) соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj) и (bi+1) соответственно.

Выходные данные умножителя, представленные первым частичным произведением (s) (сумма частичных произведений множителей) и вторым частичным произведением (p) (вектор переносов) могут быть преобразованы в итоговое произведение (x), представленное битовым вектором xn+m–1,xn+m–2,...,x1,x0, где (n+m) – размер вектора, xn+m–1 – старший (знаковый) бит.

Для получения итогового произведения (x), необходимо подать выходные данные умножителя, представленные первым и вторым частичными произведениями, на входы (n+m)-разрядного полусумматора, называемого сумматором приведения.

Итоговое произведения (x) является выходом сумматора приведения.

Заявленный параметризуемый однотактный умножитель двоичных чисел с фиксированной точкой в прямом и дополнительном коде имеет следующие преимущества.

Обладает свойством универсальности за счет того, что любой из множителей может быть представлен как в прямом, так и в дополнительном коде.

Является параметризуемым за счет того, что может быть имплементирован для множителей с любым количеством разрядов.

Имеет меньшие размеры по площади по сравнению с не универсальными умножителями.

Обладает простотой разводки при реализации в качестве топологии интегральной микросхемы, что уменьшает его размеры по площади и увеличивает быстродействие.

Выдает результат в двухрядном коде, что позволяет использовать частичные произведения дальше без задержки переноса при формировании полного произведения.

Выдает полное произведение множителей, при наличии в нем дополнительного (n+m)-разрядного полусумматора, осуществляющего суммирование частичных произведений двухрядного кода.

Хотя описанный выше вариант выполнения заявленного изобретения был изложен с целью иллюстрации заявленного изобретения, специалистам ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла заявленного изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ КОДЕР БЧХ С РЕКОНФИГУРИРУЕМОЙ КОРРЕКТИРУЮЩЕЙ СПОСОБНОСТЬЮ | 2021 |

|

RU2777527C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ | 2024 |

|

RU2829089C1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| КОНВЕЙЕРНЫЙ АРИФМЕТИЧЕСКИЙ УМНОЖИТЕЛЬ | 2013 |

|

RU2546072C1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Матричный умножитель по модулю чисел Ферма | 1990 |

|

SU1783513A1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Устройство умножения двоично-десятичных цифр | 1982 |

|

SU1073771A1 |

Изобретение относится к области цифровой обработки сигналов, к структурам вычислительных блоков микропроцессоров. Техническим результатом является повышение универсальности за счет того, что любой из множителей может быть представлен как в прямом, так и в дополнительном коде; улучшение параметризуемости, за счет возможности имплементации для множителей с любым количеством разрядов; уменьшение размеров по площади и увеличение быстродействия, за счет отсутствия дополнительных сумматоров для преобразования произведения и более простой топологии; повышение универсальности вследствие возможности вывода результата в двухрядном коде, что позволяет использовать частичные произведения дальше без задержки переноса. Устройство содержит массив одноразрядных умножителей, логические блоки XOR, массив одноразрядных полных сумматоров и полусумматоров. 8 ил.

Параметризуемый однотактный умножитель двоичных чисел с фиксированной точкой в прямом и дополнительном коде, содержащий соединенные между собой:

- массив одноразрядных умножителей [1], выполненных с возможностью формирования частичных одноразрядных произведений входных множителей;

- логические блоки XOR [2], выполненные с возможностью модифицирования множителей с учетом их типа, а также с возможностью приема входных сигналов (tcA) и (tcB)

- массив одноразрядных полных сумматоров [3] и полусумматоров [4], расположенных каскадами со сдвигом и соединенных с возможностью сформирования конечного произведения, представленного двухрядным кодом в виде двух частичных произведений, причем входными данными умножителя являются:

- первый множитель (a), представленный битовым вектором an–1,an–2,...,a1,a0, где n – размер вектора (n ≥ 1), an–1 – старший (знаковый) бит;

- второй множитель (b), представленный битовым вектором bm–1,bm–2,...,b1,b0, где m – размер вектора (m ≥ 1), bm–1 – старший (знаковый) бит;

- сигнал (tcA), выполненный с возможностью определения типа первого множителя (a): 0 – прямой код, 1 – дополнительный код;

- сигнал (tcB), выполненный с возможностью определения типа второго множителя (b): 0 – прямой код, 1 – дополнительный код;

выходными данными умножителя являются:

- первое частичное произведение (s) (сумма частичных произведений множителей), представленное битовым вектором sn+m–1,sn+m–2,...,s1,s0, где (n+m) – размер вектора, sn+m–1 – старший (знаковый) бит;

- второе частичное произведение (p) (вектор переносов), представленное битовым вектором pn+m–1,pn+m–2,...,p1,p0, где (n+m) – размер вектора, pn+m–1 – старший (знаковый) бит;

при n ≥ 4, m ≥ 4

- для любого из блоков одноразрядного умножителя [1], логического блока XOR [2], одноразрядного полного сумматора [3] и полусумматора [4] порядок входов не влияет на выходной результат, то есть входы этих блоков можно менять местами;

- сигнал (nA) на выходе логического блока XOR [2], входы которого соединены со входами умножителя (an–1) и (tcA);

- сигнал (nB) на выходе логического блока XOR [2], входы которого соединены со входами умножителя (bm–1) и (tcB);

- массив одноразрядных полных сумматоров [3] и полусумматоров [4] содержит (m–2) каскадов, которые пронумерованы при помощи индекса (i), где (i = 0,1,...,m–3);

- каскад одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 0) содержит (n) одноразрядных полных сумматоров [3] и полусумматоров [4], которые пронумерованы при помощи индекса (j), где (j = 0,1,...,n–1);

- каждый каскад одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 1, ..., m–3) содержит (n–1) одноразрядных полных сумматоров [3] и полусумматоров [4], которые пронумерованы при помощи индекса (j), где (j = 1,...,n–1);

- элементы каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 0) являются (n–1) одноразрядных полных сумматоров [3] с индексами (j = 1,...,n–1) и один одноразрядный полусумматор [4] с индексом (j = 0);

- элементами каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = 1,...,m–4), при условии (m > 4), являются (n–2) одноразрядных полных сумматоров [3] с индексами (j = 2,...,n–1) и один одноразрядный полусумматор [4] с индексом (j = 1);

- элементами каскада одноразрядных полных сумматоров [3] и полусумматоров [4] с индексом (i = m–3) являются (n–1) одноразрядных полных сумматоров [3] с индексами (j = 1,...,n–1);

- выход умножителя (p0) соединен с логическим нулем;

- выход умножителя (s0) соединен с выходом одноразрядного умножителя [1], входы которого соединены со входами умножителя (a0) и (b0);

- выход умножителя (p1) соединен с логическим нулем;

- выходы умножителя (s1) и (p2) соединены с выходами (s) и (co) соответственно одноразрядного полусумматора [4] с индексами (i = 0, j = 0), входы (a) и (b) которого соединены с выходами одноразрядных умножителей [1], входы первого из которых соединены со входами умножителя (a1) и (b0), а входы второго со входами умножителя (a0) и (b1);

- выходы умножителя (s2) и (p3) соединены с выходами (s) и (co) соответственно одноразрядного полного сумматора [3] с индексами (i = 0; j = 1), входы (a), (b) и (co) которого соединены с выходами одноразрядных умножителей [1], входы первого из которых соединены со входами умножителя (a2) и (b0), входы второго со входами умножителя (a1) и (b1), а входы третьего со входами умножителя (a0) и (b2);

- выходы умножителя (sk) и (pk+1), где (k = 3,...,m–2), при условии (m > 4), соединены с выходами (s) и (co) соответственно одноразрядных полусумматоров [4] с индексами (i = k–2; j = 1) соответственно;

- выходы умножителя (sk) и (pk+1), где (k = m–1,...,m+n–3), соединены с выходами (s) и (co) соответственно одноразрядных полных сумматоров [3] с индексами (i = m–3; j = k–m+2) соответственно;

- выход умножителя (sm+n–2) соединен с выходом логического блока XOR [2], вход (a) которого соединен с выходом одноразрядного умножителя [1], входы которого соединены со входами умножителя (an–1) и (bm–1), и вход (b) которого соединен с выходом логического блока XOR [2], входы которого соединены с сигналами (nA) и (nB);

- выход умножителя (pm+n–1) соединен с выходом логического блока XOR [2], входы которого соединены с сигналами (nA) и (nB);

- выход умножителя (sm+n–1) соединен с выходом одноразрядного умножителя [1], входы которого соединены с сигналами (nA) и (nB);

- входы (a) одноразрядных полных сумматоров [3] с индексами (i = 0,...,m–3; j = n–1), соединены с выходами логических блоков XOR [2], входы (a) которых соединены с выходами одноразрядных умножителей [1], входы которых соединены со входами умножителя (aj) и (bi+1) соответственно, и входы (b) которых соединены с сигналами (nA);

- входы (a) одноразрядных полных сумматоров [3] с индексами (i = 1,...,m–3; j = 2,...,n–2) соединены с выходами (s) одноразрядных полных сумматоров [3] с индексами (i–1; j+1) соответственно;

- вход (a) одноразрядного полного сумматора [3] с индексами (i = m–3; j = 1) соединен с выходом (s) одноразрядного полного сумматора [3] с индексами (i–1; j+1);

- входы (a) одноразрядных полусумматоров [4] с индексами (i = 1,...,m–4; j = 1), при условии (m > 4), соединены с выходами (s) одноразрядных полных сумматоров [3] с индексами (i–1; j+1).

| US 5153850 A, 06.10.1992 | |||

| US 5313414 A, 17.05.1994 | |||

| US 5351206 A, 27.09.1994 | |||

| CN 1561478 A, 05.01.2005 | |||

| ФУНКЦИОНАЛЬНАЯ ВХОДНАЯ СТРУКТУРА ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОГО УМНОЖИТЕЛЯ f(Σ) В ПОЗИЦИОННОМ ФОРМАТЕ МНОЖИМОГО [m]f(2) И МНОЖИТЕЛЯ [n]f(2) (ВАРИАНТЫ) | 2010 |

|

RU2422881C1 |

| Устройство для умножения чисел с фиксированной запятой | 1989 |

|

SU1758644A1 |

Авторы

Даты

2021-08-12—Публикация

2020-12-26—Подача