Изобретение относится к вычислительной технике и предназначено для использования в системах обработки сигнала при построении систем целеуказания и самонаведения на подводных объектах. Известные генераторы булевых функций, предназначенные для обработки сигналов, см., например, «схемы мажоритарной логики общего назначения» Патент США №3296424, 1967 г. бюллетень изобретений January №1, кл. США 235-152, логический вычислитель G06F 7/57 2324219 от 12.12.2006.

А.С. 1084782, 1990 г., G06F 7/00 устройство для вычисления систем булевых функций.

А.С. СССР №1032451, 1980 г., устройство для вычисления симметричных булевых функций, а также генераторы сигналов, изменяющихся по ортогональным функциям Радемахера-Уолша (авторское свидетельство №221757, опубликованное 17.07.1968), а также генераторы ортогональных функций.

А.С. СССР №92783 МКИ G06S 7/26, G06F 1/00, А.С. СССР №131092 МКИ2 G06S 7/26, А.С. СССР №170298 МКИ3 G06S 7/22, «генератор двоичных ортогональных последовательностей «Electronique» №17, 1967 г.

Наиболее близким по технической сущности к предлагаемому изобретению является «устройство для вычисления коэффициентов преобразования по Уолшу» (Патент США №3742201, кл. G01F 7/38, 26.06.1973 г., патент США №3792355, кл. H04J 3/18, 12.02.1974).

Названное устройство, содержащее N ступеней единичного преобразования, соединенных последовательно. Каждая ступень единичного преобразования включает блоки элементов совпадения «И», элемент задержки и сумматор-вычислитель. Недостатком прототипа устройства является его сложность, невозможность функционировать с логическими функциями, а также осуществлять преобразования в реальном масштабе времени. Патенты США содержат log2N ступеней единичного преобразования, где N число разрядов преобразуемой последовательности. Каждая из ступеней содержит первый регистр сдвига, вход и выход которого соединен со входом сумматора вычислителя, первый вход которого подключен к первым входам элементов группы совпадений «И», а второй соединен со вторыми входами элементов группы совпадений «И» через второй регистр сдвига, выходы элементов группы совпадения «И» каждой ступени соединены со входами регистра сдвига последующей ступени, и блок управления, выходы которого соединены со вторыми входами элементов группы «И» совпадений всех ступеней единичного преобразования. Недостатком устройства является то, что оно не может работать в реальном масштабе времени, поскольку первый коэффициент преобразования на выходе устройства появляется после того, как N-oe значение дискретного сигнала поступит на вход устройства. В течение последующих N тактов, т.е. от N по 2N такта, на выходе появляется N коэффициентов преобразования от последовательности, составленной из первых, т.е. от 1 до N значений входного дискретного сигнала. В течение последующих N тактов, т.е. от 2N до 3N такта, на выходе устройства появляется N коэффициентов преобразования от последовательности, составленной из следующих N значений входного сигнала, т.е. от N+1 no 2N и т.д.

Цель изобретения - расширение области применения, заключающееся в возможности функционирования устройства в реальном масштабе времени, а также с логическими булевыми функциями.

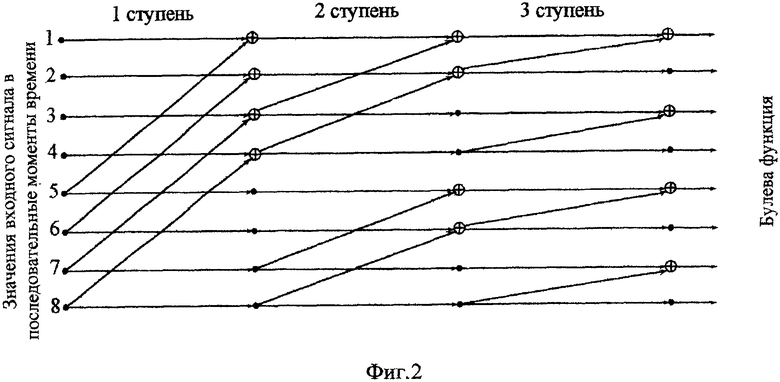

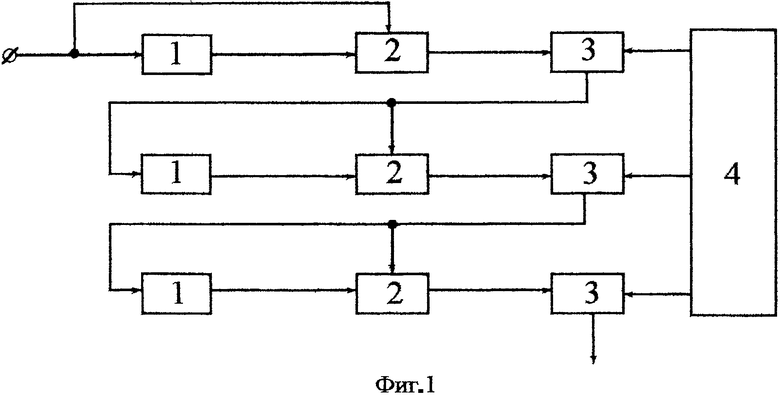

Цель изобретения достигается тем, что в него введен логический сумматор, или схема неравнозначности, выход которого каждой ступени единичного преобразования соединен с другими входами элементов группы совпадений «И». На фиг.1 представлена схема устройства, на фиг.2 - последовательность вычисления.

Устройство содержит регистр сдвига 1, логический сумматор в виде схемы неравнозначности, функционирующий по следующему правилу:

Х2 - выход регистра 1

Ф - выход сумматора, или схема неравнозначности. группу элементов совпадении «И» - 3 и блок управления - 4.

Устройство работает следующим образом. Регистры сдвига 1 во всех ступенях единичного преобразования задерживают дискретный сигнал на одинаковое число тактов, а именно N/2. Тактовая частота в регистре сдвига 1 первой ступени преобразования равна частоте следования входного сигнала, а тактовая частота регистров сдвига 1 в каждой последующей ступени преобразования в 2 раза больше, чем в предыдущей. Это позволяет получить коэффициенты преобразования от последовательностей, получаемых после каждого нового значения входного сигнала, т.е. составленных из значений входного сигнала от 1-го по N, от 2 по N+1, от 3 по N+2 и т.д. Рассмотрим работу устройства на примере N=8. В этом случае регистры 1 сдвига в любой ступени преобразования имеют длину 2. С частотой тактовых импульсов в регистре 1 сдвига первой ступени преобразования значения дискретного сигнала последовательно поступают на вход первой ступени преобразования. Логический сумматор 2 производит суммирование или не производит суммирование значений сигнала с выход регистра 1 сдвига и входа ступени преобразования. Суммируются первое и пятое, второе и шестое и т.д. значения сигнала поступающего в ступень преобразования. Блок элементов совпадения «И» - 3 работает с частотой в 2 раза больше чем тактовая частота в регистре 1 сдвига, и выдает на вход следующей ступени преобразования последовательность либо суммы, либо саму последовательность, поступающих на логический сумматор 2.

Таким образом во 2 ступени единичного преобразования числа с выхода блока элементов «И» первой ступени преобразования поступают с частотой, вдвое большей частоты следования значений входного сигнала, 2 ступень единичного преобразования, как и каждая последующая, работает аналогично первой, но только с частотой, вдвое большей чем предыдущая. Поэтому на выходе 3 ступени единичного преобразования с частотой, в 8 раз большей частоты следования входного сигнала, получают коэффициенты преобразования последовательностей в виде булевых функций в алгебре конъюнкций, состоящих из значений входного сигнала с 1 по N, с 2 по N-1, с 3 по N+2 и т.д. Блок управления осуществляет управление и синхронизацию.

Предлагаемое устройство к каждому новому значению входного сигнала вычисляет коэффициент булевого преобразования от последовательностей, состоящих из N предыдущих значений сигнала, что позволяет использовать его в системах реального времени, а единообразие задержек в схемах единичного преобразования дает возможность использовать идентичные ступени единичного преобразования.

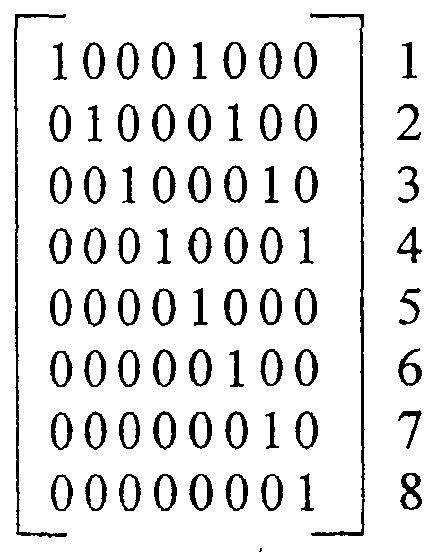

В матричном виде эти преобразования после первой ступени представятся в виде следующих последовательностей:

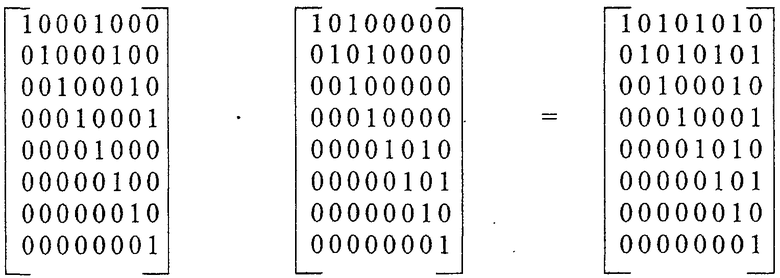

После 2 ступени:

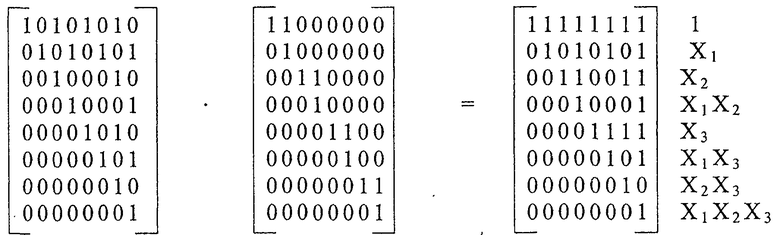

После 3 ступени:

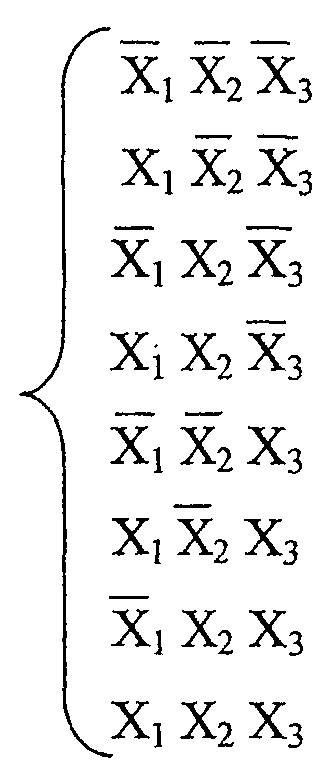

В результате после 3 ступени на строках появились последовательности в виде булевых функций в алгебре Жегалкина: 1, Х1 Х2, Х1 Х2, Х3, Х1 Х3, Х2 Х3, Х1, Х2 Х3;

Это преобразование обладает замечательным свойством.

Полученная булевая матрица А совпадает с А-1, т.е.

А·А-7=Е,

Где Е - единичная матрица.

Из чего следует, что если на вход подать последовательность в виде дизъюнктивно-конъюнктивной формы в базисе конъюнкций:

то на выходе получим значения булевой функции в алгебре полиномов Жегалкина.

Такие преобразования широко применяются в системах обработки информации в задачах классификации и распознавания объектов. Предложенное устройство осуществляет эти преобразования в реальном масштабе времени простыми средствами.

В настоящее время проведены лабораторные исследования генератора булевых функций на компьютере и подготавливается аппаратура передачи информации для натурных подводных исследований на основе предложенного генератора.

Предложенное устройство используется при проведении плановых работ по модернизации одного из разрабатываемых в институте приборов, которое рассмотрено на НТС от 26.02.2009 и рекомендовано для рассмотрения служебного охраноспособного результата интеллектуальной деятельности авторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ БУЛЕВЫХ ПРЕОБРАЗОВАНИЙ НАД ПОЛЕМ ГАЛУА GF(2) | 2011 |

|

RU2475810C2 |

| Устройство для вычисления симметричных булевых функций | 1980 |

|

SU959064A1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 1991 |

|

RU2045769C1 |

| СПОСОБ ДЕКОДИРОВАНИЯ ПСЕВДОШУМОВОГО СИГНАЛА | 2014 |

|

RU2584963C1 |

| Способ и устройство безопасной обработки служебно-технологических команд в инфокоммуникационных системах | 2018 |

|

RU2700400C1 |

| СПЕЦПРОЦЕССОР ДЛЯ ЗАДАЧИ ВЫПОЛНИМОСТИ БУЛЕВЫХ ФОРМУЛ | 2017 |

|

RU2644505C1 |

| Устройство для распознавания на линейность булевых функций | 1990 |

|

SU1756879A1 |

| Регистр сдвига | 2017 |

|

RU2691852C2 |

| Устройство для вычисления систем булевых функций | 1988 |

|

SU1532912A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

Изобретение относится к вычислительной технике и может быть использовано при обработке гидроакустических сигналов в системах передачи информации. Технический результат заключается в обеспечении возможности функционирования в реальном масштабе времени. Генератор сигналов содержит log2N ступеней единичного преобразования, где N - число разрядов преобразуемой последовательности, каждая из ступеней содержит регистр сдвига, элементы группы совпадения «И», выходы элементов группы совпадения «И» каждой ступени соединены с входами регистра сдвига последующей ступени, и блок управления, выходы которого соединены со вторыми входами элементов группы совпадения «И» всех ступеней единичного преобразования, в каждой ступени единичного преобразования введен элемент «исключающее ИЛИ», первый вход которого подключен к входу регистра сдвига этой же ступени, а второй вход - к выходу регистра сдвига этой же ступени, при этом выходы элементов «исключающее ИЛИ» соединены с первыми входами элементов группы совпадения «И» той же ступени единичного преобразования. 2 ил.

Генератор сигналов, изменяющихся по булевым функциям, содержащий log2N ступеней единичного преобразования, где N - число разрядов преобразуемой последовательности, каждая из ступеней содержит синхронизированный от блока управления регистр сдвига, элементы группы совпадения «И», выходы элементов группы совпадения «И» каждой ступени соединены с входами регистра сдвига последующей ступени, и блок управления, выходы которого соединены со вторыми входами элементов группы совпадения «И» всех ступеней единичного преобразования, отличающийся тем, что в каждой ступени единичного преобразования введен элемент «исключающее ИЛИ», первый вход которого подключен к входу регистра сдвига этой же ступени, а второй вход - к выходу регистра сдвига этой же ступени, при этом выходы элементов «исключающее ИЛИ» соединены с первыми входами элементов группы совпадения «И» той же ступени единичного преобразования.

| Устройство для вычисления коэффициентов преобразования по уолшу | 1975 |

|

SU744555A1 |

| US 3792355 A, 12.02.1974 | |||

| US 3742201 A, 26.06.1973 | |||

| УСТРОЙСТВО ДЛЯ ОРТОГОНАЛЬНОГО ПРЕОБРАЗОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ ПО УОЛШУ-АДАМАРУ | 1989 |

|

RU2012047C1 |

Авторы

Даты

2014-01-27—Публикация

2010-12-03—Подача