П 16

сл со ю

со

к

Шиг.1

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления систем булевых функций о

Цель изобретения - повышение производительности устройства, за счет обработки логических переменных группами переменной длины.

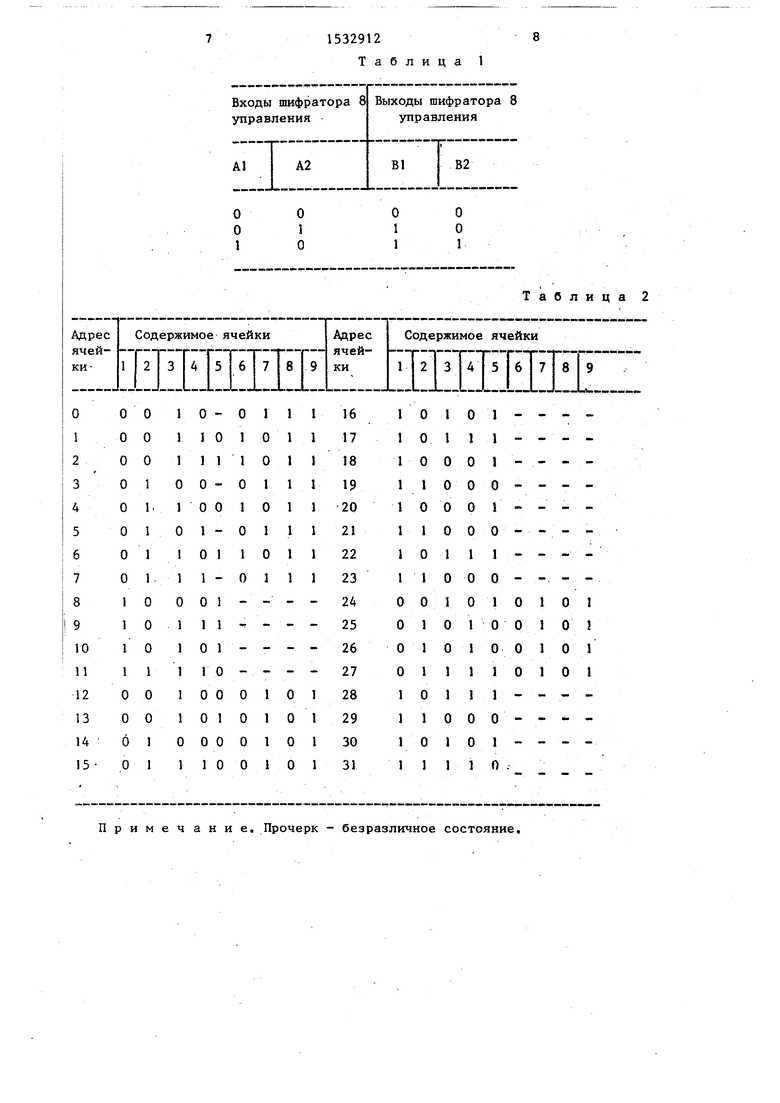

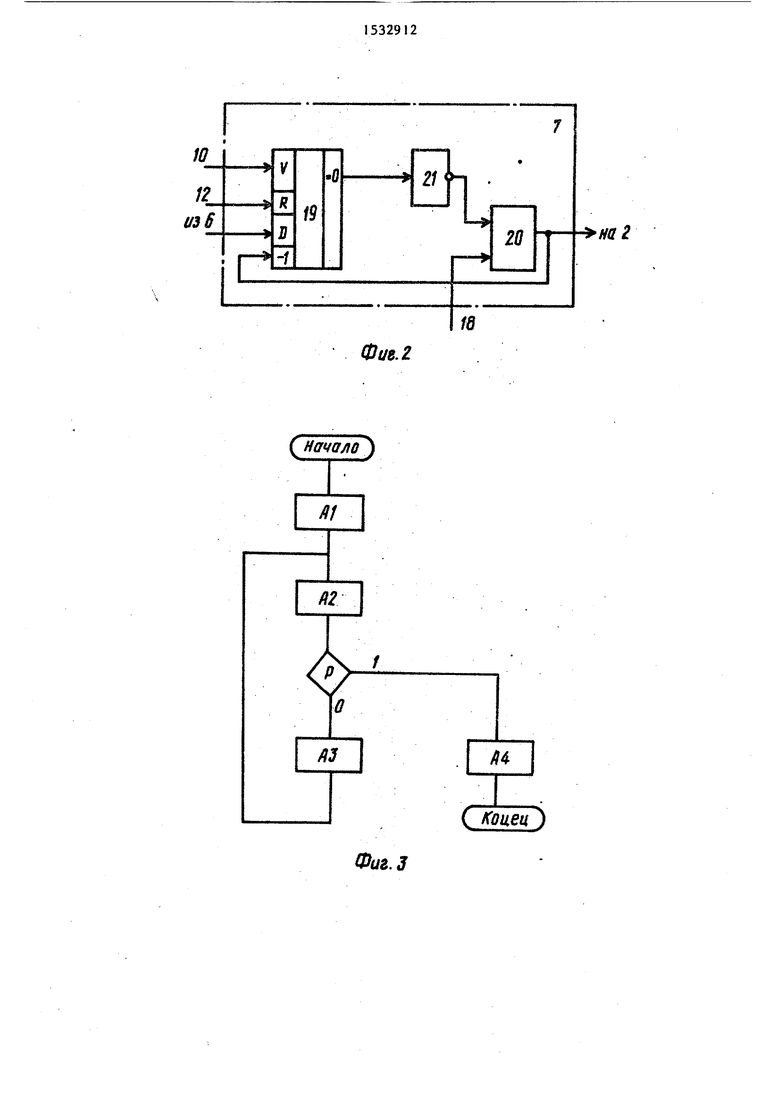

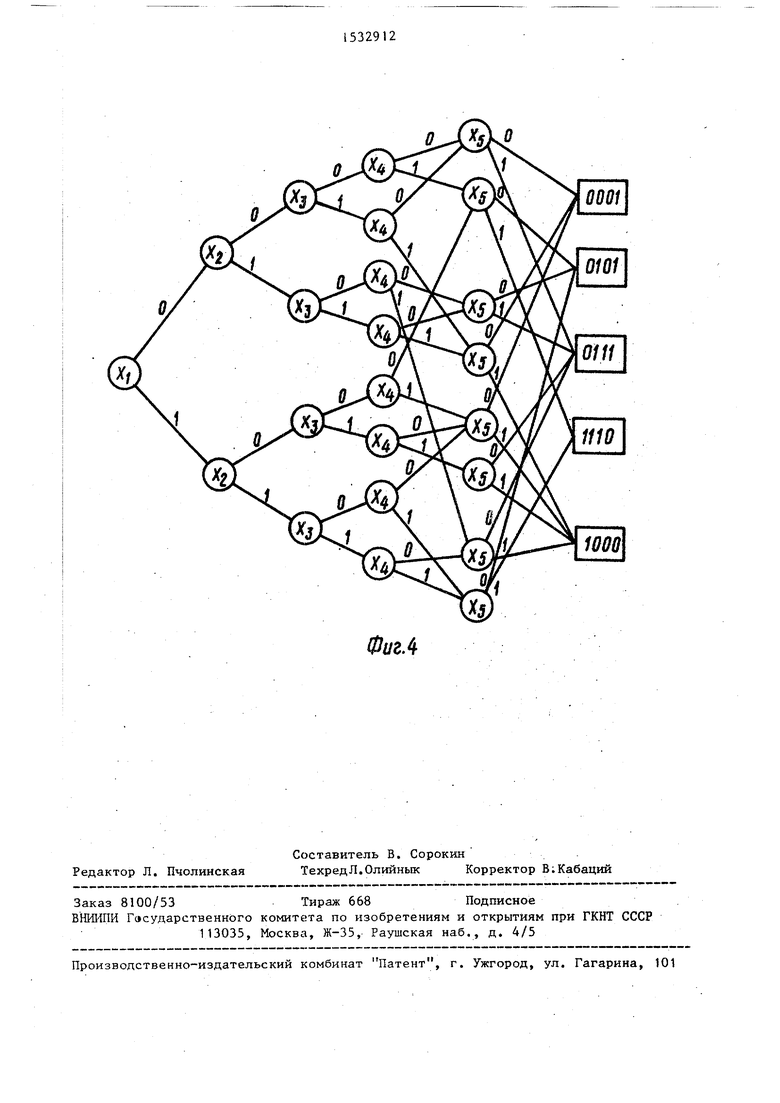

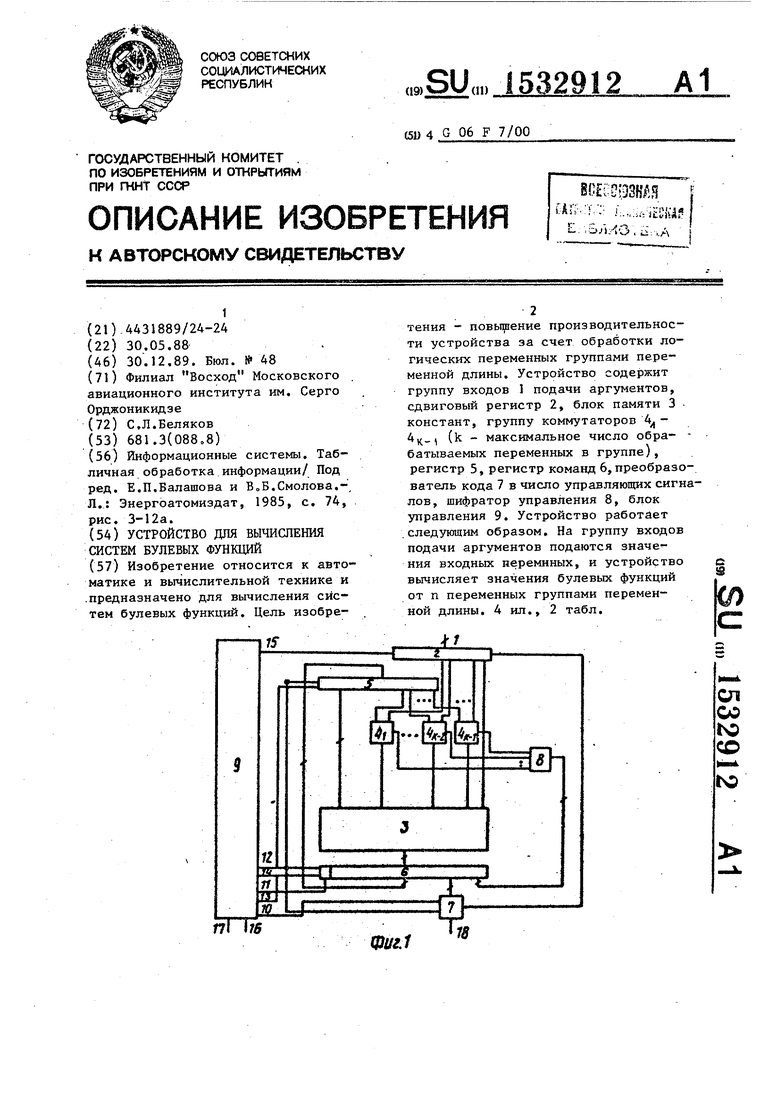

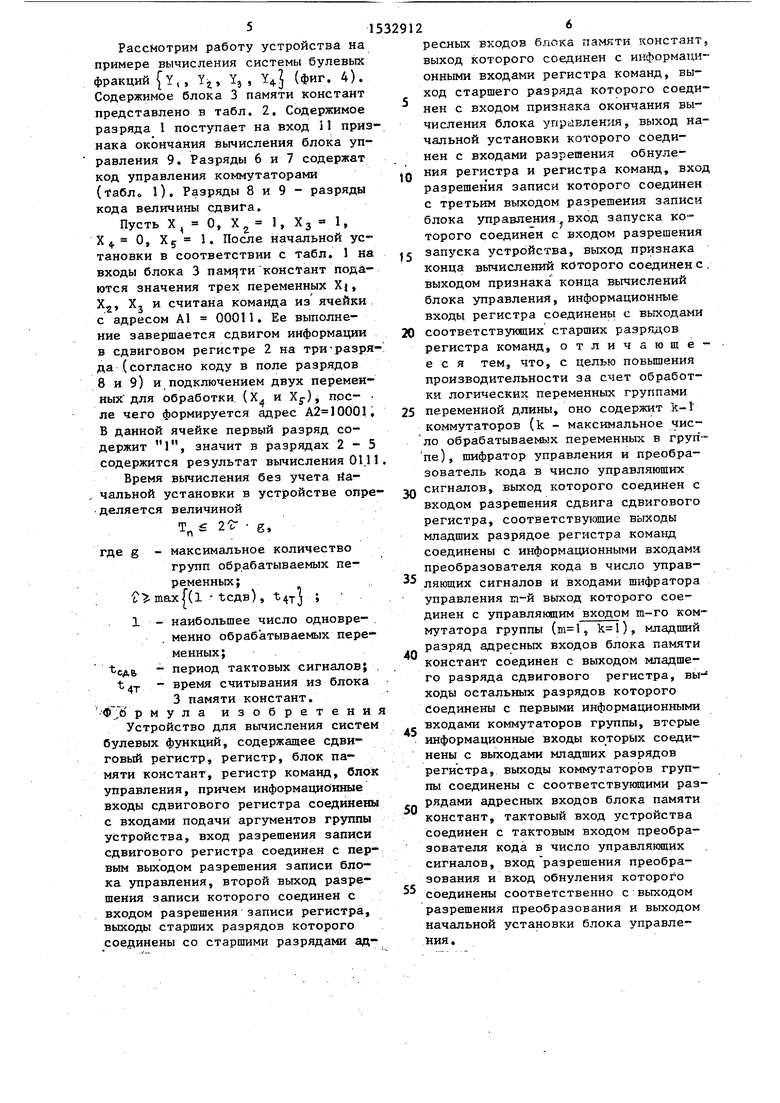

На фиг. 1 представлена структурная схема устройства для вычисления систем булевых функций; на фиг. 2 - функциональная схема преобразования кода в число управляющих сигналов; на фиг. 3 - алгоритм работы блока управления; на ф лг„ 4 граф-схема вычисления системы булевых функций.

Устройство для вычисления систем булевых функций содержит группу входов -1 подачи аргументов, сдвиговый регистр 2, блок - 3 памяти констант, группу коммутаторов 4,- 4К (где k - максимальное число обрабатываемых переменных в группе), регистр 5 регистр 6 команд, преобразователь 7 кода в число управляющих сигналов , шифратор 8 управления, блок 9 управления, выход 10 разрешения преобразования блока 9 управления, вход 11 признака окончания вычисления блока 9 управления, выход 12 начальной установки блока 9 управления, три выхода 13-15 разрешения записи блока 9 управления, выход 16 признака конца вычислений, вход 17 разрешения запуска и тактовый вход 18.

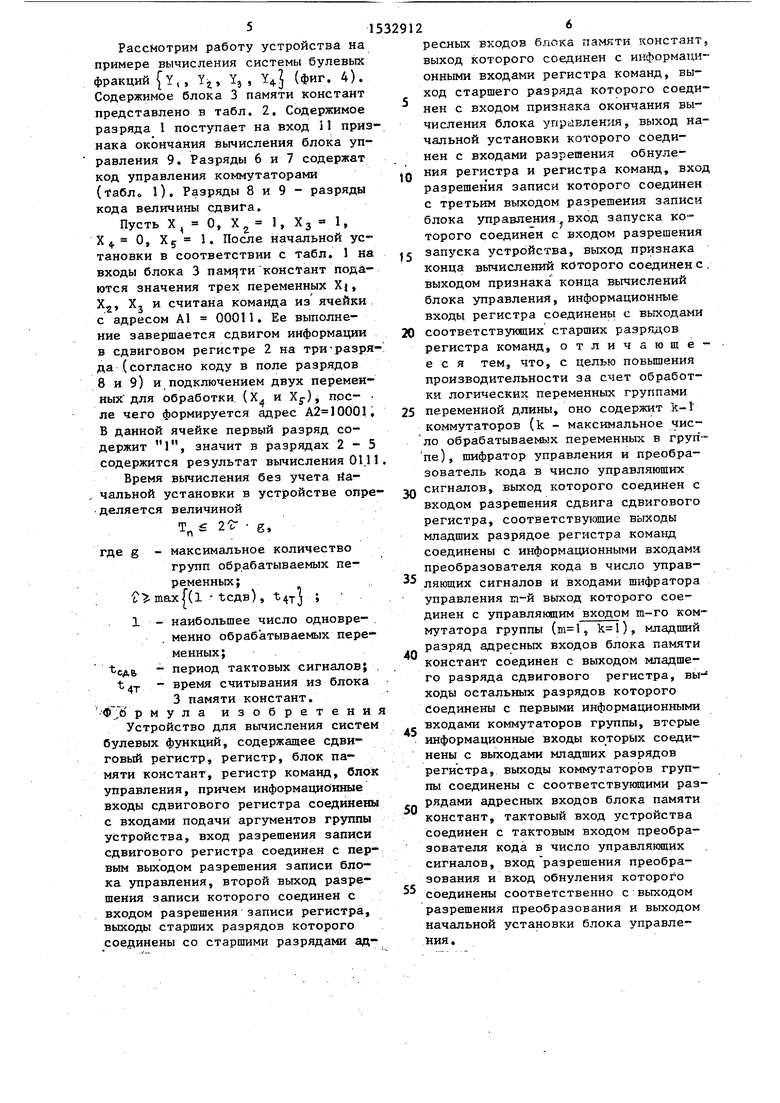

Преобразователь 7 кода в число управляющих сигналов образуют вычитающий счетчик 19, элемент И 20 и элемент НЕ 21„

На фиг. 3 приняты следующие обозначения: А1 - микрооперация начальной .установки (обнуления) регистра 5S регистра 6 команд и преобразо- ва теля 7 кода в число управляющих сигналов разрешения записи в сдвиговый регистр 2; А2 - микрооперация записи в регистр 6 команд; A3 - микрооперация записи в регистр 5 и разрешения преобразования в преобразователе 7 кода в число управляющих сигналов; АД - выход 16 признака конца вычислений равен I1 ; р - значение выхода старшего разреза регистра команд 6 (признак окончания вычисления).

5

0

5

0

5

0

5

0

5

Шифратор 8 управления служит для преобразования информации с выхода регистра команд 6 в сигналы, управляющие выбором информации в соответствующем коммутаторе 4,- 4К группы.

В табл. 1 приведена таблица истинности шифратора 8 управления для k 3.

Устройство работает следующим образомо

В исходном состоянии на группу входов 1 подачи аргументов поданы значения входных переменных, на тактовый вход 18 непрерывно поступают тактовые сигналы. Устройство начинает работать согласно алгоритму на фиг. 3 после поступления сигнала единичного уровня на вход 17 разрешения запуска. При этом количество одновременно обрабатываемых переменных (путем соответствующей коммутации значений разрядов переменных и разрядов регистра 5) определяется значением кода, поступающего с выхода регистра 6 команд на входы шифратора 8 управления, При этом полагается, что на т-й адресный вход блока памяти констант 3 поступает информация с выхода т-го разряда регистра 5, если управляющий сигнал т-го коммутатора равен 1 (т 1, k-l), в противном слу- . чае на in-й адресный вход блока 3 памяти констант поступает информация с выхода ла-го разряда сдвигового регистра 2, Таким образом, для (табл. 1) при В1 В2 О происходит обработка трех переменных, при Bl e О, В2 1 - двух переменных, при , одной переменной .

Информация с выходов разрядов кода величины сдвига регистра 6 команд используется для соответствующего сдвига переменных в сдвиговом регистре 2, при этом преобразователь 7 кода в число управляющих сигналов под управлением сигнала единичного уровня с выхода 10 разрешения преоб-., разования блока 9 управления вырабатывает m-И сигналов, разрешающих сдвиг информации на один разряд. После осуществления операции сдвига на адресных входах блока 3 памяти констант формируется адрес следующей, команды.

51

Рассмотрим работу устройства на примере вычисления системы булевых фракций Y,, Yt, Y, , Y45 (фиг. 4). Содержимое блока 3 памяти констант представлено в табл. 2. Содержимое разряда 1 поступает на вход I1 признака окончания вычисления блока управления 9. Разряды 6 и 7 содержат код управления коммутаторами (табл. 1). Разряды 8 и 9 - разряды кода величины сдвига.

Пусть X, - О, Х4- 1, Х3 - 1, X4. О, Х5 1. После начальной установки в соответствии с табл. 1 на входы блока 3 памяти констант подаются значения трех переменных Xj, Х2, X, и считана команда из ячейки с адресом А1 00011. Ее выполнение завершается сдвигом информации в сдвиговом регистре 2 на три-разряда (согласно коду в поле разрядов 8 и 9) и подключением двух переменных для обработки (X, и Xf), пос- ле чего формируется адрес А2 10001, В данной ячейке первый разряд содержит 1, значит в разрядах 2-5 содержится результат вычисления 01.11

Время вычисления без учета начальной установки в устройстве опре деляется величиной

ТпЈ 2Ъ в,

где g - максимальное количество групп обрабатываемых переменных;(l -Ьсдв), t4T5 ;

1 - наибольшее число одновременно обрабатываемых переменных;сдь период тактовых сигналов} - время считывания из блока

3 памяти констант. Формула изобретения

Устройство для вычисления систем булевых функций, содержащее сдвиговый регистр, регистр, блок памяти констант, регистр команд, блок управления, причем информационные входы сдвигового регистра соединены с входами подачи аргументов группы устройства, вход разрешения записи сдвигового регистра соединен с первым выходом разрешения записи блока управления, второй выход разрешения записи которого соединен с входом разрешения записи регистра, выходы старших разрядов которого соединены со старшими разрядами ад

JQ

jj 20 25

30

дд

35

45

0

5

26

ресных входов блока памяти констант, выход которого соединен с информационными входами регистра команд, выход старшего разряда которого соединен с входом признака окончания вычисления блока управления, выход начальной установки которого соединен с входами разрешения обнуления регистра и регистра команд, вход разрешения записи которого соединен с третьим выходом разрешения записи блока управления вход запуска которого соединен с входом разрешения запуска устройства, выход признака конца вычислений которого соединен с . выходом признака конца вычислений блока управления, информационные входы регистра соединены с выходами соответствующих старших разрядов регистра команд, отличающееся тем, что, с целью повышения производительности за счет обработки логических переменных группами переменной длины, оно содержит k-1 коммутаторов (k - максимальное число обрабатываемых переменных в груп- пе), шифратор управления и преобразователь кода в число управляющих сигналов, выход которого соединен с входом разрешения сдвига сдвигового регистра, соответствующие выходы младших разрядов регистра команд соединены с информационными входами преобразователя кода в число управляющих сигналов и входами шифратора управления n-й выход которого соединен с управляющим входом m-го коммутатора группы ( ), младший разряд адресных входов блока памяти констант соединен с выходом младшего разряда сдвигового регистра, вы- ходы остальных разрядов которого соединены с первыми информационными входами коммутаторов группы, вторые информационные входы которых соединены с выходами младших разрядов регистра, выходы коммутаторов группы соединены с соответствующими разрядами адресных входов блока памяти констант, тактовый вход устройства соединен с тактовым входом преобразователя кода в число управляющих сигналов, вход разрешения преобразования и вход обнуления которого соединены соответственно с выходом разрешения преобразования и выходом начальной установки блока управления.

1532912

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления систем булевых функций | 1988 |

|

SU1631537A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Устройство логической обработки | 1982 |

|

SU1124317A1 |

| Программируемый контроллер | 1989 |

|

SU1647594A1 |

| Устройство для вычисления булевых функций | 1988 |

|

SU1501033A1 |

| Устройство для вычисления систем булевых функций | 1989 |

|

SU1644126A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство для вычисления систем булевых функций | 1987 |

|

SU1509865A1 |

| Устройство для моделирования конечных автоматов | 1977 |

|

SU717775A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для вычисления систем булевых функций. Цель изобретения - повышение производительности устройства за счет обработки логических переменных группами переменной длины. Устройство содержит группу входов 1 подачи аргументов, сдвиговый регистр 2, блок памяти 3 констант, группу коммутаторов 41-4K-1 (K - максимальное число обрабатываемых переменных в группе), регистр 5, регистр команд 6, преобразователь кода 7 в число управляющих сигналов, шифратор управления 8, блок управления 9. Устройство работает следующим образом. На группу входов подачи аргументов подаются значения входных переменных, и устройство вычисляет значения булевых функций от N переменных группами переменной длины. 4 ил., 2 табл.

Примем ание. Прочерк - безразличное состояние.

{начало}

Фиг. 2

№

{Конец )

Фи&.З

Фиг А

| Информационные системы | |||

| Табличная обработка информации/ Под ред | |||

| Е.П.Балашова и В„Б.Смолова.-, Л.: Энергоатомиэдат, 1985, с | |||

| Приспособление в центрифугах для регулирования количества жидкости или газа, оставляемых в обрабатываемом в формах материале, в особенности при пробеливании рафинада | 0 |

|

SU74A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-30—Публикация

1988-05-30—Подача