Изобретение относится к цифровой вычислительной и информационной технике и может быть использовано в станках с программным управлением и для предварительной обработки входной информации в автоматизированных системах научных исследований.

Известны интерполятор для программного управления станками [А.с. 253896 СССР Интерполятор для программного управления станками, 1969 г.], а также цифровой линейный интерполятор [SU 1629897 А1, 26.09.88г.] для прямых линий на экране дисплея путем их кусочно-линейной аппроксимации. Недостатками известных цифровых интерполяторов является невозможность цифровой интерполяции других линий, кроме прямых, например, логарифмической.

Наиболее близким по технической сущности является линейный интерполятор по оценочной функции с одновременным шагом [Кошкин В.Л. Аппаратные системы числового программного управления. - М.: Машиностроение, 1989, с.61, рис.3.14]. Он состоит из сумматора, двух регистров со входом предварительной установки их содержимого, блока элементов ИЛИ и двух блоков элементов И, двух счетчиков со входами предварительной установки начального значения, двух триггеров, двух линий задержки, четырех элементов И, двух элементов НЕ. Причем вход сумматора через блок элементов ИЛИ связан через первый и второй блоки элементов И с первым и вторым регистрами, а управляющие входы блоков элементов И через линии задержки связаны с выходами первого и второго элементов И, первые входы которых связаны через логический элемент НЕ с выходом знакового разряда сумматора, а вторые входы тех же элементов И связаны с выходом четвертого элемента И, на вход которого поступают тактовые импульсы. Выходы Х и Y связаны с выходами четвертого и второго элементов И. Недостатком этого интерполятора является невозможность интерполяции им логарифмической кривой и большая абсолютная погрешность, равная шагу интерполяции.

Задачей настоящего изобретения является расширение функциональных возможностей цифрового интерполятора в части цифровой интерполяции логарифмической кривой.

Технический результат настоящего изобретения - возможность цифровой интерполяции логарифмической кривой и снижение максимальной абсолютной погрешности в два раза.

Поставленная задача решена предложенным цифровым интерполятором, который содержит сумматор, регистр, первый и второй двоичные счетчики (все со входами установки начальных значений), первый и второй блоки элементов И, блок элементов ИЛИ, первый и второй триггеры, первую и вторую линии задержки, первый, второй, третий и четвертый элементы И, первый и второй элементы НЕ, причем регистр m-разрядными шинами через второй блок элементов И и блок элементов ИЛИ связан с сумматором, знаковый разряд которого связан со вторым элементом И и через первый элемент НЕ связан со входом первого элемента И, а выходы первого и второго элементов И через первую и вторую линии задержки связаны с разрешающими входами второго и первого блоков элементов И соответственно, при этом выход второго элемента И является выходом Y интерполятора и связан со счетным входом второго двоичного счетчика, выход которого связан со входом сброса в "0" первого триггера, прямой выход которого связан со входом первого элемента И, а инверсный выход которого связан со входом третьего элемента И, как и инверсный выход второго триггера, но вход сброса в "0" которого связан с выходом первого двоичного счетчика, счетный вход которого связан выходом Х интерполятора и с выходом четвертого элемента И, выход которого также связан со входами первого и второго элементов И, кроме того, выход третьего элемента И связан с выходом "окончание отработки" и через второй элемент НЕ связан со входом четвертого элемента И, вход которого связан со входом тактовых импульсов, а вход второго элемента И связан с прямым выходом второго триггера, вход установки в "1" которого, как и аналогичный вход первого триггера, связан со входом Пуск, и, наконец, вход предварительной установки интерполятора связан со входами сброса в "0" первого и второго триггеров, а прямой выход второго триггера связан со входом второго элемента И. Кроме того, в цифровой интерполятор дополнительно введен третий двоичный счетчик со входом установки его начального значения, счетный вход второго младшего разряда которого соединен с выходом Х интерполятора, а выход связан через второй блок элементов И со входом блока элементов ИЛИ.

Замена первого регистра на двоичный счетчик со входом предварительной установки его начального значения является новым техническим решением в технике цифровой интерполяции, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и элементов позволяет цифровую интерполяцию логарифмической кривой.

Предложенный цифровой интерполятор промышленно применим, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральные логические микросхемы).

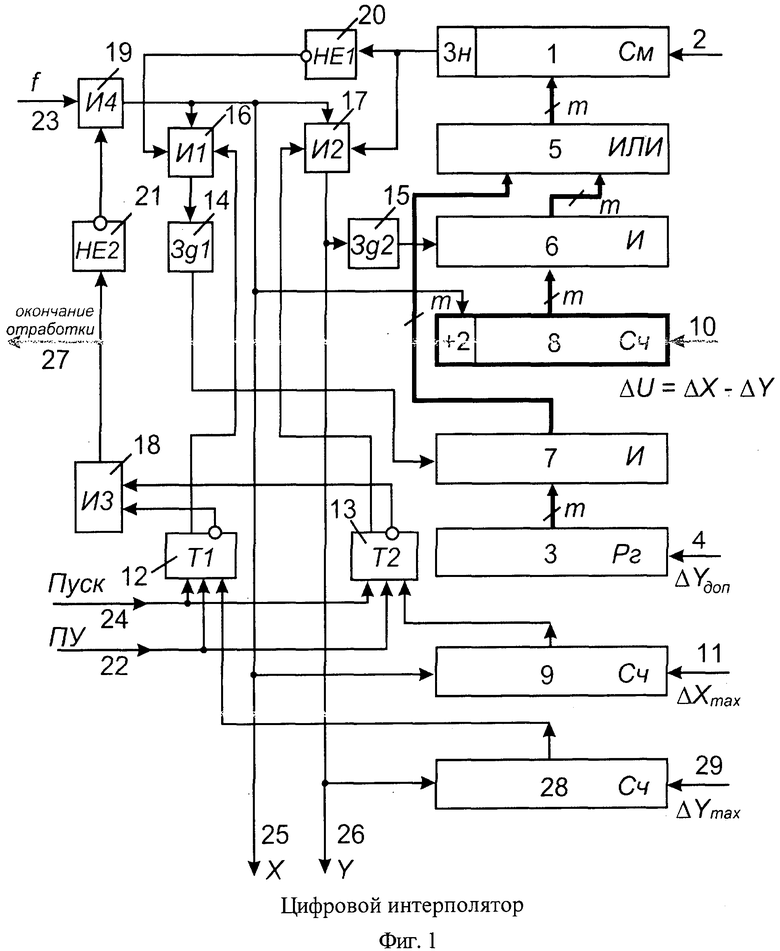

На фиг.1 приведена функциональная схема цифрового интерполятора, а на фиг.2 - график интерполяции логарифмической кривой.

Заявленное устройство содержит (фиг.1) сумматор 1 со входом 2 предварительной установки значения, регистр 3 со входом 4 предварительной установки значения, блок ИЛИ 5, первый 6 и второй 7 блоки элементов И, первого 28, второго 9 и третьего 8 двоичных счетчиков со входами 29, 11, 10 предварительной установки их начального значения, первого 12 и второго 13 триггеров, первой 14 и второй 15 линий задержки, первого 16, второго 17, третьего 18 и четвертого 19 элементов И и первого 20 и второго 21 элементов НЕ. Сумматор 1, регистр 3, блок элементов ИЛИ 5, блоки элементов И 6, 7, счетчики 8, 9 и 28 имеют m разрядов, где m - максимальная разрядность входных данных, включая знак. Триггеры 12, 13 имеют прямой и инверсный выходы, а также входы установки "1" и сброса в "0". Два элемента И 18, 19 имеют два входа, а два элемента И 16, 17 - по три входа. Вход 22 - сигнал предварительной установки - обозначен ПУ. Вход 23 - тактовых импульсов - обозначен ƒ. Вход 24 обозначен Пуск. Выходы 25, 26 обозначены X, Y соответственно. Выход 27 обозначен "окончание отработки". Регистр 3 и третий двоичный счетчик 28 m-разрядными шинами через блоки элементов И 6 и 7 соответственно связаны с сумматором 1 через блок элементов ИЛИ 5, реализуя связь с сумматором фактически через мультиплексор на два входа. Знаковый разряд Зн сумматора 1 связан с элементом И 17 и через элемент НЕ 20 - с первым элементом И 16. Их выходы через линии задержки 14 и 15 связаны с разрешающими входами блоков элементов И 7 и 6 соответственно. Кроме того, выход второго элемента И 17 является выходом Y 26 интерполятора. Вход ПУ 22 связан со входами сброса в "0" триггеров 12 и 13. Вход Пуск связан со входами установки в "1” тех же триггеров. Прямой выход первого триггера 12 связан с первым элементом И 16, а инверсный - с третьим элементом И 18. Входы сброса в "0" триггеров 12 и 13 имеют связь с выходами обнуления первого 9 и второго 28 счетчиков соответственно. Прямой выход триггера 13 связан со вторым элементом И 17, а инверсный - с третьим элементом И 18. Выход элемента И 18 связан с выходом 27 "окончание отработки" и через второй элемент НЕ 21 со входом четвертого элемента И 19, на другой вход которого поступают тактовые импульсы ƒ (вход 23). Выход четвертого элемента И 19 соединен со входами элементов И 16 и 17, а также со счетными входами счетчиков 8 и 9 и, кроме того, - с выходом Х 25 интерполятора. Выход второго элемента И 17 связан со счетным входом двоичного счетчика 28 и с выходом Y интерполятора. Выходы первого 16 и второго 17 элементов И через первую 14 и вторую 15 линии задержки связаны со входами второго 7 и первого 6 блоков элементов И соответственно.

Достоверность достижения поставленной цели изобретения - реализация цифровой интерполяции логарифмической кривой - подтверждается математическим обоснованием, изложенным в [Цифровые интерполяторы криволинейных траекторий - журнал “Известия вузов. Северо-Кавказский регион”. Технические науки, 2011, №2, с.16-18]. Уравнение логарифмической кривой

Для этого ΔY=2A-2=const, а ΔU=2B-2A+2+2i≠const. Для обеспечения минимальной для цифровой интерполяции погрешности (не более 0,5 шага интерполяции), необходимо начальное значение сумматора-вычитателя 1 взять не нулевым, как у прототипа [3], а равным B-2A.

В исходном состоянии интерполятора подачей импульса на вход ПУ 22 триггеры 12 и 13 сбрасываются в "0". По сигналу Пуск (вход 24) триггеры 12 и 13 устанавливаются в "1", кроме того, по входу 2 в сумматор 1 заносится константа (2B-2A), по входу 10 в счетчик 8 заносится константа (2B-2A), по входу 4 в регистр 3 заносится константа -(2A-1) в дополнительном коде и по входу 11 в счетчик 9 величина "-ΔXmax" в дополнительном коде. Далее два сигнала "0" с триггеров 12 и 13 через элемент И 18 и элемент НЕ 21 откроют элемент И 19, и очередной положительный импульс частотой ƒ (вход 23) проследует на вход элементов И 16 и 17, а также на выход Х 25 интерполятора. На выход Y 26 интерполятора он проследует, если знак сумматора 1 будет "-" (единица в знаковом разряде Зн). Одновременно положительный импульс с выхода элемента И 19 поступает на счетный вход с весом "+2" двоичного счетчика 8, увеличивая его значение на два.

Если же знак Зн сумматора 1 будет "+" (ноль в знаковом разряде), то на выход Y 26 сигнал не пройдет (элемент И 17 будет закрыт). Спустя некоторое время (время задержки менее четверти периода частотой ƒ) возникает положительный импульс на выходе первой линии задержки Зд 14 или второй линии задержки Зд 15 (только одной), каждый из которых либо подсуммирует содержимое регистра Рг 3 (через блок элементов И 7 и блок элементов ИЛИ 5) к сумматору См 1, либо - содержимое двоичного счетчика Сч 8 (через блок элементов И 6 и блок элементов ИЛИ 5) к сумматору См 1. На этом один такт ƒ входных импульсов закончится. Новое значение знака Зн сумматора См 1 будет управлять работой интерполятора в следующем такте. Каждый отработанный такт ƒ по входу 23 подсчитывается по сигналу с выхода Х 25 счетчиком Сч 9, работающим как вычитающий. При поступлении ровно Xmax импульсов двоичный счетчик Сч 9 выдаст сигнал на сброс в "0" триггеров 12 и 13. Сигналы "1" с их инверсных выходов через третий элемент И 18 и третий элемент НЕ 21 закроют четвертый элемент И 19, прервав тем самым поступление импульсов со входа ƒ 23.

Работа интерполятора окончена. Высокий уровень "1" с выхода третьего элемента И 18 выдает сигнал "окончена отработка". В результате отработки будет произведена цифровая интерполяция логарифмической кривой с максимальной абсолютной погрешностью, равной 0,5 шага интерполяции.

Достоверность функционирования заявленного цифрового интерполятора подтвердим на простом примере при А=7 и В=11 (см. таблицу 1 и фиг.2). Малые значения А и В взяты по соображениям сокращения размеров таблицы 1.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2513683C1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1290354A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Цифровой адаптивный линейный интерполятор | 1982 |

|

SU1095189A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2120137C1 |

| Цифровой квадратичный интерполятор | 1985 |

|

SU1317452A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| ИНТЕРПОЛЯТОР | 1997 |

|

RU2127902C1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

Изобретение относится к цифровой вычислительной и информационной технике и может быть использовано в станках с программным управлением и в автоматизированных системах научных исследований. Техническим результатом является возможность цифровой интерполяции логарифмической кривой. Цифровой интерполятор содержит сумматор, регистр, первый и второй двоичные счетчики, первый и второй блоки элементов И, блок элементов ИЛИ, первый и второй триггеры, первую и вторую линии задержки, первый, второй, третий и четвертый элементы И, первый и второй элементы НЕ. В цифровой интерполятор дополнительно введен третий двоичный счетчик со входом установки его начального значения, счетный вход второго младшего разряда которого соединен с выходом Х интерполятора, а выход связан через второй блок элементов И со входом блока элементов ИЛИ. 2 ил., 1 табл.

Цифровой интерполятор, содержащий сумматор, регистр, первый и второй двоичные счетчики (все со входами установки начальных значений), первый и второй блоки элементов И, блок элементов ИЛИ, первый и второй триггеры, первую и вторую линии задержки, первый, второй, третий и четвертый элементы И, первый и второй элементы НЕ, причем регистр m-разрядными шинами через второй блок элементов И и блок элементов ИЛИ связан с сумматором, знаковый разряд которого связан со вторым элементом И и через первый элемент НЕ связан со входом первого элемента И, а выходы первого и второго элементов И через первую и вторую линии задержки связаны с разрешающими входами второго и первого блоков элементов И соответственно, при этом выход второго элемента И является выходом Y интерполятора и связан со счетным входом второго двоичного счетчика, выход которого связан со входом сброса в "0" первого триггера, прямой выход которого связан со входом первого элемента И, а инверсный выход которого связан со входом третьего элемента И, как и инверсный выход второго триггера, но вход сброса в "0" которого связан с выходом первого двоичного счетчика, счетный вход которого связан с выходом Х интерполятора и с выходом четвертого элемента И, выход которого также связан со входами первого и второго элементов И, кроме того, выход третьего элемента И связан с выходом "окончание отработки" и через второй элемент НЕ связан со входом четвертого элемента И, вход которого связан со входом тактовых импульсов, а вход второго элемента И связан с прямым выходом второго триггера, вход установки в "1" которого, как и аналогичный вход первого триггера, связан со входом Пуск, и, наконец, вход предварительной установки интерполятора связан со входами сброса в "0" первого и второго триггеров, а прямой выход второго триггера связан со входом второго элемента И, отличающийся тем, что дополнительно введен третий двоичный счетчик со входом установки его начального значения, счетный вход второго младшего разряда которого соединен с выходом Х интерполятора, а выход связан через второй блок элементов И со входом блока элементов ИЛИ.

| Цифровой линейный интерполятор | 1988 |

|

SU1629897A1 |

| ИНТЕРПОЛЯТОР ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯСТАНКАМИ | 0 |

|

SU253896A1 |

| US 7171435 B2, 30.01.2007 | |||

| КОШКИН В.Л., "Аппаратные системы числового программного управления", Москва, Машиностроение, 1989, стр | |||

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

2014-04-20—Публикация

2013-02-22—Подача