Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления станками.

Известен круговой интерполятор, содержащий накапливающий сумматор, соединенный с выходами двух ревер- сивных счетчиков, с блоком сравнения координат, блоком сравнения с радиусом и блоком выбора сектора, соединенным с генератором Ц.

Известен- также линейный интерполятор, содержащий коммутатор, соединенный с двумя регистрами, схемой сравнения, блоком управления и с последовательно соединенными делителем, блоком памяти, двоичным сумматором, накапливающим сумматором и выходным коммутатором 2.

Недостатком этих интерполяторов является большая сложность, обусловленная применением специальных зна- ковых разрядов арифметических узлов, и низкое быстродействие, связанное с; необходимостью выполнения нескольких вычислительных тактов для размещения единичного приращения координат при круговой,интерполяции.

Наиболее близким техническим решением к изобретению является интерполятор, содержащий вводное устройство, соединенное с координатными регистрами и блоком задания скорости, подключенный к накапливающему сумматору через блок определения знака оценочной функции, причем координатные регистры через злемент И-ИЛИ и НЕ подсоединены к накапливающему сумматору 3. Недостатком известного интерполя10тора является его сложность и уменьшение быст родействия при круговой интерполяции. Это связано с тем, что в соответствии с выражением круговой интерполяции по оценочным функциям

15

r:(2x.)-E:().0.

текущие значения параметров интерполяции суммированием необходимо удваи20вать, для чего требуются дополнительные разряды сумматора и регистров, а также дополнительный такт (на сдвиг или повторное суммирование). Усложняет интерполятор также использование

25 специальных знаковых разрядов, по которым устанавливается текущее значение знака оценочной функции.

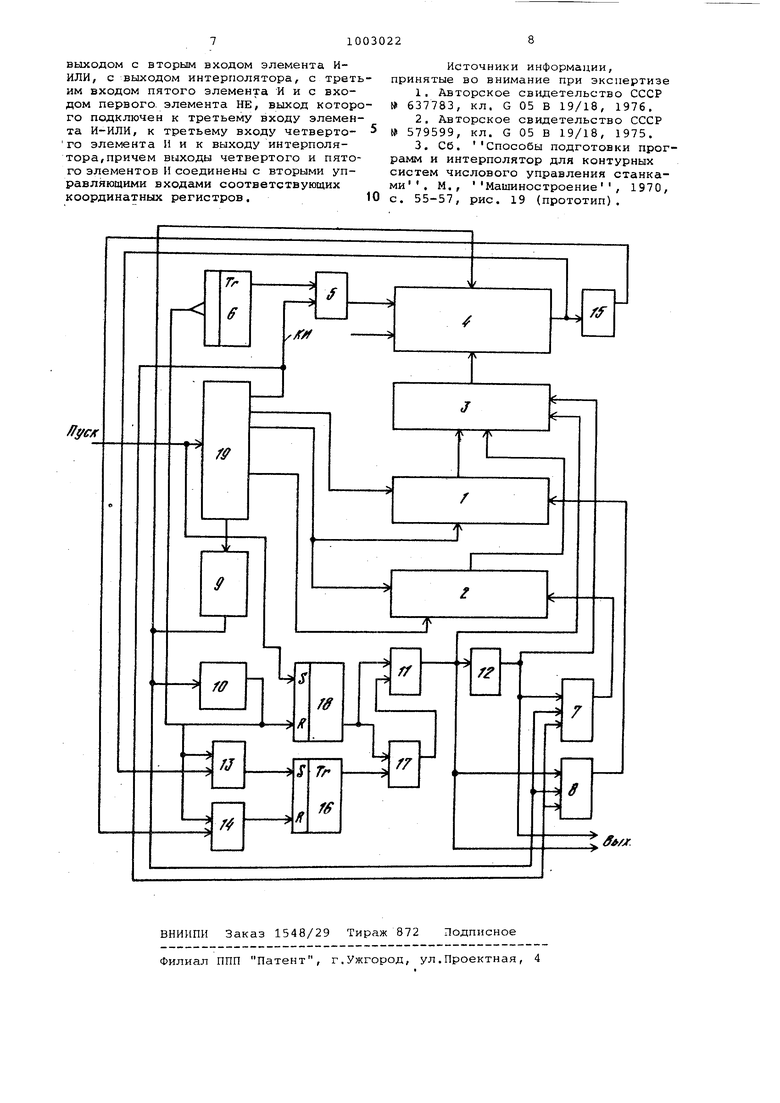

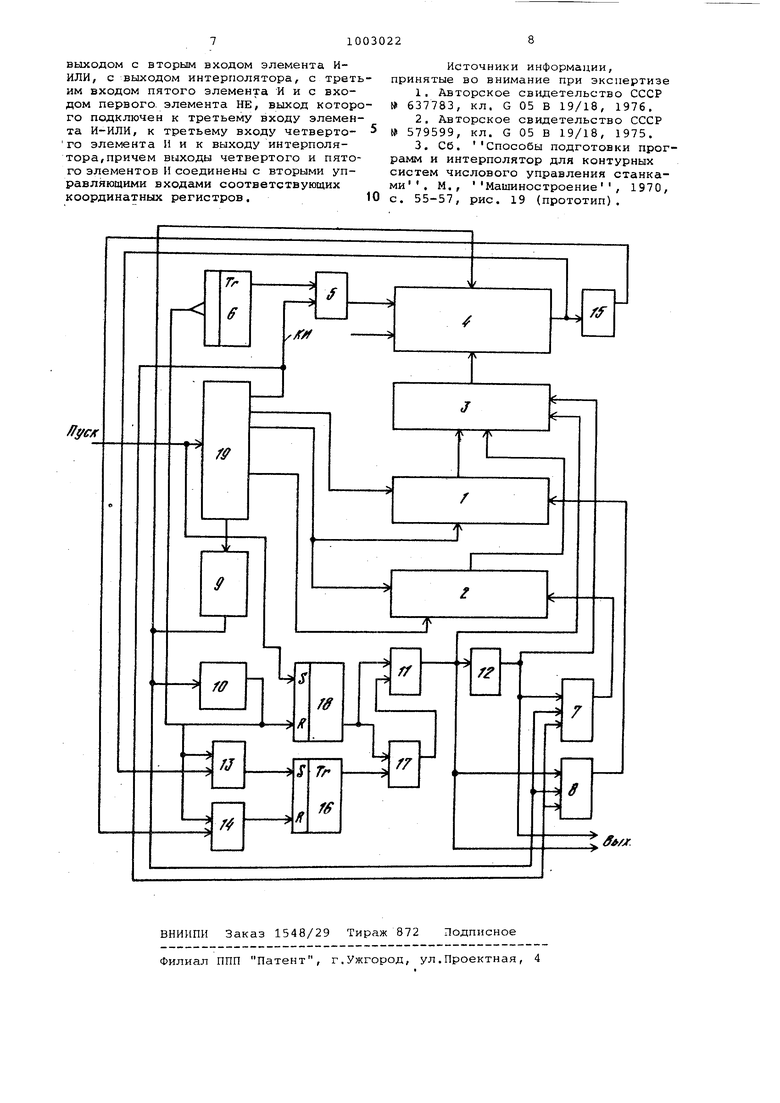

. Целью изобретения является упрощение интерполятора, что приводит так30же и к повышению его быстродействия. Поставленная цель достигается те что цифровой интерполятор, содержащий первый элемент НЕ, элемент заде ки, блок ввода программы, соединенный входом с запускающим входом интерполятора, первым выходом - с вхо дом блока задания скорости, а вторы выходами - с установочными и первыми управляющими входами координатны регистров, подключенных выходами к nepBEiM входам элемента И-ИЛИ, выход JKOTOporo соединен с информационным входом накапливающего сумматора, св ванного командным входом с выходом блока задания скорости, а выходом с первым входом первого элемента И и через второй элемент НЕ - с первы входом второго элемента И, выход ко торого подключен к R-входу первого RS-триггера, связанного с S-входом с выходом первого элемента И, содер жит три элемента И, элемент ИЛИ, триггер со счетным входом, элемент ЗАПРЕТ и второй RS-триггер, S-вход которого соединен с запускающим вхо дом интерполятора, R-выход - с управляющим входом элемента ЗАПРЕТ и с первым входом элемента ИЛИ, а Rвход - с вторыми входами первого и второго элементов И, с выходом элемента задержки и через триггер со счетным входом - с первым входом тр тьего элемента И, подключенного выходом «к управляющему входу накапливающего сумматора, а вторым входом к третьему выходу блока ввода программы и к первым входам четвертого пятого элементов И, соединенных вто рыми входами с входом элемента задержки и с выходом блока задания ск рости, информационный вход элемента ЗАПРЕТ подключен к S-выходу первого RS-триггера, а выход - к второму вхо ду элемента ИЛИ, соединенного выходом с вторым входом элемента И-ИЛИ, с выходом интерполятора, с третьим входом пятого элемента И и с входом первого элемента НЕ, выход которого подключен к третьему входу элемента И-ИЛИ, к третьему входу четвертого элемента И и к выходу интерполятора причем выходы четвертого и пятого элементов И соединены с вторыми управляющими входами соответствующих координатных регистров. На чертеже представлена функциональная схема интерполятора. Интерполятор содержит координатные регистры 1 и 2, элемент И-ИЛИ 3 накапливающий сумматор 4, третий элемент И 5, триггер б со счетным входом, четвертый 7 и пятый 8 элемен ты И, блок 9 задания скорости, элемент 10 задержки, элемент ИЛИ 11, первый элемент НЕ 12, первый 13 и второй 14 элементы И, второй элемент НЕ 15, первый RS-триггер 1б, элемент ЗАПРЕТ 17, второй RS-триггер 18 и блок 19 ввода программы. Принцип работы интерполятора заключается в следующем. На младший разряд накапливающего сумматора при круговой интерполяции текущие значения операндов после их удвоения (сдвига) не воздействует и этот разряд суммирует в накапливающем режиме единицу, что позволяет путем введения триггера со счетным входом реализовать функцию младшего разряда сумматора, при этом текущие значения операндов окажутся сдвинутыми по отношению к добавочно;му разряду на разряд в сторону старших, т.е. удвоенными. При линейной интерполяции работа триггера может быть заблокирована, в этом случае по отношению к разрядам сумматора операнды оказываются не сдвинутыми. При выполнении операций в соответствии с выражениями для линейной и круговой интерполяции по оценочной функции прямой код операнда меняется на дополнительный и обратно при каждой смене знака оценочной функции и, следовательно, суммирование дополнительных кодов после смены знака исключается. Это позволяет заменить операции над знаковыми разрядами простой идентификацией наличия или отсутствия сигнала Перенос на выходе сумматора, а, следовательно, исключить знаковые разряды. Несоответствие знака оценочной функции сигналу Перенос при начальном ходе ликвидируется его детерминированием. Интерполятор работает следующим образом. При поступлении- на блок 1Э сигнала Пуск информация программоносителя блока 19 дешифрируется и на его выходах возникают информационные и управляющие сигналы, при этом при линейной интерполяции в регистр 1 записывается в прямом коде заданное пе-. ремещение по первой координате (например Л X) ив регистр 2 - обратный код заданного перемещения по второй координате (например Z); при круговой интерполяции в эти регистры записываются соответственно прямой и обратный коды параметров интерполяции I и К . При линейной интерполяции блок 19 на выходе круговая интерполяция формирует запрещающий сигнал и элементы И 5, 7 и 8 отключены. Таким образом, на управляющий вход (переноса) сумматора 4 при обработке участка линейной интерполяции сигналов передаваться не будет. Сигнал Пуск устройства 19 поступает также на .Sвход триггера 18 и переводит его в состояние S, в результате- запрещающий потенциал поступает на управляющий вход элемента 17 и запрещает передачу управляющего сигнала от триггера 16,Таким образом,перед поступлением первого командного импульса от блока 9 на элемент И-ИЛИ 3 поступит сигнал,разрешающий передачу содержимого регистра на информационный вход (суммирования)сумматора 4.

Первый командный импульс, поступивший от блока задания 9, поступает на командный вход (суммирование) сумматора 4 и записывает содержимое регистра 2 в сумматор 4. Таким образом, блокирующий сигнал с триггера 18 обеспечивает принудительный шаг по первой коор- динате, так как в соответствии с алроритмом оценочной функции для линейной интерполяции шаг координаты противоположен заносимой в сумматор оординаты: ЛХ--1 при при II .-11л2.0 д X - ВЫХОД при Л Z - выход 1 Первый командный импульс блока 9 поступает также на вход элемента 10, а с его выхода на R-вход триггера 18 и входы элементов И 13 и 14. Триггер 18 переводится в состояние R, сигнал блокировки с входа элемента 17 снимается, и Элемент ИЛИ 11 подключен теперь через элемент 17 к триггеру 16. Так как при первом принудительном ходе сигнал на выходе Перенос сумматора 4 не возникает, то через элемент НЕ 15 разрешающий сигнал поступает на второй вход элемента И 14 и сигналом с его выхода триггер Г6 переводится в состояние Р. Сигнал с выхода триггера 16 через элементы 17 и 11 подключит теперь к входам сумматора 4 через элемент 3 выходы регистра 1. При последующих шагах передачи на суммирование содержимого регистров 1 или 2 зависит от возникновения или отсутствия сигнала Перенос на выходе сумматора 4. При этом наличию сигнала соответствует значение оценочной функции , а его отсутствию - значение . При круговой интерполяции разрешающий сигнал с выхода блока 19 подключает элементы и 5, 7 и 8. Через элемент И 5 на управляющий вход Пе ренос сумматора 4 теперь будет передаваться содержимое дополнительного разряда сумматора, реализованного на триггере Ь. Записанные в регистры 1 и 2 параметры I и К круговой интер поляции теперь по отношению к дополнительному разряду сдвинуты на один разряд в сторону старшего, что соответствуе их удвоению, необходимому для реализации алгоритма круговой

интерполяции методом оценочной функции.

Через элементы И 7 и 8 на регистры 1 и 2 поступают импульсы для преобразования параметров интерполяции. Первый принудительный шаг, независящий от состояния сумматора 4, выполняется аналогично рассмотренному при линейной интерполяции. А последующие шаги выполняются по знаку оценочной функции, формируемому элементами 15, 13, 14, 16, 17, 11 и12 по сигналу Перенос с выхода сумматора 4. Таким образом, благодаря триггеру 6 производится псевдоудвоение разрядности оборудования и при круговой интерполяции максимальновозможные перемещения не отличаются от максимальных перемещений при линейной интерполяции. Формула изобретения Цифровой интерполятор, содержащий первый элемент НЕ, элемент задержки, блок ввода программы, соединенный входом с запускающим входом интерполятора, первым выходом - с входом блока задания скорости, а вторыми выходами - с установочными и первыми управляющими входами координатных регистров , подключенных к первым входам элемента И-ИЛИ,выход которого соединен с информационным входом накапливающего сумматора,связанного командным входом с выходом блока задания скорости,а- выходом - с первым входом первого элемента И и через второй элемент НЕ - с первым входом второго элемента И, выход которого подключен к R-входу первого RS-триггера, связанногоS-входом с выходом, первого элемента И, отличающийся тем, что, с целью упрощения интерполятора, он содержит три элемента И, элемент ИЛИ, триггер со счетным входом, элемент ЗАПРЕТ и второй RS-тpиггep,S-вxoд которого соединен с запускающим входом интерполятора,R-ьыход- с управлякяцим входом эле-. мента ЗАПРЕТ и с первым входом элемен та ИЛИ, а R-вход - с вторыми входами первого и второго элементов И, с выходом элемента задержки и через триггер со счетным входом - с первым входом третьего элемента И, подключенного выходом к управляющему входу накапливающего сумматора, а вторым входом - к третьему выходу блока ввода программы, и к первым входам четвертого и пятого элементов И, соединенных вторыми входами с входом элемента задержки и с выходом блока задания скорости, информационный вход элемента ЗАПРЕТ подключен к S-выходу первого КЗ-триггера, а выход - к второму входу элемента ИЛИ, соединенного

выходом с вторым входом элемента ИИЛИ, с выходом интерполятора, с третьим входом пятого элемента И и с входом первого, элемента НЕ, выход которого подключен к третьему входу элемента И-ИЛИ, к третьему вход,у четверто- - То элемента Инк выходу интерполятора, причем выходы четвертого и пятого элементов И соединены с вторыми управляющими входами соответствующих координатных регистров,10

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 637783, кл. G 05 В 19/18, 1976.

2,Авторское свидетельство СССР № 579599, кл. G 05 В 19/18, 1975.

3,Сб. Способы подготовки программ и интерполятор для контурных систем числового управления станками. М., Машиностроение, 1970, с. 55-57, рис. 19 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции положения резца на станке с программным управлением | 1981 |

|

SU983651A1 |

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Графический интерполятор | 1985 |

|

SU1401509A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Линейно-круговой интерполятор | 1984 |

|

SU1215090A2 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

Авторы

Даты

1983-03-07—Публикация

1981-10-02—Подача