Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны комбинационные сумматоры (см., например, рис.9.2а на стр.98 в книге Браммер Ю.А. Цифровые устройства: Учеб. пособие для вузов / Ю.А.Браммер, И.Н.Пащук. - М.: Высш. шк., 2004 г.), которые формируют двоичный код суммы двух одноразрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных комбинационных сумматоров, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается сложение трехразрядных двоичных чисел, а также элементный базис, образованный логическими элементами трех типов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип комбинационный сумматор (рис.1.346 на стр.56 в книге Шило В.Л. Популярные цифровые микросхемы: Справочник. - М: Радио и связь, 1988 г.), который содержит элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и формирует двоичный код суммы двух одноразрядных двоичных чисел, задаваемых двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не допускается сложение трехразрядных двоичных чисел.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения формирования двоичного кода суммы двух трехразрядных двоичных чисел, задаваемых двоичными сигналами, при сохранении элементного базиса прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в комбинационном сумматоре, содержащем элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, особенность заключается в том, что в него дополнительно введены семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и пять элементов И, причем первый и второй входы i-го

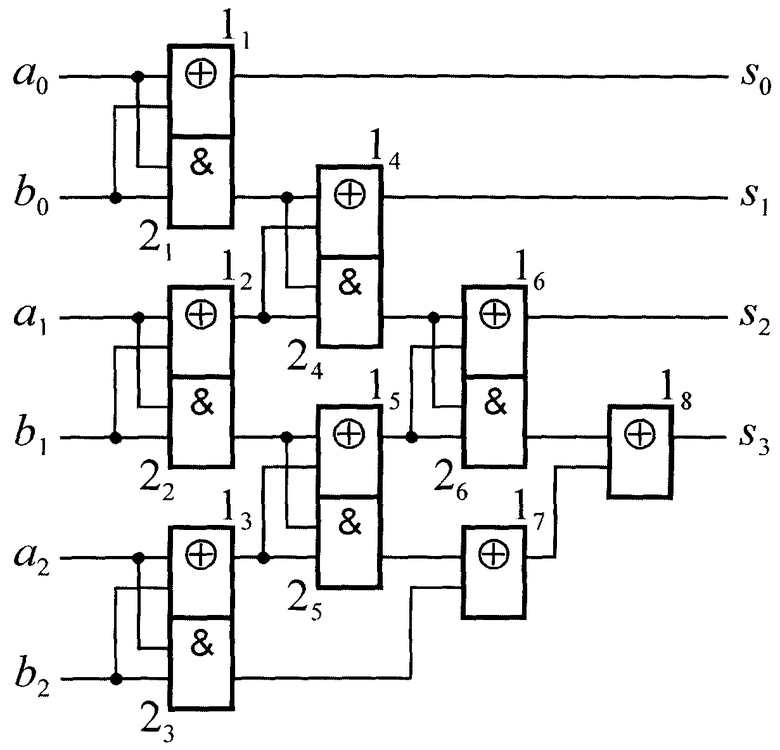

На чертеже представлена схема предлагаемого комбинационного сумматора.

Комбинационный сумматор содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 11, …,18 и элементы И 21, …, 26, причем первый и второй входы элемента 2i

Работа предлагаемого комбинационного сумматора осуществляется следующим образом. На его первый, второй, третий и четвертый, пятый, шестой входы подаются соответственно двоичные сигналы a 0, a 1, a 2∈{0,1} и b0, b1, b2∈{0,l}, которые задают трехразрядные двоичные числа A=a 2 a 1 a 0, B=b2b1b0 так, что a 2, b2 и a 0, b0 есть старшие и младшие разряды соответственно. В представленной ниже таблице приведены значения действующих на выходах предлагаемого сумматора сигналов s0,s1,s2,s3 для всех возможных наборов значений сигналов a 0, a 1, a 2, b0, b1, b2.

Таким образом, на выходах предлагаемого сумматора получим четырехразрядное двоичное число S=s3s2s1s0=A+B.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый комбинационный сумматор построен в элементном базисе прототипа и обладает более широкими по сравнению с прототипом функциональными возможностями, поскольку формирует двоичный код суммы двух трехразрядных двоичных чисел, задаваемых двоичными сигналами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1982 |

|

SU1023315A1 |

| Устройство для программного управления шаговым двигателем | 1986 |

|

SU1352463A1 |

| СПОСОБЫ ПЕРЕДАЧИ ДЛЯ CCFI/PCFICH В СИСТЕМЕ БЕСПРОВОДНОЙ СВЯЗИ | 2008 |

|

RU2444134C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ДАННЫХ С ИСПРАВЛЕНИЕМ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ И ОБНАРУЖЕНИЕМ ОШИБОК В БАЙТАХ ИНФОРМАЦИИ | 2011 |

|

RU2448359C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2022 |

|

RU2789750C1 |

| Суммирующее устройство | 1987 |

|

SU1451681A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 2011 |

|

RU2516528C2 |

| @ -Разрядный счетчик в коде Грея | 1982 |

|

SU1070695A1 |

| УСТРОЙСТВО ХРАНЕНИЯ И ПЕРЕДАЧИ ИНФОРМАЦИИ С ОБНАРУЖЕНИЕМ ДВОЙНЫХ ОШИБОК | 2009 |

|

RU2403615C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой вычислительной техники как средство арифметической обработки дискретной информации. Техническим результатом является обеспечение формирования двоичного кода суммы двух трехразрядных чисел, задаваемых двоичными сигналами. Устройство содержит восемь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и шесть элементов И. 1 ил., 1 табл.

Комбинационный сумматор, содержащий элемент И, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и отличающийся тем, что в него дополнительно введены семь элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и пять элементов И, причем первый и второй входы i-го

| М-разрядный комбинационный сумматор | 1988 |

|

SU1580348A1 |

| М-разрядный комбинационный сумматор | 1988 |

|

SU1580349A1 |

| Комбинационный сумматор | 1988 |

|

SU1589269A1 |

| СУММАТОР КОМБИНАЦИОННОГО ТИПА | 2004 |

|

RU2275676C1 |

| US 6199090 B1, 06.03.2001 | |||

| JP 8212057 A, 20.08.1996 | |||

| US 2009204659 A1, 13.08.2009 | |||

| KR 20040091849 A, 02.11.2004 | |||

Авторы

Даты

2014-05-10—Публикация

2013-02-01—Подача