Изобретение относится к области вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в других устройствах цифровой автоматики.

Известен сумматор комбинационного типа, см., например, М.А.Карцев Арифметика цифровых машин, М., 1969, изд. Наука, стр.147-156, рис.2-8, 2-9, 2-10. Недостатком известных сумматоров этого типа является наличие в каждом разряде трех RS-триггеров, что определяет время выполнения операции сложения, требуемое оборудование, потребление электроэнергии и стоимость устройства в целом.

Наиболее близким аналогом, принятым за прототип, является объект а.с. 1418705, прототип устраняет ряд недостатков известных объектов. Он содержит только два RS-триггера в каждом разряде и выполняет операцию сложения за два временных такта (под тактом понимается время, равное длительности исполнительного импульса или паузы между импульсами). В известных устройствах аналогичного назначения время сложения равно трем тактам. Однако прототип имеет ряд недостатков, которые мешают его широкому применению. Основным недостатком является одна выполняемая арифметическая операция (сложение) и большая временная задержка сигнала переноса, достигающая 3nt, здесь n - число разрядов, t - задержка сигнала при прохождении через один элемент И (ИЛИ). Задачей изобретения является расширение перечня выполняемых операций и повышение быстродействия выполнения арифметических и логических операций при минимальных затратах аппаратных средств. Для чего предложен объект, выполненный на основе логических элементов И, ИЛИ, НЕ, содержащий в каждом разряде первый и второй RS-триггера, первый, второй, третий и четвертый элемент И, первый и второй элемент ИЛИ, первый, второй и третий элементы НЕ, причем в каждом разряде вторые входы первого и второго элементов И связаны с входом разрешения сложения, первые входы этих элементов соединены с входом и выходом первого элемента НЕ соответственно, третий вход первого элемента И подключен к выходу третьего элемента НЕ, выход второго элемента И соединен с входом второго элемента НЕ, первые входы первого элемента ИЛИ и третьего элемента И соединены с входом переноса из младшего разряда, выходы первого и второго элементов ИЛИ соединены с первым и вторым входами четвертого элемента И, выход которого соединен с первым входом первого элемента И и входом первого элемента НЕ, отличающийся тем, что в каждый разряд устройства введены первый, второй, третий и четвертый входы управления, пятый, шестой и седьмой элементы И, третий и четвертый элементы ИЛИ и четвертый элемент НЕ, при этом единичный выход первого триггера соединен с первым входом пятого элемента И, второй его вход связан с третьим входом управления, выход упомянутого элемента И соединен с первым входом третьего элемента ИЛИ, с вторым входом третьего элемента И, с первым входом второго элемента ИЛИ и с первым входом седьмого элемента И, второй вход третьего элемента ИЛИ подключен к входу переноса из младшего разряда, а выход его соединен с третьим входом второго элемента И, выход которого через второй элемент НЕ соединен с S-входом второго триггера и с первым входом шестого элемента И, выход первого элемента И соединен с входом четвертого элемента НЕ и с вторым входом четвертого элемента ИЛИ, первый вход этого элемента ИЛИ подключен к единичному выходу второго триггера, а его выход соединен с вторым входом шестого элемента И, выход которого подключен к вторым входам второго элемента ИЛИ и седьмого элемента И, выход седьмого элемента И соединен с вторым входом первого элемента ИЛИ, а выход четвертого элемента НЕ подключен к R-входу второго триггера, кроме того, первый и второй входы управления соединены с вторыми входами первого и второго элементов И, четвертый вход управления подключен к третьему входу четвертого элемента И, в его каждый разряд введен пятый элемент ИЛИ, первый вход которого соединен с выходом четвертого элемента И, второй вход подключен к выходу седьмого элемента И, а выход пятого элемента ИЛИ соединен с первым входом первого элемента И и с входом первого элемента НЕ; в каждый разряд введен шестой элемент ИЛИ, пятый и шестой входы управления, при этом пятый вход управления подключен к первому входу введенного элемента ИЛИ, его второй вход связан с выходом пятого элемента И, выход шестого элемента ИЛИ подключен к первому входу седьмого элемента И, а шестой вход управления соединен с третьим входом третьего элемента ИЛИ; в каждый разряд введены седьмой элемент ИЛИ и седьмой вход управления, при этом первый вход седьмого элемента ИЛИ связан с седьмым входом управления, второй вход этого элемента ИЛИ соединен с входом переноса из младшего разряда, выход седьмого элемента ИЛИ соединен с первым входом третьего элемента И, кроме того, седьмой вход управления связан с третьим входом пятого элемента ИЛИ, выход шестого элемента ИЛИ соединен с первым входом седьмого элемента И и с вторым входом третьего элемента И.

Покажем, что позволяет получить каждый из основных отличительных признаков объекта.

1. Включение в состав оборудования третьего элемента ИЛИ и шестого элемента И, связей с выхода первого элемента И через четвертый элемент ИЛИ с вторым входом шестого элемента И и связи с выходом второго элемента НЕ с первым входом шестого элемента И обеспечивают истинное значение сформированного сигнала переноса при переключении второго триггера, что позволяет исключить из оборудования третий RS-триггер и выполнять операцию сложения за два временных такта. По первому такту формируется максимальный по времени перенос, по второму такту - занесение суммы во вторые триггеры.

2. Включение в состав каждого разряда пятого элемента ИЛИ и связей с выходов четвертого и седьмого элементов И с входами упомянутого элемента ИЛИ и подключение выхода этого элемента ИЛИ к входам ИЗ и НЕ 20 обеспечивает выполнение операции сложения по модулю два.

3. Включение в состав каждого разряда шестого элемента ИЛИ, пятого и шестого входов управления с соответствующими связями обеспечивает выполнение операции инвертирования кода второго триггера.

4. Включение в состав каждого разряда седьмого и восьмого входов управление с соответствующими связями обеспечивает выполнение операций логического умножения и логического сложения.

5. Связь с выхода шестого элемента ИЛИ с вторым входом третьего элемента И обеспечивает выполнение операции сдвига кода влево.

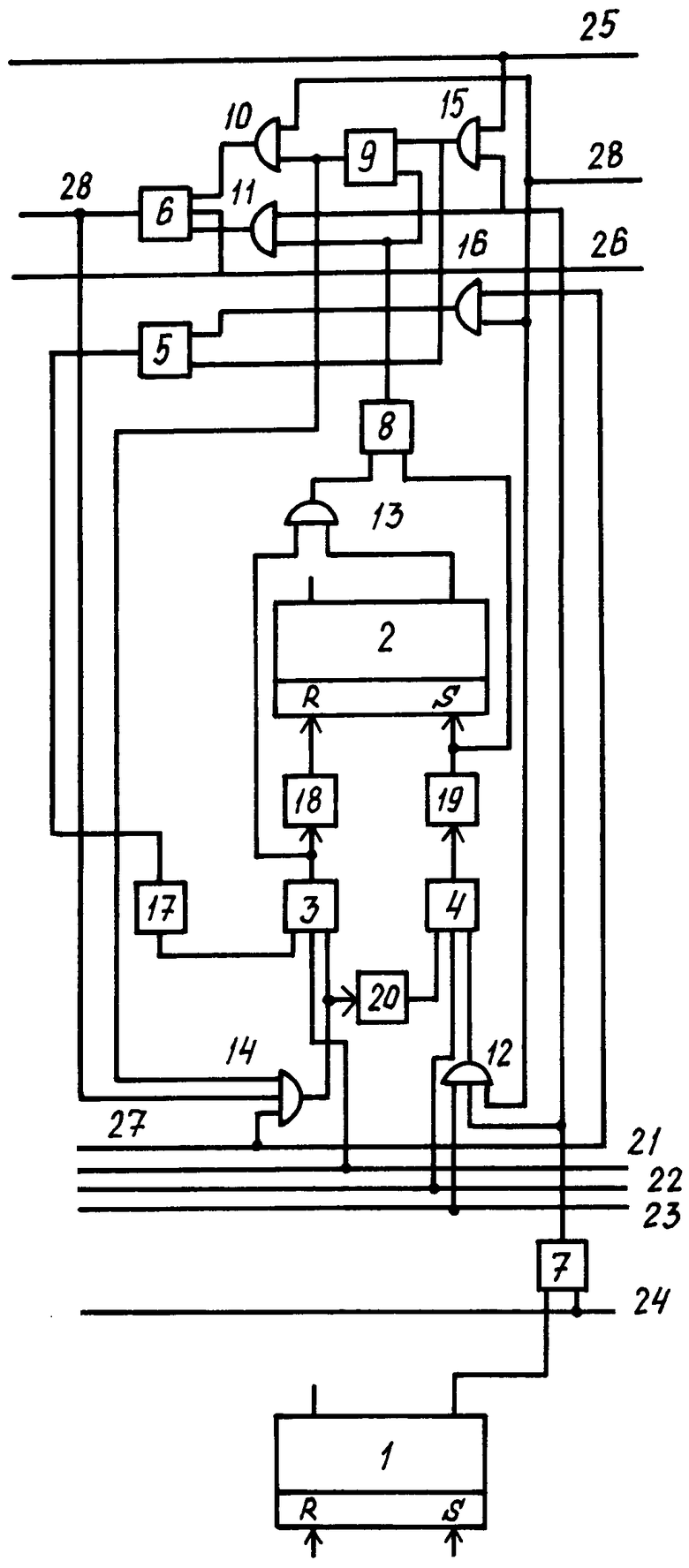

Предлагаемый объект позволяет расширить перечень выполняемых операций по сравнению с прототипом в шесть раз (дополнительно выполняются операции сложения по модулю два, инвертирование, логическое сложение, логическое умножение, сдвиг кода влево), повысить быстродействие выполнения операций сложения (вычитания) за счет сокращения числа тактов с трех до двух и меньшей задержки сигналов в цепи сквозного переноса с 3tn до 2tn при минимальных затратах дополнительного оборудования. Для пояснения работы на чертеже, приведена функциональная схема одного разряда предлагаемого объекта. На чертеже приняты следующие обозначения: RS-триггеры 1, 2, логические элементы И 3-9, логические элементы ИЛИ 10-16, логические элементы НЕ 17-20, импульсный вход установки триггера в "нуль" 21, импульсный вход установки триггера в "единицу" 22, потенциальный вход инвертирования 23, вход выдачи кода первого триггера 24, вход разрешения операций инвертирования и сдвига 25, вход запрета переноса 26, вход операции логического умножения 27, вход переноса из младшего разряда 28. Предложенный объект осуществляется следующим образом. До начала выполнения операций в RS-триггерах 1, 2 хранятся коды второго и первого слагаемых соответственно. Единичный выход триггера 1 соединен с выходом И7, второй выход этого элемента связан с входом 24. Выход И7 соединен с входами ИЛИ 12, 11, 15. Вход 21 подключен к входу И3, первый и третий входы И3 соединены с выходами ИЛИ14, НЕ17. Выход И3 соединен с входами НЕ18, ИЛИ13. Выход НЕ18 подключен к R-входу триггера 2. Вход 22 соединен с входом И4. Первый и третий его входы связаны с выходами НЕ20, ИЛИ12. Выход И4 через НЕ19 соединен с S- входом триггера 2 и с входом И8.

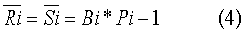

Единичный выход триггера 2 через ИЛИ 13 соединен с входом И8, выход которого подключен к входам ИЛИ11, И9. Первой и второй входы ИЛИ10 связаны с входом 28 и с выходом И9. Выходы ИЛИ10, 11 соединены в входами И6. Третий вход И6 связан с входом управления 26. Выход упомянутого И6 является шиной переноса в старший разряд и соединен с входом ИЛИ14 i-го разряда. Выход И9 подключен к второму входу ИЛИ14, третий вход этого элемента соединен с входом 27. Вход управления 25 подключен к входу ИЛИ15, выход которого соединен с вторыми выходами И9, И5. Выход И5 соединен с входом НЕ17. Вход управления 23 соединены с третьим входом ИЛИ12. Выход ИЛИ16 соединен с первым входом И5. В статике до начала выполнения операций на входах управления 21-27 и на входе 28 отсутствуют высокие потенциалы. С выходов элементов НЕ17-20 на управляемые ими входы поступают высокие потенциалы. Рассмотрим работу объекта при выполнении операций.

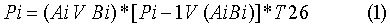

1. Операция сложения. Будем считать, что до начала выполнения операции коды слагаемых хранятся в триггерах 1, 2. Операция выполняется за два временных такта. На это время по входам 24 и 26 подаются высокие потенциалы, разрешающие выдачу второго слагаемого из первого триггера на схемы формирования суммы и разрешающие работу И6. По первому временному такту формируется максимальный потенциал сквозного переноса согласно соотношению

здесь Pi - перенос, выработанный в i - том разряде.

Pi-1 перенос i-1-го разряда.

Ai - первое слагаемое (триггер 2),

Bi - второе слагаемое (триггер 1),

Т - потенциал разрешения формирования переносов (шины 26).

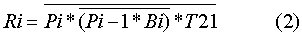

По второму временному такту сформированный в каждом разряде потенциал переноса разрешает прохождение импульсов формирования суммы на R-вход или на S-вход триггера 2. Прохождение импульсов, поступающих по входам 21 и 22, на R и S входы обеспечивается при выполнении следующих логических соотношений

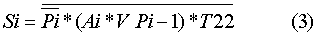

При выполнении второго такта операции сформированный потенциал переноса в каждом разряде искусственно поддерживается, независимо от переключения триггера 2. Эта функция, соответствующая временной задержке переключения триггера, выполняется следующим образом. При установке второго триггера в "нуль" импульс по цепи элементов И1, ИЛИ13, И8 поступает на вторые входы элементов ИЛИ11, И9 и поддерживает потенциал сформированного переноса при переключении триггера 2 из "единицы" в "нуль". Если триггер 2 переключается в "единицу", то исполнительный импульс по цепи вход 22, И4, НЕ 19, И8 запрещает работу И8 и препятствует возникновению ложного сигнала переноса. Заметим, что при формировании суммы состояние триггера 2 не меняется, если выполняется соотношение

При этом запрет прохождения импульсов на входы триггера выполняется за счет прохождения потенциала переноса по цепи входа 28, ИЛИ16, И5, НЕ17 и прохождение потенциала второго слагаемого по цепи вход 24, И7, ИЛИ15, И5. По истечении второго временного такта в триггерах 2 будет сформирован результат суммирования кодов двух чисел.

2. Операция вычитания. Выполняется аналогично рассмотренной операции. Отличие только в том, что второе слагаемое выдается инверсным кодом.

3. Операция инвертирования. При ее выполнении на входы 25 и 23 поступают высокие потенциалы. Если триггер 2 хранит "единицу", то высокий потенциал по цепи ИЛИ13, И8, И9, ИЛИ14 поступает на вход И3. Одновременно на входы 21 и 22 подаются исполнительные импульсы, которые приходят на R-вход, если триггер до выполнения операции хранил "единицу", и на S-вход если раньше триггер хранил код "нуля". На этом операция завершается.

4. Операция сложения по модулю два. Выполняется за один временной такт. Для ее выполнения на вход 24 подается высокий потенциал. Если в триггерах 1 и 2 хранятся коды "единицы", то высокий потенциал с триггера 1 по цепи И7, ИЛИ15 и с триггера 2 по цепи ИЛИ13, И8 поступают на входы И9 и далее через ИЛИ14 на вход И3. Исполнительный импульс, поступивший по входам 21 и 22, установит триггер в "нуль". Если первое слагаемое равно "нулю", а второе - "единица", то исполнительный импульс по цепи вход 23, И4, НЕ 19 поступит на S-вход триггера 2, так как на втором и третьем входах И4 присутствуют высокие потенциалы с НЕ20 и поступивший по цепи триггера 1, И7, ИЛИ12. На этом операция завершается. Для ее выполнения не требуется дополнительного оборудования.

5. Операция логического сложения. Выполняется за один такт. Для ее выполнения на вход 24 подается высокий потенциал, который, в случае кода "единицы" второго слагаемого по цепи И7, ИЛИ12 поступает на вход И4. Одновременно по входу 22 поступает исполнительный импульс, который по цепи И4, НЕ19 поступит на S-вход триггера 2. На этом операция завершается. Дополнительное оборудование не требуется.

6. Операция логического умножения. Операция выполняется за один временной такт. Для ее выполнения на входы 24 и 27 подаются высокие потенциалы. Если второй сомножитель равен "единице", то высокий потенциал с выхода И7, ИЛИ15, И5, НЕ17 запретит прохождение исполнительного импульса с входа 21 через И3, НЕ18 на R-вход триггера 2. На этом операция завершается.

7. Операция сдвига кода влево. Для выполнения этой операции требуется два временных такта для сдвига кода на один разряд. На время выполнения операции по входам 25 и 26 поступают высокие потенциалы. Если триггер 2 i-го разряда хранит код "единицы", а в i-1 разряде триггер 2 хранит код "нуля", то исполнительный импульс, поступивший одновременно по входам 21, 22 пройдет по цепи И3, НЕ18 на R-вход триггера, так как на первом и третьем входах И3 присутствуют высокие потенциалы, поступающие с выхода И6 через ИЛИ14 и с выхода НЕ17. Если в i-том и i-1-ом разрядах хранится код "единицы", то триггер i-того разряда после поступления исполнительного импульса сохранит свое состояние за счет запрета работы элемента И3 низким потенциалом с выхода НЕ17. При этом перенос из младшего разряда проходит по цепи вход 28, ИЛИ16 на первый вход И5. На второй вход поступает потенциал с входа 25, ИЛИ15. Второй такт (пауза) используется для подготовки объекта к прохождению нового импульса сдвига. Сдвиги кода будут производится до тех пор, пока будут поступать исполнительные импульсы по входам 21, 22. Для выполнения операции сдвига влево не требуется дополнительного оборудования.

Таким образом, предлагаемый объект позволяет повысить быстродействие выполнения операции сложения (вычитания) и расширить перечень выполняемых операций в шесть раз при минимальных затратах аппаратных средств.

| название | год | авторы | номер документа |

|---|---|---|---|

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия и расширение перечня арифметических и логических операций, выполняемых устройством, при минимальных затратах оборудования. Устройство содержит два RS-триггера, семь элементов И, семь элементов ИЛИ, четыре элемента НЕ, семь шин управления, шину переноса. 1 ил.

Сумматор комбинационного типа, выполненный на основе логических элементов И, ИЛИ, НЕ, содержащий в каждом разряде два RS-триггера, четыре элемента И, два элемента ИЛИ, три элемента НЕ, причем в каждом разряде первые входы первого и второго элементов И соединены с входом и выходом первого элемента НЕ соответственно, третий вход первого элемента И подключен к выходу третьего элемента НЕ, выход второго элемента И соединен с входом второго элемента НЕ, первый вход первого элемента ИЛИ соединен с шиной переноса из младшего разряда, выходы первого и второго элементов ИЛИ соединены с первым и вторым входами четвертого элемента И, выход которого является шиной переноса в старший разряд, отличающийся тем, что в каждый разряд введены семь шин управления, пятый, шестой и седьмой элементы И, третий, четвертый, пятый, шестой и седьмой элементы ИЛИ и четвертый элемент НЕ, при этом единичный выход первого триггера, в котором хранится код второго слагаемого, соединен с первым входом пятого элемента И, второй вход которого связан с третьей шиной управления, выход пятого элемента И соединен с первым входом третьего элемента ИЛИ, с первым входом второго элемента ИЛИ, со вторым входом шестого элемента ИЛИ, первый вход которого соединен с пятой шиной управления, на которую подается сигнал, разрешающий выполнение операций инвертирования и сдвига кода, выход упомянутого элемента ИЛИ соединен с первым входом седьмого элемента И и вторым входом третьего элемента И, первый вход которого соединен с выходом седьмого элемента ИЛИ, второй вход которого соединен с шиной переноса из младшего разряда и со вторым входом третьего элемента ИЛИ, третий вход которого соединен с шестой шиной управления, на которую подается высокий потенциал для выполнения операции инвертирования, выход третьего элемента ИЛИ соединен с третьим входом второго элемента И, второй вход которого соединен со второй шиной управления, на которую подается сигнал установки триггера в "1", первая шина управления, на которую подается сигнал установки триггера в "0", соединена со вторым входом первого элемента И, выход которого соединен со вторым входом четвертого элемента ИЛИ и с входом четвертого элемента НЕ, выход которого соединен с R-входом второго триггера, S-вход которого соединен с выходом второго элемента НЕ и с первым входом шестого элемента И, выход второго триггера соединен с первым входом четвертого элемента ИЛИ, выход которого соединен со вторым входом шестого элемента И, выход которого соединен со вторым входом второго элемента ИЛИ и со вторым входом седьмого элемента И, выход которого соединен со вторым входом первого элемента ИЛИ и со вторым входом пятого элемента ИЛИ, первый вход которого соединен с выходом четвертого элемента И, третий вход пятого элемента ИЛИ соединен с седьмой шиной управления, на которую подается высокий потенциал для выполнения операции логического умножения, и с первым входом седьмого элемента ИЛИ, выход пятого элемента ИЛИ соединен с первым входом первого элемента И, выход третьего элемента И соединен с входом третьего элемента НЕ, третий вход четвертого элемента И соединен с четвертой шиной управления, являющейся шиной запрета переноса.

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| ЦИФРОВОЙ СУММАТОР | 1994 |

|

RU2099776C1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| US 5691931 А, 25.11.1995 | |||

| 1972 |

|

SU416869A1 | |

Авторы

Даты

2006-04-27—Публикация

2004-12-16—Подача