Изобретение относится к области автоматики и вычислительной техники и может быть использовано для связи цифровых вычислительных устройств с аналоговыми устройствами.

Известен формирователь временных интервалов, содержащий последовательно соединенные генератор импульсов, делитель частоты, формирователь питания, блок фазовращателей и два блока формирователей импульсов [1]. Недостатком известного устройства является его сложность, связанная с необходимостью использования высокоточного фазовращателя и устройства для его установки.

Наиболее близким техническим решением к данному изобретению является формирователь временных интервалов в устройстве для проверки многоотсчетных преобразователей временных интервалов в код. В известном устройстве для формирования временных интервалов используется блок программируемых периферийных адаптеров, выходы которого подключены к информационным входам блока регистров, выходы блока регистров подключены к одной группе входов блока цифровых компараторов, выходы которого подключены к входам блока формирователей импульсов и через блок дешифраторов - к управляющим входам блока регистров. Выход генератора импульсов подключен к входу делителя частоты, выходы разрядов которого подключены к другой группе входов блока цифровых компараторов [2].

В известном устройстве изменение формируемых временных интервалов осуществляют путем изменения входной информации блока регистров в каждом периоде временной развертки делителя частоты. При этом обновление информации в блоке программируемых периферийных адаптеров производится в первой половине развертки делителя частоты, а моменты перезаписи обновленной информации из блока программируемых адаптеров в блок регистров перемещаются в зависимости от положения выходных импульсов блока формирователей импульсов относительно временной развертки делителя частоты. Для исключения сбоев при обновлении информации в блоке регистров и для обеспечения постоянства заданной дискретности изменения временных интервалов при неограниченном количестве циклов перемещения выходных импульсов относительно периода временной развертки делителя частоты в динамическом режиме работы в известном устройстве предназначен блок дешифраторов и задействован сложный алгоритм вычисления приращений. Блок регистров при этом выполняет функцию буфера. Таким образом, недостатком известного формирователя временных интервалов является его сложность.

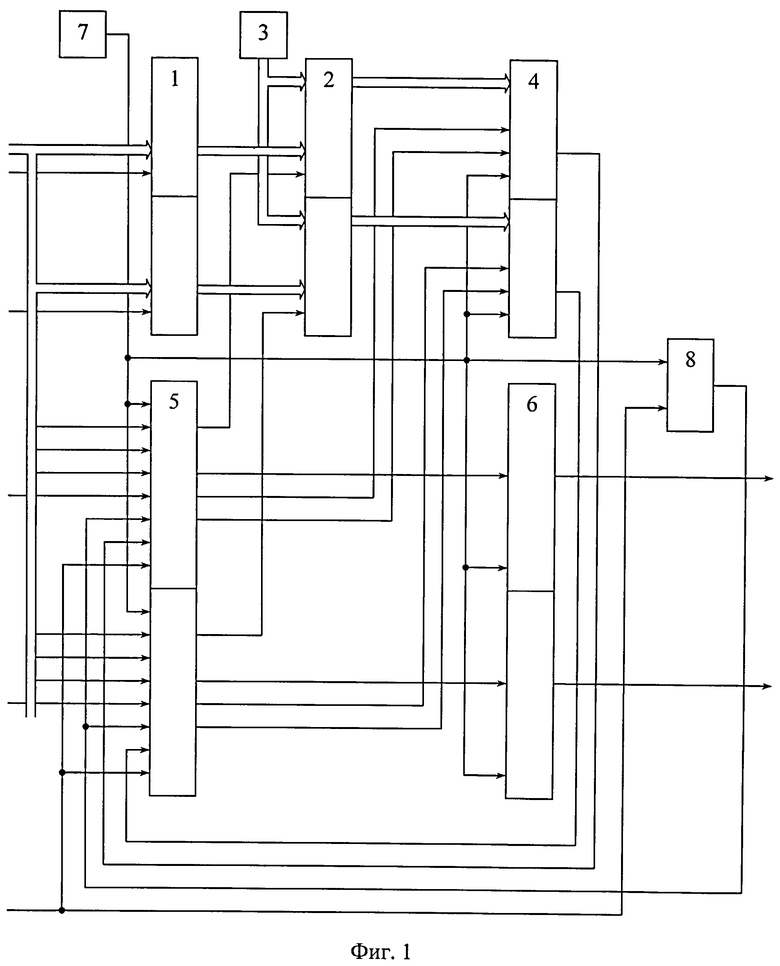

Структурная схема предложенного формирователя временных интервалов представлена на фиг.1, а структурные схемы входящих в его состав формирователей команд и формирователей импульсов представлены соответственно на фиг.2 и фиг.3.

Формирователь временных интервалов (фиг.1) содержит блок 1 регистров, выходы которого подключены к одним группам входов блока 2 коммутаторов. Другие группы входов блока 2 соединены с выходами блока 3 памяти, а выходы блока 2 подключены к информационным входам блока 4 делителей частоты. Выходы блока 4 подключены к первым управляющим входам блока 5 формирователей команд. Информационные входы блока 1 и блока 5 подключены к шине данных. Входы синхронизации блока 1 и блока 5 подключены к входам синхронизации формирователя временных интервалов. Первые выходы блока 5 подключены к управляющим входам блока 2, а вторые и третьи выходы блока 5 подключены соответственно к информационным входам блока 6 формирователей импульсов и к управляющим входам блока 4. Выход генератора 7 импульсов подключен к тактовым входам блоков 4, 5, 6 и делителя 8 частоты. Выход делителя 8 подключен ко вторым управляющим входам блока 5. Вход сброса формирователя временных интервалов подключен к входам сброса блока 5 и делителя 8. Выходы сброса блока 5 подключены к входам сброса блока 4. Выходы блока 6 являются выходами формирователя временных интервалов.

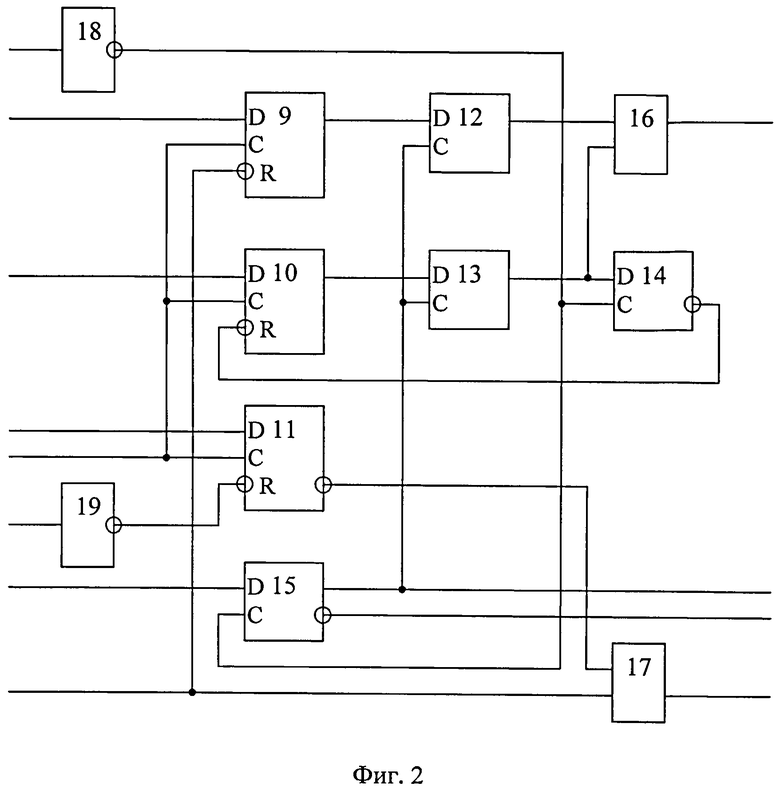

Формирователь команд (фиг.2) блока 5 содержит семь триггеров с 9-го по 15-й, два элемента 16 и 17 ИЛИ и два инвертора 18 и 19. Информационные входы первого 9, второго 10 и третьего 11 триггеров являются информационными входами формирователя команд, а входы синхронизации этих триггеров являются входом синхронизации формирователя команд. Выходы триггеров 9 и 10 подключены к информационным входам соответственно четвертого 12 и пятого 13 триггеров, выходы которых подключены к входам первого элемента 16 ИЛИ. Выход элемента 16 ИЛИ является первым выходом формирователя команд. Выход триггера 13 подключен к информационному входу шестого триггера 14, инверсный выход которого подключен к входу сброса триггера 10. Информационный вход седьмого триггера 15 является первым управляющим входом формирователя команд. Прямой выход триггера 15 подключен к входам синхронизации триггеров 12 и 13. Вход первого инвертора 18 является тактовым входом формирователя команд. Выход инвертора 18 подключен к входам синхронизации триггеров 14 и 15. Вход второго инвертора 19 является вторым управляющим входом формирователя команд. Выход инвертора 19 подключен к входу сброса триггера 11. Вход сброса триггера 9 является входом сброса формирователя команд и подключен к одному входу второго элемента 17 ИЛИ, другой вход которого соединен с инверсным выходом триггера 11. Прямой и инверсный выходы триггера 15 и выход элемента 17 ИЛИ являются соответственно вторым, третьим выходами и выходом сброса формирователя команд.

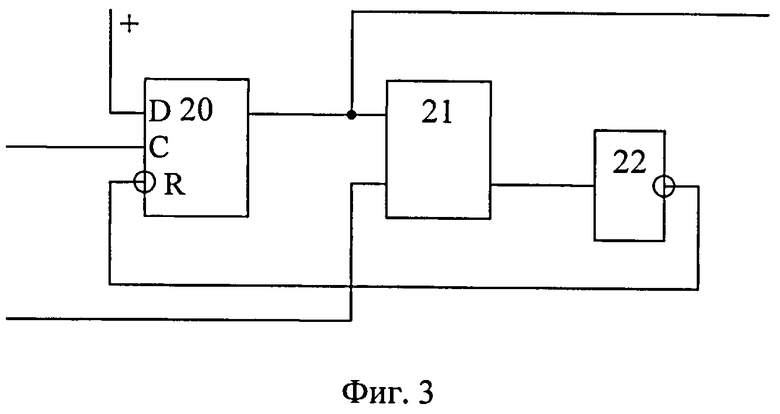

Формирователь импульсов (фиг.3) блока 6 содержит триггер 20, делитель 21 частоты и инвертор 22. Вход синхронизации триггера 20 и тактовый вход делителя 21 являются соответственно управляющим и тактовым входами формирователя импульсов. Выход триггера 20 подключен к управляющему входу делителя 21, выход которого через инвертор 22 подключен к входу сброса триггера 20. Информационный вход триггера 20 подключен к шине питания, а выход триггера 20 является выходом формирователя импульсов.

Устройство, представленное на фиг.1, содержит два регистра в блоке 1, два коммутатора в блоке 2, два делителя частоты в блоке 4 и по два формирователя в блоках 5 и 6. Такое устройство формирует одну последовательность временных интервалов между старт- и стоп-импульсами с выходов двух формирователей импульсов блока 6. Изменение длительности временных интервалов осуществляют смещением по фазе старт- и стоп-импульсов путем изменения коэффициентов передачи соответствующих делителей блока 4. Коэффициенты передачи задают с помощью регистров блока 1. Коммутатор 2 переключает коэффициенты передачи. Блок 5 формирует команды управления работой устройства в двух режимах: статический, динамический. Блок 6 предназначен для формирования длительности выходных старт- и стоп-импульсов.

По импульсу сброса делители частоты блока 4 и делитель 8 устанавливаются в 0 и при нулевых сигналах на входах триггеров 9, 10 и 11 работают синхронно и синфазно. Выходным импульсом переполнения делителя блока 4, задержанным триггером 15 на половину периода ТГИ следования импульсов генератора 7, устанавливаются в нулевое состояние триггеры 10 и 11. Единичный потенциал с выхода элемента 13 разрешает прохождение через коммутатор 2 исходного кода (например, 1 в старшем разряде и 0 во всех остальных разрядах) с выходов блока 3 на информационные входы делителей блока 4. Во время отрицательного импульса с инверсного выхода триггера 15 выходной код блока 3 записывается в соответствующий делитель блока 4. Процесс записи выходного кода блока 3 в соответствующий делитель блока 4 повторяется при каждом переполнении этого делителя. При этом частота следования импульсов переполнения делителей блока 4 соответствует номинальному значению частоты делителя 8.

По фронту выходного импульса триггера 15 устанавливается в 1 триггер 20 формирователя импульсов блока 6, разрешая делителю 21 счет импульсов генератора 7. Импульсом переполнения делителя 21 триггер 20 сбрасывается в 0. Длительность выходного импульса триггера 16 равна произведению периода ТГИ на коэффициент передачи делителя 17. Триггер 15 в формирователях блока 5 предназначен для подавления помех переходных процессов при формировании импульсов переполнения делителей блока 4. На выходах блока 6 формируются совпадающие по фазе старт- и стоп-импульсы заданной длительности. Формируемый временной интервал равен нулю.

Для работы устройства в динамическом режиме на информационные входы регистров блока 1 подают коды смещения по фазе выходных старт- и стоп-импульсов в каждом периоде их следования. Обычно выбирают код смещения для старт- (стоп-) импульса больше исходного на определенную величину, а для стоп- (старт-) импульса на такую же величину меньше исходного. На информационные входы триггеров 9 подают сигналы 1, а на информационные входы триггеров 10 и 11 подают сигналы 0. Синхроимпульсами заданные коды смещения записываются в соответствующие регистры блока 1, а триггеры 9 устанавливаются в 1. По импульсам переполнения делителей блока 4 устанавливаются в 1 триггеры 12. Единичный сигнал элемента 12 разрешает прохождение кода регистра блока 1 на информационные входы делителя блока 4. При каждом переполнении соответствующего делителя блока 4 отрицательным импульсом с инверсного выхода триггера 15 выходной код регистра блока 1 записывается в соответствующий делитель блока 4. Частота следования выходных импульсов в сторону уменьшения или увеличения по отношению к номинальной частоте делителя 8 определяется величиной и знаком отклонения кода регистра блока 1 от исходного кода блока 3. При работе в динамическом режиме триггеры 10, 11, 13, и 14 остаются в нулевом состоянии. Для перехода из динамического режима в статический необходимо на информационный вход триггера 9 подать сигнал 0 и записать синхросигналом его значение в триггер 9. Накопленный фазовый сдвиг между старт- и стоп-импульсами сохранится. Для продолжения динамического режима следует повторно установить триггер 9 в 1. Накопление фазового сдвига продолжится.

Для сброса в 0 делителей блока 4 необходимо соответствующими сигналами по информационным входам и входам синхронизации установить триггер 11 в 1, а триггеры 9 и 10 в 0. Сигнал сброса с выхода триггера 11 через элемент 17 поступит на входы сброса блока 4. Сигналом переполнения делителя 8 триггер 11 возвращается в 0 и делители блока 4 начинают работу синфазно с делителем 8.

Для работы устройства в режиме единичного сдвига по фазе на информационные входы регистров блока 1 подают коды единичного фазового сдвига соответствующих последовательностей выходных импульсов. На информационные входы триггеров 10 подают сигналы 1, а на триггеры 9 и 11 - сигналы 0. Синхроимпульсом код величины единичного сдвига записывается в соответствующий регистр блока 1, триггер 10 устанавливается в 1, а по импульсу переполнения делителя блока 4 устанавливается в 1 триггер 13. Единичный сигнал элемента 16 разрешает прохождение кода регистров блока 1 на информационные входы делителей блока 4. В текущем импульсе переполнения делителя выходной код регистра блока 1 записывается в соответствующий делитель блока 4.

После установки в 1 триггера 13 устанавливается в 1 и триггер 14 выходным сигналом инвертора 18. Триггер 14 сбрасывает в 0 триггер 10. Следующим сигналом переполнения делителя блока 4, задержанным на 0,5 ТГИ триггером 15, триггер 13 устанавливается в 0. На выходе элемента 16 устанавливается нулевой сигнал и к информационным входам делителя блока 4 подключаются выходы блока 3. Устройство переходит в статический режим работы. Так в устройстве осуществляются единичные сдвиги по фазе выходных сигналов на величины, задаваемые кодами в регистрах блока 1.

Для формирования нескольких временных интервалов необходимо иметь несколько блоков, аналогичных блокам 1, 2, 4 и 6, представленным на фиг.1. Блок 3, генератор 7 и делитель 8 являются общими для формирователя нескольких временных интервалов. Загрузка информации в регистры блока 1 производится последовательно при наличии одной многоразрядной шины данных на все регистры. При этом одна часть блоков устройства может работать в динамическом режиме, а другая часть тех же блоков одновременно может работать в статическом режиме.

Устройство может быть выполнено на программируемых логических интегральных микросхемах (ПЛИС).

Техническим эффектом при использовании предложенного устройства является его программное и аппаратное упрощение. При работе устройства в динамическом режиме нет необходимости вычислять смещение по фазе выходных импульсов в каждом периоде их следования и обновлять при этом содержимое регистров задания кодов смещения.

Источники информации

1. Патент РФ №1807560, кл. Н03М 1/64, 1991 г.

2. Патент РФ №2355105, кл. Н03М 1/10, 2008 г.

Дополнительные источники информации

Патент РФ №2051471, кл. Н03М 1/66, 1995 г.

Патент РФ №2037960, кл Н03М 1/86, 1992 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Многоканальное устройство для формирования временных интервалов | 1980 |

|

SU932603A1 |

| Преобразователь временных интервалов в код | 1985 |

|

SU1305853A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2090840C1 |

| Устройство для измерения временных интервалов | 1986 |

|

SU1368852A1 |

| АКУСТИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЙ | 1994 |

|

RU2099864C1 |

| Приемное стартстопное устройство | 1986 |

|

SU1389007A2 |

| Программное временное устройство | 1990 |

|

SU1762298A1 |

Изобретение относится к области автоматики и вычислительной техники. Технический результат - упрощение конструкции устройства. Формирователь временных интервалов содержит блок регистров, блок коммутаторов, блок памяти, блок делителей частоты, блок формирователей команд, блок формирователей импульсов, генератор импульсов и делитель частоты, при этом формирователь команд блока содержит семь триггеров, два элемента ИЛИ и два инвертора, формирователь импульсов блока содержит триггер, делитель частоты и инвертор. 1 з.п. ф-лы, 3 ил.

1. Формирователь временных интервалов, содержащий блок регистров, блок формирователей импульсов, генератор импульсов, подключенный к входу делителя частоты, отличающийся тем, что в него введены блок делителей частоты, блок коммутаторов, блок формирователей команд и блок памяти, информационные входы блока регистров и блока формирователей команд подключены к шине данных, входы синхронизации блока регистров и блока формирователей команд подключены к входам синхронизации формирователя временных интервалов, выходы блока регистров подключены к одним группам входов блока коммутаторов, другие группы входов которого соединены с выходами блока памяти, а выходы блока коммутаторов подключены к информационным входам блока делителей частоты, первые выходы блока формирователей команд подключены к управляющим входам блока коммутаторов, а вторые и третьи выходы - соответственно к информационным входам блока формирователей импульсов и к управляющим входам блока делителей частоты, выходы которого подключены к первым управляющим входам блока формирователей команд, выход генератора импульсов подключен к тактовым входам блоков формирователей команд, формирователей импульсов и делителей частоты, выход делителя частоты подключен к вторым управляющим входам блока формирователей команд, вход сброса формирователя временных интервалов подключен к входам сброса делителя частоты и блока формирователей команд, выходы сброса которого подключены к входам сброса блока делителей частоты, а выходы блока формирователей импульсов являются выходами формирователя временных интервалов.

2. Формирователь временных интервалов по п.1, отличающийся тем, что каждый из формирователей команд блока формирователей команд содержит семь триггеров, два элемента ИЛИ и два инвертора, информационные входы первого, второго и третьего триггеров являются информационными входами формирователя команд, а входы синхронизации этих триггеров являются входом синхронизации формирователя команд, выходы первого и второго триггеров подключены к информационным входам соответственно четвертого и пятого триггеров, выходы которых подключены к входам первого элемента ИЛИ, выход первого элемента ИЛИ является первым выходом формирователя команд, выход пятого триггера подключен к информационному входу шестого триггера, инверсный выход которого подключен к входу сброса второго триггера, информационный вход седьмого триггера является первым управляющим входом формирователя команд, прямой выход седьмого триггера подключен к входам синхронизации четвертого и пятого триггеров, вход первого инвертора является тактовым входом формирователя команд, выход первого инвертора подключен к входам синхронизации шестого и седьмого триггеров, вход второго инвертора является вторым управляющим входом формирователя команд, выход второго инвертора подключен к входу сброса третьего триггера, вход сброса первого триггера является входом сброса формирователя команд и подключен к одному входу второго элемента ИЛИ, другой вход которого соединен с инверсным выходом третьего триггера, а прямой и инверсный выходы седьмого триггера и выход второго элемента ИЛИ являются соответственно вторым, третьим выходами и выходом сброса формирователя команд.

| ВСЕСОЮЗИАЗ I mmm'iu-i:^iu.,m | 0 |

|

SU364096A1 |

| Формирователь временных интервалов | 1988 |

|

SU1649645A1 |

| Формирователь временных интервалов | 1980 |

|

SU868689A1 |

| Формирователь временных интервалов | 1988 |

|

SU1622926A2 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ МНОГООТСЧЕТНЫХ ПРЕОБРАЗОВАТЕЛЕЙ ВРЕМЕННЫХ ИНТЕРВАЛОВ В КОД | 2008 |

|

RU2355105C1 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2014-09-10—Публикация

2013-04-30—Подача