Изобретение относится к области автоматики и вычислительной техники и может быть использовано для проверки многоотсчетных преобразователей аналоговой величины в код.

Известны устройства для проверки преобразователей временных интервалов в код, содержащие генератор импульсов, счетчик импульсов, выходы которого подключены к дешифратору, группа выходов дешифратора через одновибраторы подключена к первой группе входов первого и второго сумматоров, выходы задатчика кодов подключены к второй группе входов первого сумматора, выходы которого подключены к второй группе входов второго сумматора, третья группа входов которого соединена с выходом проверяемого преобразователя, выходы второго сумматора подключены к группе входов блока элементов И, один вход которого соединен с одним выходом дешифратора, фазовращатель с блоком питания, выходы которых через соответствующие компараторы и элементы И подключены к входам проверяемого преобразователя [1].

В известном устройстве временные интервалы задают с помощью фазовращателей и компараторов, а контрольные коды - с помощью задатчика кодов. Недостатком известного устройства является его сложность, связанная с необходимостью использования высокоточного фазовращателя и невозможностью проверки многоотсчетных преобразователей временных интервалов в код.

Наиболее близким техническим решением к данному изобретению является устройство для проверки многоотсчетных преобразователей временных интервалов в код (в составе преобразователя угла поворота вала в код), содержащее генератор импульсов, подключенный к входу делителя частоты, выходы которого через формирователь питания подключены к входам блока фазовращателей, выходы блока фазовращателей подключены к входам блока формирователей импульсов, выходы которого подключены к одной группе входов проверяемого преобразователя, другая группа входов которого соединена с выходами блока памяти, а выходы подключены к входам вычислительного блока [2].

Блок памяти не входит в состав проверяемого преобразователя и выполнен в виде разъема с перемычками. Запись юстировочных констант (ЮК) в блок памяти производится в технологическом режиме работы проверяемого преобразователя после установки его на объект. ЮК определяются в виде разности согласующих разрядов для каждой пары согласуемых отсчетов, а также отклонения начального кода от нулевого значения в исходном положении. Поскольку фазовращатели на объекте устанавливаются произвольно, то ЮК могут иметь любые значения. Поэтому необходимо проверить целостность всех цепей соединения ответной части разъема блока памяти с другими элементами преобразователя. Однако известное устройство такую проверку не обеспечивает. Задание временных интервалов в известном устройстве осуществляется с помощью блоков фазовращателей и формирователей импульсов. Взаимное смещение начальных установок фазовращателей в известном устройстве не предусмотрено. ЮК в процессе проверки не изменяются, поэтому не проверяется работа преобразователя во всем диапазоне допустимых рассогласований отсчетов.

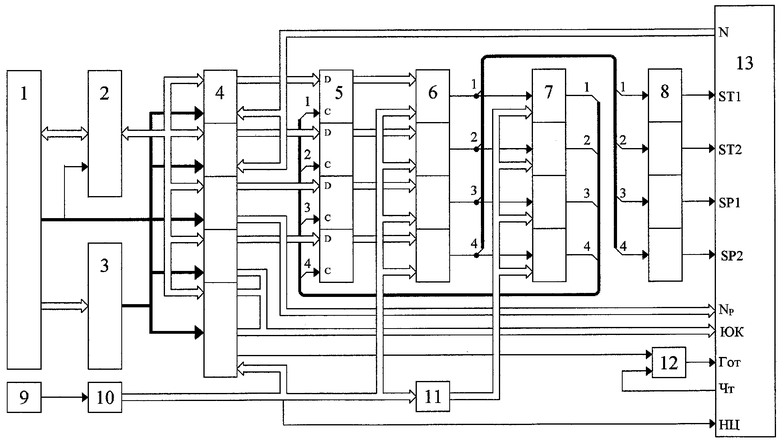

Структурная схема предложенного устройства вместе с проверяемым преобразователем представлена на чертеже. Устройство содержит вычислительный блок 1, шина данных которого соединена с первой группой выводов приемопередатчика 2, управляющие выходы и одна группа адресных выходов вычислительного блока 1 подключены к входам дешифратора 3, выходы которого и другая группа адресных выходов вычислительного блока 1 подключены к управляющим входам приемопередатчика 2 и блока 4 программируемых периферийных адаптеров (ППА), шины данных каждого ППА блока 4 соединены с второй группой выводов приемопередатчика 2. Первая группа выходов портов ППА блока 4 подключена к информационным входам регистров блока 5, выходы которых подключены к одной группе входов блока 6 цифровых компараторов (ЦК). Выход каждого из ЦК блока 6 подключен к одному входу соответствующего дешифратора блока 7 и входу соответствующего формирователя импульсов (ФИ) блока 8. Выход каждого из дешифраторов блока 7 подключен к управляющему входу соответствующего регистра блока 5. Выход генератора 9 импульсов подключен к входу делителя 10 частоты, выходы младших разрядов которого подключены к другой группе входов блока 6 и к входам дешифратора 11. Выходы дешифратора 11 подключены к группе входов каждого из дешифраторов блока 7. Выходы блока 8, вторая и третья группы выходов портов ППА блока 4 подключены соответственно к первой, второй и третьей группам входов проверяемого преобразователя 13. Группа информационных выходов преобразователя 13 и выходы старших разрядов делителя 10 частоты подключены соответственно к одной и другой группам входов портов ППА блока 4. Один выход портов ППА блока 4 и один выход преобразователя 13 подключены соответственно к входам установки и сброса триггера 12, выход которого и выход старшего разряда делителя 10 подключены соответственно к одному и другому входам проверяемого преобразователя 13.

Приемопередатчик 2 предназначен для разгрузки шины данных вычислительного блока 1 и может быть выполнен, например, на стандартных микросхемах типа АП6, ИП6 и др. В качестве ППА могут быть использованы микросхемы типа К580ВВ55 (см., например, Б.М.Каган и др. Основы проектирования микропроцессорных устройств автоматики, М., Энергоатомиздат, 1987, с.166, рис.5.18). Цифровые компараторы могут быть выполнены на микросхемах типа СП1. Формирователи блока 8 могут быть выполнены на одновибраторах или сдвигающих регистрах, тактируемых выходными импульсами генератора 9 и делителя 10. Дешифратор 11 и дешифраторы блока 7 предназначены для синхронизации моментов обновления информации в регистрах блока 5 в зависимости от моментов срабатывания компараторов блока 6. В качестве вычислительного блока 1 может быть использована ПЭВМ, совместимая с IBM PC AT и выше.

Предложенное устройство должно обеспечить формирование на одной группе входов преобразователя 13 совокупности периодически повторяющихся временных интервалов между ST и SP импульсами в соответствии с заданными ЮК, сравнение заданных и выходных ЮК проверяемого преобразователя 13, в технологическом режиме работы преобразователя 13, сравнение в штатном режиме контрольного и выходного кода, полученного в преобразователе 13 с использованием заданных ЮК, на третьей группе входов, в исходном положении, а также при пропорциональном изменении временных интервалов на входах проверяемого преобразователя 13 во всем диапазоне его работы и изменениях ЮК в допустимых пределах.

Технический эффект от использования предложенного устройства заключается в повышении достоверности проверки преобразователя 13.

Код NР режима работы проверяемого преобразователя 13 задается вычислительным блоком 1 и через приемопередатчик 2 и ППА блока 4 передается на вторую группу входов преобразователя 13. Одновременно сигналом с одного выхода блока 4 триггер 12 устанавливается в 1, вырабатывая сигнал готовности (Гот). После прочтения кода режима работы преобразователь 13 вырабатывает сигнал чтения (Чт), сбрасывающий в 0 триггер 12.

Цикл работы преобразователя 13 составляет несколько периодов ST (SP) импульсов. Для формирования вычислительным блоком 1 последовательности сигналов управления работой всего устройства код старших разрядов делителя 10 частоты передается через блок 4 и приемопередатчик 2 в вычислительный блок 1. При этом делитель 10 выполняет функцию таймера для вычислительного блока 1. Для синхронизации работы устройства с проверяемым преобразователем 13 выход старшего разряда делителя 10 передается в качестве сигнала начала цикла (НЦ) в проверяемый преобразователь 13.

В предложенном устройстве ЮК задают исходя из полноты проверки преобразователя 13, например, в виде чередующихся 1 и 0. По заданным ЮК в вычислительном блоке 1 определяют граничные коды временных интервалов для всех отсчетов и запоминают их. При проверке преобразователя 13 в технологическом режиме его работы граничные коды с выходов вычислительного блока 1 через приемопередатчик 2 и ППА блока 4 записывают в соответствующие регистры блока 5.

Генератор 9 работает в непрерывном режиме. На выходах младших разрядов делителя 10, подключенных к группе входов каждого из ЦК блока 6, формируется временная развертка в виде пилообразно изменяющегося кода с периодом Т, равным периоду ST и SP импульсов. При совпадениях выходных кодов младших разрядов делителя 10 с выходным кодом соответствующего регистра блока 5 в ЦК блока 6 формируются импульсы, временное положение каждого из которых относительно начала развертки изменяется в зависимости от кода регистра блока 5. Выходные импульсы ЦК блока 6 в ФИ блока 8 нормализуются по длительности, амплитуде и мощности и в качестве ST и SP импульсов поступают на входы преобразователя 13. Каждая пара ЦК блока 6 вырабатывает ST и SP импульсы для одного из отсчетов преобразователя 13. На выходах N преобразователя 13 формируется код, соответствующий заданным ЮК. Этот код через ППА блока 4 и приемопередатчик 2 поступает на шину данных вычислительного блока 1. В вычислительном блоке 1 принятые из преобразователя 13 коды ЮК сравниваются на соответствие заданным и принимается решение о соответствии норме.

При проверке начального кода преобразователя 13 в штатном режиме его работы входные ST и SP импульсы формируются аналогично технологическому режиму. На выходах N преобразователя 13 формируется полный код N совокупности временных интервалов на первой группе его входов. Для формирования полного кода N в штатном режиме используются значения ЮК на третьей группе входов преобразователя 13. Выходной код N через ППА блока 4 и приемопередатчик 2 поступает в вычислительный блок 1, в котором сравнивается с исходным кодом, и по результатам сравнения принимается решение о соответствии принятого кода N норме.

При проверке преобразователя 13 во всем диапазоне его работы временные интервалы между ST и SP импульсами изменяют пропорционально коэффициентам редукции Р этих отсчетов. Изменение временных интервалов осуществляют путем изменения входной информации регистров блока 5 с выходов вычислительного блока 1 в каждом периоде Т временной развертки делителя 10. При этом в одном из каждой пары регистров блока 5, соответствующих одному отсчету, входной код увеличивается, а в другом уменьшается. В отсчете с самым большим коэффициентом Р изменение кода в каждом периоде Т может составлять одну или несколько единиц младшего разряда в соответствии с заданной программой проверки. Преобразователь 13 проверяют при изменении временных интервалов в обоих направлениях.

С изменением входных временных интервалов изменяется и выходной код N преобразователя 13, который поступает в вычислительный блок 1 и сравнивается с контрольным кодом, соответствующим входным временным интервалам на первой группе входов проверяемого преобразователя 13. При отклонении от нормы в блоке 1 формируется сигнал несоответствия.

Для исключения сбоев при обновлении информации в регистрах блока 5 предусмотрены дешифратор 11 и блок 7 дешифраторов. Дешифратор 11 формирует из выходных сигналов делителя 10 три сигнала: первый - типа «меандр» с периодом Т, смещенный на Т/4 относительно начала временной развертки на входах ЦК блока 6, второй и третий - импульсные сигналы длительностью в один или несколько периодов генератора 9, фронты которых отстоят соответственно на ~5Т/8 и ~7Т/8 от начала временной развертки.

Выходные сигналы дешифратора 11 поступают на входы каждого из дешифраторов блока 7. Если выходные сигналы ЦК блока 6 находятся внутри временного интервала (1/4…3/4)Т развертки, то выходным импульсом соответствующего дешифратора блока 7 является третий выходной импульсный сигнал дешифратора 11, в противном случае - второй импульсный сигнал. По выходному сигналу каждого из дешифраторов блока 7 выходной код ППА блока 4 записывается в соответствующий регистр блока 5. При этом обновление информации в ППА блока 4 производится в первой половине временной развертки делителя 10.

Для проверки преобразователя 13 при возможном рассогласовании его отсчетов в блоке 1 изменяют ЮК смещения отсчетов, сохраняя временные интервалы на входах преобразователя 13 в соответствии с исходными ЮК. Тогда при согласовании отсчетов в преобразователе 13 произойдет смещение кода каждого ТО, а вместе с ним выходного кода N преобразователя 13 и контрольного кода вычислительного блока 1 на величину изменения ЮК. Отклонение выходного кода N преобразователя 13 от контрольного кода во всем диапазоне изменения временных интервалов определяется в вычислительном блоке 1.

Дешифратор 3 предназначен для формирования сигналов управления работой ППА блока 4 и направлением передачи информации приемопередатчика 2. Входными сигналами дешифратора 3 являются сигналы с управляющих и адресных выходов блока 1. Выходы дешифратора 3 подключены к управляющим входам ППА блока 4 и приемопередатчика 2.

Для исключения сбоев работа всех блоков устройства синхронизирована импульсами генератора 9 (на чертеже не представлено).

Определение в вычислительном блоке 1 границ временных интервалов, которые записывают в процессе проверки преобразователя в регистры блока 5, можно производить в последовательности, обратной процессу формирования выходного кода N преобразователя 13 в штатном режиме его работы.

Выходной код N преобразователя 13 в исходном положении должен быть нулевым. Для приведения измеренного кода в исходное положение используют юстировочную константу С0. При проверке преобразователя 13 константу С0 задают исходя из полноты проверки электрических цепей связи с блоком памяти ЮК. Тогда полный многоотсчетный код преобразователя 13 перед его приведением является дополнительным кодом С0 и составляет NП=0-С0.

Код NП можно представить в виде двух отсчетов: согласованного кода NГ старших значащих разрядов грубого отсчета ГО и кода NT точного отсчета ТО, состоящего из кода NC старших согласующих разрядов ГО, смещенного на юстировочную константу C1, и кода NM в младших несмещенных разрядах ТО, т.е. NT=(Nc-C1)+NM.

Если в преобразователе 13 данный ТО представлен кодом NT с числом разрядов n=log2(Т/TГИ) (где ТГИ - период следования импульсов ГИ заполнения временных интервалов в преобразователе 13, Т - период следования ST или SP импульсов) и однозначно определяет величину временных интервалов в диапазоне 0…Т/2, то код NST, записываемый в регистр блока 5 для формирования ST импульса младшего отсчета с наибольшим Р преобразователя 13, может быть произвольным. Код NSP для формирования SP импульса этого отсчета определяется из соотношения NSP=NST-NT.

Если NT имеет число разрядов n+1 и определяет величину временного интервала в диапазоне 0…Т, то NT состоит из двух отсчетов. Старшие n разрядов кода NT представляют собой код NПГ промежуточного ГО с одним старшим значащим разрядом, определяющим номер полпериода (0…Т/2 или Т/2…Т), и остальными согласующими, в старших из которых записан код NПС согласующих разрядов промежуточного ГО. Младшие n разрядов кода NT являются кодом NПТ промежуточного ТО (для диапазона 0…Т/2), смещенным на юстировочную константу С2 относительно кода NПС, т.е. NПТ=(NПС-С2)+NM. В этом случае коды NST и NSP, записываемые в регистр блока 5 для формирования ST и SP импульсов младшего отсчета преобразователя 13, определяются из соотношений:

NST=[NT/2],

NSP=NST-NПТ, где […] - целая часть числа.

Для определения кодов NST и NSP соседнего старшего (j-1) отсчета необходимо вычислить полный код NП(j-1) этого отсчета, исключив младший j отсчет

NП(j-1)=[(Pj-1/Pj)×NПj],

где Pj, Pj-1 - коэффициенты редукции соответствующих отсчетов,

NПj - полный код младшего отсчета.

После этого с кодом NП(j-1) проделывают все описанные выше операции по нахождению NST и NSP. Так последовательно можно определить коды NST и NSP исходного положения для всех отсчетов.

После проверки преобразователя 13 с первым набором ЮК (например, чередующиеся 1 и 0 с 1 в старшем разряде) изменяют ЮК на инверсные, определяют новые значения исходных NST и NSP для всех отсчетов и повторяют частично или полностью весь цикл проверок.

Источники информации

1. Авторское свидетельство СССР №1275765, кл. Н03М 1/10, 1985.

2. Патент РФ №1807560, кл. Н03М 1/64,1991.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРОВЕРКИ МНОГООТСЧЕТНЫХ ПРЕОБРАЗОВАТЕЛЕЙ ВРЕМЕННЫХ ИНТЕРВАЛОВ В КОД | 2007 |

|

RU2349029C1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В КОД | 2013 |

|

RU2534971C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДВИЖЕНИЯ ТРАНСПОРТНЫХ СРЕДСТВ | 1992 |

|

RU2054198C1 |

| Устройство для программного управления синхронно-асинхронными приемопередатчиками | 1982 |

|

SU1043649A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ В ЦИФРОВОЙ КОД ОТКЛОНЕНИЯ | 1992 |

|

RU2074396C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВЛЯЮЩЕЙ СПОСОБНОСТИ ПРИЕМНИКОВ ДИСКРЕТНЫХ СИГНАЛОВ | 1992 |

|

RU2040118C1 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для определения взаимных корреляционных функций | 1981 |

|

SU1016791A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для проверки многоотсчетных преобразователей аналоговой величины в код. Достигаемый технический результат - повышение достоверности проверки преобразователя. Устройство содержит вычислительный блок, приемопередатчик, два дешифратора, блок программируемых периферийных адаптеров, блок регистров, блок цифровых компараторов, блок дешифраторов, блок формирователей импульсов, генератор импульсов, делитель частоты, триггер, проверяемый преобразователь. 1 ил.

Устройство для проверки многоотсчетных преобразователей временных интервалов в код, содержащее вычислительный блок, генератор импульсов, подключенный к входу делителя частоты, блок формирователей импульсов, выходы которого подключены к первой группе входов проверяемого преобразователя, отличающееся тем, что в него введены приемопередатчик, первый и второй дешифраторы, блок периферийных программируемых адаптеров, блок регистров, блок цифровых компараторов, блок дешифраторов, триггер, шина данных вычислительного блока соединена с первой группой выводов приемопередатчика, управляющие выходы и одна группа адресных выходов вычислительного блока подключены к входам первого дешифратора, выходы которого и другая группа адресных выходов вычислительного блока подключены к управляющим входам приемопередатчика и блока программируемых периферийных адаптеров, шина данных которого соединена с второй группой выводов приемопередатчика, первая группа выходов портов блока программируемых периферийных адаптеров подключена к информационным входам блока регистров, выходы которого подключены к одной группе входов блока цифровых компараторов, выходы блока цифровых компараторов подключены к входам блока формирователей импульсов и к одной группе входов блока дешифраторов, выходы которого подключены к управляющим входам блока регистров, выходы младших разрядов делителя частоты подключены к другой группе входов блока цифровых компараторов и к входам второго дешифратора, выходы которого подключены к другой группе входов блока дешифраторов, вторая и третья группы выходов портов блока программируемых периферийных адаптеров подключены соответственно к второй и третьей группам входов проверяемого преобразователя, группа выходов которого и выходы старших разрядов делителя частоты подключены соответственно к одной и другой группам входов портов блока программируемых периферийных адаптеров, один выход портов блока программируемых периферийных адаптеров и один выход проверяемого преобразователя подключены к соответствующим входам триггера, выход которого и выход старшего разряда делителя частоты подключены соответственно к одному и другому входам проверяемого преобразователя.

| Преобразователь угла поворота вала в код | 1991 |

|

SU1807560A1 |

| ПАРАЛЛЕЛЬНЫЙ КАСКАДНЫЙ СВЕРТОЧНЫЙ КОД С КОНЕЧНОЙ ПОСЛЕДОВАТЕЛЬНОСТЬЮ БИТОВ И ДЕКОДЕР ДЛЯ ТАКОГО КОДА | 1997 |

|

RU2187196C2 |

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| US 5282216 A, 25.01.1994 | |||

| Манипулятор для сварки | 1976 |

|

SU610648A1 |

Авторы

Даты

2009-05-10—Публикация

2008-01-09—Подача