Изобретение относится к области радиотехники и связи и может быть использовано в качестве высокочастотного устройства усиления аналоговых сигналов по мощности, в структуре аналоговых микросхем различного функционального назначения (например, широкополосных выходных каскадов ВЧ- и СВЧ-диапазонов).

В современной микроэлектронике находят широкое применение классические составные транзисторы (СТ) (так называемые схемы Дарлингтона), которые являются основой выходных каскадов и буферных усилителей различного функционального назначения.

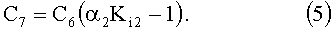

Наиболее близким по технической сущности к заявляемому устройству является составной транзистор (фиг.1) по патенту 6.611.172. Он содержит выходной транзистор 1, база которого связана с эмиттером входного транзистора 2, коллектор подключен к коллектору входного транзистора 2 и связан с эквивалентным коллекторным выводом 3 составного транзистора, база входного транзистора 2 соединена с эквивалентным базовым выводом 4 составного транзистора, а эмиттер выходного транзистора 1 связан с эквивалентным эмиттерным выводом 5 составного транзистора, причем между коллектором и базой выходного транзистора 1 включена первая 6 паразитная емкость коллектор-база, а между коллектором и базой входного транзистора 2 включена вторая 7 паразитная емкость коллектор-база.

Существенный недостаток известного СТ, архитектура которого присутствует также во многих других СТ [1-28], состоит в том, что он обладает сравнительно большой выходной Свых паразитной емкостью, обусловленной паразитными конденсаторами «коллектор-база» входного 1 и выходного 2 транзисторов, что отрицательно сказывается на диапазоне его рабочих частот в структуре различных ВЧ- и СВЧ-усилителей.

Основная задача предлагаемого изобретения состоит в уменьшении эквивалентной выходной емкости составного транзистора и, как следствие, повышении верхней граничной частоты различных усилителей на базе заявляемого СТ.

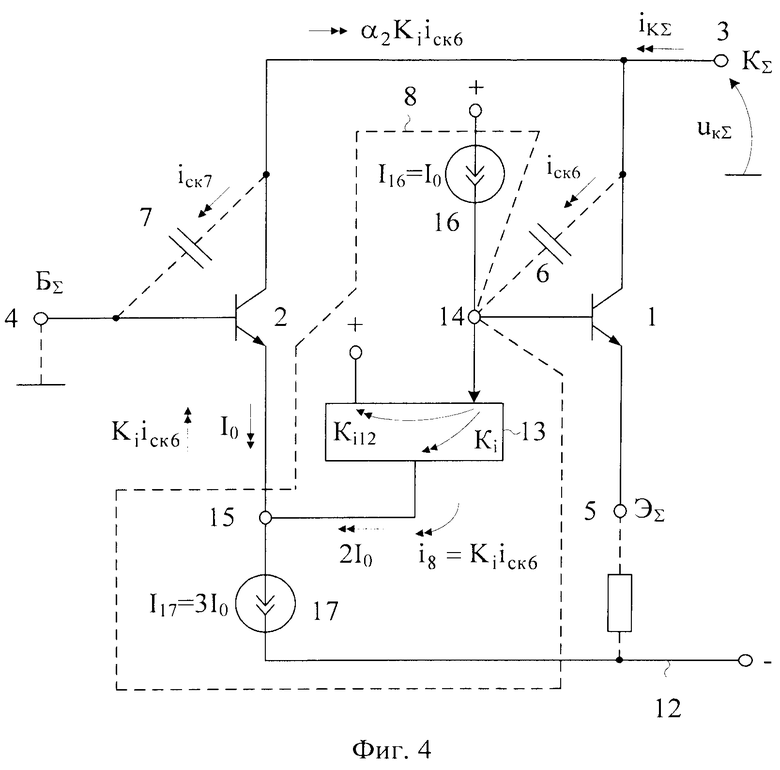

Поставленная задача решается тем, что в составном транзисторе, фиг.1, содержащем выходной транзистор 1, база которого связана с эмиттером входного транзистора 2, коллектор подключен к коллектору входного транзистора 2 и связан с эквивалентным коллекторным выводом 3 составного транзистора, база входного транзистора 2 соединена с эквивалентным базовым выводом 4 составного транзистора, а эмиттер выходного транзистора 1 связан с эквивалентным эмиттерным выводом 5 составного транзистора, причем между коллектором и базой выходного транзистора 1 включена первая 6 паразитная емкость коллектор-база, а между коллектором и базой входного транзистора 2 включена вторая 7 паразитная емкость коллектор-база, предусмотрены новые элементы и связи - база выходного транзистора 1 связана с эмиттером входного транзистора 2 через неинвертирующий усилитель тока 8.

На фиг.1 представлена схема составного транзистора-прототипа.

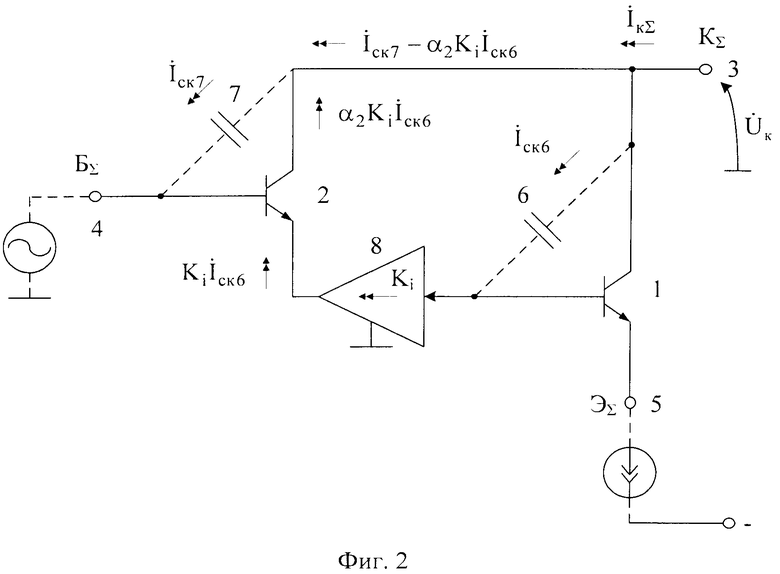

На фиг.2 представлена схема заявляемого устройства в соответствии с п.1 формулы изобретения.

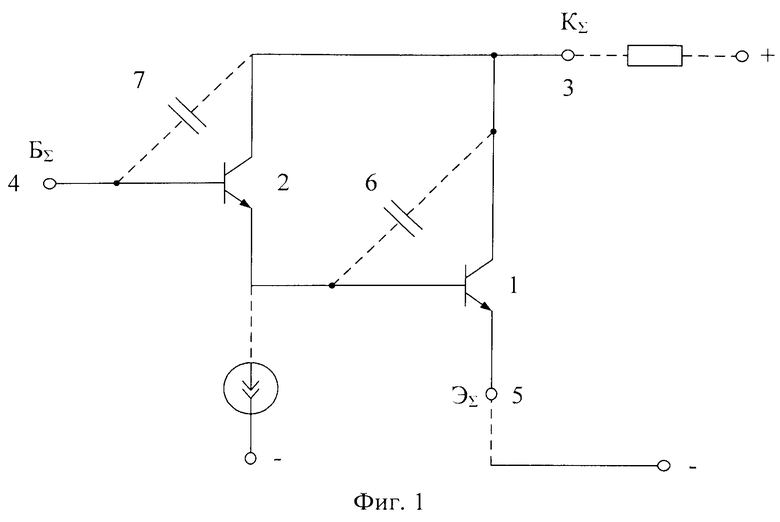

На фиг.3 показан заявляемый СТ для случая, когда неинвертирующий усилитель тока 8 реализован как токовое зеркало на p-n-p транзисторе 9 и дополнительном p-n переходе 10, источнике опорного тока 11, что соответствует п.2 формулы изобретения.

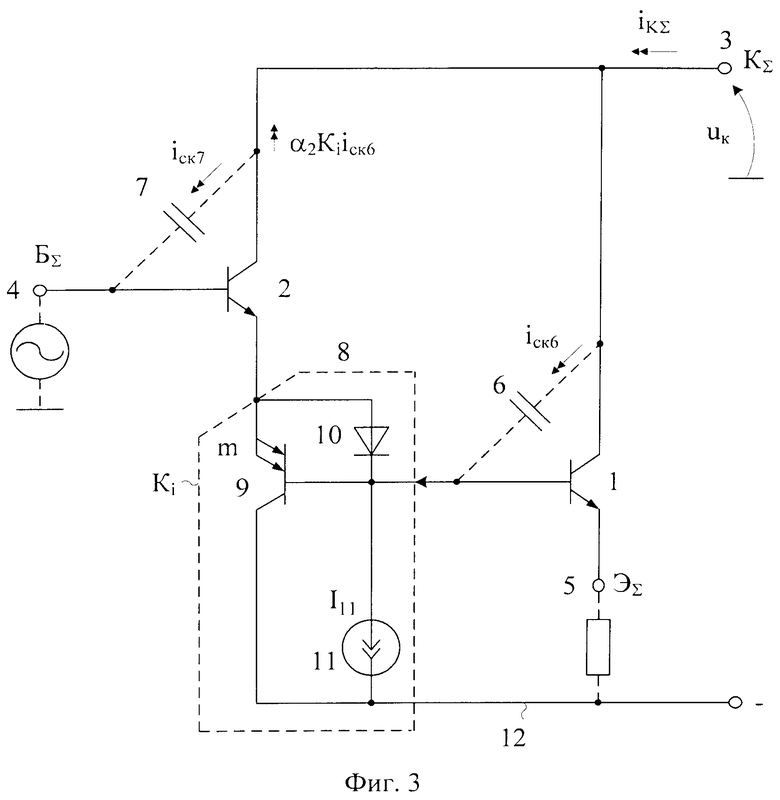

На фиг.4 представлена схема заявляемого СТ для случая, когда неинвертирующий усилитель тока 8 реализуется на основе токового зеркала 13 на транзисторах, имеющих такой же тип проводимости, что и выходной транзистор 1 и входной транзистор 2, а также включает источники опорного тока 16 и 17 для обеспечения статического режима.

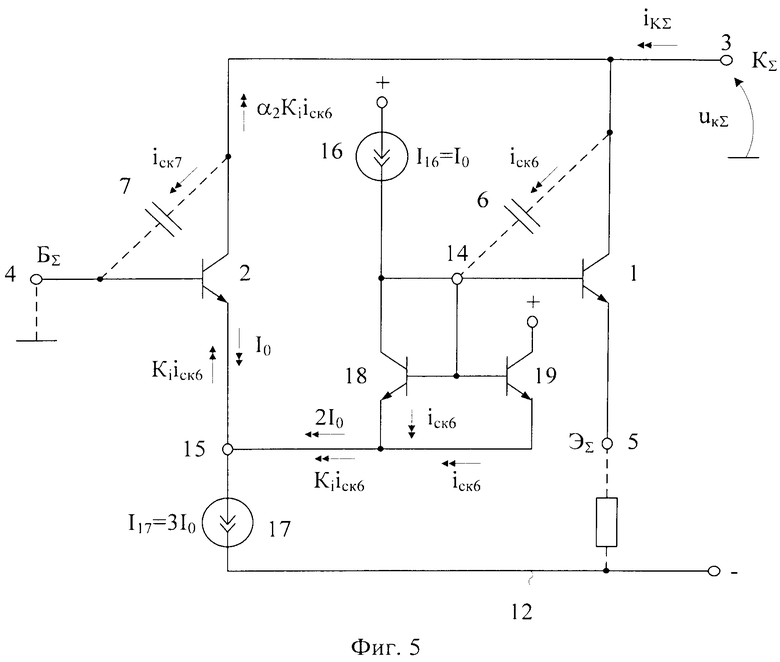

Пример практической реализации схемы по фиг.4 показан на фиг.5.

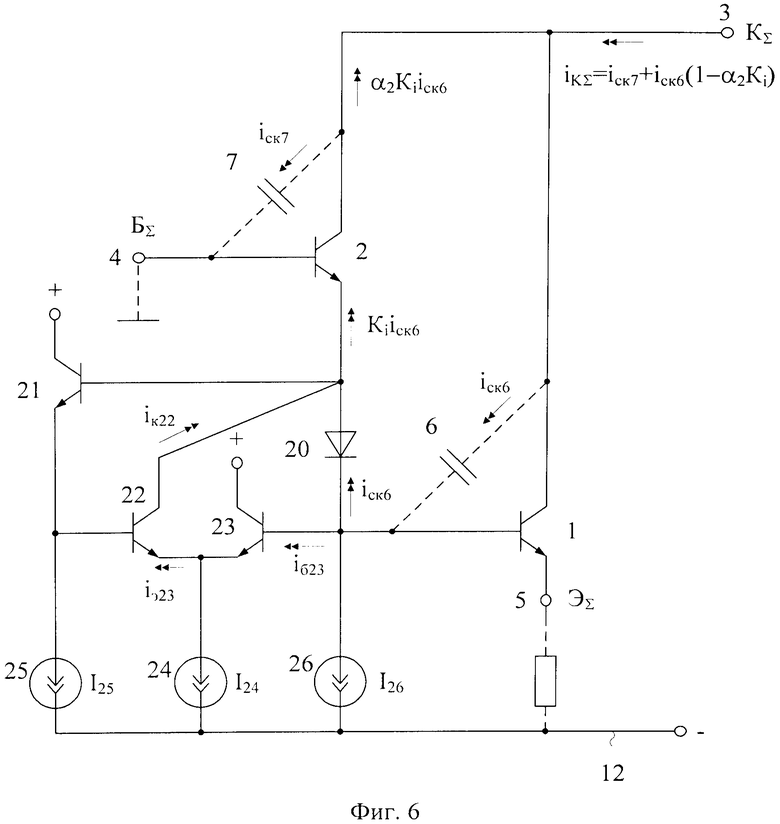

На фиг.6 приведен пример построения заявляемого СТ по фиг.2 для случая, когда неинвертирующий усилитель тока 8 выполнен на основе известной ячейки Гильберта, включающей элементы 20, 21, 22, 23, 24, 25, 26.

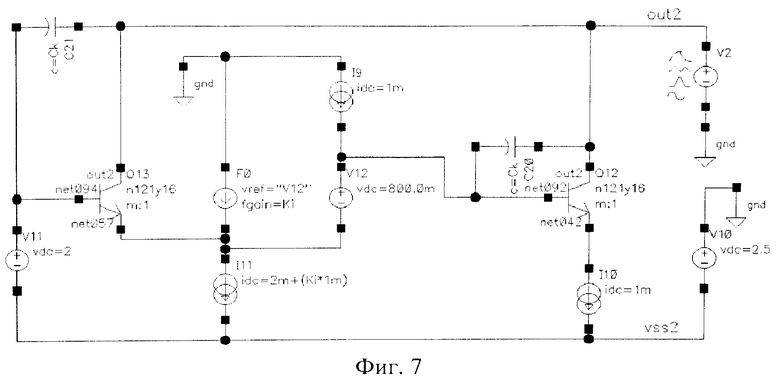

На фиг.7 приведена схема заявляемого устройства по фиг.4 в среде Cadence на моделях SiGe интегральных транзисторов. При этом выбраны паразитные емкости С7=С8=Ск=2пФ.

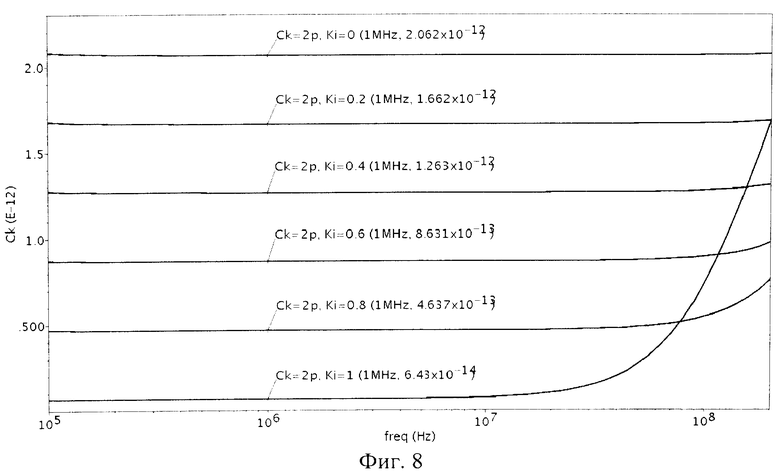

На фиг.8 показана зависимость эквивалентной выходной емкости составного транзистора по фиг.7 при различных значениях коэффициента передачи неинвертирующего усилителя тока 8 (Ki=0÷1) в диапазоне частот 100 кГц - 200 МГц. Из данного графика следует, что при Ki=1 эффективная выходная емкость СТ по фиг.7 уменьшается в 32 раза.

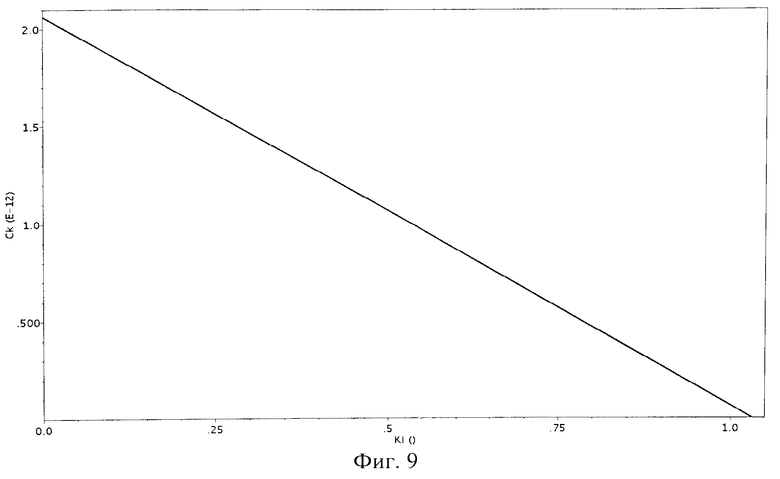

На фиг.9 представлена зависимость эквивалентной выходной емкости составного транзистора по фиг.7 от изменения коэффициента передачи по току Ki неинвертирующего усилителя тока 8.

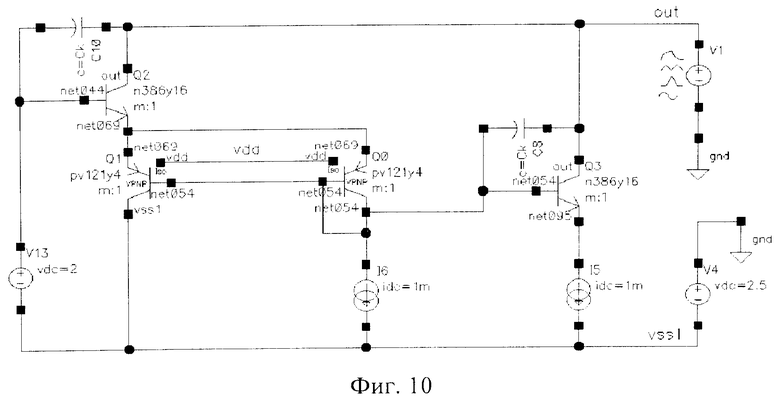

На фиг.10 показана схема составного транзистора по фиг.3 в среде Cadence на моделях SiGe интегральных транзисторов.

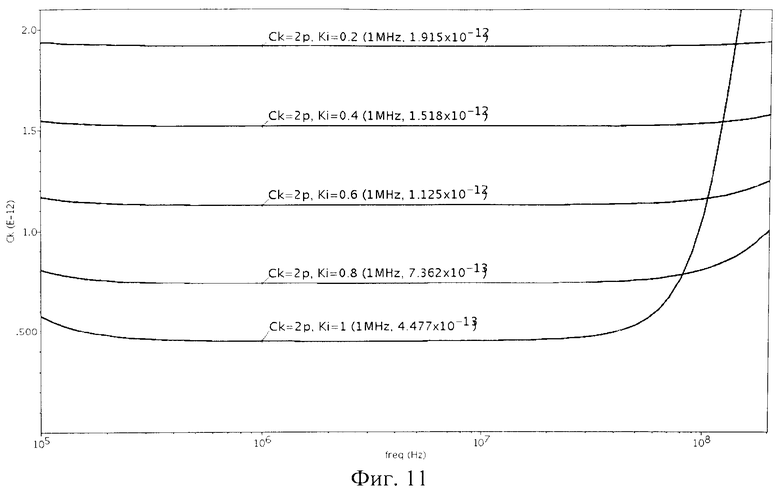

На фиг.11 показана зависимость эквивалентной выходной емкости составного транзистора по фиг.10 при различных значениях коэффициента передачи неинвертирующего усилителя тока 8 (Ki=0÷1), в диапозоне частот 100 кГц - 200 МГц. Из данного графика следует, что при Ki=1 эффективная выходная емкость СТ уменьшается.

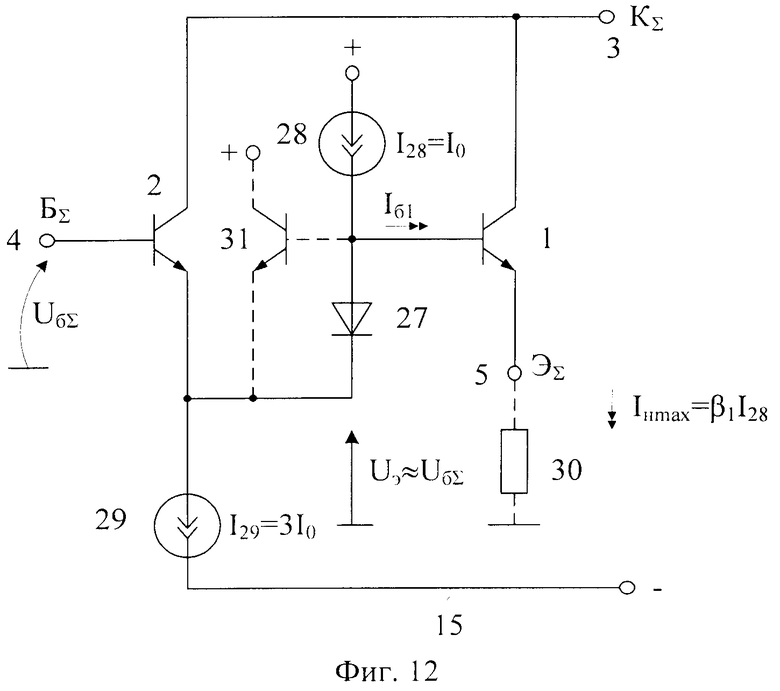

На фиг.12 показан фрагмент схемы по фиг.5, поясняющий работу заявляемого устройства при больших амплитудах входного напряжения UбΣ и низкоомных сопротивлениях резистора 29 в эмиттерной цепи выходного транзистора 1.

Составной транзистор с малой выходной емкостью, фиг.2, содержит выходной транзистор 1, база которого связана с эмиттером входного транзистора 2, коллектор подключен к коллектору входного транзистора 2 и связан с эквивалентным коллекторным выводом 3 составного транзистора, база входного транзистора 2 соединена с эквивалентным базовым выводом 4 составного транзистора, а эмиттер выходного транзистора 1 связан с эквивалентным эмиттерным выводом 5 составного транзистора, причем между коллектором и базой выходного транзистора 1 включена первая 6 паразитная емкость коллектор-база, а между коллектором и базой входного транзистора 2 включена вторая 7 паразитная емкость коллектор-база. База выходного транзистора 1 связана с эмиттером входного транзистора 2 через неинвертирующий усилитель тока 8.

На фиг.3 в соответствии с п.2 формулы изобретения неинвертирующий усилитель тока 8 выполнен на основе вспомогательного транзистора 9, параллельно эмиттерно-базовому переходу которого включен дополнительный p-n переход 10, причем база вспомогательного транзистора 9, являющаяся входом неинвертирующего усилителя тока 8, соединена через дополнительный источник опорного тока 11 с шиной источника питания 12, а эмиттер вспомогательного транзистора 9 является выходом неинвертирующего усилителя тока 8 и соединен с эмиттером входного транзистора 2.

На фиг.4 в соответствии с п.3 формулы изобретения неинвертирующий усилитель тока 8 выполнен в виде токового зеркала 13, базовый вход 14 которого соединен с базой выходного транзистора 1, а эмиттерный выход 15 является выходом неинвертирующего усилителя тока 8 и соединен с эмиттером входного транзистора 2, причем статический режим токового зеркала 13 устанавливается первым 16 источником опорного тока, связанным с базовым входом 14 токового зеркала 13, а статический режим входного транзистора 2 устанавливается вторым 17 источником опорного тока, связанным с эмиттерным выходом 15 токового зеркала 13.

На фиг.5 токовое зеркало 15 реализовано на транзисторах 18 и 19.

На фиг.6 неинвертирующий усилитель тока 8 содержит p-n переход 20, транзисторы 21, 22 и 23, а также источники опорного тока 24, 25, 26.

На фиг.12 токовое зеркало содержит p-n переход 27 и источник опорного тока 28. Статический режим транзистора 2 устанавливается источником опорного тока 29. Низкоомный резистор 30 моделирует работу СТ при больших приращениях напряжения на базе транзистора 2. Транзистор 3 1 является элементом токового зеркала.

Рассмотрим работу СТ, фиг.2.

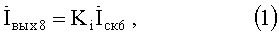

Приращение напряжения на коллекторе «КΣ» (узел 3) составного транзистора в схеме по фиг.2 вызывает изменение тока İск6 через паразитную емкость коллектор-база 6 выходного транзистора 1. Данный ток поступает на вход, а затем на выход неинвертирующего усилителя тока 8:

где Ki - коэффициент усиления по току неинвертирующего усилителя тока 8.

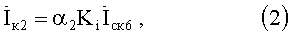

Таким образом, комплекс коллекторного тока транзистора 1 и, следовательно, суммарный ток коллектора IкΣ составного транзистора:

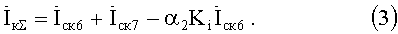

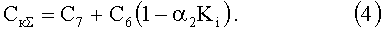

Из (3) следует, что эффективная выходная емкость предлагаемого СТ уменьшается

Для получения СкΣ≈0, необходимо, чтобы

При Ki=2, α2≈1, должно выполняться равенство С7≈С6.

Как следствие, уменьшается эквивалентная постоянная времени коллекторной цепи нагрузки СТ и увеличивается верхняя граничная частота схемы.

Схема по фиг.3 рекомендуется для использования в технологических процессах, обеспечивающих создание микросхем на n-p-n и p-n-p транзисторах. В частном случае источник тока 11 в данной схеме может принимать малые значения.

Схемы по фиг.4, фиг.5 могут применяться в том случае, если микросхема реализуется только на n-p-n транзисторах. Данные схемы обладают функциями защиты от чрезмерно больших эмиттерных токов выходного транзистора, причем данные их свойства поясняются фиг.12.

Особенность схемы по фиг.6 - реализация неивертирующего усилителя тока 8 на основе каскада Гильберта, который обладает более широким частотным диапазоном.

При больших уровнях напряжения на базе транзистора 2 в схеме по фиг.12 максимально возможный ток эмиттера транзистора 1 не больше чем произведение β1I28. В то же время входное сопротивление предлагаемого составного транзистора, так же как и СТ-прототипа, определяется по формуле β1β2R30, где R30 - сопротивление в эмиттерной цепи транзистора 1, где βi - коэффициент усиления по току базы i-го транзистора. Таким образом, заявляемая схема имеет такое же, как и в прототипе, входное сопротивление и максимальный ток в эмиттерной цепи транзистора 1 не больше чем произведение β1I28. В прототипе максимальный ток в эмиттерной цепи транзистора 1 при больших напряжениях на базе транзистора 2 практически не ограничивается, что может привести к его выходу из строя.

Данные теоретические выводы подтверждают результаты моделирования, показанные на фиг.8, фиг.9, фиг.11.

Таким образом, заявляемое схемотехническое решение составного транзистора, который может использоваться не только как элемент интегральных микросхем, но и как СТ на основе мощных дискретных транзисторов с большой площадью p-n перехода и, следовательно, емкостью коллектор-база, характеризуется меньшей величиной выходной емкости и более высокими значениями верхней граничной частоты.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.806.778.

2. Патент US 4.706.038.

3. Патент US 4.024.462.

4. Патент US 3.510.791.

5. Патент US 4.890.067.

6. Патент US 7.123.091.

7. Патент ЕР 0648010.

8. Патент US 7.692.492.

9. Патент US 6.611.172.

10. Патент ЕР 0623993.

11. Патент US 5.488.330.

12. Патент US 7.436.262.

13. Патент US 6.653.901.

12. Патент US 5.900.774.

15. Патент US 5.694.031.

16. Патент US 6.798.285.

17. Патент US 6.107.886.

18. Патент ЕР 385547.

19. Патент US 2.658.673.

20. Патент US 4.547.744.

21. Патент US 4.219.839.

22. Патент US 7.088.174.

23. Патент US 7.834.695.

24. Патент US 2.658.675.

25. Патент US 4.914.533.

26. Патент US 3.694.763.

27. Патент US 5.218.319.

28. Патент ЕР 0767989.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВУХКАНАЛЬНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2452078C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421885C1 |

| КАСКОДНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ РАБОЧИХ ЧАСТОТ | 2014 |

|

RU2572376C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ В МОСТОВОМ ВХОДНОМ ДИФФЕРЕНЦИАЛЬНОМ КАСКАДЕ | 2023 |

|

RU2797168C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МОСТОВЫМ ВХОДНЫМ ДИФФЕРЕНЦИАЛЬНЫМ КАСКАДОМ | 2022 |

|

RU2791274C1 |

| Быстродействующий операционный усилитель | 2024 |

|

RU2822112C1 |

| УСИЛИТЕЛЬ ПЕРЕМЕННОГО ТОКА С ПРОТИВОФАЗНЫМИ ТОКОВЫМИ ВЫХОДАМИ | 2011 |

|

RU2475946C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2013 |

|

RU2523124C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ЧАСТОТНЫМ ДИАПАЗОНОМ | 2014 |

|

RU2568316C1 |

Изобретение относится к вычислительной технике. Технический результат заключается в уменьшении эквивалентной выходной емкости составного транзистора. Составной транзистор с малой выходной емкостью содержит выходной транзистор, база которого связана с эмиттером входного транзистора, коллектор подключен к коллектору входного транзистора и связан с эквивалентным коллекторным выводом составного транзистора, база входного транзистора соединена с эквивалентным базовым выводом составного транзистора, а эмиттер выходного транзистора связан с эквивалентным эмиттерным выводом составного транзистора, причем между коллектором и базой выходного транзистора включена первая паразитная емкость коллектор-база, а между коллектором и базой входного транзистора включена вторая паразитная емкость коллектор-база, причем база выходного транзистора связана с эмиттером входного транзистора через неинвертирующий усилитель тока. 2 з.п. ф-лы, 12 ил.

1. Составной транзистор с малой выходной емкостью, содержащий выходной транзистор (1), база которого связана с эмиттером входного транзистора (2), коллектор подключен к коллектору входного транзистора (2) и связан с эквивалентным коллекторным выводом (3) составного транзистора, база входного транзистора (2) соединена с эквивалентным базовым выводом (4) составного транзистора, а эмиттер выходного транзистора (1) связан с эквивалентным эмиттерным выводом (5) составного транзистора, причем между коллектором и базой выходного транзистора (1) включена первая (6) паразитная емкость коллектор-база, а между коллектором и базой входного транзистора (2) включена вторая (7) паразитная емкость коллектор-база, отличающийся тем, что база выходного транзистора (1) связана с эмиттером входного транзистора (2) через неинвертирующий усилитель тока (8).

2. Составной транзистор с малой выходной емкостью по п.1, отличающийся тем, что неинвертирующий усилитель тока (8) выполнен на основе вспомогательного транзистора (9), параллельно эмиттерно-базовому переходу которого включен дополнительный p-n переход (10), причем база вспомогательного транзистора (9), являющаяся входом неинвертирующего усилителя тока (8), соединена через дополнительный источник опорного тока (11) с шиной источника питания (12), а эмиттер вспомогательного транзистора (9) является выходом неинвертирующего усилителя тока (8) и соединен с эмиттером входного транзистора (2).

3. Составной транзистор с малой выходной емкостью по п.1, отличающийся тем, что неинвертирующий усилитель тока (8) выполнен в виде токового зеркала (13), базовый вход (14) которого соединен с базой выходного транзистора (1), а эмиттерный выход (15) является выходом неинвертирующего усилителя тока (8) и соединен с эмиттером входного транзистора (2), причем статический режим токового зеркала (13) устанавливается первым (16) источником опорного тока, связанным с базовым входом (14) токового зеркала (13), а статический режим входного транзистора (2) устанавливается вторым (17) источником опорного тока, связанным с эмиттерным выходом (15) токового зеркала (13).

| US 6611172 B1, 26.08.2003 | |||

| ТОКОВОЕ ЗЕРКАЛО | 2008 |

|

RU2367996C1 |

| RU 2003116641 A, 20.12.2004 | |||

| US 6756840 B1, 29.06.2004 | |||

| ВЫСОКОЧАСТОТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2396697C2 |

| US 6194959 B1, 27.02.2001 | |||

Авторы

Даты

2014-12-27—Публикация

2013-06-18—Подача