Изобретение относится к радиоэлектронике и может быть использовано в качестве операционных усилителей (ОУ), предназначенных для применения в подклассе так называемых дискретно-аналоговых SC-фильтров на переключаемых конденсаторах [1], для которых (в ряде важных случаев) требуются повышенные значения максимальной скорости нарастания выходного напряжения ОУ, а также в драйверах быстродействующих аналого-цифровых преобразователей.

В современной радиоэлектронной аппаратуре находят применение операционные усилители с входными каскадами подкласса dual-input-stage, которые содержат два параллельно включенных по входам классических ДК на комплементарных транзисторах [2-12]. Однако, в данном классе известных ОУ при их изготовлении на основе микронных технологических процессов не решаются проблемы существенного повышения максимальной скорости нарастания выходного напряжения (SR).

Схемы ОУ с входным каскадом подкласса dual-input-stage, выходы которого связаны с токовыми зеркалами, согласованными с положительной и отрицательной шинами источника питания, применяются:

- в ОУ по патенту US 5.515.005 fig. 1, fig. 2;

- в ОУ по патенту US 5.291.149;

- в ОУ по патенту US 4.636.743 в качестве выходной подсхемы.

Кроме этого модификации рассматриваемой архитектуры ОУ нашли применение во многих других патентах ведущих электронных фирм мира, в том числе на CMOS транзисторах (US 6.794.940 fig. 1, US 3.701.032).

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту фирмы Harris Corporation US 4636743, фиг. 1, 1987 г. ОУ-прототип содержит (фиг.1) выход 1 устройства, инвертирующий вход 2 и неинвертирующий вход 3, первый 4 входной транзистор, база которого соединена с инвертирующим входом 2, а коллектор подключен к первой 5 шине источника питания, второй 6 входной транзистор, база которого соединена с инвертирующим входом 2 устройства, а коллектор подключен ко второй 7 шине источника питания, первый 8 выходной транзистор, коллектор которого соединен со входом первого 9 токового зеркала, согласованного со второй 7 шиной источника питания, второй 10 выходной транзистор, коллектор которого соединен со входом второго 11 токового зеркала, согласованного с первой 5 шиной источника питания, первый 12 и второй 13 согласующие транзисторы, первый 14 и второй 15 токостабилизирующие двухполюсники.

Существенный недостаток известного ОУ фиг. 1, также как и десятков других операционных усилителей данного класса, например [2-12], состоит в том, что здесь максимальная скорость нарастания выходного напряжения имеет небольшие значения (50-80 В/мкс), что обусловлено нелинейным режимом работы входного дифференциального каскада [8-12]:

SR=2πUгрf1,

где Uгр – напряжение ограничения проходной характеристики входного каскада [8-12],

f1 – частота единичного усиления скорректированного ОУ.

Основная задача предполагаемого изобретения состоит в повышении SR ОУ за счет применения входного каскада, обеспечивающего форсирование процесса перезаряда интегрирующей емкости коррекции ОУ в его неинвертирующем и инвертирующем включениях. В конечном итоге это повышает быстродействие ОУ в режиме большого сигнала, уменьшает время установления переходного процесса.

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем выход 1 устройства, инвертирующий вход 2 и неинвертирующий вход 3, первый 4 входной транзистор, база которого соединена с инвертирующим входом 2, а коллектор подключен к первой 5 шине источника питания, второй 6 входной транзистор, база которого соединена с инвертирующим входом 2 устройства, а коллектор подключен ко второй 7 шине источника питания, первый 8 выходной транзистор, коллектор которого соединен со входом первого 9 токового зеркала, согласованного со второй 7 шиной источника питания, второй 10 выходной транзистор, коллектор которого соединен со входом второго 11 токового зеркала, согласованного с первой 5 шиной источника питания, первый 12 и второй 13 согласующие транзисторы, первый 14 и второй 15 токостабилизирующие двухполюсники, предусмотрены новые элементы и связи – эмиттер первого 4 входного транзистора соединен с эмиттером первого 8 выходного транзистора, эмиттер второго 6 входного транзистора соединен с эмиттером второго 10 выходного транзистора, база первого 8 выходного транзистора связана с базой и коллектором первого 12 согласующего транзистора и через первый 14 источник опорного тока соединена со второй 7 шиной источника питания, база второго 10 выходного транзистора связана с базой и коллектором второго 13 согласующего транзистора и через второй 15 источник опорного тока соединена с первой 5 шиной источника питания, неинвертирующий вход 3 соединен с базой первого 16 дополнительного транзистора, эмиттер которого соединен с эмиттером первого 12 согласующего транзистора, а коллектор подключен к первой 5 шине источника питания, неинвертирующий вход 3 соединен с базой второго 17 дополнительного транзистора, эмиттер которого соединен с эмиттером второго 13 согласующего транзистора, а коллектор подключен ко второй 7 шине источника питания, причем между базами первого 8 и второго 10 выходных транзисторов включен дополнительный корректирующий конденсатор 18, а выход первого 9 токового зеркала соединен с выходом второго 11 токового зеркала и подключен к выходу устройства 1.

На чертеже фиг. 1 приведена схема операционного усилителя – прототипа.

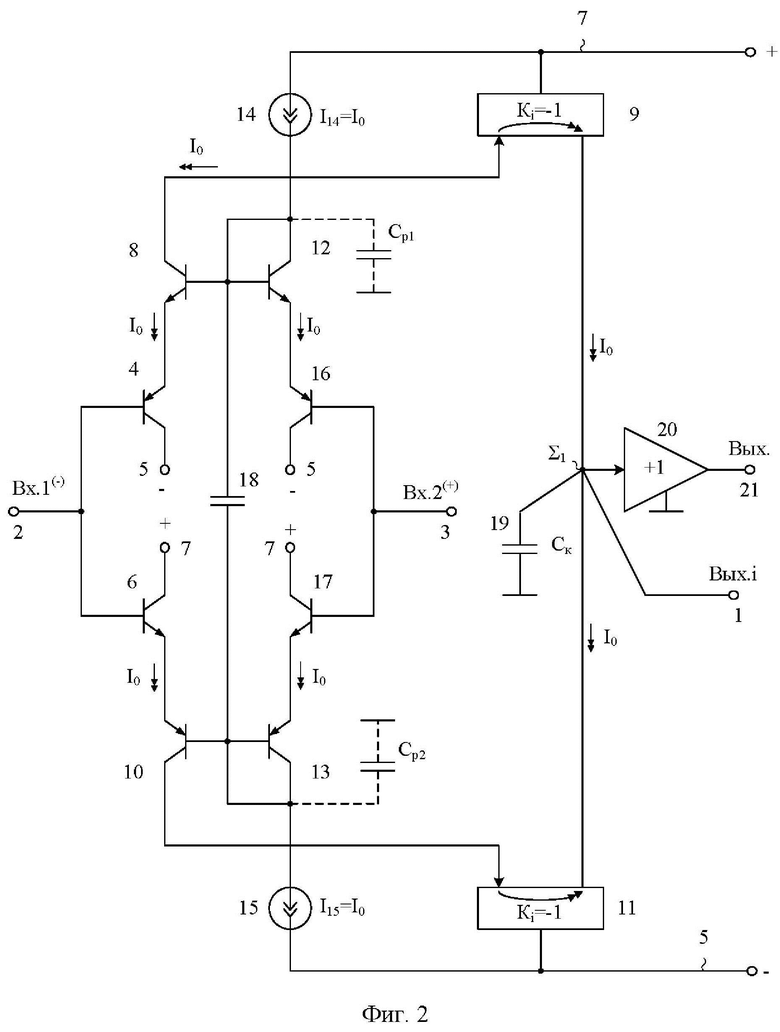

На чертеже фиг. 2 показана схема заявляемого ОУ в соответствии с п. 1 и п.2 формулы изобретения для случая, когда в схеме используются комплементарные n-p-n и p-n-p биполярные транзисторы.

На чертеже фиг. 3 приведена схема, соответствующая фиг. 2, в которой для повышения входного сопротивления входные транзисторы ОУ выполнены как полевые транзисторы с управляющим p-n переходом.

На чертеже фиг. 4 представлен статический режим схемы ОУ фиг. 2 для его неинвертирующего включения со 100% отрицательной обратной связью в среде LTspice при t=27oC, Ск=Ск1=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА.

На чертеже фиг. 5 показана логарифмическая амплитудно-частотная характеристика (ЛАЧХ) ОУ фиг. 4 в среде LTspice.

На чертеже фиг. 6 приведены переходные процессы для переднего фронта ОУ фиг. 4 в среде LTspice при разных значениях емкости дополнительного корректирующего конденсатора 18 (С18=Ск1=0 пФ; 5 пФ; 7 пФ; 10 пФ).

На чертеже фиг. 7 представлены переходные процессы для заднего фронта ОУ фиг. 4 в среде LTspice при Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА и разных значениях емкости C18=Ск1=0 пФ; 5 пФ; 7 пФ; 10 пФ.

На чертеже фиг. 8 показана схема инвертирующего включения ОУ фиг. 2 в среде LTspice при t=27oC, Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА, Ск1=0 пФ; 2 пФ; 3 пФ; 4 пФ.

На чертеже фиг. 9 приведены переходные процессы ОУ фиг. 8 для переднего фронта в среде LTspice при t= 27oC, Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100мкА и разных значениях емкости Ск1=0 пФ; 2 пФ; 3 пФ; 4 пФ.

На чертеже фиг. 10 представлен статический режим неинвертирующего включения ОУ фиг.4 в среде LTSpice на моделях транзисторов MH2XA031_25.01.21 при наличии низкоомных резисторов R1=R2=R4=R5=100 Ом в эмиттерных цепях транзисторов Q3, Q4, Q5, Q6, температуре 27°С, источниках опорного тока I1=I2=100мкА, конденсаторах С1=1 пФ, Ск1=0 пФ, Cp2=Сp3=1 пФ, напряжениях питания V1=V2=±5В.

На чертеже фиг. 11 показана ЛАЧХ коэффициента усиления ОУ фиг. 10 при С1=1 пФ, Ск1=0 пФ, Cp1=Сp2=1 пФ.

На чертеже фиг. 12 приведен передний фронт переходного процесса в ОУ фиг. 10.

На чертеже фиг. 13 показан задний фронт для переходного процесса в ОУ фиг. 10.

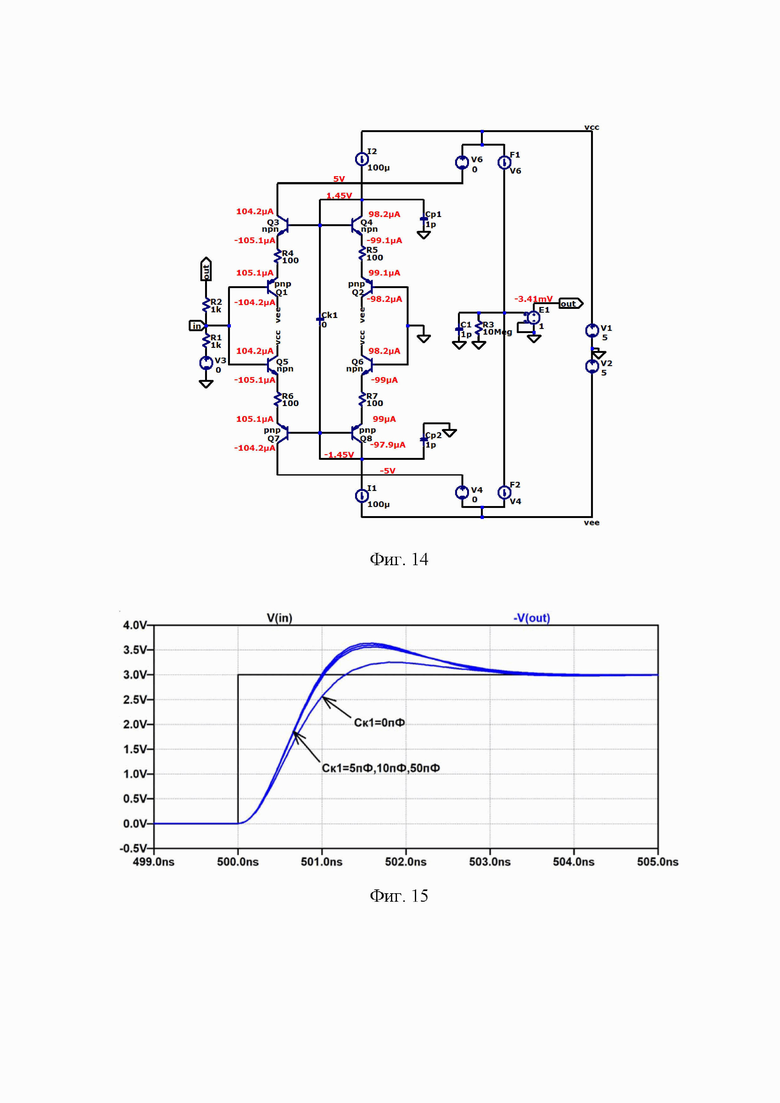

На чертеже фиг. 14 приведен статический режим ОУ фиг. 2 в инвертирующем включении в среде LTSpice на моделях транзисторов MH2XA031_25.01.21 при 27°С, источниках опорного тока I1=I2=100 мкА, конденсаторах С1=1 пФ, Ск1=0 пФ, Cp2=Сp3=1 пФ и напряжениях питания V1=V2=±5В.

На чертеже фиг. 15 приведен передний фронт переходного процесса в ОУ фиг. 14.

На чертеже фиг. 16 показан задний фронт переходного процесса в ОУ фиг. 14.

На чертеже фиг. 17 представлен статический режим неинвертирующего включения ОУ фиг. 3 с входными полевыми транзисторами в среде LTspice при t= 27oC, Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА.

На чертеже фиг. 18 приведены переходные процессы (передний фронт) в неинвертирующем включении ОУ фиг. 17 с входными полевыми транзисторами в среде LTspice при Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА и разных значениях емкости конденсатора Ск1=0 пФ; 5 пФ; 10 пФ; 25 пФ; 50 пФ; 100 пФ.

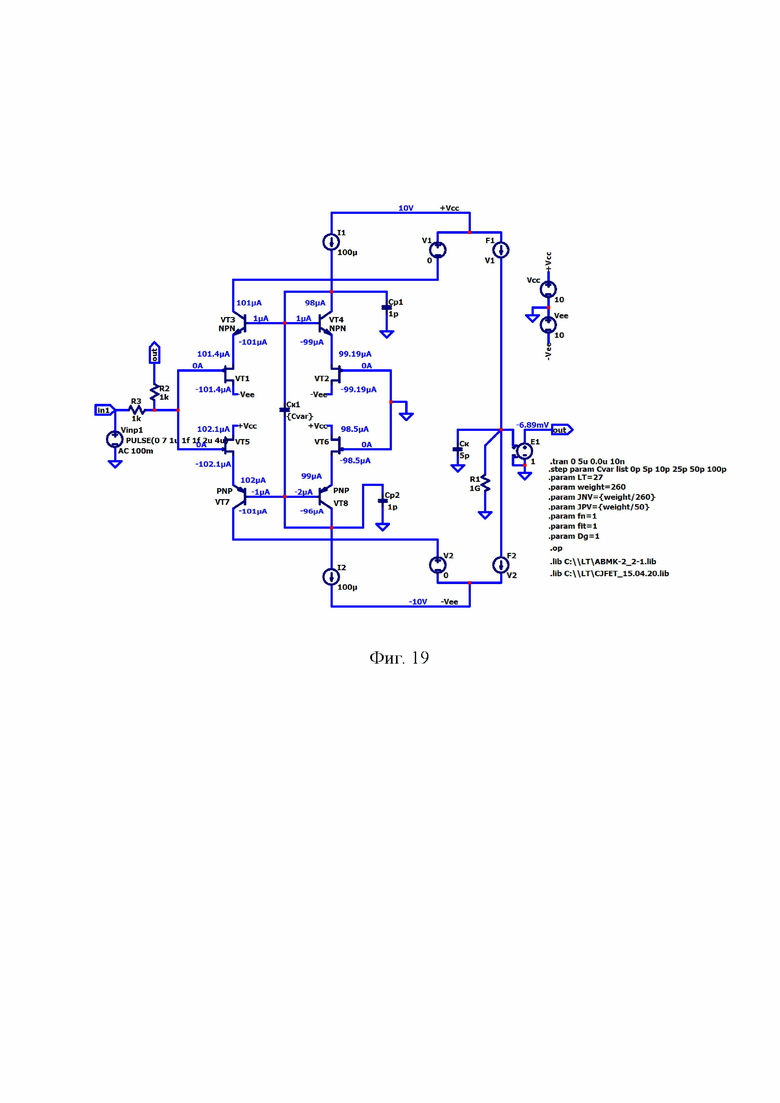

На чертеже фиг. 19 показан статический режим инвертирующего включения ОУ фиг. 3 с входными полевыми транзисторами в среде LTspice при t= 27oC, Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА, R2 =R3=1 кОм.

На чертеже фиг. 20 представлены переходные процессы для переднего фронта инвертирующего включения ОУ фиг. 19 с входными полевыми транзисторами в среде LTspice при разных значениях емкости Ск1=0 пФ; 5 пФ; 10 пФ; 25 пФ; 50 пФ; 100 пФ.

На чертеже фиг. 21 приведены переходные процессы для заднего фронта инвертирующего включения ОУ фиг. 19 в среде LTspice при разных значениях емкости Ск1=0 пФ; 5 пФ; 10 пФ; 25 пФ; 50 пФ; 100 пФ.

Быстродействующий операционный усилитель фиг. 2 содержит выход 1 устройства, инвертирующий вход 2 и неинвертирующий вход 3, первый 4 входной транзистор, база которого соединена с инвертирующим входом 2, а коллектор подключен к первой 5 шине источника питания, второй 6 входной транзистор, база которого соединена с инвертирующим входом 2 устройства, а коллектор подключен ко второй 7 шине источника питания, первый 8 выходной транзистор, коллектор которого соединен со входом первого 9 токового зеркала, согласованного со второй 7 шиной источника питания, второй 10 выходной транзистор, коллектор которого соединен со входом второго 11 токового зеркала, согласованного с первой 5 шиной источника питания, первый 12 и второй 13 согласующие транзисторы, первый 14 и второй 15 токостабилизирующие двухполюсники. Эмиттер первого 4 входного транзистора соединен с эмиттером первого 8 выходного транзистора, эмиттер второго 6 входного транзистора соединен с эмиттером второго 10 выходного транзистора, база первого 8 выходного транзистора связана с базой и коллектором первого 12 согласующего транзистора и через первый 14 источник опорного тока соединена со второй 7 шиной источника питания, база второго 10 выходного транзистора связана с базой и коллектором второго 13 согласующего транзистора и через второй 15 источник опорного тока соединена с первой 5 шиной источника питания, неинвертирующий вход 3 соединен с базой первого 16 дополнительного транзистора, эмиттер которого соединен с эмиттером первого 12 согласующего транзистора, а коллектор подключен к первой 5 шине источника питания, неинвертирующий вход 3 соединен с базой второго 17 дополнительного транзистора, эмиттер которого соединен с эмиттером второго 13 согласующего транзистора, а коллектор подключен ко второй 7 шине источника питания, причем между базами первого 8 и второго 10 выходных транзисторов включен дополнительный корректирующий конденсатор 18, а выход первого 9 токового зеркала соединен с выходом второго 11 токового зеркала и подключен к выходу устройства 1.

В схеме фиг. 2 интегрирующий корректирующий конденсатор 19 ОУ обеспечивает устойчивость петли общей отрицательной обратной связи. В некоторых случаях данный элемент может отсутствовать и тогда устойчивость ОУ может обеспечиваться за счет паразитных емкостей первого 9 и второго 11 токовых зеркал и входной емкости дополнительного буферного усилителя 20.

Кроме этого на чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, токовый выход 1 устройства соединен со входом дополнительного буферного усилителя 20, выход которого 21 является потенциальным выходом устройства.

Рассмотрим работу ОУ фиг. 2 в неинвертирующем включении со 100% отрицательной обратной связью.

Статический режим схемы устанавливается первым 14 и вторым 15 токостабилизирующими двухполюсниками. При этом в ОУ обеспечиваются следующие эмиттерные (Iэ) и коллекторные (Iк) токи транзисторов:

где I0 – заданные разработчиком токи первого 14 и второго 15 токостабилизирующих двухполюсников, например, 100 мкА. Поэтому выходные токи первого 9 и второго 10 токовых зеркал одинаковы.

Рассмотрим вначале случай, когда емкость дополнительного корректирующего конденсатора 18 равна нулю (С18=0).

Если на неинвертирующий вход 3 подается большой импульсный сигнал uc, то это приводит к практически мгновенному запиранию первого 16 дополнительного транзистора. Из-за наличия паразитной емкости Ср1 напряжение на базе первого 8 выходного транзистора будет изменяться во времени в соответствии с формулой

Как следствие, коллекторный ток первого 8 выходного транзистора и выходной ток первого 9 токового зеркала, перезаряжающий корректирующий конденсатор 19 (Ск), также изменяются в соответствии с формулой (5). Поэтому скорость нарастания напряжения на выходе 1 устройства получается небольшой из-за малых значений I0, который существенно влияет на входные токи ОУ, и выбирается в диапазоне 50-100 мкА.

Введение дополнительного корректирующего конденсатора 18 форсирует переходные процессы в схеме фиг. 2. Импульсное приращение напряжения на неинвертирующем входе 2 (uс(+)) передается (с минимальной задержкой) на второй 15 токостабилизирующий двухполюсник и вызывает импульсное изменение тока i18(+), зависящее от емкости дополнительного корректирующего конденсатора 18. Этот ток ускоряет перезаряд паразитного конденсатора Cp1. Как следствие, коллекторный ток iк8(+) первого 8 выходного транзистора имеет более «прямоугольную» форму. Поэтому выходной ток первого 9 токового зеркала i9(+)≈i18(+) быстро перезаряжает интегрирующий конденсатор 19, что способствует повышению SR(+). Аналогичные процессы происходят и для отрицательных значений uс(-) на неинвертирующем входе 2. В таблице 1 приведена информация о зависимости максимальной скорости нарастания выходного напряжения ОУ фиг.4 от емкости Cк1=С18. Полученные значения SR определены по графикам переходных процессов фиг. 6, фиг. 7.

Таблица 1 - Значения SR для неинвертирующего включения ОУ фиг. 4 при Ск1=0 пФ; 5 пФ; 7 пФ; 10 пФ, Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА

(передний фронт)

(задний фронт)

Из таблицы 1 следует, что SR предлагаемого ОУ в неинвертирующем включении увеличивается за счет Ск1 с 80 В/мкс до 8000-10000 В/мкс, т.е. более чем на два порядка.

В таблице 2 приведена информация о зависимости максимальной скорости нарастания выходного напряжения ОУ фиг.8 от емкости Cк1=С18 при R2=R3=1 кОм (графики фиг. 9).

Таблица 2 - Значения SR для инвертирующего включения ОУ фиг. 8 при разных емкостях конденсатора Ск1=0 пФ; 5 пФ; 7 пФ; 10 пФ, Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА

(передний фронт)

(задний фронт)

На основании данных таблицы 2 можно сделать вывод о том, что при инвертирующем включении ОУ максимальная скорость нарастания выходного напряжения увеличивается за счет Ск1 не более чем в 2 раза.

В тех случаях, когда в схеме предлагаемого ОУ возникает перерегулирование переходного процесса в режиме большого сигнала, рекомендуется введение низкоомных резисторов в эмиттерные цепи входных транзисоров (фиг. 10).

Таблица 3 - Значения SR ОУ фиг. 10 в неинвертирующем включении при наличии низкоомных резисторов R1=R2=R4=R5=100 Ом в эмиттерных цепях транзисторов Q3, Q4, Q5, Q6 и разных значениях Ск1=0 пФ; 5 пФ; 7 пФ; 10 пФ, Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА

(передний фронт)

(задний фронт)

Анализ таблицы 3 и графиков переходных процессов (фиг. 12, фиг. 13) показывает, что введение низкоомных резисторов в неинвертирующем включении ОУ фиг.10 позволяет уменьшить перерегулирование переходного процесса при достаточно высоком выигрыше по SR – увеличении SR за счет Ск1 с 85,5 В/мкс до 5312,5 В/мкс.

Влияние низкоомных резисторов R1=R2=R4=R5=100 Ом на переходные процессы в инвертирующем включении ОУ фиг. 14 характеризует графики фиг. 15, фиг. 16 и данные таблицы 4.

Таблица 4 - Значения SR ОУ фиг. 14 в его инвертирующем включении при разных значениях емкости Ск1=0 пФ; 5 пФ; 7 пФ; 10 пФ, Ск=5 пФ, Ср1=Ср2=1 пФ, I1=I2=100 мкА

(передний фронт)

(задний фронт)

Таким образом, в инвертирующем включении рассматриваемое схемотехническое решение ОУ фиг. 14 обеспечивает достаточно высокий уровень SR при незначительном увеличении максимальной скорости нарастания выходного напряжения за счет конденсатора Ск1.

Далее, в таблицах 5 и 6 приведены численные значения SR ОУ с входными полевыми транзисторами фиг. 3. Эти данные получены в результате анализа переходных процессов фиг. 18 и фиг. 20.

Таблица 5 – Максимальная скорость нарастания выходного напряжения неинвертирующего ОУ с входными полевыми транзисторами (фиг. 17) при разных значениях емкости дополнительного конденсатора Ск1=0 пФ; 5 пФ; 10 пФ; 25 пФ; 50 пФ; 100 пФ

(передний фронт)

(задний фронт)

Анализ таблицы 5 позволяет установить, что SR ОУ фиг. 17 с входными полевыми транзисторами в неинвертирующем включении возрастает с 57 В/мкс до 800 В/мкс.

Таблица 6 - Значения SR в инвертирующем включении ОУ с входными полевыми транзисторами (фиг. 19)

(передний фронт)

(задний фронт)

Схема ОУ с входными полевыми транзисторами в инвертирующем включении обеспечивает SR=360÷400 В/мкс.

Таким образом, выполненное компьютерное моделирование показывает, что заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимальной скорости нарастания выходного напряжения.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Naderi M. H., Prakash S., Silva-Martinez J. Operational transconductance amplifier with class-B slew-rate boosting for fast high-performance switched-capacitor circuits //IEEE Transactions on Circuits and Systems I: Regular Papers. – 2018. – Т. 65. – №. 11. – С. 3769-3779

2. Патент US 4.636.743, fig. 1, 1987 г.

3. Патент US 5.515.005, fig. 2, 1996 г.

4. Патент US 5.374.897, fig. 3, 1994 г.

5. Патент RU 2684500, fig. 2, 2019 г.

6. Патент US 5.291.149, 1994 г.

7. Патентная заявка US 2002/0180526, fig. 3, 2002 г.

Монографии по теории ОУ:

8. Матавкин В. Быстродействующие операционные усилители. – М: Радио и связь, 1989. – С. 100, рис. 6.9, ОУ154УД4

9. Операционные усилители с непосредственной связью каскадов : монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

10. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: монография / Н.Н.Прокопенко. - Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. – 222 с.

11. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. – Шахты: Изд-во ЮРГУЭС, 2006. – 231 с.

12. Операционные усилители для всех / Брюс Картер и Рон Манчини; пер. с англ. А.Н. Рабодзея. – М.: Додэка-XXI, 2011. – 544 с. : ил. – (Серия «Схемотехника). – Доп.тит.л.англ. – ISBN 978-5-94120-242-3, рис. 6.15-рис. 6.17

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ ПЕРЕХОДНОГО ПРОЦЕССА | 2022 |

|

RU2784706C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МОСТОВЫМ ВХОДНЫМ ДИФФЕРЕНЦИАЛЬНЫМ КАСКАДОМ | 2022 |

|

RU2791274C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ В МОСТОВОМ ВХОДНОМ ДИФФЕРЕНЦИАЛЬНОМ КАСКАДЕ | 2023 |

|

RU2797168C1 |

| Быстродействующий дифференциальный операционный усилитель на комплементарных биполярных транзисторах | 2024 |

|

RU2827743C1 |

| Операционный усилитель с повышенной максимальной скоростью нарастания выходного напряжения | 2023 |

|

RU2810544C1 |

| Быстродействующий операционный усилитель с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2811071C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

Изобретение относится к радиоэлектронике. Технический результат: повышение максимальной скорости нарастания выходного напряжения операционного усилителя за счет применения входного каскада, обеспечивающего форсирование процесса перезаряда интегрирующей емкости коррекции операционного усилителя в его неинвертирующем и инвертирующем включениях. Такой результат обеспечивается за счет того, что эмиттер первого входного транзистора соединен с эмиттером первого выходного транзистора, эмиттер второго входного транзистора соединен с эмиттером второго выходного транзистора, база первого выходного транзистора связана с базой и коллектором первого согласующего транзистора, база второго выходного транзистора связана с базой и коллектором второго согласующего транзистора, неинвертирующий вход соединен с базой первого дополнительного транзистора, эмиттер которого соединен с эмиттером первого согласующего транзистора, неинвертирующий вход соединен с базой второго дополнительного транзистора, эмиттер которого соединен с эмиттером второго согласующего транзистора, причем между базами первого и второго выходных транзисторов включен дополнительный корректирующий конденсатор, а выход первого токового зеркала соединен с выходом второго токового зеркала и подключен к выходу устройства. 1 з.п. ф-лы, 21 ил.

1. Быстродействующий операционный усилитель, содержащий выход (1) устройства, инвертирующий вход (2) и неинвертирующий вход (3), первый (4) входной транзистор, база которого соединена с инвертирующим входом (2), а коллектор подключен к первой (5) шине источника питания, второй (6) входной транзистор, база которого соединена с инвертирующим входом (2) устройства, а коллектор подключен ко второй (7) шине источника питания, первый (8) выходной транзистор, коллектор которого соединен со входом первого (9) токового зеркала, согласованного со второй (7) шиной источника питания, второй (10) выходной транзистор, коллектор которого соединен со входом второго (11) токового зеркала, согласованного с первой (5) шиной источника питания, первый (12) и второй (13) согласующие транзисторы, первый (14) и второй (15) токостабилизирующие двухполюсники, отличающийся тем, что эмиттер первого (4) входного транзистора соединен с эмиттером первого (8) выходного транзистора, эмиттер второго (6) входного транзистора соединен с эмиттером второго (10) выходного транзистора, база первого (8) выходного транзистора связана с базой и коллектором первого (12) согласующего транзистора и через первый (14) источник опорного тока соединена со второй (7) шиной источника питания, база второго (10) выходного транзистора связана с базой и коллектором второго (13) согласующего транзистора и через второй (15) источник опорного тока соединена с первой (5) шиной источника питания, неинвертирующий вход (3) соединен с базой первого (16) дополнительного транзистора, эмиттер которого соединен с эмиттером первого (12) согласующего транзистора, а коллектор подключен к первой (5) шине источника питания, неинвертирующий вход (3) соединен с базой второго (17) дополнительного транзистора, эмиттер которого соединен с эмиттером второго (13) согласующего транзистора, а коллектор подключен ко второй (7) шине источника питания, причем между базами первого (8) и второго (10) выходных транзисторов включен дополнительный корректирующий конденсатор (18), а выход первого (9) токового зеркала соединен с выходом второго (11) токового зеркала и подключен к выходу устройства (1).

2. Быстродействующий операционный усилитель по п.1, отличающийся тем, что выход (1) устройства соединен со входом дополнительного буферного усилителя (20), выход которого (21) является потенциальным выходом устройства.

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2676014C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩЕЙ ЦЕПЬЮ КОРРЕКЦИИ | 2018 |

|

RU2669075C1 |

| US 6710654 B2, 23.03.2004 | |||

| US 6867649 B2, 15.03.2005. | |||

Авторы

Даты

2024-07-01—Публикация

2024-01-31—Подача