Изобретение относится к электронно-вычислительной технике, предназначено для синтеза многофазных сигналов и может использоваться в радиолокации, системах связи и телевидения.

Изобретение позволяет синтезировать когерентные фазомодулированные сигналы и сигналы с фазовой манипуляцией.

Известны цифровые синтезаторы частот, содержащие генератор тактовых импульсов и блок задержки, первый блок постоянного запоминания и счетчик с предварительной установкой, второй блок постоянного запоминания, второй регистр памяти, второй цифровой накопитель, первый регистр памяти, первый цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь, фильтр низких частот, выход которого является выходом цифрового синтезатора частот, а входами являются адресные входы первого и второго блоков постоянного запоминания [1].

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой вычислительный синтезатор с квадратурными выходами, содержащий последовательно соединенные опорный генератор и блок задержки, последовательно соединенные первый регистр памяти, первый цифровой накопитель, второй регистр памяти, второй цифровой накопитель, первый преобразователь кодов, первый цифроаналоговый преобразователь (ЦАП), первый фильтр низких частот (ФНЧ); третий регистр памяти и делитель с переменным коэффициентом деления; последовательно соединенные инвертор, второй преобразователь кодов, второй цифроаналоговый преобразователь и второй фильтр низких частот; входами цифрового синтезатора являются входы первого и второго регистров памяти, а выходами - выходы первого и второго фильтров низких частот [2]. Однако известные цифровые вычислительные синтезаторы не позволяют синтезировать многофазные сигналы.

Технический результат заключается в расширении функциональных возможностей цифровых синтезаторов и в возможности синтезирования многофазных частотно- и фазомодулированных сигналов.

Технический результат достигается за счет того, что цифровой синтезатор содержит последовательно соединенные первый регистр памяти, первый цифровой накопитель, второй цифровой накопитель, первый преобразователь кодов, первый цифроаналоговый преобразователь, первый фильтр низких частот; последовательно соединенные второй регистр памяти и делитель частоты с переменным коэффициентом деления; последовательно соединенные генератор тактовых импульсов и блок задержки; последовательно соединенные первый инвертор, второй цифроаналоговый преобразователь, второй фильтр низких частот; причем выход делителя частоты с переменным коэффициентом деления подключен к входу первого цифрового накопителя, выходы блока задержки подсоединены к тактовому входу делителя частоты с переменным коэффициентом деления, к тактовому входу первого и к тактовому входу второго цифровых накопителей, к тактовому входу первого и к тактовому входу второго цифроаналоговых преобразователей; старший разряд второго цифрового накопителя подключен к входу управления инверсией первого преобразователя кодов, при этом с выхода первого преобразователя кодов сигналы старших разрядов через инвертор поступают на информационные входы второго цифроаналогового преобразователя; первым и вторым входами цифрового синтезатора многофазных сигналов являются входы первого и второго регистров памяти, а первым и вторым выходами цифрового синтезатора многофазных сигналов - выходы первого и второго фильтров низких частот; причем новым является то, что введены последовательно соединенные третий регистр памяти, сумматор, второй преобразователь кодов, третий цифроаналоговый преобразователь, третий фильтр низких частот; последовательно соединенные второй инвертор, четвертый цифроаналоговый преобразователь, четвертый фильтр низких частот; кроме того, выход второго цифрового накопителя подключен к входу сумматора, а старший разряд сумматора подключен к входу управления инверсией второго преобразователя кодов; выход второго преобразователя кодов подключен к входу второго инвертора, выходы блока задержки подсоединены к тактовому входу третьего и к тактовому входу четвертого цифроаналоговых преобразователей, причем вход третьего регистра памяти является третьим входом цифрового синтезатора многофазных сигналов, а третьим и четвертым выходами цифрового синтезатора многофазных сигналов являются выходы третьего и четвертого фильтров низких частот.

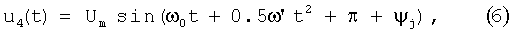

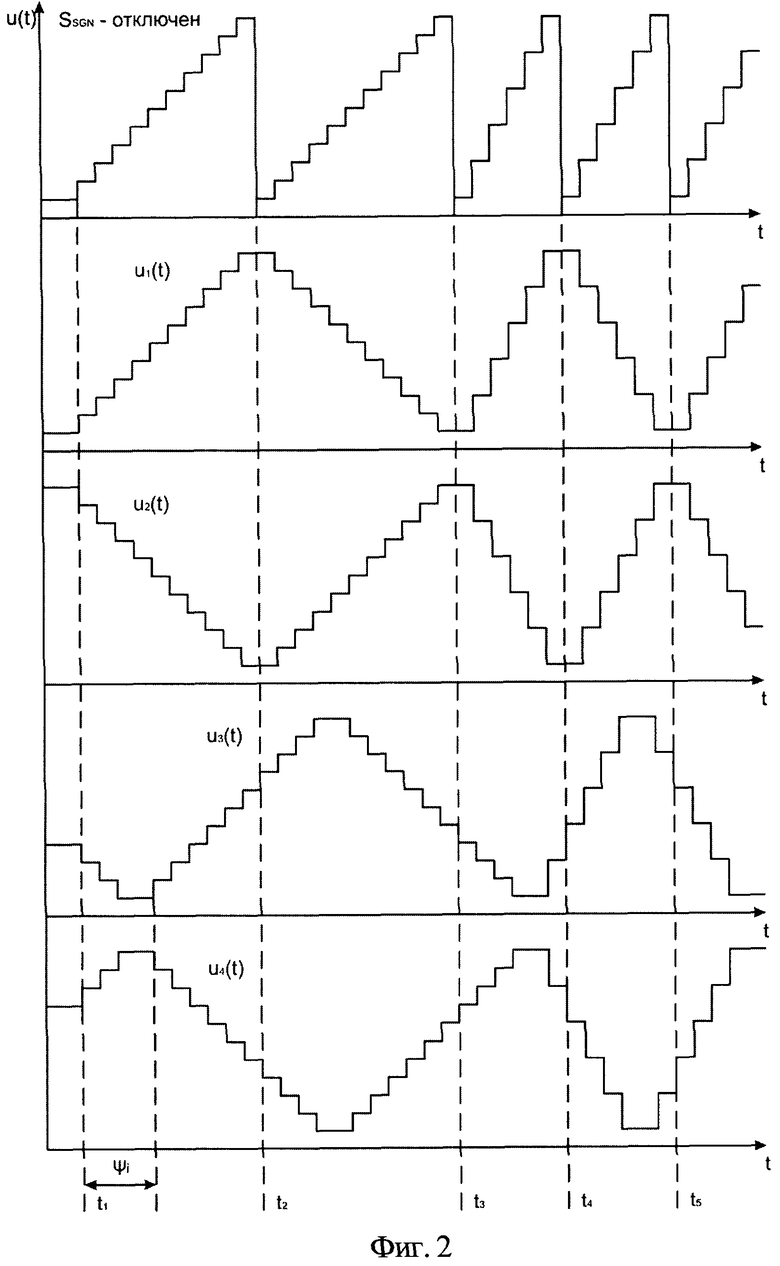

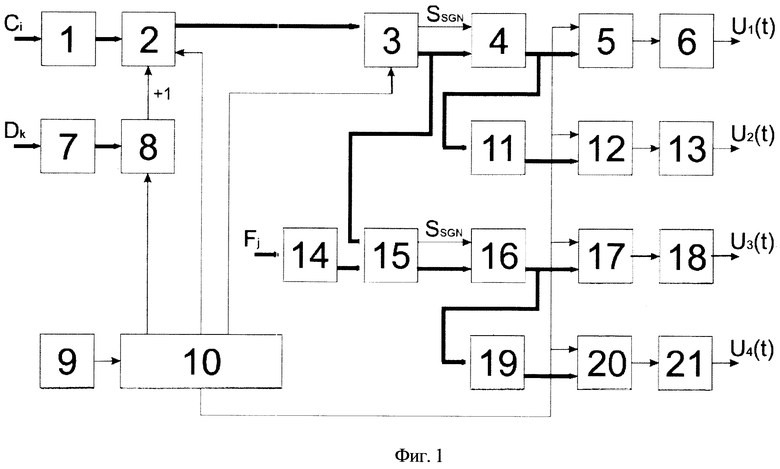

На фиг.1 приведена структурная схема цифрового синтезатора многофазных сигналов, на фиг.2 - графики выходных сигналов цифрового синтезатора многофазных сигналов.

Цифровой синтезатор многофазных сигналов (фиг.1) содержит первый регистр памяти 1, первый цифровой накопитель 2, второй цифровой накопитель 3, первый преобразователь кодов 4, первый цифроаналоговый преобразователь 5, первый фильтр низких частот 6, второй регистр памяти 7, делитель частоты с переменным коэффициентом деления 8, опорный генератор 9, блок задержки 10, первый инвертор 11, второй цифроаналоговый преобразователь 12, второй фильтр низких частот 13, третий регистр памяти 14, сумматор 15, второй преобразователь кодов 16, третий цифроаналоговый преобразователь 17, третий фильтр низких частот 18, второй инвертор 19, четвертый цифроаналоговый преобразователь 20, четвертый фильтр низких частот 21.

Цифровой синтезатор многофазных сигналов работает следующим образом. На вход первого регистра памяти 1 поступает код начальной частоты Сi, а на вход второго регистра памяти 7 - код Dk, определяющий коэффициент деления делителя с переменным коэффициентом деления 8 и, соответственно, скорость изменения частоты цифрового синтезатора многофазных сигналов.

Опорный генератор 9 выдает сигнал синусоидальной формы тактовой частоты, который поступает на вход блока задержки 10. Блок задержки формирует разнесенные во времени последовательности прямоугольных импульсов формы «меандр», которые поступают на соответствующие тактовые входы делителя с переменным коэффициентом деления 8, первого, второго, третьего и четвертого цифроаналоговых преобразователей 5, 12, 17, 20 и служат для синхронизации работы цифрового синтезатора многофазных сигналов.

С первым тактовым импульсом в момент времени t1 код начальной частоты Сi записывается из первого регистра памяти 1 в первый цифровой накопитель 2, а код коэффициента Dk из второго регистра памяти 7 записывается в делитель частоты с переменным коэффициентом деления 8, с выхода которого импульсы поступают на вход последовательного переноса первого цифрового накопителя кодов 2. Код Dk будет определять скорость изменения частоты синтезируемых сигналов. Чем больше код Dk, тем меньше скорость изменения частоты ω'.

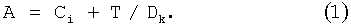

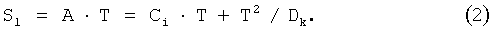

Затем с каждым тактовым импульсом код А на выходе первого цифрового накопителя 2 будет изменяться по закону:

Этот код А из первого цифрового накопителя 2 поступает на вход второго цифрового накопителя 3, результат суммирования в котором будет изменятся по формуле:

Старший разряд кода суммы SSGN является знаковым и поступает на вход управления инверсией первого преобразователя кодов 4. С выхода первого преобразователя кодов 4 остальные N старших разрядов (где N - разрядность цифроаналогового преобразователя) поступают на информационные входы первого ЦАП 5 и через инвертор 11 на информационные входы второго ЦАП 12.

Если сигнал SSGN=0, то на первый ЦАП 5 поступает прямой двоичный код суммы, а на второй ЦАП 12 - обратный двоичный код суммы. Если SSGN=1, то на первый ЦАП 5 поступает обратный двоичный код суммы, а на второй ЦАП 12 - прямой двоичный код суммы.

На выходах ЦАП 5 и 12 формируются ступенчатые сигналы «треугольной» формы, сдвинутые по фазе относительно друг друга на угол π. Фильтры низких частот 6 и 13 имеют частоты среза fср<fm/2, где fm - тактовая частота.

Фильтры низких частот пропускают только первую гармонику синтезированных сигналов.

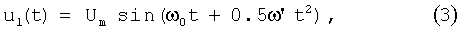

Если принять, что ω0=Сi - начальная циклическая частота, 0.5ω'=1/Dk - скорость изменения циклической частоты, Δt=T - длительность тактового интервала, то тогда на выходах фильтров низких частот 6 и 13 будут присутствовать сигналы, изменяющиеся по формулам:

где Um - амплитуда сигнала;

ω0 - начальная циклическая частота;

ω' - скорость изменения циклической частоты.

На вход третьего регистра памяти 14 поступает код фазового сдвига Fj, который подается на первый вход сумматора 15, а на второй вход этого сумматора 15 поступает сигнал с выхода второго накопителя кодов 3. Тогда на выходе сумматора 15 формируется двоичный код фазы сигнала, который изменяется по формуле:

С выхода сумматора 15 полученный код поступает на вход второго преобразователя кодов 16, причем старший разряд кода с выхода сумматора 15 поступает на вход управления инверсией второго преобразователя кодов 16.

С выхода второго преобразователя кодов 16 двоичный код поступает на вход третьего ЦАП 17 и на вход второго инвертора 19. Двоичный код с выхода второго инвертора 19 поступает на вход четвертого ЦАП 20, а сигналы с выходов третьего ЦАП 17 и четвертого ЦАП 20 поступают на входы третьего и четвертого фильтров низких частот 18 и 21 соответственно.

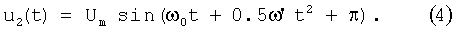

Если принять, что Fj=ψj, то сигналы на выходах третьего и четвертого фильтров низких частот 18, 21 будут описываться следующими формулами:

где ψj - угол фазового сдвига синтезируемых сигналов на выходах ФНЧ 6 и ФНЧ 18 (или на выходах ФНЧ 13 и ФНЧ 21 соответственно).

На выходах ЦАП 17 и 20 формируются ступенчатые сигналы «треугольной» формы, сдвинутые по фазе относительно друг друга на угол π. Фильтры низких частот 18 и 21 имеют частоты среза fср<fm/2, где fm - тактовая частота.

Таким образом, в цифровом синтезаторе многофазных сигналов формируются четыре когерентных частотно-модулированных сигнала, фазовый сдвиг между которыми можно задавать программно.

Литература

1. Патент РФ №2058659, МКИ Н03В 19/00. Цифровой синтезатор частот / Рябов И.В., Фищенко П.А. Заявл. 23.09.1993. Опубл. 20.04.1996. Бюл. №11.

2. Патент РФ №2294054, МПК 1103L 7/18. Цифровой вычислительный синтезатор с квадратурными выходами. Рябов И.В. Заявл. 25.10.2005. Опубл. 20.02.2007. Бюл. №5. (Прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР ПАРНЫХ СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 2022 |

|

RU2795263C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| ИЗМЕРИТЕЛЬНЫЙ ГЕНЕРАТОР ПАРНЫХ ИМПУЛЬСОВ | 2022 |

|

RU2788980C1 |

| Цифровой вычислительный синтезатор частотно-модулированных сигналов | 2019 |

|

RU2718461C1 |

| Цифровой синтезатор фазоманипулированных сигналов | 2019 |

|

RU2701050C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2580444C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2012 |

|

RU2490789C1 |

| Цифровой вычислительный синтезатор двухчастотных частотно-модулированных сигналов | 2024 |

|

RU2826705C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

Изобретение относится к электронно-вычислительной технике и предназначено для синтеза многофазных сигналов и может использоваться в радиолокации, системах связи и телевидения. Достигаемый технический результат - расширение функциональных возможностей. Цифровой синтезатор многофазных сигналов содержит первый регистр памяти 1, первый цифровой накопитель 2, второй цифровой накопитель 3, первый преобразователь кодов 4, первый цифроаналоговый преобразователь 5, первый фильтр низких частот 6, второй регистр памяти 7, делитель частоты с переменным коэффициентом деления 8, генератор тактовых импульсов 9, блок задержки 10, первый инвертор 11, второй цифроаналоговый преобразователь 12, второй фильтр низких частот 13, третий регистр памяти 14, сумматор 15, второй преобразователь кодов 16, третий цифроаналоговый преобразователь 17, третий фильтр низких частот 18, второй инвертор 19, четвертый цифроаналоговый преобразователь 20, четвертый фильтр низких частот 21. 2 ил.

Цифровой синтезатор многофазных сигналов, содержащий последовательно соединенные первый регистр памяти, первый цифровой накопитель, второй цифровой накопитель, первый преобразователь кодов, первый цифроаналоговый преобразователь, первый фильтр низких частот; последовательно соединенные второй регистр памяти и делитель частоты с переменным коэффициентом деления; последовательно соединенные генератор тактовых импульсов и блок задержки; последовательно соединенные первый инвертор, второй цифроаналоговый преобразователь, второй фильтр низких частот; причем выход делителя частоты с переменным коэффициентом деления подключен к входу первого цифрового накопителя, выходы блока задержки подсоединены к тактовому входу делителя частоты с переменным коэффициентом деления, к тактовому входу первого и к тактовому входу второго цифровых накопителей, к тактовому входу первого и к тактовому входу второго цифроаналоговых преобразователей; старший разряд второго цифрового накопителя подключен к входу управления инверсией первого преобразователя кодов, при этом с выхода первого преобразователя кодов сигналы старших разрядов через инвертор поступают на информационные входы второго цифроаналогового преобразователя; первым и вторым входами цифрового синтезатора многофазных сигналов являются входы первого и второго регистров памяти, а первым и вторым выходами цифрового синтезатора многофазных сигналов - выходы первого и второго фильтров низких частот, отличающийся тем, что введены последовательно соединенные третий регистр памяти, сумматор, второй преобразователь кодов, третий цифроаналоговый преобразователь, третий фильтр низких частот; последовательно соединенные второй инвертор, четвертый цифроаналоговый преобразователь, четвертый фильтр низких частот; кроме того, выход второго цифрового накопителя подключен к входу сумматора, а старший разряд сумматора подключен к входу управления инверсией второго преобразователя кодов; выход второго преобразователя кодов подключен к входу второго инвертора, выходы блока задержки подсоединены к тактовому входу третьего и тактовому входу четвертого цифроаналоговых преобразователей, причем вход третьего регистра памяти является третьим входом цифрового синтезатора многофазных сигналов, а третьим и четвертым выходами цифрового синтезатора многофазных сигналов являются выходы третьего и четвертого фильтров низких частот.

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2149503C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

| US 5235531 A, 10.08.1993 | |||

| US 5070310, 03.12.1991. | |||

Авторы

Даты

2011-07-10—Публикация

2010-03-25—Подача