Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза частотно-модулированных сигналов и может быть использовано в радиолокации, навигации и современных адаптивных системах связи.

Известны цифровые синтезаторы частот, содержащие два блока постоянного запоминания цифровой накопитель, умножитель кодов, счетчик с предварительной установкой, преобразователь кодов, регистр памяти, цифроаналоговый преобразователь, фильтр нижних частот, генератор тактовых импульсов, блок задержки [1].

Наиболее близким техническим решением (прототипом) является цифровой синтезатор частот, содержащий генератор тактовых импульсов, блок задержки, блок постоянного запоминания, счетчик с предварительной установкой, умножитель кодов, цифровой накопитель, цифроаналоговый преобразователь, фильтр нижних частот, регистр памяти [2].

Однако, известные цифровые синтезаторы частот не обладают высокой скоростью перестройки частоты и имеют ограниченные функциональные возможности при формировании сигналов с линейной частотной модуляции.

Технический результат - повышение скорости перестройки частоты - достигается тем, что в цифровой вычислительный синтезатор, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; второй регистр памяти, вход которого является цифровым входом цифрового вычислительного синтезатора; последовательно соединенные первый счетчик, умножитель кодов, цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом цифрового вычислительного синтезатора; выходы блока формирования и задержки подключены к тактовым входам множимого, множителя и произведения умножителя кодов, а также к тактовым входам цифрового накопителя и цифроаналогового преобразователя, причем новым является то, что введены первый и третий регистр памяти, второй счетчик, делитель с переменным коэффициентом деления, при этом цифровыми входами цифрового вычислительного синтезатора являются входы первого и третьего регистров памяти; выход первого регистра памяти подключен к входу первого счетчика; выход второго регистра памяти подключен к входу второго счетчика, а выход второго счетчика подключен к входу множителя умножителя кодов; выход третьего регистра памяти подсоединен к входу делителя с переменным коэффициентом деления, выход последнего подключен к тактовому входу второго счетчика; выходы блока формирования и задержки подключены к соответствующим тактовым входам первого счетчика, делителя с переменным коэффициентом деления.

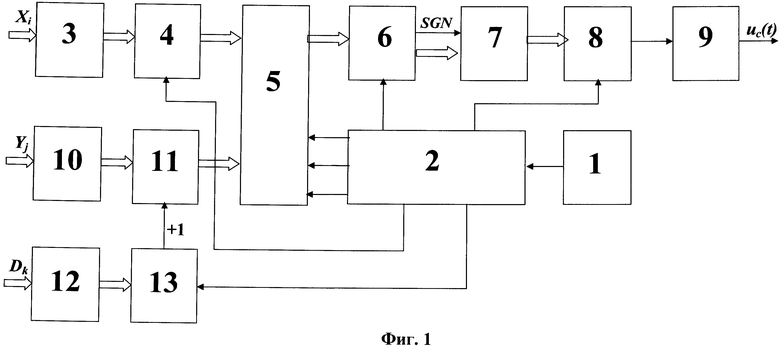

Цифровой вычислительный синтезатор содержит эталонный генератор 1 и блок формирования и задержки 2, первый регистр памяти 3, первый счетчик 4, умножитель кодов 5, цифровой накопитель 6, преобразователь кодов 7, цифроаналоговый преобразователь (ЦАП) 8, фильтр нижних частот (ФНЧ) 9, выход которого является аналоговым выходом цифрового вычислительного синтезатора, второй регистр памяти 10, второй счетчик 11, третий регистр памяти 12, делитель с переменным коэффициентом деления 13; входы первого, второго и третьего регистров памяти являются цифровыми входами цифрового вычислительного синтезатора.

Цифровой вычислительный синтезатор содержит последовательно соединенные эталонной генератор 1 и блок формирования и задержки 2; последовательно соединенные первый регистр памяти 3, первый счетчик 4, умножитель кодов 5, цифровой накопитель 6, преобразователь кодов 7, цифроаналоговый преобразователь 8 и фильтр нижних частот 9, выход которого является аналоговым выходом цифрового вычислительного синтезатора; последовательно соединенные второй регистр памяти 10 и второй счетчик 11, выход которого подключен к входу множителя умножителя кодов 5; последовательно соединенные третий регистр памяти 12 и делитель с переменным коэффициентом деления 13, выход последнего подключен к тактовому входу первого счетчика 11; выходы блока формирования и задержки 2 подключены к соответствующим тактовым входам множимого, множителя и произведения умножителя кодов 5, цифрового накопителя 6, цифроаналогового преобразователя 8, первого счетчика 4, делителя с переменным коэффициентом деления 13; цифровыми входами цифрового вычислительного синтезатора являются входы первого, второго и третьего регистров памяти 3, 10 и 12.

Цифровой вычислительный синтезатор работает следующим образом: Эталонный генератор 1 вырабатывает синусоидальный сигнал тактовой частоты, из которого в блоке формирования и задержки 2 формируются тактовые импульсы формы «меандр», разнесенные во времени и служащие для синхронизации работы цифрового вычислительного синтезатора.

На входы первого регистра памяти 3 поступает код Xi (код множимого), на вход второго регистра памяти 10 поступает код Yj (код множителя), на вход третьего регистра памяти 12 поступает код Dk.

Эти коды записываются соответственно: код Xi - в первый счетчик 4, код Yj - во второй счетчик 11, код Dk - в делитель с переменным коэффициентом деления 13.

С первым тактовым импульсом в момент t1 коды Xi и Yj поступают на входы множимого и множителя умножителя кодов 5.

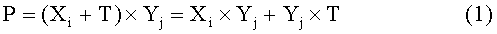

Начиная со второго тактового импульса - момент t2 и далее код произведения (код частоты) в умножителе кодов будет изменяться по формуле:

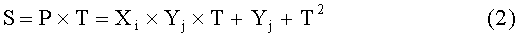

Код суммы в цифровом накопителе 6 (код фазы) будет изменяться по формуле:

Если ввести обозначения

ω0=Xi×Yj - начальная циклическая частота;

ω'=0.5Yj - скорость изменения частоты;

T=Δt - тактовый интервал,

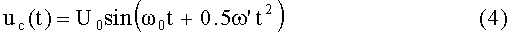

то фаза синтезируемого сигнала ЦВС будет описываться формулой:

Код фазы φi поступает на преобразователь кодов 7, причем старший разряд SGN, являющийся знаковым, поступает на вход управления инверсией преобразователя кодов 7, а остальные разряды через преобразователь кодов 7 поступают на информационные входы ЦАП 8.

Если SGN=0, то на ЦАП 8 поступает прямой код фазы, а если SGN=1, то на ЦАП 8 поступает обратный код фазы.

В ЦАП 8 формируется «ступенчатый» сигнал «треугольной» формы. После фильтрации в ФНЧ 9, который имеет частоту среза, равную половину тактовой частоты, на выходе ЦВС формируется сигнал с линейной частотной модуляцией:

Делитель с переменным коэффициентом деления 13 служит для управления скоростью изменения частоты, чем больше код Dk, тем меньше скорость изменения частоты.

В предлагаемом цифровом вычислительном синтезаторе имеется возможность дополнительно управлять частотой выходного сигнала, например, передавать информационное сообщение в режиме ЛЧМ, изменяя код множителя Yj.

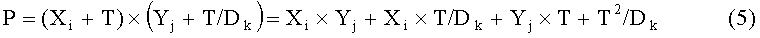

Данный ИБС позволяет формировать сигнал с квадратичным законом изменения частоты. Если запустить оба счетчика, то в первом счетчике код будет изменяться по формуле: Х=Xi+Т,

а во втором счетчике по формуле: Y=Yj+T/Dk

Тогда частота сигнала будет изменяться по формуле:

При этом фаза синтезируемого сигнала будет изменяться по формуле:

Таким образом, данный цифровой вычислительный синтезатор обладает более широкими функциональными возможностями и позволяет формировать сигналы с линейным и квадратичным законом изменения частоты, а также имеется возможность передавать информационное сообщение в режиме ЛЧМ.

Литература

1. А.с. СССР №1774464. МКИ H03B 19/00. Цифровой синтезатор частот / Рябов И.В., Рябова Н.В., Урядов В.П.. Заявл. 30.08.1990. Опубл. 07.11.1992. Бюл. №41. - 4 с.

2. Патент РФ №2143173. МПК H03L 7/18, H03B 19/00. Цифровой синтезатор частот / Рябов И.В., Рябов В.И. Заявл. 04.02.1999. Опубл. 20.12.1999. Бюл. №35. - 6 с. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 1999 |

|

RU2143173C1 |

| Цифровой синтезатор частот с высокой линейностью закона изменения частоты | 2016 |

|

RU2635278C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| Цифровой вычислительный синтезатор частотно-модулированных сигналов | 2019 |

|

RU2718461C1 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР | 2005 |

|

RU2286645C1 |

| Цифровой синтезатор фазоманипулированных сигналов | 2019 |

|

RU2701050C1 |

| Цифровой синтезатор частот | 1990 |

|

SU1774464A1 |

| Цифровой вычислительный синтезатор двухчастотных частотно-модулированных сигналов | 2024 |

|

RU2826705C1 |

| Цифровой синтезатор с М-образным законом изменения частоты | 2017 |

|

RU2682847C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204196C2 |

Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для синтеза частотно-модулированных сигналов и может быть использовано в радиолокации, навигации и современных адаптивных системах связи. Технический результат заключается в повышении скорости перестройки рабочей частоты. Цифровой вычислительный синтезатор содержит эталонный генератор 1 и блок формирования и задержки 2, первый регистр памяти 3, первый счетчик 4, умножитель кодов 5, цифровой накопитель 6, преобразователь кодов 7, цифроаналоговый преобразователь (ЦАП) 8, фильтр нижних частот (ФНЧ) 9, выход которого является аналоговым выходом цифрового вычислительного синтезатора, второй регистр памяти 10, второй счетчик 11, третий регистр памяти 12, делитель с переменным коэффициентом деления 13; входы первого, второго и третьего регистров памяти являются цифровыми входами цифрового вычислительного синтезатора. 1 ил.

Цифровой вычислительный синтезатор, содержащий последовательно соединенные эталонный генератор и блок формирования и задержки; второй регистр памяти, вход которого является цифровым входом цифрового вычислительного синтезатора; последовательно соединенные первый счетчик, умножитель кодов, цифровой накопитель, преобразователь кодов, цифроаналоговый преобразователь и фильтр нижних частот, выход которого является аналоговым выходом цифрового вычислительного синтезатора; выходы блока формирования и задержки подключены к тактовым входам множимого, множителя и произведения умножителя кодов, а также к тактовым входам цифрового накопителя и цифроаналогового преобразователя, отличающийся тем, что введены первый и третий регистр памяти, второй счетчик, делитель с переменным коэффициентом деления, при этом цифровыми входами цифрового вычислительного синтезатора являются входы первого и третьего регистров памяти; выход первого регистра памяти подключен к входу первого счетчика; выход второго регистра памяти подключен к входу второго счетчика, а выход второго счетчика подключен к входу множителя умножителя кодов; выход третьего регистра памяти подсоединен к входу делителя с переменным коэффициентом деления, выход последнего подключен к тактовому входу второго счетчика; выходы блока формирования и задержки подключены к соответствующим тактовым входам первого счетчика, делителя с переменным коэффициентом деления.

| ПАРАЛЛЕЛЬНЫЙ КОРОТКОВОЛНОВЫЙ МОДЕМ | 2004 |

|

RU2286648C2 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР С КВАДРАТУРНЫМИ ВЫХОДАМИ | 2005 |

|

RU2294054C1 |

| US 4349897, 14.09.1982 | |||

| Станок для скручивания концов проволок у панцирных сеток | 1959 |

|

SU125790A1 |

Авторы

Даты

2013-08-27—Публикация

2012-07-03—Подача