Область техники

Изобретение относится к области радиотехники и электроники и может быть использовано в качестве источника тока или высокоомной нагрузки усилителя в структуре аналоговых микросхем и блоков различного функционального назначения.

Уровень техники

Развитие современной микроэлектроники сопровождается уменьшением размеров элементов микросхем и снижением напряжения питания. При этом в КМОП-микросхемах снижается выходное сопротивление транзисторов и коэффициент усиления аналоговых блоков.

Традиционным способом повышения коэффициента усиления является последовательное (каскодное) включение МОП-транзисторов с подачей на их затворы разного напряжения смещения [1,2]. Однако при каскодном включении транзисторов повышается минимальное выходное напряжение на последовательно включенных транзисторах, что ограничивает динамический диапазон выходного сигнала.

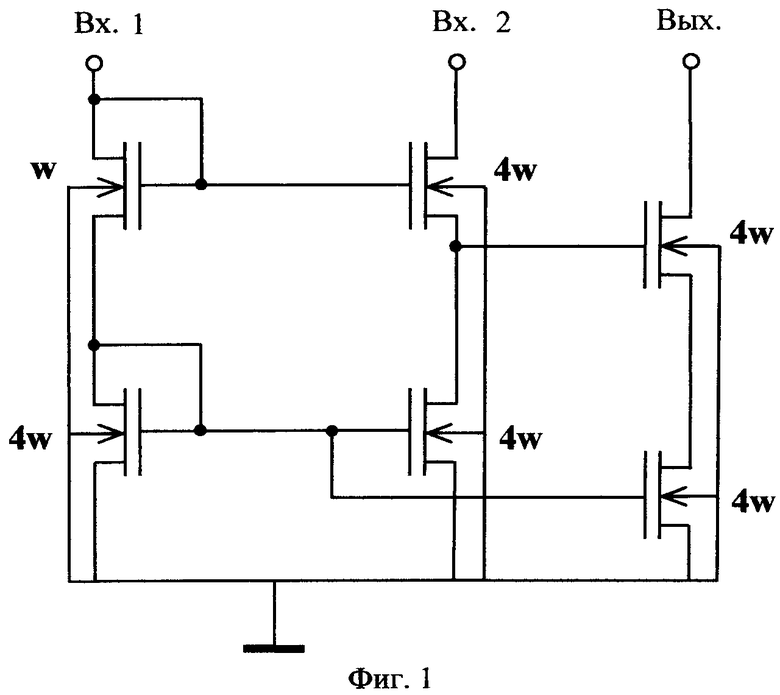

Известно техническое решение [3], где во входной цепи токового зеркала используются два каскада для независимого смещения затворов транзисторов в выходной цепи. При этом разность напряжений на затворах МОП-транзисторов в выходной цепи определяются разностью ширины транзисторов (w) в двух каскадах входной цепи (фиг.1).

К недостаткам данного технического решения можно отнести высокое входное напряжение; увеличение числа элементов в схеме, а также снижение точности передачи тока из входной цепи токового зеркала в выходную за счет разных режимов работы транзисторов.

Раскрытие изобретения

Задачей предлагаемого изобретения является понижение минимального выходного напряжения токового зеркала при сохранении высокого выходного сопротивления. Техническим результатом, позволяющим выполнить поставленную задачу, является снижение напряжения питания или увеличение динамического диапазона выходного сигнала аналогового блока токового зеркала за счет использования в каскодной цепи МОП-транзисторов с разным пороговым напряжением.

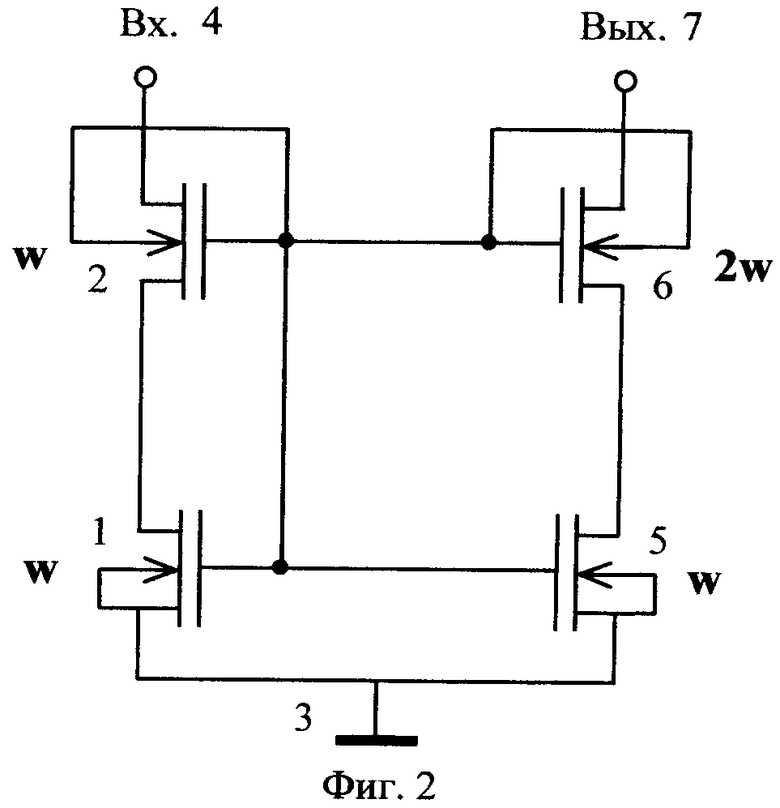

Согласно изобретению этот технический результат достигается за счет того, что в токовом зеркале с пониженным выходным напряжением (фиг.2), включающем первый (1) и второй (2) входные МОП-транзисторы, включенные последовательно между шиной питания (3) и входом токового зеркала (4), а также первый (5) и второй (6) выходные МОП-транзисторы, включенные последовательно между шиной питания (3) и выходом токового зеркала (7); истоки и изолирующие «карманы» первого входного (1) и первого выходного (5) МОП-транзисторов соединены с шиной питания (3); затворы всех МОП-транзисторов и изолирующие карманы второго входного (2) и второго выходного (6) МОП-транзисторов подключены к входу токового зеркала.

Первый выходной (5) и первый входной (1) МОП-транзисторы реализованы топологически в виде блока параллельно соединенных секций минимальной ширины (w), при этом их пороговое напряжение возрастает.

Дополнительно разница пороговых напряжений МОП-транзисторов увеличивается благодарят использованию изолирующих «карманов» с повышенным уровнем легирования.

Повышенное выходное сопротивление токового зеркала достигается за счет увеличения напряжения на стоке первого выходного МОП-транзистора (5) до уровня перехода в пологую область выходной вольтамперной характеристики. Значение этого напряжения равно разнице напряжений затвор-исток первого (5) и второго (6) выходных МОП-транзисторов. Эта разница напряжений складывается из разности пороговых напряжений, влияния положительного смещения изолирующего кармана и вдвое более высокой плотности тока в первом выходном МОП-транзисторе (5).

Краткое описание чертежей

На фиг.1 представлена схема токового зеркала с пониженным выходным напряжением на основе одинаковых МОП-транзисторов (w - минимальная ширина используемых МОП-транзисторов).

На фиг.2 представлена схема токового зеркала с пониженным выходным напряжением на основе МОП-транзисторов с разными пороговыми напряжениями (w - минимальная ширина используемых МОП-транзисторов).

Осуществление изобретения

Основная задача предлагаемого изобретения состоит в уменьшении числа элементов в схеме и повышении точности передачи тока токового зеркала при сохранении высокого выходного сопротивления и низкого выходного напряжения.

Поставленная задача решается тем, что в схеме каскодного токового зеркала использованы МОП-транзисторы с разным пороговым напряжением [4]. Первый входной (1) и первый выходной (5) МОП-транзисторы имеют увеличенное по модулю пороговое напряжение, а второй входной (2) и второй выходной (6) МОП-транзисторы - уменьшенное по модулю пороговое напряжение.

Входные первый (1) и второй (2) транзисторы включены последовательно между шиной питания (3) и входом токового зеркала (4). Выходные первый (5) и второй (6) транзисторы включены последовательно между шиной питания (3) и выходом токового зеркала (7). Истоки и изолирующие карманы первого выходного (5) и первого входного (1) транзисторов подключены к шине питания (3). Затворы всех МОП-транзисторов и изолирующие карманы второго входного (2) и второго выходного (6) транзисторов подключены к входу токового зеркала (4). Такое включение уменьшает напряжение затвор-исток второго входного (2) и второго выходного (6) МОП-транзисторов и увеличивает напряжение сток-исток первого входного (1) и первого выходного (5) транзисторов.

Увеличение по модулю величины порогового напряжения первого входного (1) и первого выходного (5) МОП-транзисторов достигается их реализацией в форме блока параллельно включенных транзисторов минимальной ширины (w), а уменьшение порогового напряжения - объединением электродов затвора и изолирующего «кармана» [4]. Топологическое и схемотехническое изменения порогового напряжения не требуют изменения технологии производства микросхем.

Дополнительное увеличение разницы пороговых напряжений МОП-транзисторов может быть достигнуто применением изолирующих «карманов» с разным уровнем легирования.

За счет того, что пороговое напряжение второго входного (2) и второго выходного (6) транзисторов меньше по модулю, чем у первого входного (1) и первого выходного (5) транзисторов, напряжение в точках последовательного соединения входных и выходных транзисторов увеличивается и достигает уровня, при котором выходные вольтамперные характеристики первого входного (1) и первого выходного (5) транзисторов переходят в область с высоким сопротивлением.

Согласно литературным источникам [1] реально используются режимы работы токового зеркала с выходным напряжением не менее 0,1 В. Следовательно разница пороговых напряжений МОП-транзисторов должна быть больше 0,1 В. Предложенное решение позволяет снизить минимальное выходное напряжение каскодного токового зеркала до 0,2 В без снижения выходного сопротивления.

Предлагаемое в качестве изобретения техническое решение обеспечивает возможность снижения напряжения питания аналоговых блоков, в том числе и в микросхемах на основе нанометровых КМОМ-технологий.

Реализуемость изобретения подтверждается результатами моделирования характеристик токового зеркала с использованием практически проверенных методик, лицензированных программных средств (Spectre Cadence) и верифицированных моделей элементов (Silterra Microelectronics).

[1] S.Chatterjee, К.Pun, N.Stanic', Y.Tsividis, P Kinget. Analog Circuit Design Techniques at 0.5 V. Springer, 2007.

[2] Эннс В.И., Кобзев Ю.М. Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика / Под редакцией канд. техн. наук В.И. Эннса. - М.: Горячая линия - Телеком. - 2005. - 454 с.: ил.

[3] P.Е.Allen, D.R.Holberg. CMOS Analog Circuit Design. New York, Oxford, Oxford University Press, 1996.

[4] A.M.Walke, N.M.Mohapatra. Effects of Small Geometries on the Performance of Gate First High-k Metal Gate NMOS Transistors. IEEE Transactions on Electron Devices. V. 59, N. 10, 2012.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫСОКОЧАСТОТНЫЙ УСИЛИТЕЛЬ С УСТРОЙСТВОМ СТАБИЛИЗАЦИИ ТОКА КОЛЛЕКТОРА ГЕТЕРОСТРУКТУРНОГО БИПОЛЯРНОГО ТРАНЗИСТОРА | 2012 |

|

RU2497271C1 |

| НИЗКОВОЛЬТНОЕ КМОП ТОКОВОЕ ЗЕРКАЛО | 2013 |

|

RU2544780C1 |

| ЭНЕРГОЭФФЕКТИВНЫЙ НИЗКОВОЛЬТНЫЙ КМОП-ТРИГГЕР | 2015 |

|

RU2611236C1 |

| СХЕМА СЧИТЫВАНИЯ СИГНАЛОВ ИЗ ЯЧЕЕК МАТРИЦЫ ФОТОДЕТЕКТОРОВ | 2008 |

|

RU2356177C1 |

| УСТРОЙСТВО ЗАЩИТЫ ВЫВОДОВ ИНТЕГРАЛЬНЫХ СХЕМ СО СТРУКТУРОЙ МДП ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2005 |

|

RU2308146C2 |

| СХЕМА СЧИТЫВАНИЯ СИГНАЛОВ ИЗ ЯЧЕЕК МАТРИЦЫ ФОТОДЕТЕКТОРОВ | 2007 |

|

RU2343588C1 |

| ОБНАРУЖЕНИЕ ЗАРЯДА ИЛИ ЧАСТИЦЫ | 2003 |

|

RU2339973C2 |

| РАДИАЦИОННО-СТОЙКИЙ И НИЗКОТЕМПЕРАТУРНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2020 |

|

RU2741056C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720557C1 |

| ШИРОКОДИАПАЗОННЫЙ ГЕНЕРАТОР, УПРАВЛЯЕМЫЙ НАПРЯЖЕНИЕМ | 2007 |

|

RU2330377C1 |

Изобретение относится к области радиотехники и электроники и может быть использовано в качестве источника тока или высокоомной нагрузки усилителя в структуре аналоговых микросхем и блоков различного функционального назначения. Достигаемый технический результат - повышение точности передачи тока при сохранении высокого выходного сопротивления и низкого выходного напряжения. Токовое зеркало с пониженным выходным напряжением содержит первый и второй входные МОП-транзисторы, включенные последовательно между шиной питания и входом токового зеркала, а также первый и второй выходные МОП-транзисторы, включенные последовательно между шиной питания и выходом токового зеркала, истоки и изолирующие карманы первого входного и первого выходного МОП-транзисторов соединены с шиной питания, а затворы всех МОП-транзисторов и изолирующие карманы второго входного и второго выходного МОП-транзисторов подключены к входу токового зеркала. 2 з.п. ф-лы, 2 ил.

1. Токовое зеркало с пониженным выходным напряжением, включающее первый и второй входные МОП-транзисторы, включенные последовательно между шиной питания и входом токового зеркала, а также первый и второй выходные МОП-транзисторы, включенные последовательно между шиной питания и выходом токового зеркала; истоки и изолирующие «карманы» первого входного и первого выходного МОП-транзисторов соединены с шиной питания, отличающееся тем, что затворы всех МОП-транзисторов и изолирующие карманы второго входного и второго выходного МОП-транзисторов подключены к входу токового зеркала.

2. Токовое зеркало с пониженным выходным напряжением по п.1, отличающееся тем, что первый выходной и первый входной МОП-транзисторы конструктивно реализованы в виде блока параллельно соединенных секций минимальной ширины.

3. Токовое зеркало с пониженным выходным напряжением по п.1, отличающееся тем, что разница пороговых напряжений МОП-транзисторов достигается использованием изолирующих «карманов» с разным уровнем легирования.

| ТОКОВОЕ ЗЕРКАЛО | 2011 |

|

RU2474954C1 |

Авторы

Даты

2015-02-27—Публикация

2013-06-04—Подача