Предлагаемое изобретение относится к области радиотехники и аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах (активных RC-фильтрах, нормирующих преобразователях и т.п.), работающих в условиях низких температур и воздействия радиации.

В современной микроэлектронике достаточно популярны архитектуры двухкаскадных ОУ на КМОП транзисторах [1-11], содержащие входной дифференциальный каскад, токовое зеркало и буферный усилитель. Причем в качестве входных КМОП транзисторов могут использоваться КМОП как с p-каналами [1-7] так и с n-каналами [8-11].

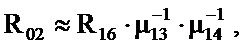

Ближайшим прототипом заявляемого устройства является операционный усилитель, представленный в патенте US 6.342.814 (2002 г., fig. 1). Он содержит первый 1 и второй 2 входы устройства, выход 3 устройства, первый 4 входной полевой транзистор, затвор которого подключен к первому 1 входу устройства, второй 5 входной полевой транзистор, затвор которого подключен ко второму 2 входу устройства, а исток соединен с истоком первого 4 входного полевого транзистора, источник опорного тока 6, включенный между первой 7 шиной источника питания и объединенными истоками первого 4 и второго 5 входных полевых транзисторов, активную динамическую нагрузку 8, согласованную со второй 9 шиной источника питания, которая связана со стоком второго 5 входного полевого транзистора и входом буферного усилителя 10, выход которого является выходом 3 устройства.

Существенный недостаток ОУ-прототипа, который относится к числу классических схем современной микроэлектроники, состоит в том, что при его практической реализации по JFet (не КМОП) технологиям в нем не обеспечивается малое напряжение смещения нуля Uсм. Кроме этого, известная КМОП схема при её построении на JFet не позволяет получить высокие значения коэффициента усиления по напряжению и коэффициента ослабления входных синфазных сигналов. Вышеназванные недостатки обусловлены отсутствием в современной микросхемотехнике качественных JFet токовых зеркал, что связано с особенностью работы JFet транзисторов, у которых полярность напряжения исток-затвор противоположна полярности напряжения исток-сток.

Основная задача предлагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного JFet операционного усилителя без управляемых токовых зеркал, который обеспечивает малые значения систематической составляющей напряжения смещения нуля (Uсм), а также повышенные коэффициент усиления (Ку) по напряжению и коэффициент ослабления входных синфазных сигналов (Кос.сф).

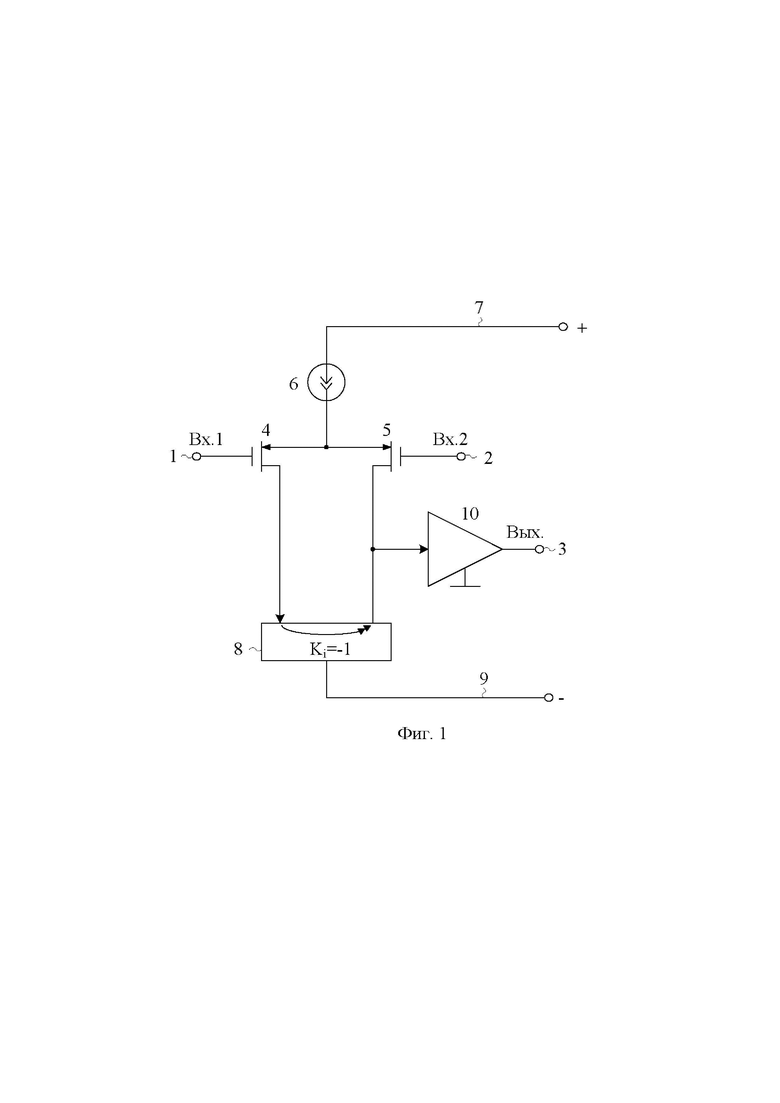

Поставленная задача достигается тем, что в ОУ фиг. 1, содержащем первый 1 и второй 2 входы устройства, выход 3 устройства, первый 4 входной полевой транзистор, затвор которого подключен к первому 1 входу устройства, второй 5 входной полевой транзистор, затвор которого подключен ко второму 2 входу устройства, а исток соединен с истоком первого 4 входного полевого транзистора, источник опорного тока 6, включенный между первой 7 шиной источника питания и объединенными истоками первого 4 и второго 5 входных полевых транзисторов, активную динамическую нагрузку 8, согласованную со второй 9 шиной источника питания, которая связана со стоком второго 5 входного полевого транзистора и входом буферного усилителя 10, выход которого является выходом 3 устройства, предусмотрены новые элементы и связи - в качестве первого 4 и второго 5 входных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом, источник опорного тока 6 содержит первый 11, второй 12, третий 13 и четвертый 14 дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор первого 11 дополнительного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого 4 и второго 5 входных полевых транзисторов с управляющим p-n переходом, исток первого 11 дополнительного полевого транзистора с управляющим p-n переходом соединен с затвором второго 12 дополнительного полевого транзистора с управляющим p-n переходом и связан с объединенными истоками первого 4 и второго 5 входных полевых транзисторов с управляющим p-n переходом через первый 15 дополнительный резистор, сток первого 11 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком второго 12 дополнительного полевого транзистора с управляющим p-n переходом, сток второго 12 дополнительного полевого транзистора с управляющим p-n переходом подключен к первой 7 шине источника питания, затвор третьего 13 дополнительного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого 4 и второго 5 входных полевых транзисторов с управляющим p-n переходом, исток третьего 13 дополнительного полевого транзистора с управляющим p-n переходом соединен с затвором четвертого 14 дополнительного полевого транзистора с управляющим p-n переходом и связан с объединенными истоками первого 4 и второго 5 входных полевых транзисторов с управляющим p-n переходом через второй 16 дополнительный резистор, сток третьего 13 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком четвертого 14 дополнительного полевого транзистора с управляющим p-n переходом, сток четвертого 14 дополнительного полевого транзистора с управляющим p-n переходом подключен к первой 7 шине источника питания, первый 4 входной полевой транзистор с управляющим p-n переходом выполнен в виде каскодного составного транзистора, содержащего пятый 17 и шестой 18 дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор пятого 17 дополнительного полевого транзистора с управляющим p-n переходом соединен с первым 1 входом устройства, сток пятого 17 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком шестого 18 дополнительного полевого транзистора с управляющим p-n переходом, сток шестого 18 дополнительного полевого транзистора с управляющим p-n переходом связан со второй 9 шиной источника питания, второй 5 входной полевой транзистор с управляющим p-n переходом выполнен в виде каскодного составного транзистора, содержащего шестой 18, седьмой 19 и восьмой 20 дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор седьмого 19 дополнительного полевого транзистора с управляющим p-n переходом соединен со вторым 2 входом устройства, сток седьмого 19 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком восьмого 20 дополнительного полевого транзистора с управляющим p-n переходом, затворы шестого 18 и восьмого 20 дополнительных полевых транзисторов с управляющим p-n переходом соединены с объединенными истоками пятого 17 и седьмого 19 дополнительных полевых транзисторов с управляющим p-n переходом, сток восьмого 20 дополнительного полевого транзистора с управляющим p-n переходом подключен ко входу буферного усилителя 10, выход которого является выходом 3 устройства, активная динамическая нагрузка 8 выполнена в виде неуправляемой активной динамической нагрузки, содержащей девятый 21 и десятый 22 дополнительные полевые транзисторы с управляющим p-n переходом, причем сток десятого 22 дополнительного полевого транзистора с управляющим p-n переходом подключен ко входу буферного усилителя 10, исток десятого 22 дополнительного полевого транзистора с управляющим p-n переходом соединен со стоком девятого 21 дополнительного полевого транзистора с управляющим p-n переходом, затвор десятого 22 дополнительного полевого транзистора с управляющим p-n переходом связан с истоком девятого 21 дополнительного полевого транзистора с управляющим p-n переходом и подключен ко второй 9 шине источника питания через третий 23 дополнительный резистор, а затвор девятого 21 дополнительного полевого транзистора с управляющим p-n переходом связан со второй 9 шиной источника питания.

На чертеже фиг. 1 представлена схема ОУ-прототипа по патенту US 6342814 (2002 г., fig. 1), а на чертеже фиг. 2 - схема заявляемого ОУ в соответствии с п. 1 и п. 2 формулы изобретения.

На чертеже фиг. 3 показана схема заявляемого ОУ фиг. 2 с конкретным выполнением буферного усилителя 10 на основе вспомогательных транзисторов 25, 27, 28, 29 и пассивных элементов 26 и 30.

На чертеже фиг. 4 приведена схема заявляемого ОУ фиг. 2 с конкретным выполнением буферного усилителя 10 на основе вспомогательных транзисторов 32, 35 и резисторов 33, 34.

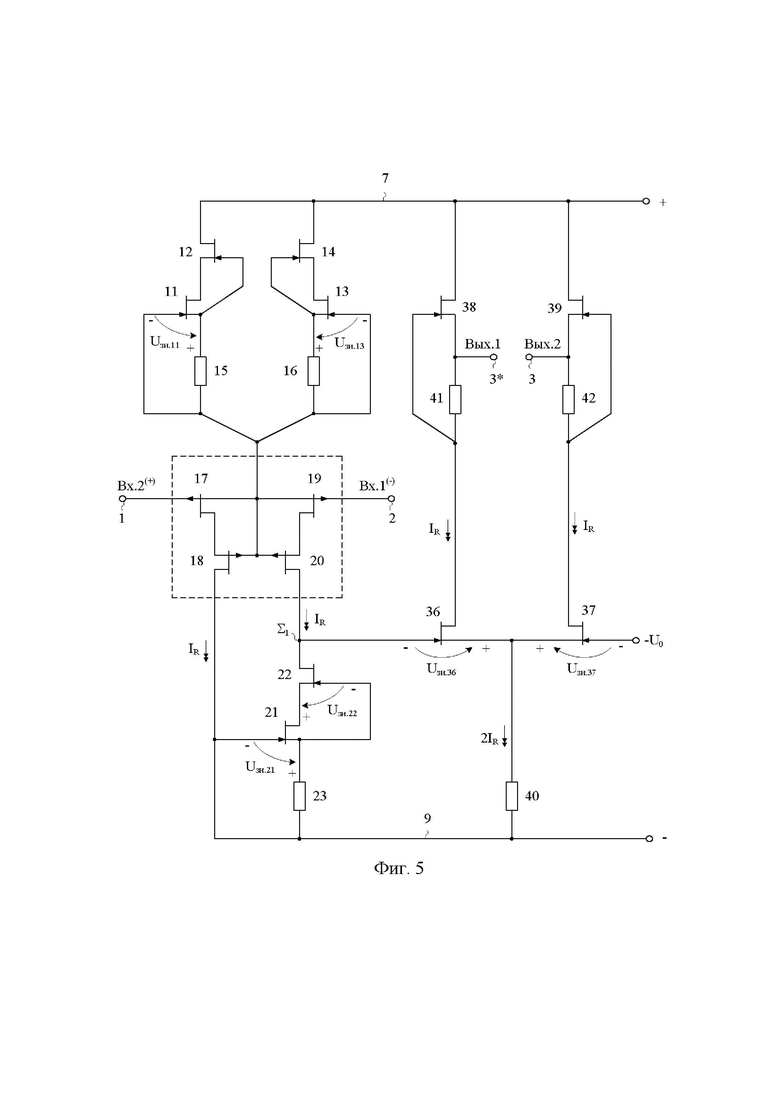

На чертеже фиг. 5 показана схема заявляемого ОУ фиг. 2 с другим выполнением буферного усилителя 10 на основе вспомогательных транзисторов 36, 37, 38, 39 и резисторов 40, 41 и 42.

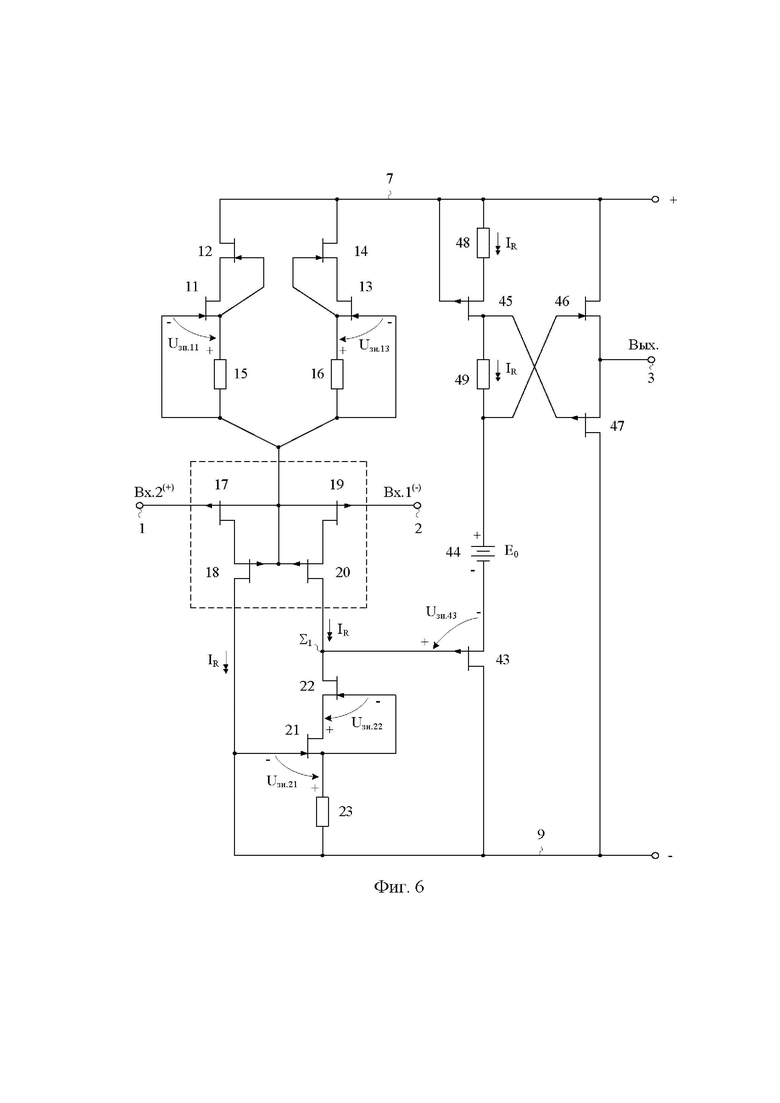

На чертеже фиг. 6 представлена схема заявляемого ОУ фиг. 2 с другим конкретным выполнением буферного усилителя 10 на основе вспомогательных транзисторов 43, 45, 46, 47 и пассивных элементов 44, 48 и 49.

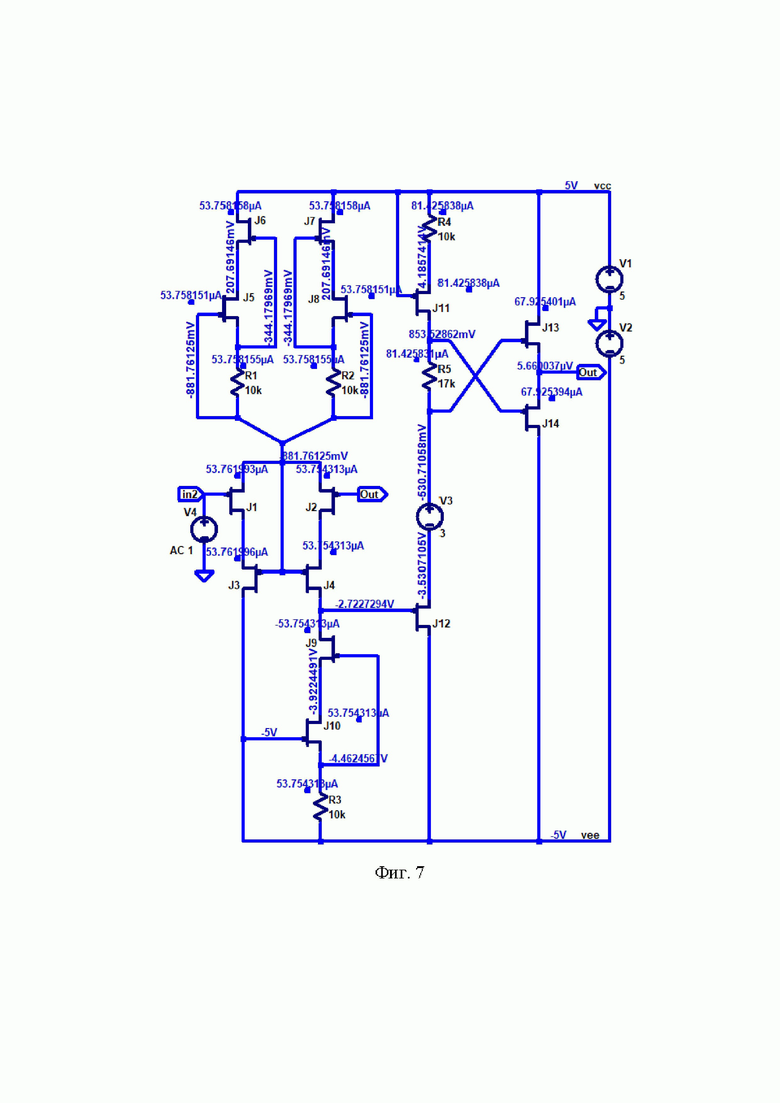

На чертеже фиг. 7 приведена схема ОУ фиг. 6 в среде компьютерного моделирования LTSpice на моделях JFET транзисторов (ОАО «Интеграл», г. Минск) при t=-197°C.

На чертеже фиг. 8 показаны амплитудно-частотные характеристики (АЧХ) JFet ОУ фиг. 7 при t=27°C.

На чертеже фиг. 9 представлены амплитудно-частотные характеристики JFet ОУ фиг. 7 при t=-197°C.

На чертеже фиг. 10 приведена схема ОУ фиг. 3 в среде компьютерного моделирования LTSpice на моделях JFET транзисторов (ОАО «Интеграл», г. Минск) при t=-197°C.

На чертеже фиг. 11 показано влияние потока нейтронов на коэффициент усиления по напряжению разомкнутого ОУ фиг. 10 при t=-197°C.

Радиационно-стойкий и низкотемпературный операционный усилитель на комплементарных полевых транзисторах фиг. 2 содержит первый 1 и второй 2 входы устройства, выход 3 устройства, первый 4 входной полевой транзистор, затвор которого подключен к первому 1 входу устройства, второй 5 входной полевой транзистор, затвор которого подключен ко второму 2 входу устройства, а исток соединен с истоком первого 4 входного полевого транзистора, источник опорного тока 6, включенный между первой 7 шиной источника питания и объединенными истоками первого 4 и второго 5 входных полевых транзисторов, активную динамическую нагрузку 8, согласованную со второй 9 шиной источника питания, которая связана со стоком второго 5 входного полевого транзистора и входом буферного усилителя 10, выход которого является выходом 3 устройства. В качестве первого 4 и второго 5 входных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом, источник опорного тока 6 содержит первый 11, второй 12, третий 13 и четвертый 14 дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор первого 11 дополнительного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого 4 и второго 5 входных полевых транзисторов с управляющим p-n переходом, исток первого 11 дополнительного полевого транзистора с управляющим p-n переходом соединен с затвором второго 12 дополнительного полевого транзистора с управляющим p-n переходом и связан с объединенными истоками первого 4 и второго 5 входных полевых транзисторов с управляющим p-n переходом через первый 15 дополнительный резистор, сток первого 11 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком второго 12 дополнительного полевого транзистора с управляющим p-n переходом, сток второго 12 дополнительного полевого транзистора с управляющим p-n переходом подключен к первой 7 шине источника питания, затвор третьего 13 дополнительного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого 4 и второго 5 входных полевых транзисторов с управляющим p-n переходом, исток третьего 13 дополнительного полевого транзистора с управляющим p-n переходом соединен с затвором четвертого 14 дополнительного полевого транзистора с управляющим p-n переходом и связан с объединенными истоками первого 4 и второго 5 входных полевых транзисторов с управляющим p-n переходом через второй 16 дополнительный резистор, сток третьего 13 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком четвертого 14 дополнительного полевого транзистора с управляющим p-n переходом, сток четвертого 14 дополнительного полевого транзистора с управляющим p-n переходом подключен к первой 7 шине источника питания, первый 4 входной полевой транзистор с управляющим p-n переходом выполнен в виде каскодного составного транзистора, содержащего пятый 17 и шестой 18 дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор пятого 17 дополнительного полевого транзистора с управляющим p-n переходом соединен с первым 1 входом устройства, сток пятого 17 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком шестого 18 дополнительного полевого транзистора с управляющим p-n переходом, сток шестого 18 дополнительного полевого транзистора с управляющим p-n переходом связан со второй 9 шиной источника питания, второй 5 входной полевой транзистор с управляющим p-n переходом выполнен в виде каскодного составного транзистора, содержащего шестой 18, седьмой 19 и восьмой 20 дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор седьмого 19 дополнительного полевого транзистора с управляющим p-n переходом соединен со вторым 2 входом устройства, сток седьмого 19 дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком восьмого 20 дополнительного полевого транзистора с управляющим p-n переходом, затворы шестого 18 и восьмого 20 дополнительных полевых транзисторов с управляющим p-n переходом соединены с объединенными истоками пятого 17 и седьмого 19 дополнительных полевых транзисторов с управляющим p-n переходом, сток восьмого 20 дополнительного полевого транзистора с управляющим p-n переходом подключен ко входу буферного усилителя 10, выход которого является выходом 3 устройства, активная динамическая нагрузка 8 выполнена в виде неуправляемой активной динамической нагрузки, содержащей девятый 21 и десятый 22 дополнительные полевые транзисторы с управляющим p-n переходом, причем сток десятого 22 дополнительного полевого транзистора с управляющим p-n переходом подключен ко входу буферного усилителя 10, исток десятого 22 дополнительного полевого транзистора с управляющим p-n переходом соединен со стоком девятого 21 дополнительного полевого транзистора с управляющим p-n переходом, затвор десятого 22 дополнительного полевого транзистора с управляющим p-n переходом связан с истоком девятого 21 дополнительного полевого транзистора с управляющим p-n переходом и подключен ко второй 9 шине источника питания через третий 23 дополнительный резистор, а затвор девятого 21 дополнительного полевого транзистора с управляющим p-n переходом связан со второй 9 шиной источника питания.

Кроме того на чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, сток шестого 18 дополнительного полевого транзистора с управляющим p-n переходом связан со второй 9 шиной источника питания через цепь согласования потенциалов 24.

Рассмотрим работу предлагаемого ОУ фиг. 2.

Для схемы ОУ фиг. 2 можно найти, что напряжение смещения нуля определяется формулой

ли после преобразований

где S4, S5 - крутизна стоко-затворных характеристик первого 4 и второго 5 входных полевых транзисторов; IR15, IR16 - токи в первом 15 и втором 16 дополнительных резисторах; IR23 - ток в третьем 23 дополнительном резисторе; Uзи.11=Uзи.13=Uзи.21 - напряжения затвор-исток первого 11, третьего 13 и девятого 21 дополнительных полевых транзисторов соответственно;

Особенность схемы фиг. 2 состоит в том, что здесь равенство Uзи.11=Uзи.13=Uзи.21 обеспечивается с высокой точностью за счет работы идентичных первого 11, третьего 13 и девятого 21 дополнительных полевых транзисторов при одинаковых напряжениях затвор-сток. Это позволяет создавать одинаковые статические токи IR23=IR15=IR16=0. Поэтому в соответствии с формулой (1) в заявляемой схеме ОУ Uсм≈0.

Важно отметить, что данный эффект реализуется без применения управляемых JFET токовых зеркал, функции которых в заявляемой схеме успешно выполняет предлагаемая активная динамическая нагрузка. При воздействии криогенных температур и радиации токи IR16, IR15, IR23 изменяются одинаково, что не приводит к существенному изменению Uсм.

При этом общий коэффициент усиления ОУ определяется формулой

где

Таким образом, в предлагаемом JFET ОУ фиг. 2 для получения малых

Компьютерное моделирование (фиг. 8, фиг. 9, фиг. 11) в среде LTSpice показало, что систематическая составляющая напряжения смещения нуля предлагаемого кремниевого JFet ОУ, не содержащего токовых зеркал, не превышает 150 мкВ в широком диапазоне температур и потоке нейтронов до 1012 н/см2 при коэффициенте усиления по напряжению более 80 дБ.

Для схемы ОУ фиг. 2 можно найти, что коэффициент ослабления входных синфазных сигналов

где

где

Особенность схемы фиг. 3 - применение неинвертирующего буферного усилителя (БУ) с двухтактным выходным каскадом на вспомогательных транзисторах 28 и 29. За счет стабилитрона 26 здесь обеспечивается согласование потенциалов БУ.

В схеме фиг. 4 используется инвертирующий буферный усилитель 10 на вспомогательных транзисторах 32, 35 и резисторах 34, 33. Это позволяет получить более высокие значения Ку.

Особенность ОУ фиг. 5 состоит в построении выходного буферного усилителя 10 по схеме с парафазными выходами 3 и 3*. Это значительно расширяет функциональные возможности заявляемого устройства.

Таким образом, предлагаемый ОУ имеет ряд преимуществ в сравнении с ОУ-прототипом, не требует применения JFET токовых зеркал и позволяет получить при этом малые значения систематической составляющей Uсм напряжения смещения нуля, приемлемые для многих применений значения Ку и

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6 342814, 2002 г., fig. 1.

2. Патент US 5714 906, 1998г., fig. 9a.

3. Патент US 6 762646, 2004 г.

4. Патент US 7595695, 2009 г.

5. Эннс В.И., Кобзев Ю.М. Проектирование аналоговых КМОП-микросхем. Краткий справочник разработчика / Под редакцией канд. техн. наук В.И. Эннса. - М.: Горячая линия-Телеком. - 2005. - 454 с. - С. 207. (рис. 3.45, стр. 168).

6. Патентная заявка US 2006/022698, fig. 2, 2006 г.

7. Патентная заявка US 2010/0164624, fig. 2, 2010 г.

8. Патент US 6566952, 2003 г.

9. S. Alam Chowdhury, et al., "Design of a Two Stage CMOS Operational Amplifier in 100nm Technology with Low Offset Voltage," 2018 IEEE ICISET, Bangladesh, 2018, pp. 56-59. doi: 10.1109/ICISET.2018.8745659 (fig. 1)

10. R.R. Bharath, and S.K. Gowda, "Design and Analysis of CMOS Two Stage OP-AMP in 180nm and 45nm Technology," IJERT, vol. 4, no. 5, 2015, pp. 1100-1103. (fig. 2)

11. N. Shukla, and J. Kaur, "Analysis of Two Stage CMOS Opamp using 90nm Technology." IJET, 2017, vol. 9, pp. 66-72. doi: 10.21817/ijet/2017/v9i3/170903S013 (fig. 4).

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2739577C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ ДЛЯ АКТИВНЫХ RC-ФИЛЬТРОВ, РАБОТАЮЩИХ В УСЛОВИЯХ ВОЗДЕЙСТВИЯ ПОТОКА НЕЙТРОНОВ И НИЗКИХ ТЕМПЕРАТУР | 2020 |

|

RU2724921C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2720555C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ И БИПОЛЯРНЫХ P-N-P ТРАНЗИСТОРАХ | 2022 |

|

RU2788498C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2766868C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ | 2021 |

|

RU2767976C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ В УСЛОВИЯХ НИЗКИХ ТЕМПЕРАТУР | 2019 |

|

RU2710847C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736412C1 |

Изобретение относится к области радиотехники и аналоговой микроэлектроники. Технический результат: малые значения систематической составляющей напряжения смещения нуля (Uсм), а также повышенные коэффициент усиления (Ку) по напряжению и коэффициент ослабления входных синфазных сигналов (Кос.сф). Технический результат обеспечивается схемой радиационно-стойкого и низкотемпературного операционного усилителя, реализованной на комплементарных полевых транзисторах с управляющим p-n переходом, включающей первый и второй входы устройства, источник опорного тока, первую и вторую шины источника питания, активную динамическую нагрузку, выполненную в виде неуправляемой активной динамической нагрузки и согласованную со второй шиной источника питания, буферный усилитель, выход которого является выходом устройства. 1 з.п. ф-лы, 11 ил.

1. Радиационно-стойкий и низкотемпературный операционный усилитель на комплементарных полевых транзисторах, содержащий первый (1) и второй (2) входы устройства, выход (3) устройства, первый (4) входной полевой транзистор, затвор которого подключен к первому (1) входу устройства, второй (5) входной полевой транзистор, затвор которого подключен ко второму (2) входу устройства, а исток соединен с истоком первого (4) входного полевого транзистора, источник опорного тока (6), включенный между первой (7) шиной источника питания и объединенными истоками первого (4) и второго (5) входных полевых транзисторов, активную динамическую нагрузку (8), согласованную со второй (9) шиной источника питания, которая связана со стоком второго (5) входного полевого транзистора и входом буферного усилителя (10), выход которого является выходом (3) устройства, отличающийся тем, что в качестве первого (4) и второго (5) входных полевых транзисторов используются полевые транзисторы с управляющим p-n переходом, источник опорного тока (6) содержит первый (11), второй (12), третий (13) и четвертый (14) дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор первого (11) дополнительного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого (4) и второго (5) входных полевых транзисторов с управляющим p-n переходом, исток первого (11) дополнительного полевого транзистора с управляющим p-n переходом соединен с затвором второго (12) дополнительного полевого транзистора с управляющим p-n переходом и связан с объединенными истоками первого (4) и второго (5) входных полевых транзисторов с управляющим p-n переходом через первый (15) дополнительный резистор, сток первого (11) дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком второго (12) дополнительного полевого транзистора с управляющим p-n переходом, сток второго (12) дополнительного полевого транзистора с управляющим p-n переходом подключен к первой (7) шине источника питания, затвор третьего (13) дополнительного полевого транзистора с управляющим p-n переходом соединен с объединенными истоками первого (4) и второго (5) входных полевых транзисторов с управляющим p-n переходом, исток третьего (13) дополнительного полевого транзистора с управляющим p-n переходом соединен с затвором четвертого (14) дополнительного полевого транзистора с управляющим p-n переходом и связан с объединенными истоками первого (4) и второго (5) входных полевых транзисторов с управляющим p-n переходом через второй (16) дополнительный резистор, сток третьего (13) дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком четвертого (14) дополнительного полевого транзистора с управляющим p-n переходом, сток четвертого (14) дополнительного полевого транзистора с управляющим p-n переходом подключен к первой (7) шине источника питания, первый (4) входной полевой транзистор с управляющим p-n переходом выполнен в виде каскодного составного транзистора, содержащего пятый (17) и шестой (18) дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор пятого (17) дополнительного полевого транзистора с управляющим p-n переходом соединен с первым (1) входом устройства, сток пятого (17) дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком шестого (18) дополнительного полевого транзистора с управляющим p-n переходом, сток шестого (18) дополнительного полевого транзистора с управляющим p-n переходом связан со второй 9 шиной источника питания, второй (5) входной полевой транзистор с управляющим p-n переходом выполнен в виде каскодного составного транзистора, содержащего шестой (18), седьмой (19) и восьмой (20) дополнительные полевые транзисторы с управляющим p-n переходом, причем затвор седьмого (19) дополнительного полевого транзистора с управляющим p-n переходом соединен со вторым (2) входом устройства, сток седьмого (19) дополнительного полевого транзистора с управляющим p-n переходом соединен с истоком восьмого (20) дополнительного полевого транзистора с управляющим p-n переходом, затворы шестого (18) и восьмого (20) дополнительных полевых транзисторов с управляющим p-n переходом соединены с объединенными истоками пятого (17) и седьмого (19) дополнительных полевых транзисторов с управляющим p-n переходом, сток восьмого (20) дополнительного полевого транзистора с управляющим p-n переходом подключен ко входу буферного усилителя (10), выход которого является выходом (3) устройства, активная динамическая нагрузка (8) выполнена в виде неуправляемой активной динамической нагрузки, содержащей девятый (21) и десятый (22) дополнительные полевые транзисторы с управляющим p-n переходом, причем сток десятого (22) дополнительного полевого транзистора с управляющим p-n переходом подключен ко входу буферного усилителя (10), исток десятого (22) дополнительного полевого транзистора с управляющим p-n переходом соединен со стоком девятого (21) дополнительного полевого транзистора с управляющим p-n переходом, затвор десятого (22) дополнительного полевого транзистора с управляющим p-n переходом связан с истоком девятого (21) дополнительного полевого транзистора с управляющим p-n переходом и подключен ко второй (9) шине источника питания через третий (23) дополнительный резистор, а затвор девятого (21) дополнительного полевого транзистора с управляющим p-n переходом связан со второй (9) шиной источника питания.

2. Радиационно-стойкий и низкотемпературный операционный усилитель на комплементарных полевых транзисторах по п.1, отличающийся тем, что сток шестого (18) дополнительного полевого транзистора с управляющим p-n переходом связан со второй (9) шиной источника питания через цепь согласования потенциалов (24).

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ ДВУХКАСКАДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2721942C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ ВХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2721943C1 |

| US 6342814 B1, 29.01.2002 | |||

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляющим p-n переходом | 2018 |

|

RU2688225C1 |

| ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2712416C1 |

| Дифференциальный каскад на комплементарных полевых транзисторах | 2018 |

|

RU2684473C1 |

| US 6504431 B2, 07.01.2003 | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| US 5285168 A1, 08.02.1994 | |||

| JP 5412968 B2, 12.04.2004. | |||

Авторы

Даты

2021-01-22—Публикация

2020-09-01—Подача