Изобретение относится к области микроэлектроники и может быть использовано в устройствах цифровой информации.

Известны схемы низковольтных триггеров на основе КМОП технологии [1-3]. Все известные схемы обладают рядом недостатков:

- узкий диапазон допустимых напряжений питания;

- большое число используемых элементов (более 20);

- повышенное энергопотребление;

- повышенное минимальное напряжение питания.

Ближайшим прототипом предлагаемого изобретения является известное техническое решение с поочередно отключаемым напряжением питания в каскадах синхронного триггера. Пример этого решения описан в монографии [1]. Как и в других источниках [1, 2, 4, 5] в схеме прототипа входной и выходной каскады триггера поочередно отключаются от шины питания. Схема устойчиво работает при напряжении питания более трех величин порогового напряжения МОП транзисторов. Сейчас выпускаются микросхемы с меньшими напряжениями питания. Наименьшие значения напряжения питания имеют КМОП схемы, в которых управляющее напряжение подается на затвор и изолирующий «карман» МОП транзисторов [3].

Их общим недостатком является низкое быстродействие, определяемое емкостью изолирующего «кармана», и увеличенные утечки изолирующих «карманов» при прямом смещении p-n переходов.

Основной недостаток схемы триггера прототипа состоит в том, что при снижении напряжения питания выходной ток входного каскада снижается и не может переключить состояние выходного каскада, так как РМОП транзисторы выходного каскада остаются подключенными к шине питания и охвачены цепью положительной обратной связи. Моделирование схемы прототипа показывает, что напряжение питания должно превышать на три величины порогового напряжения МОП транзисторов.

Основная цель предлагаемого изобретения состоит в расширении диапазона допустимых значений напряжений питания, повышении быстродействия и снижении энергопотребления синхронных триггеров.

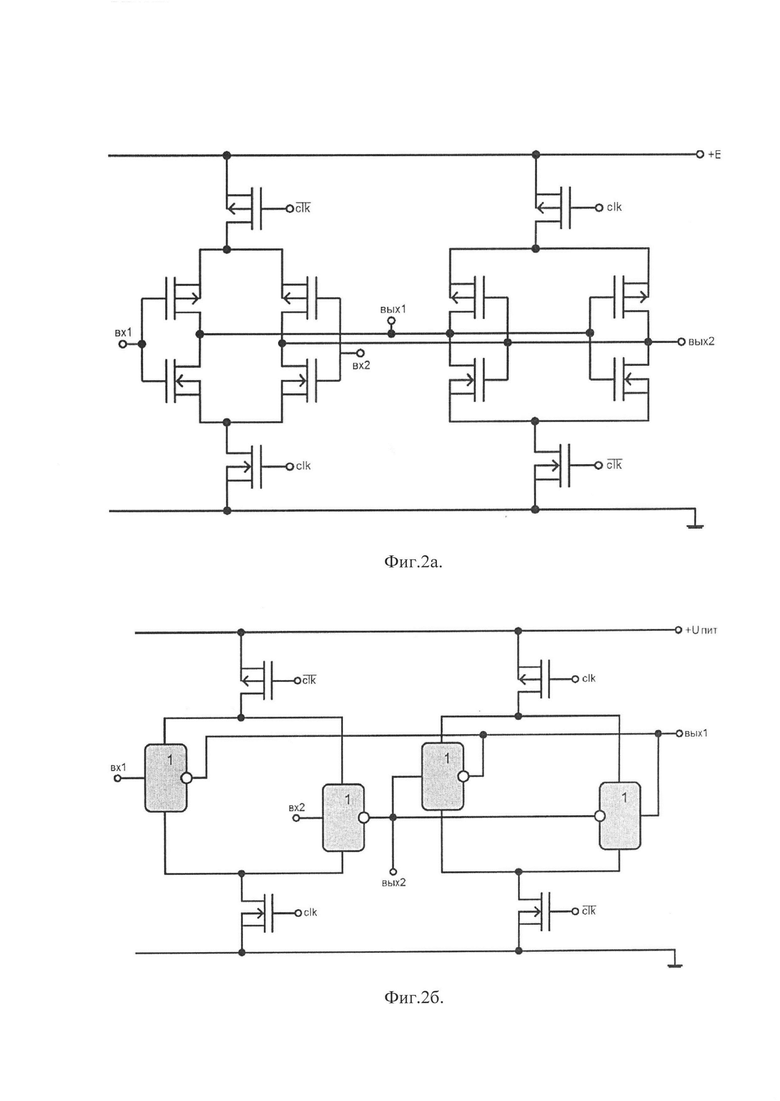

Технический результат достигается тем, что энергоэффективный низковольтный КМОП триггер, включающий входной и выходной каскады, каждый из которых построен на двух идентичных КМОП инверторах, а также имеет ключевой КМОП транзистор, соединяющий вывод инверторов «общий» с общей шиной питания; вход первого инвертора входного каскада подключен к неинвертирующему входу триггера, а вход второго - к инвертирующему; выход первого инвертора входного каскада подключен к инвертирующему выходу триггера, а выход второго - к неинвертирующему; вход первого инвертора выходного каскада подключен к неинвертирующему выходу триггера, а вход второго - к инвертирующему; выход первого инвертора выходного каскада подключен к инвертирующему выходу триггера, а выход второго - к неинвертирующему; первый ключевой NМОП транзистор соединен истоком с общей шиной питания, стоком - с объединенными выводами «общий» первого и второго инверторов входного каскада, а затвором - с прямым входом синхронизации триггера; второй ключевой NМОП транзистор соединен истоком с общей шиной питания, стоком - с объединенными выводами «общий» первого и второго инверторов выходного каскада, а затвором - с инверсным входом синхронизации, имеет схему, в которую введены третий и четвертый ключевые РМОП транзисторы, причем третий ключевой РМОП транзистор соединен истоком с шиной положительного питания, стоком - с объединенными выводами питания первого и второго инверторов входного каскада, а затвором - с инверсным входом синхронизации триггера; четвертый ключевой РМОП транзистор соединен истоком с шиной положительного питания, стоком - с объединенными выводами питания первого и второго инверторов выходного каскада, а затвором - с прямым входом синхронизации триггера.

Т.е. входной и выходной каскады триггера поочередно отключаются от обеих шин питания, имеют одинаковую структуру и порог переключения. Выходы каскадов объединены, а выходное напряжение определяется подключенным к питанию каскадом.

В заявляемой схеме снижение напряжения питания достигается тем, что в режиме передачи информации от входного каскада к выходному входной каскад подключен к обеим шинам питания, а выходной отключен от шин питания. Величина выходного тока не влияет на процесс изменения выходного напряжения триггера.

Моделирование заявляемой схемы показывает, что функционирование сохраняется до уровня напряжения питания, равного двум величинам порогового напряжения МОП транзисторов.

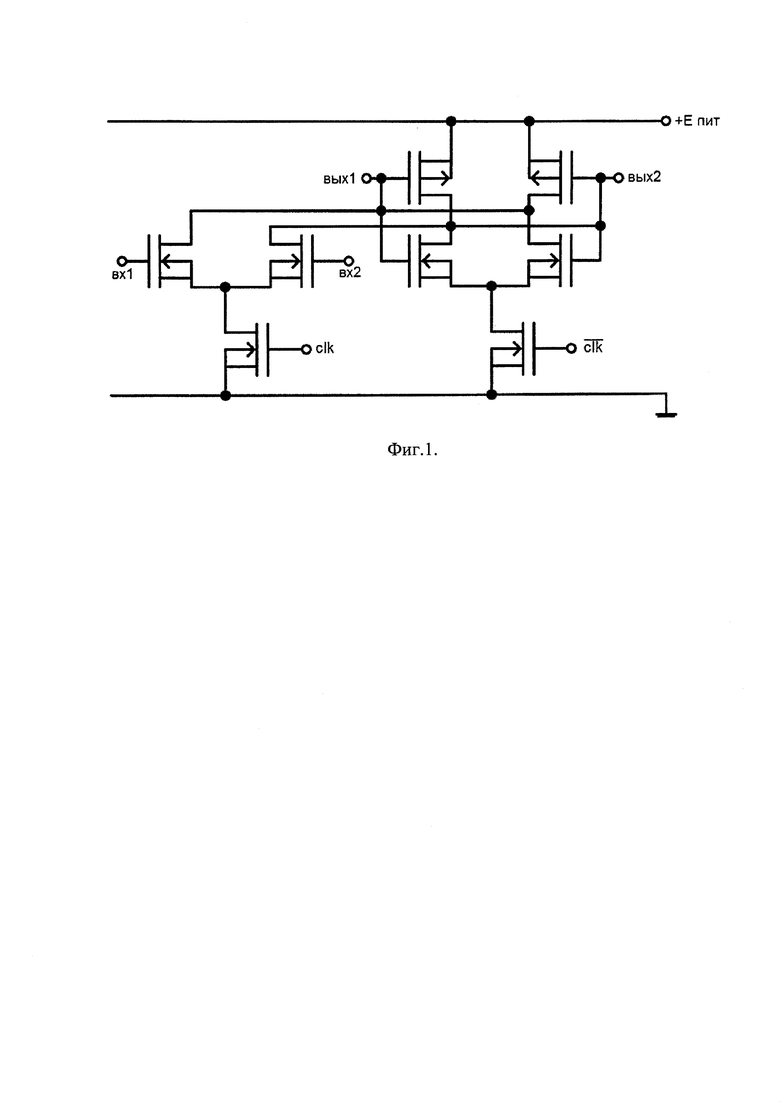

На фиг.1 изображена схема триггера - прототипа.

На фиг. 2а и 2б изображена схема заявляемого триггера.

На фиг. 3 показана схема делителя частоты на 2, построенная на заявляемых триггерах.

На фиг. 4 приведена временная диаграмма работы делителя частоты на 2 при напряжении 0,5 В.

Таким образом, отличительным признаком предлагаемого технического решения является, что энергоэффективный низковольтный КМОП триггер, включающий входной и выходной каскады, каждый из которых построен на двух идентичных КМОП инверторах, а также имеет ключевой NМОП транзистор, соединяющий вывод инверторов «общий» с общей шиной питания; вход первого инвертора входного каскада подключен к неинвертирующему входу триггера, а вход второго - к инвертирующему; выход первого инвертора входного каскада подключен к инвертирующему выходу триггера, а выход второго - к неинвертирующему; вход первого инвертора выходного каскада подключен к неинвертирующему выходу триггера, а вход второго - к инвертирующему; выход первого инвертора выходного каскада подключен к инвертирующему выходу триггера, а выход второго - к неинвертирующему; первый ключевой NМОП транзистор соединен истоком с общей шиной питания, стоком - с объединенными выводами «общий» первого и второго инверторов входного каскада, а затвором - с прямым входом синхронизации триггера; второй ключевой NМОП транзистор соединен истоком с общей шиной питания, стоком - с объединенными выводами «общий» первого и второго инверторов выходного каскада, а затвором - с инверсным входом синхронизации, имеет схему, в которую введены третий и четвертый ключевые РМОП транзисторы, причем третий ключевой РМОП транзистор соединен истоком с шиной положительного питания, стоком - с объединенными выводами питания первого и второго инверторов входного каскада, а затвором - с инверсным входом синхронизации триггера; четвертый ключевой РМОП транзистор соединен истоком с шиной положительного питания, стоком - с объединенными выводами питания первого и второго инверторов выходного каскада, а затвором - с прямым входом синхронизации триггера позволяет реализовать поочередное полное отключение входного и выходного каскадов КМОП триггера от шин электропитания, что снижает величину тока переключения выходного каскада и, соответственно, минимальное напряжение питания.

Используемая литература

[1] Cao Z., Yan S., et. al. «Low-power high-speed ADCs for nanometer CMOS integration». Pict. 3.13. Springer, 2008, ISBN:978-1-4020-8449-2.

[2] Ndjountche T. «CMOS analog integrated circuits. High-speed and power-efficient design». Pict. 6.8. CRS Press, 2011, ISBN: 978-1-4398-5500-3.

[3] Chatterjee S., Pun K., Stanic N., Tsividis Y., Kinget P. «Analog circuit design techniques at 0,5 V». Springer, 2007, ISBN:978-0-378-69953-0.

[4] Jespers P. «The  methodology a sizing tool for loe-voltage analog CMOS circuits». Springer, 2010, ISBN:978-0-378-47100-6.

methodology a sizing tool for loe-voltage analog CMOS circuits». Springer, 2010, ISBN:978-0-378-47100-6.

[5] Патент RU №2119716 «Синхронная триггерная ячейка», авт.: Адамов Д.Ю.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫХОДНОЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ ДЛЯ КМОП МИКРОСХЕМ | 2013 |

|

RU2540813C1 |

| Логический элемент сравнения комплементарной металл-оксид-полупроводниковой структуры ассоциативного селектора запоминающего устройства | 2016 |

|

RU2621011C1 |

| Асинхронный логический элемент комплементарной металл-оксид-полупроводниковой структуры | 2018 |

|

RU2693685C1 |

| БЛОК ПАМЯТИ КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ ОЗУ | 2015 |

|

RU2580072C1 |

| ТРИГГЕР КОМПЛЕМЕНТАРНОЙ МЕТАЛЛ-ОКСИД-ПОЛУПРОВОДНИКОВОЙ СТРУКТУРЫ МИКРОСХЕМЫ | 2013 |

|

RU2541894C1 |

| ВЫХОДНОЙ КАСКАД ДЛЯ КМОП МИКРОСХЕМ С УСТРОЙСТВОМ ЗАЩИТЫ ОТ ЭЛЕКТРОСТАТИЧЕСКИХ РАЗРЯДОВ | 2014 |

|

RU2560822C1 |

| ДИНАМИЧЕСКИЙ D-ТРИГГЕР | 2018 |

|

RU2679220C1 |

| Интегральный электронный синаптический КМОП-элемент | 2024 |

|

RU2836650C1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| Усилитель-формирователь импульсов | 1980 |

|

SU944110A1 |

Изобретение относится к области микроэлектроники. Технический результат заключается в расширении диапазона допустимых значений напряжений питания, повышении быстродействия и снижении энергопотребления синхронных триггеров. Для этого предложен энергоэффективный низковольтный КМОП-триггер, включающий входной и выходной каскады, каждый из которых построен на двух идентичных КМОП инверторах, а также имеет ключевой NМОП транзистор, соединяющий вывод инверторов «общий» с общей шиной питания, при этом дополнительно в схему введены третий и четвертый ключевые РМОП транзисторы, причем третий ключевой РМОП транзистор соединен истоком с шиной положительного питания, стоком - с объединенными выводами питания первого и второго инверторов входного каскада, а затвором - с инверсным входом синхронизации триггера; четвертый ключевой РМОП транзистор соединен истоком с шиной положительного питания, стоком - с объединенными выводами питания первого и второго инверторов выходного каскада, а затвором - с прямым входом синхронизации триггера. 5 ил.

Энергоэффективный низковольтный КМОП-триггер, включающий входной и выходной каскады, каждый из которых построен на двух идентичных КМОП инверторах, а также имеет ключевой NМОП транзистор, соединяющий вывод инверторов «общий» с общей шиной питания; вход первого инвертора входного каскада подключен к неинвертирующему входу триггера, а вход второго - к инвертирующему; выход первого инвертора входного каскада подключен к инвертирующему выходу триггера, а выход второго - к неинвертирующему; вход первого инвертора выходного каскада подключен к неинвертирующему выходу триггера, а вход второго - к инвертирующему; выход первого инвертора выходного каскада подключен к инвертирующему выходу триггера, а выход второго - к неинвертирующему; первый ключевой NМОП транзистор соединен истоком с общей шиной питания, стоком - с объединенными выводами «общий» первого и второго инверторов входного каскада, а затвором - с прямым входом синхронизации триггера; второй ключевой NМОП транзистор соединен истоком с общей шиной питания, стоком - с объединенными выводами «общий» первого и второго инверторов выходного каскада, а затвором - с инверсным входом синхронизации, отличающийся тем, что в схему введены третий и четвертый ключевые РМОП транзисторы, причем третий ключевой РМОП транзистор соединен истоком с шиной положительного питания, стоком - с объединенными выводами питания первого и второго инверторов входного каскада, а затвором - с инверсным входом синхронизации триггера; четвертый ключевой РМОП транзистор соединен истоком с шиной положительного питания, стоком - с объединенными выводами питания первого и второго инверторов выходного каскада, а затвором - с прямым входом синхронизации триггера.

| CAO ZHIHENG ET AL, Low-power high-speed ADCs for nanometer CMOS integration, Springer, 2008, ISBN: 978-1-4020-8449-2, стр | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| САМОСИНХРОННЫЙ ТРИГГЕР С ОДНОФАЗНЫМ ИНФОРМАЦИОННЫМ ВХОДОМ | 2008 |

|

RU2405246C2 |

| Быстродействующий Д-триггер | 1990 |

|

SU1734195A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

Авторы

Даты

2017-02-21—Публикация

2015-11-12—Подача