Изобретение относится к области вычислительной техники и может быть использовано в устройствах для решения комбинаторных задач.

Из уровня техники известно устройство для перебора сочетаний [Патент SU 1658167, МПК G06F 15/20, 1988 г.], содержащее генератор тактовых импульсов, m регистров на N сдвигов, первый и второй блоки с m линиями задержки и блок m счетчиков, а также содержит пять групп элементов И, две группы элементов ИЛИ и блок сдвига кодов, выполненный из шести триггеров, каждый из которых имеет прямой и инверсный выход, которые позволяют формировать сочетания из шести двоичных чисел.

Недостаток известного устройства состоит в низкой достоверности формирования сочетаний с помощью триггеров, так число сочетаний из двух устойчивых состояний шести триггеров может быть только 12, в то время как из шести символов (чисел) по два  формируется 15 сочетаний, не хватает трех комбинаций (15-12=3), что свидетельствует о неполном нахождении всех возможных сочетаний двоичных чисел.

формируется 15 сочетаний, не хватает трех комбинаций (15-12=3), что свидетельствует о неполном нахождении всех возможных сочетаний двоичных чисел.

Наиболее близким известным техническим решением к заявляемому в качестве прототипа является формирователь сочетаний из N по m символов [Патент RU 95872, МПК G06F 17/22, 2010], который содержит генератор счетных (тактовых) импульсов, блок m счетчиков, первый и второй блоки с линиями задержки и блок вывода (элементов отображения) m сочетаний, а также содержит шину ввода (задания) числа N, формирователь (задатчик) числа m, блок m регистров, блок m замыкающих и блок m размыкающих ключей и треугольную матрицу Паскаля, которые обеспечивают формирование всех возможных сочетаний из заданных N чисел по заданным m числам. При этом общее количество

Недостаток прототипа состоит в его относительно сложной схемной и алгоритмической реализации, а также в том, что перебор сочетаний осуществляется только для чисел одной заданной системы счисления, в других системах счисления перебор сочетаний не представляется технически возможным, что свидетельствует об ограниченных функциональных возможностях прототипа.

Целью изобретения (техническим результатом) является упрощение схемной и алгоритмической реализации формирователя сочетаний и расширение его функциональных возможностей - генерирования полного объема сочетаний из N по m чисел в µ-й системе счисления при m≤N и µ≥N+1 в количестве

Задачей изобретения является обеспечение формирования каждого элемента сочетания в n-разрядном двоичном счетчике, контроль значений которого осуществляется с помощью позиционного дешифратора, имеющего µ выходов. При этом сигнал «1» появляется на том выходе позиционного дешифратора, порядковый номер которого совпадает с дешифруемым числом, поступающим на его вход с информационного выхода счетчика. В соответствии со значением, записанным в i-м n-разрядном двоичном счетчике, i-й позиционный дешифратор формирует два сигнала управления процессами: на i-м и на (N-m+i+1)-M выходах. На i-м выходе i-го позиционного дешифратора сигнал «1» используется для управления процессом формирования i-го элемента первого сочетания. На (N-m+i+1)-M выходе i-го позиционного дешифратора сигнал «1» соответствует сигналу «условное переполнение i-го n-разрядного двоичного счетчика» и используется для управления процессами формирования последующих сочетаний, а с выхода первого дешифратора этот сигнал «1» соответствует сигналу «завершение процесса работы формирователя сочетаний».

Сущность изобретения состоит в том, что, кроме известных и общих существенных отличительных признаков, а именно: генератора счетных импульсов, блока m счетчиков, блока m элементов отображения сочетаний, первого и второго блоков линий задержек, предлагаемый формирователь сочетаний из N по m символов содержит блок m позиционных дешифраторов, первый и второй асинхронные RS триггеры, линию задержки, блок m элементов ИЛИ, первый, второй и третий блоки элементов И, каждый элемент отображения сочетаний выполнен с n-разрядным информационным и управляющим входами, первый и второй блоки линий задержки выполнены с (m-1) линиями задержек, каждый счетчик выполнен двоичным n-разрядным с управляющим входом R для установки значения счетчика в ноль соединенным с запускающим входом формирователя, с счетным входом C, с n-разрядным информационным входом A для записи в счетчик информации в параллельном коде, с n-разрядным информационным выходом B для съема информации со счетчика в параллельном коде и с управляющим входом V для разрешения записи в счетчик информации через вход A, счетчики соединены между собой последовательно n-разрядными шинами, так, что выход B i-го счетчика соединен со входом A (i+1)-го счетчика, при этом выход B каждого i-го счетчика соединен посредством n-разрядной шины с информационным входом соответствующего элемента отображения сочетаний, управляющие входы R первого и второго асинхронных RS триггеров соединены с запускающим входом формирователя, инверсный выход первого асинхронного RS триггера связан с входом запуска генератора счетных импульсов, каждый i-й позиционный дешифратор выполнен с информационным n-разрядным входом, соединенным посредством n-разрядной шины с выходом B i-го счетчика, и с µ выходами, на которых формируется сигнал «1», если порядковый номер позиционного дешифратора совпадает с значением числа, поступившего на его информационный вход, (N-m+1)-й выход первого позиционного дешифратора соединен с входом S первого асинхронного RS триггера, первый элемент ИЛИ блока m элементов ИЛИ выполнен на два входа, остальные (m-1) элементы ИЛИ выполнены на три входа, выход i-го элемента ИЛИ соединен с входом C i-го счетчика, элементы И первого блока m элементов И выполнены с двумя инверсными входами и с одним прямым входом, который подключен к выходу генератора счетных импульсов, один инверсный вход i-го элемента И первого блока m элементов И соединен с i-м выходом i-го позиционного дешифратора, другой инверсный вход i-го элемента И первого блока m элементов И подключен к прямому выходу второго асинхронного RS триггера, выход i-го элемента И первого блока m элементов И соединен с одним из входов i-го элемента ИЛИ, элементы И второго блока m элементов И выполнены с двумя прямыми входами и с одним инверсным входом, который соединен с (N-m+i+1)-м выходом i-го позиционного дешифратора, один прямой вход i-го элемента И второго блока m элементов И соединен с (N-m+i+2)-м выходом (i+1)-го позиционного дешифратора, другой прямой вход i-го элемента И второго блока m элементов И связан с выходом генератора счетных импульсов, выход i-го элемента И второго блока m элементов И соединен с одним из входов i-го элемента ИЛИ и с входом i-й линии задержки первого блока линий задержки, линия задержки включена в цепь между входом m-го элемента ИЛИ и выходом m-го элемента И второго блока m элементов И, к которому подключены управляющие входы всех элементов отображения блока элементов отображения, элементы И третьего блока из (m-1) элементов И выполнены с прямым и инверсным входом, который соединен с (N-m+i+1)-м выходом i-го позиционного дешифратора, прямой вход элемента И третьего блока из (m-1) элементов И связан с выходом i-й линии задержки первого блока линий задержки, выход i-го элемента И третьего блока из (m-1) элементов И соединен с входом V (i+1)-го счетчика и с входом i-й линии задержки второго блока линий задержки, выход которой соединен с одним из входов (i+1)-го элемента ИЛИ, вход S второго асинхронного RS триггера соединен с (N+1)-м выходом m-го позиционного дешифратора, прямой выход второго асинхронного RS триггера подключен к одному инверсному входу каждого элемента И первого блока т элементов N и к одному прямому входу m-го элемента И второго блока m элементов И, где n≥log2(N+1) и µ≥N+1.

Новизна изобретения состоит в том, что формирователь сочетаний из N по m символов содержит блок m позиционных дешифраторов, первый и второй асинхронные RS триггеры, линию задержки, блок m элементов ИЛИ, первый, второй и третий блоки элементов И, каждый элемент отображения сочетаний выполнен с n-разрядным информационным и управляющим входами, первый и второй блоки линий задержки выполнены с (m-1) линиями задержек, каждый счетчик выполнен двоичным n-разрядным с счетным входом C, с управляющим входом R для установки значения счетчика в ноль, соединенным с запускающим входом формирователя, с n-разрядным информационным входом A для записи в счетчик информации в параллельном коде, с n-разрядным информационным выходом B для съема информации со счетчика в параллельном коде и с управляющим входом V для разрешения записи в счетчик информации через вход A, счетчики соединены между собой последовательно n-разрядными шинами, так, что выход B i-го счетчика соединен со входом A (i+1)-го счетчика, при этом выход B каждого i-го счетчика соединен посредством n-разрядной шины с информационным входом соответствующего элемента отображения сочетаний, управляющие входы R первого и второго асинхронных RS триггеров соединены с запускающим входом формирователя, инверсный выход первого асинхронного RS триггера связан с входом запуска генератора счетных импульсов, каждый i-й позиционный дешифратор выполнен с информационным n-разрядным входом, соединенным посредством n-разрядной шины с выходом B i-го счетчика, и с µ выходами, на которых формируется сигнал «1», если порядковый номер позиционного дешифратора совпадает с значением числа, поступившего на его информационный вход, (N-m+1)-й выход первого позиционного дешифратора соединен с входом S первого асинхронного RS триггера, первый элемент ИЛИ блока m элементов ИЛИ выполнен на два входа, остальные (m-1) элементы ИЛИ выполнены на три входа, выход i-го элемента ИЛИ соединен с входом C i-го счетчика, элементы И первого блока m элементов И выполнены с двумя инверсными входами и с одним прямым входом, который подключен к выходу генератора счетных импульсов, один инверсный вход i-го элемента И первого блока m элементов И соединен с i-м выходом i-го позиционного дешифратора, другой инверсный вход i-го элемента И первого блока m элементов И подключен к прямому выходу второго асинхронного RS триггера, выход i-го элемента И первого блока m элементов И соединен с одним из входов i-го элемента ИЛИ, элементы И второго блока m элементов И выполнены с двумя прямыми входами и с одним инверсным входом, который соединен с (N-m+i+1)-м выходом i-го позиционного дешифратора, один прямой вход i-го элемента И второго блока m элементов И соединен с (N-m+i+2)-м выходом (i+1)-го позиционного дешифратора, другой прямой вход i-го элемента И второго блока m элементов И связан с выходом генератора счетных импульсов, выход i-го элемента И второго блока m элементов И соединен с одним из входов i-го элемента ИЛИ и с входом i-й линии задержки первого блока линий задержки, линия задержки включена в цепь между входом m-го элемента ИЛИ и выходом m-го элемента И второго блока m элементов И, к которому подключены управляющие входы всех элементов отображения блока элементов отображения, элементы И третьего блока из (m-1) элементов И выполнены с прямым и с инверсным входом, который соединен с (N-m+i+1)-м выходом i-го позиционного дешифратора, прямой вход элемента И третьего блока из (m-1) элементов И связан с выходом i-й линии задержки первого блока линий задержки, выход i-го элемента И третьего блока из (m-1) элементов И соединен с входом V (i+1)-го счетчика и с входом i-й линии задержки второго блока линий задержки, выход которой соединен с одним из входов (i+1)-го элемента ИЛИ, вход S второго асинхронного RS триггера соединен с N-м выходом m-го позиционного дешифратора, прямой выход второго асинхронного RS триггера подключен к инверсному входу каждого элемента И первого блока m элементов И и к одному прямому входу m-го элемента И второго блока m элементов И, где n≥log2(N+1) и µ≥N+1, что обеспечивает упрощение схемной и алгоритмической реализации формирователя сочетаний и расширяет его функциональные возможности - генерирование полного объема сочетаний из N по m чисел в µ-й системе счисления при m≤N и µ≥N+1 в количестве

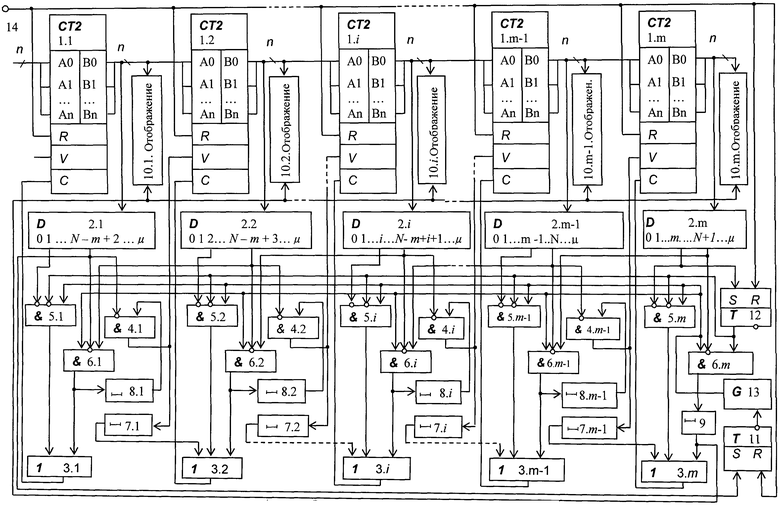

На чертеже представлена функциональная схема формирователя сочетаний из N по m символов, где обозначено:

1.1, 1.2, …, 1.m - блок из m двоичных n-разрядных счетчиков (CT2), где n определяется из выражения n≥log2(N+1). Каждый из счетчиков 1.1, 1.2, …, 1.m имеет: n-разрядный информационный вход A (A0, A1, …, An) для записи в счетчик числовых значений в параллельном коде; n-разрядный информационный выход B (B0, B1, …, Bn) для считывания значений счетчика в n-разрядном параллельном коде; управляющий вход R для установки счетчика в «0»; управляющий вход C для ввода счетных импульсов; управляющий вход V, при подаче сигнала «1» на который разрешается запись в счетчик информации, поступившей на вход A в n-разрядном параллельном коде;

2.1, 2.2, …, 2.m - блок из m позиционных дешифраторов (D) двоичного n-разрядного кода по модулю µ при условии, что µ≥N+1. Значение «1» появляется на том выходе i-го позиционного дешифратора, порядковый номер которого в µ-й системе счисления совпадает со значением числа, записанного в i-м счетчике и поступившего на вход i-го позиционного дешифратора;

3.1, 3.2, …, 3.m - блок из m элементов ИЛИ, из которых первый элемент ИЛИ выполнен на два входа, остальные элементы ИЛИ выполнены на три входа;

4.1, 4.2, …, 4.(m-1) - третий блок из m-1 элементов И, каждый из которых выполнен с одним прямым и с одним инверсным входами;

5.1, 5.2, …, 5.m - первый блок из m элементов И, каждый из которых выполнен на два инверсных и один прямой вход;

6.1, 6.2, …, 6.m - второй блок из m элементов И, каждый из которых выполнен на два прямых и один инверсный вход;

7.1, 7.2, … 7.(m-1) - первый блок линий задержки на интервал времени τ1, учитывающий время записи информации, поступающей в параллельном коде на информационный вход A счетчика при подаче управляющего импульса на вход V счетчика с последующим добавлением «+1» к записанному в счетчик значению счетных импульсов при поступлении на вход C счетчика управляющего импульса, задержанного с помощью линии задержки блока 7.1, 7.2, …, 7.(m-1);

8.1, 8.2, …, 8.(m-1) - второй блок из (m-1) линий задержки на интервал времени τ2, достаточный для завершения переходных процессов при поступлении счетного импульса на вход C соответствующих счетчиков 1.1, 1.2, …, 1.(m-1) с выхода соответствующего элемента И второго блока элементов И 6.1, 6.2, …, 6.m;

9 - линия задержки на интервал времени τ3, необходимый для отображения сочетаний, текущие значения которых записаны в счетчиках 1.1, 1.2, …, 1.m;

10.1, 10.2, …, 10.m - блок из m элементов отображения элементов сочетаний символов µ-й системы счисления (отображение);

11 и 12 - асинхронные триггеры RS-типа;

13 - генератор счетных импульсов (G);

14 - вход запуска формирователя сочетаний;

i=1, 2, …, m.

В исходном положении выход B каждого счетчика 1.1, 1.2, …, 1.m подключен с помощью n-разрядной шины к входу соответствующего позиционного дешифратора 2.1, 2.2, …, 2.m и ко входу соответствующего элемента отображения сочетаний 10.1, 10.2, …, 10.m. Кроме того, выходы B (m-1) счетчиков 1.1. 1.2, …, 1.(m-1) подключены ко входам A (m-1) счетчиков 1.2. 1.3, …, 1.m соответственно.

Выход с номером i каждого позиционного дешифратора 2.i соединен с инверсным входом элемента И 5.i, при этом выход с номером N позиционного дешифратора 2.m соединен с прямым входом S асинхронного RS триггера 12, а выход с номером N-m+i+1 каждого позиционного дешифратора 2.i соединен с инверсным входом соответствующего элемента И 5.i.

Выход каждого элемента ИЛИ 3.i подключен к входу C соответствующего счетчика 1.i. Один вход каждого элемента ИЛИ 3.i соединен с выходом соответствующего элемента И 5.i другой вход элемента ИЛИ 3.i связан с выходом соответствующего элемента И 6.i, причем в цепь между этим входом элемента ИЛИ 3.m и выходом элемента И 6.m включена линия задержки 9. Третий вход каждого элемента ИЛИ 3.i, кроме ИЛИ 3.1, подключен соответственно к выходу линии задержки 7.(i-1).

Выход каждого элемента И 4.i подключен к управляющему входу V соответственно счетчика 1.(i+1), кроме того, выход каждого элемента И 4.i через соответствующую линию задержки 7.i подключен к входу элемента ИЛИ 3.(i+1).

Каждая линия задержки 8.i включена в электрическую цепь между выходом элемента И 6.i и прямым входом элемента И 4.i.

Входы R триггеров 11 и 12 подключены к запускающему входу 14, который также подключен к входам R установки счетчиков 1.1, 1.2, …, 1.m в исходное нулевое положение.

Прямой вход S триггера 11 подключен к (N-m+1)-му выходу позиционного дешифратора 2.1, который также соединен с инверсными входами элементов И 4.1 и И 6.1. Инверсный выход триггера 11 подключен ко входу запуска генератора счетных импульсов 13, выход которого подключен к прямым входам элементов И 5.1, 5.2, …, 5.m и элементов И 6.1, 6.2, …, 6.m. Прямой вход S триггера 12 соединен с выходом N позиционного дешифратора 2.m, а прямой выход триггера 12 связан с одним из прямых входов элемента И 6.m и с одним из инверсных входов каждого элемента И первого блока элементов И 5.1. 5.2, …, 5.m.

В работе формирователя сочетаний можно выделить следующие этапы:

1. Начальная установка элементов.

На запускающий вход 14 формирователя сочетаний подают импульс «Старт», который поступает на входы R всех счетчиков блока 1.1, 1.2, …, 1.m и триггеров 11 и 12, что приводит их в нулевое состояние. Нулевые значения счетчиков 1.1, 1.2, …, 1.m, с информационных выходов A поступают в параллельном n-разрядном коде на входы соответствующих позиционных дешифраторов 2.1, 2.2, …, 2.m. Поэтому на выходах с номером i и N-m+i каждого позиционного дешифратора 2.i появляется сигнал «0».

Сигнал «0» с прямого выхода триггера 12 подготавливает к открытию по инверсному входу элементы И первого блока элементов И 5.1, 5.2, …, 5.m.

Сигнал «0» с i-го выхода позиционного дешифратора 2.i подготавливает к открытию по другому инверсному входу соответствующий элемент И 5.i.

Сигнал «0» с выхода N-m+i+1 позиционного дешифратора 2.i подготавливает к открытию по инверсному входу соответствующий элемент И 6.i и, соответственно, этими же сигналом с выходов первых (m-1) позиционных дешифраторов 2.i готовятся к открытию по инверсному входу соответствующие элементы И третьего блока элементов И 4.1, 4.2, …, 4.(m-1).

Сигнал с инверсного выхода триггера 11 запускает генератор счетных импульсов 13 в работу.

2. Установка начальных значений счетчиков.

Счетные импульсы с выхода генератора 13 поступают на прямые входы готовых к открытию элементов И первого блока элементов И 5.1, 5.2, …, 5.m и на прямые входы элементов И второго блока элементов И 6.1, 6.2, …, 6.m, каждый из которых в данный момент времени по прямому входу закрыт сигналом «0». Элементы И 6.1, 6.2, …, 6.m закрыты сигналами, поступившими с выходов N-m+i+1, где

Счетные импульсы с выхода каждого элемента И 5.i через соответствующие элементы ИЛИ 3.i, где

С приходом m-го счетного импульса в счетчик 1.m в нем будет записано число m, при этом выходным сигналом «1» с выхода m дешифратора 2.m по инверсному входу закрывается элемент И 5.m и по входу S опрокидывается триггер 12, так что на прямом выходе триггера 12 появляется сигнал «1», который по прямому входу подготавливает к открытию элемент И 6.m и закрывает по инверсному входу все элементы И первого блока элементов И 5.1, 5.2, …, 5.m.

На этом процесс записи начальных значений в счетчики 1.1, 1.2, …, 1.m завершается. При этом значения элементов первого сочетания {1; 2; 3; …; m-1; m}, записанные в счетчиках 1.1, 1.2, …, 1.m, с информационных выходов B0, B1, …, Bn в n-разрядным параллельном коде поступают на информационные входы соответствующих позиционных дешифраторов 2.1, 2.2, …, 2.m и на входы соответствующих элементов отображения 10.1, 10.2, …, 10.m, на управляющие входы которых подан сигнал «0» (запрет обновления) с выхода подготовленного к открытию, но закрытого в данный момент времени элемента И 6.m.

3. Отображение и формирование элементов сочетаний.

3.1. Очередной импульс с выхода генератора 13 через элемент И 6.m поступает на вход линии задержки 9 и на управляющие входы элементов отображения 10.1, 10.2, …, 10.m, разрешая отображение значений элементов текущего сочетания, записанного в счетчиках 1.1, 1.2, …, 1.m на предыдущем этапе.

Задержанный с помощью линии задержки 9 счетный импульс через элемент ИЛИ 3.m поступает на вход C счетчика 1.m, что приводит к увеличению записанного в нем значения на «+1».

Процесс продолжается до тех пор, пока значение счетчика 1.m не станет равным N+1, при этом на выходе N+1 позиционного дешифратора 2.m появляется сигнал «1» («условное переполнение счетчика 1.m»), который закрывает по инверсному входу элемент И 6.m и готовит к открытию по прямому входу элемент И 6.(m-1).

3.2. Начинается процесс пересчета начальных значений счетчиков 1.(m-1) и 1.m. Очередной счетный импульс генератора 13 через открытый элемент И 6.(m-1) и элемент ИЛИ 3.(m-1) поступает на управляющий вход C счетчика 1.(m-1), увеличивая его значение на «+1». В то же время с выхода открытого элемента И 6.(m-1) задержанный в линии задержки 8.(m-1) счетный импульс поступает на прямой вход элемента И 4.(m-1), который при значении счетчика 1.(m-1) меньше N+1 («нет переполнения счетчика 1.(m-1)») открыт по инверсному входу сигналом «0», сформированным на выходе с номером N позиционного дешифратора 2.(m-1). С выхода элемента И 4.(m-1) счетный импульс поступает на управляющий вход V счетчика 1.m, разрешая произвести перезапись информации с выхода B счетчика 1.(m-1) в n-разрядном параллельном коде через вход A в счетчик 1.m, так, что значение счетчика 1.m становится равным значению счетчика 1.(m-1) и меньше N+1. На выходе N+1 позиционного дешифратора 2.m появляется сигнал «0», который закрывает по прямому входу элемент И 6.(m-1) и открывает по инверсному входу элемент И 6.m. Задержанный в линии задержки 7.(m-1) счетный импульс через элемент ИЛИ 3.m поступает на вход C счетчика 1.m,увеличивая его значение на «+1».

Вновь начинается процесс по п.3.1 при новых начальных значениях счетчиков.

3.3. Если в процессе, рассмотренном в п.3.2, с приходом счетного импульса на управляющий вход C счетчика 1.(m-1) его значение станет равным N («условное переполнение счетчика 1.(m-1)»), то начнется процесс пересчета начальных значений счетчиков 1.(m-2) и 1.(m-1) аналогично показанному в п.3.2.

Процессы, приведенные в п.п 3.1, 3.2, 3.3, продолжаются до тех пор, пока в счетчике 1.1 с приходом очередного счетного импульса его значение не станет равным N-m+1. При этом на выходе N-m+1 позиционного дешифратора 2.1 появится сигнал «1», который опрокидывает триггер 11. На инверсном выходе триггера 11 образуется сигнал «0», с помощью которого генератор счетных импульсов 13 останавливается и процесс формирования сочетаний заканчивается.

Осуществимость изобретения обосновывается тем, что в нем используются по своему прямому функциональному назначению известные в электронной промышленности блоки, узлы и элементы. В организации-заявителе изготовлена модель заявленного формирователя сочетаний в 2013 году.

Положительный эффект от использования изобретения состоит в том, что упрощается схемная и алгоритмическая реализация формирователя сочетаний за счет замены сложных функциональных блоков, используемых в прототипе, а именно: матрицы перебора сочетаний Паскаля, релейных замыкающих и размыкающих коммутаторов, на предлагаемые типовые двоичные n-разрядные счетчики и дешифраторы. Кроме того, расширяются функциональные возможности формирователя сочетаний за счет обеспечения возможности формирования сочетаний из N по m чисел в µ-й системе счисления при m≤N и µ≥N+1 в количестве

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Устройство для моделирования графов | 1984 |

|

SU1218392A1 |

| Устройство для управления асинхронным электроприводом | 1987 |

|

SU1522373A1 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Устройство для определения медианы случайного процесса | 1986 |

|

SU1352502A2 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ НЕПЕРЕКРЫВАЮЩИХСЯ ШАБЛОНОВ БИТ | 2023 |

|

RU2798197C1 |

| Измеритель временных интервалов | 1979 |

|

SU845140A1 |

Изобретение относится к области вычислительной техники и может быть использовано в устройствах для решения комбинаторных задач. Технический результат заключается в обеспечении возможности формирования каждого элемента сочетания в n-разрядном двоичном счетчике, контроль значений которого осуществляется с помощью позиционного дешифратора. Технический результат достигается за счет формирователя сочетаний, который содержит блок m двоичных n-разрядных счетчиков, m позиционных дешифраторов, блок m элементов ИЛИ, блоки элементов И, блоки линий задержек, линию задержки, блок m элементов отображения сочетаний, триггеры RS-типа и генератор счетных импульсов. 1 ил.

Формирователь сочетаний из N по m символов, содержащий генератор счетных импульсов, блок m счетчиков, блок m элементов отображения сочетаний, первый и второй блок линий задержек, отличающийся тем, что содержит блок m позиционных дешифраторов, первый и второй асинхронные RS триггеры, линию задержки, блок n элементов ИЛИ, первый, второй и третий блоки элементов И, каждый элемент отображения сочетаний выполнен с n-разрядным информационным и управляющим входами, первый и второй блоки линий задержки выполнены с (m-1) линиями задержек, каждый счетчик выполнен двоичным n-разрядным с счетным входом C, с n-разрядным информационным входом A для записи в счетчик информации в параллельном коде, с n-разрядным информационным выходом B для съема информации со счетчика в параллельном коде, с управляющим входом V для разрешения записи в счетчик информации через вход A и с управляющим входом R для установки значения счетчика в ноль, соединенным с запускающим входом формирователя, счетчики соединены между собой последовательно n-разрядными шинами, так, что выход B i-го счетчика соединен со входом A (i+1)-го счетчика, при этом выход B каждого i-го счетчика соединен посредством n-разрядной шины с информационным входом соответствующего элемента отображения сочетаний, управляющие входы R первого и второго асинхронных RS триггеров соединены с запускающим входом формирователя, инверсный выход первого асинхронного RS триггера связан с входом запуска генератора счетных импульсов, каждый i-й позиционный дешифратор выполнен с информационным n-разрядным входом, соединенным посредством n-разрядной шины с выходом B i-го счетчика, и с µ выходами, на которых формируется сигнал «1», если порядковый номер позиционного дешифратора совпадает с значением числа, поступившего на его информационный вход, (N-m+1)-й выход первого позиционного дешифратора соединен с входом S первого асинхронного RS триггера, первый элемент ИЛИ блока m элементов ИЛИ выполнен на два входа, остальные (m-1) элементы ИЛИ выполнены на три входа, выход i-го элемента ИЛИ соединен с входом С i-го счетчика, элементы И первого блока m элементов И выполнены с двумя инверсными входами и с одним прямым входом, который подключен к выходу генератора счетных импульсов, один инверсный вход i-го элемента И первого блока m элементов И соединен с i-м выходом i-го позиционного дешифратора, другой инверсный вход i-го элемента И первого блока m элементов И подключен к прямому выходу второго асинхронного RS триггера, выход i-го элемента И первого блока m элементов И соединен с одним из входов i-го элемента ИЛИ, элементы И второго блока m элементов И выполнены с двумя прямыми входами и с одним инверсным входом, который соединен с (N-m+i+1)-м выходом i-го позиционного дешифратора, один прямой вход г-го элемента И второго блока m элементов И соединен с (N-m+i+2)-м выходом (i+1)-го позиционного дешифратора, другой прямой вход i-го элемента И второго блока m элементов И связан с выходом генератора счетных импульсов, выход i-го элемента И второго блока m элементов И соединен с одним из входов i-го элемента ИЛИ и с входом i-й линии задержки первого блока линий задержки, линия задержки (отдельная) включена в цепь между входом m-го элемента ИЛИ и выходом m-го элемента И второго блока m элементов И, к которому подключены управляющие входы всех элементов отображения блока элементов отображения, элементы И третьего блока из (m-1) элементов И выполнены с прямым и с инверсным входом, который соединен с (N-m+i+1)-м выходом i-го позиционного дешифратора, прямой вход элемента И третьего блока из (m-1) элементов И связан с выходом i-й линии задержки первого блока линий задержки, выход i-го элемента И третьего блока из (m-1) элементов И соединен с входом V (i+1)-го счетчика и с входом i-й линии задержки второго блока линий задержки, выход которой соединен с одним из входов (i+1)-го элемента ИЛИ, вход S второго асинхронного RS триггера соединен с (N+1)-м выходом m-го позиционного дешифратора, прямой выход второго асинхронного RS триггера подключен к одному инверсному входу каждого элемента И первого блока m элементов И и к одному прямому входу m-го элемента И второго блока m элементов И, где n≥log2(N+1), i=1, 2, …, m и µ≥N+1.

| Устройство для отливки металлической дроби (песка) | 1951 |

|

SU95872A1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2002 |

|

RU2216850C1 |

| Устройство для перебора сочетаний | 1977 |

|

SU665303A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕБОРА СОЧЕТАНИЙ | 0 |

|

SU238238A1 |

| US 6016401 A, 18.01.2000 | |||

Авторы

Даты

2015-02-27—Публикация

2013-09-25—Подача