Изобретение относится к области импульсной техники и может быть использовано в преобразователях систем управления асинхронными электродвигателями.

Наиболее близким по технической сущности является цифровой модулятор для преобразователя частоты асинхронного двигателя (см. патент РФ 2111608, опубл. в БИ 14, 1998г.), содержащий генератор прямоугольных импульсов, два счетчика, триггер знака, триггер, четыре элемента ИЛИ, элемент И, шесть элементов И-НЕ, дешифратор, два формирователя импульсов, сумматор, регистр, двоично-шестиричный счетчик, схему ограничения и схему сброса.

Недостатком наиболее близкого цифрового модулятора для преобразователя частоты асинхронного двигателя является то, что его выходной сигнал формирует с помощью силового трехфазного транзисторного моста на фазах асинхронного электродвигателя трехфазную систему напряжений переменной частоты и амплитуды, но прямоугольной формы (с учетом усреднения широтно-модулированного сигнала).

Сущность изобретения заключается в том, что в цифровой модулятор для преобразователя частоты асинхронного электродвигателя, содержащий генератор прямоугольных импульсов, первый и второй счетчики, триггер знака, первый триггер, первый, второй, третий и четвертый элементы ИЛИ, инвертор, первый элемент И, первый, второй, третий, четвертый, пятый и шестой элементы И-НЕ, первый дешифратор, первый и второй формирователи импульсов, первый сумматор, первый регистр, двоично-шестиричный счетчик, схему ограничения и схему сброса, причем выход генератора прямоугольных импульсов соединен со счетным входом первого счетчика и первыми входами первого и второго элементов ИЛИ и первого регистра, вторые входы первого и второго элементов ИЛИ соединены соответственно с прямым и инверсным выходами триггера знака, первый вход которого соединен с шиной знака, а второй вход - с выходом инвертора, выходы первого и второго элементов ИЛИ соединены соответственно с входами обратного и прямого счета второго счетчика, разрядные входы которого соединены с выходом схемы ограничения, разрядные входы которой соединены с шиной входного сигнала, а знаковый вход - с шиной знака, разрядные входы первого счетчика соединены с общей шиной, а выход переноса - с первым входом первого элемента И, прямой и инверсный выходы триггера знака соединены соответственно с первыми входами третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходом первого формирователя импульсов, первый, второй и третий входы первого дешифратора соединены соответственно с первым, вторым и третьим выходами двоично-шестиричного счетчика, входы прямого и обратного счета которого соединены соответственно с выходами третьего и четвертого элементов ИЛИ, выход схемы ограничения соединен с первым входом первого сумматора, выход которого соединен с вторым входом первого регистра, выход которого соединен с вторым входом первого сумматора, выход схемы сброса соединен с вторым входом первого элемента И и третьим входом первого регистра, выход переноса второго счетчика соединен с первым входом первого триггера, выход которого соединен с четвертым входом первого дешифратора, выход первого элемента И соединен с вторым входом первого триггера, входами записи информации первого и второго счетчиков и входом инвертора, выход первого формирователя импульсов соединен с входом второго формирователя импульсов, первый, второй, третий, четвертый, пятый и шестой выходы первого дешифратора соединены соответственно с первыми входами пятого, первого, шестого, второго, четвертого и третьего элементов И-НЕ, выходы которых соединены с выходными шинами, дополнительно введены третий и четвертый счетчики, второй триггер, второй элемент И, второй и третий дешифраторы, второй сумматор и второй регистр, причем выход схемы ограничения соединен с первым входом второго сумматора, выход которого соединен с первым входом второго регистра, выход второго регистра соединен с вторым входом второго сумматора и разрядными входами третьего счетчика, выход переноса которого соединен с первым входом второго триггера, старший разряд выхода первого регистра соединен с вторым входом второго регистра и счетным входом четвертого счетчика, выход переноса которого соединен с входом первого формирователя импульсов, первый, второй и третий выходы двочно-шестиричного счетчика соединены соответственно с первым, вторым и третьим входами второго и третьего дешифраторов, прямой и инверсный выходы второго триггера соединены соответственно с четвертыми входами второго и третьего дешифраторов, выход генератора прямоугольных импульсов соединен со счетным входом третьего счетчика, выход первого элемента И соединен с вторым входом второго триггера и входом записи информации третьего счетчика, выход первого триггера соединен с пятыми входами второго и третьего дешифраторов, выход второго формирователя импульсов соединен с пятыми входами второго и третьего дешифраторов и первым входом второго элемента И, выход которого соединен с третьим входом второго регистра, выход схемы сброса соединен с вторым входом второго элемента И, первый, второй, третий, четвертый, пятый и шестой выходы второго дешифратора соединены соответственно с вторыми входами первого, шестого, второго, четвертого, третьего и пятого элементов И-НЕ, а первый, второй, третий, четвертый, пятый и шестой выходы третьего дешифратора соединены соответственно с третьими входами третьего, пятого, первого, шестого, второго и четвертого элементов И-НЕ.

Существенные отличия находят свое выражение в новой совокупности связей между элементами устройства. Указанная совокупность связей позволяет на выходе цифрового модулятора получить сигнал, который при управлении силовым трехфазным транзисторным мостом формирует на фазах асинхронного электродвигателя трехфазную квазисинусоидальную систему напряжений переменной частоты и амплитуды.

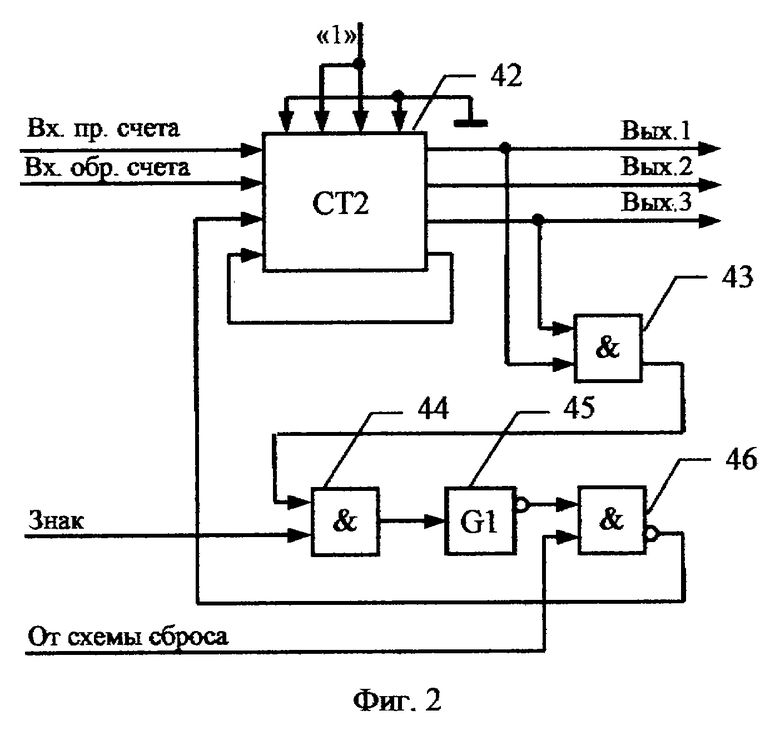

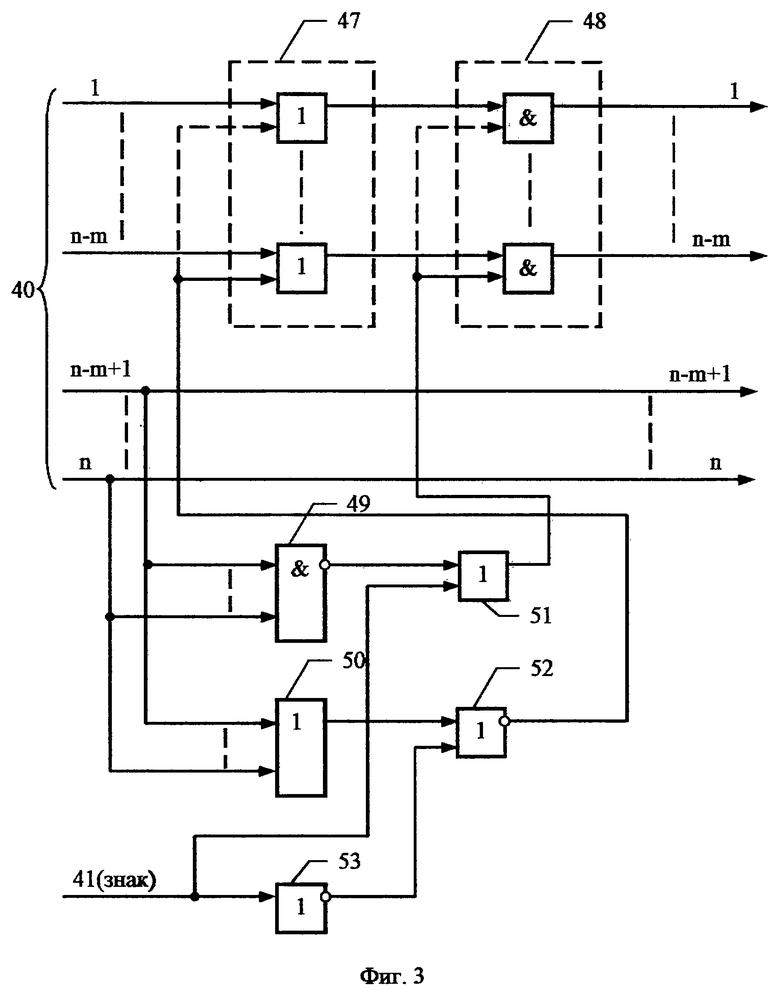

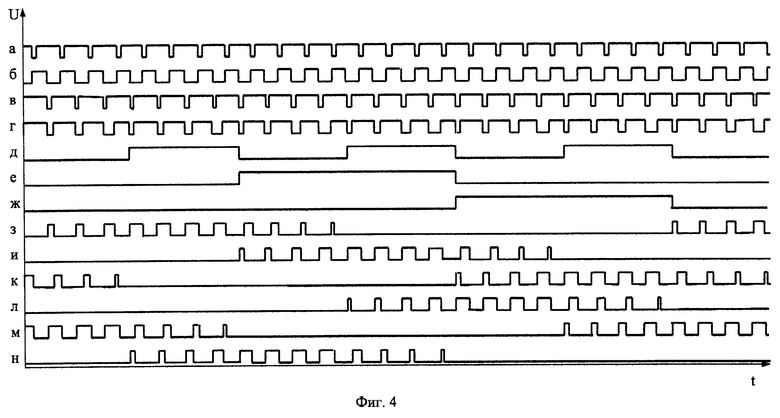

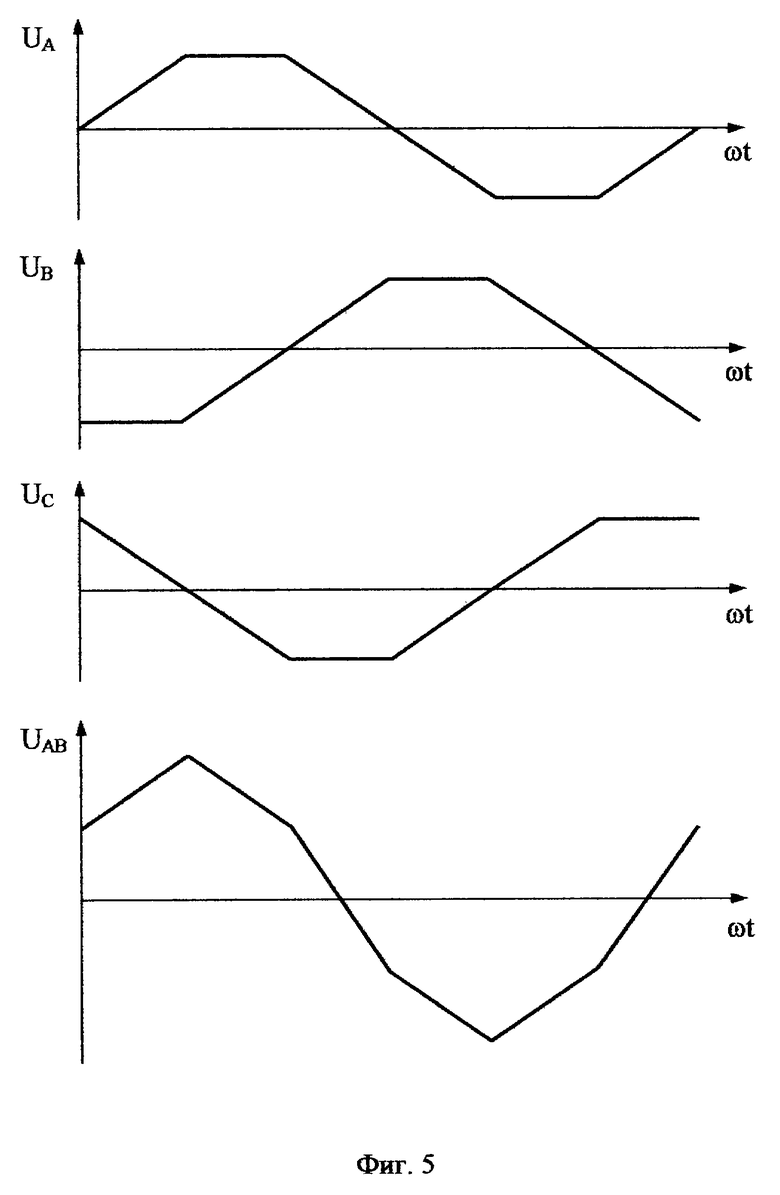

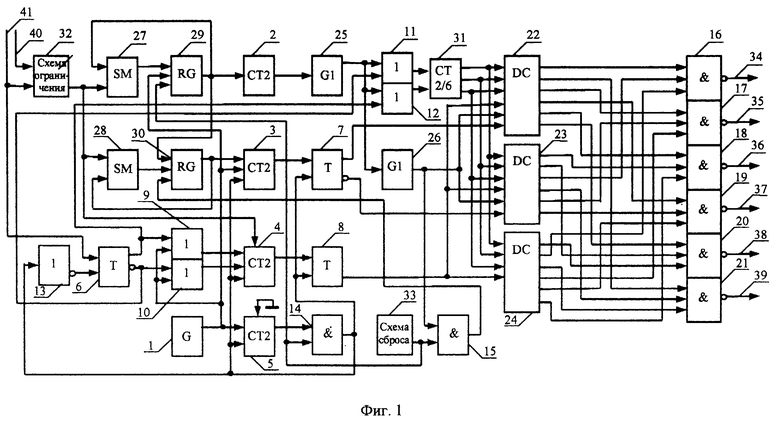

На фиг.1 представлена функциональная схема цифрового модулятора для преобразователя частоты асинхронного электродвигателя, на фиг.2 - функциональная схема двоично-шестиричного счетчика, на фиг.3 - функциональная схема схемы ограничения, на фиг.4 - временные диаграммы работы устройства, на фиг. 5 - диаграммы фазных и линейного напряжений на фазах асинхронного электродвигателя.

Цифровой модулятор для преобразователя частоты асинхронного электродвигателя (фиг. 1) содержит генератор 1 прямоугольных импульсов, счетчики 2, 3, 4 и 5, триггер 6 знака, триггеры 7 и 8, элементы 9, 10, 11 и 12 ИЛИ, инвертор 13, элементы 14 и 15 И, элементы 16, 17, 18, 19, 20 и 21 И-НЕ, дешифраторы 22, 23 и 24, формирователь 25 и 26 импульсов, сумматоры 27 и 28, регистры 29 и 30, двоично-шестиричный счетчик 31, схему 32 ограничения, схему 33 сброса, выходные шины 34, 35, 36, 37, 38 и 39, шину 40 входного сигнала и шину 41 знака.

Выход генератора 1 прямоугольных импульсов соединен со счетными входом счетчиков 3 и 5 и первыми входами элементов 9 и 10 ИЛИ и регистра 29. Вторые входы элементов 9 и 10 ИЛИ соединены соответственно с прямым и инверсным выходами триггера 6 знака, первый вход которого соединен с шиной 41 знака, а второй вход - с выходом инвертора 13. Выходы элементов 9 и 10 ИЛИ соединены соответственно с входами обратного и прямого счета счетчика 4, разрядные входы которого соединены с выходом схемы 32 ограничения. Разрядные входы схемы 32 ограничения соединены с шиной 40 входного сигнала, а знаковый вход - с шиной 41 знака. Разрядные входы счетчика 5 соединены с общей шиной, а выход переноса - с первым входом элемента 14 И. Прямой и инверсный выходы триггера 6 знака соединены соответственно с первыми входами элементов 12 и 11 ИЛИ, вторые входы которых соединены с выходом формирователя 25 импульсов. Первый, второй и третий входы дешифраторов 22, 23 и 24 соединены соответственно с первым, вторым и третьим выходами двоично-шестиричного счетчика 31, входы прямого и обратного счета которого соединены соответственно с выходами элементов 12 и 11 ИЛИ. Выход схемы 32 ограничения соединен с первым входом сумматора 27, выход которого соединен с вторым входом регистра 29. Выход регистра 29 соединен с вторым входом сумматора 27. Выход схемы 33 сброса соединен с вторым входом элемента 14 И и третьим входом регистра 29, выход переноса счетчика 4 соединен с первым входом триггера 8, выход которого соединен с четвертым входом дешифратора 24. Выход элемента 14 И соединен с вторым входом триггера 8, входами записи информации счетчиков 3, 4 и 5 и входом инвертора 13. Выход формирователя 25 импульсов соединен с входом формирователя 26 импульсов. Первый, второй, третий, четвертый, пятый и шестой выходы дешифратора 24 соединены соответственно с первыми входами пятого, первого, шестого, второго, четвертого и третьего элементов 20, 16, 21, 17, 19 и 18 И-НЕ. Выходы элементов 16, 17, 18, 19, 20 и 21 И-НЕ соединены с выходными шинами 34, 35, 36, 37, 38 и 39. Выход схемы 32 ограничения соединен с первым входом сумматора 28, выход которого соединен с первым входом регистра 30. Выход регистра 30 соединен с вторым входом сумматора 28 и разрядными входами счетчика 3, выход переноса которого соединен с первым входом триггера 7. Старший разряд выхода регистра 29 соединен с вторым входом регистра 30 и счетным входом счетчика 2, выход переноса которого соединен с входом формирователя 25 импульсов. Прямой и инверсный выходы триггера 7 соединены соответственно с четвертыми входами дешифраторов 22 и 23. Выход элемента 14 И соединен с вторым входом триггера 7 и входом записи информации счетчика 3. Выход триггера 8 соединен с пятыми входами дешифраторов 22 и 23. Выход формирователя 26 импульсов соединен с шестыми входами дешифраторов 22 и 23 и первым входом элемента 15 И, выход которого соединен с третьим входом регистра 30. Выход схемы 33 сброса соединен с вторым входом элемента 15 И. Первый, второй, третий, четвертый, пятый и шестой выходы дешифратора 22 соединены соответственно с вторыми входами первого, шестого, второго, четвертого, третьего и пятого элементов 16, 21, 17, 19, 18 и 20 И-НЕ. Первый, второй, третий, четвертый, пятый и шестой выходы дешифратора 23 соединены соответственно с третьими входами третьего, пятого, первого, шестого, второго и четвертого элементов 18, 20, 16, 21, 17 и 19 И-НЕ.

Генератор 1 прямоугольных импульсов может быть выполнен, например, на микросхеме 155ЛА3 с кварцевой стабилизацией или с времязадающим конденсатором. Счетчики 2, 3, 4 и 5, например, выполнены на микросхемах К555ИЕ7, триггер 6 знака и триггеры 7 и 8 могут быть выполнены на микросхемах К555ТМ2. Элементы 9, 10, 11 и 12 ИЛИ, например, выполнены на микросхеме К555ЛЛ1, инвертор 13 - на микросхеме К555 ЛН1, элементы 14 и 15 И - на микросхеме К555ЛИ1, элементы 16, 17, 18, 19, 20 и 21 И-НЕ - на микросхемах К155ЛА4. Дешифраторы 22, 23 и 24 могут быть выполнены, например, на микросхемах К555ИД7, формирователи 25 и 26 импульсов - на микросхеме К555АГ3, сумматоры 27 и 28 - на микросхемах К555ИМ6, регистры 29 и 30 - на микросхемах К555ТМ8.

Двоично-шестиричный счетчик 31 (фиг.2), например, содержит двоичный счетчик 42, элементы 43 и 44 И, формирователь 45 импульсов, элемент 46 И-НЕ. Первый, второй и третий разряды счетчика 42 являются соответственно первым, вторым и третьим выходами двоично-шестиричного счетчика 31. Первый и третий выходные разряды счетчика 42 соединены соответственно с первым и вторым входами элемента 43 И, выход которого соединен с первым входом элемента 44 И. Выход элемента 44 И соединен с входом формирователя 45 импульсов, выход которого соединен с первым входом элемента 46 И-НЕ. Выход элемента 46 И-НЕ соединен с входом сброса счетчика 42. Второй вход элемента 44 И соединен с инверсным выходом триггера 6 знака. Второй вход элемента 46 И-НЕ соединен с выходом схемы 33 сброса. Выход переноса счетчика 42 соединен с входом записи информации названного счетчика. Первый и четвертый разряды входа предварительной установки счетчика 42 соединены с общей шиной, а на второй и третий разряды подается сигнал логической единицы. Входы прямого и обратного счета счетчика 42 являются одноименными входами двоично-шестиричного счетчика 31.

Схема 32 ограничения (фиг. 3) содержит, например, группу 47 элементов ИЛИ, группу 48 элементов И, элемент 49 И-НЕ, элементы 50 и 51 ИЛИ, элемент 52 ИЛИ-НЕ и инвертор 53.

В зависимости от величины, на которой должен быть ограничен входной сигнал, n-разрядные входы шины 40 разбиваются на две группы: с 1 до (n-m) и с (n-m+1) до n, причем m<n. Первая группа разрядов - с 1 до (n-m) соединена с первыми входами группы 47 элементов ИЛИ, выходы которых соединены с первыми входами группы 48 элементов И, выходы которых являются (n-m) младшими разрядами выхода схемы 32 ограничения. Вторая группа разрядных входов шины 40 - с (n-m+1) по n является соответствующими разрядами выхода схемы 32 ограничения. Они соединены с m входами элемента 49 И-НЕ и элемента 50 ИЛИ. Выход элемента 49 И-НЕ соединен с первым входом элемента 51 ИЛИ, выход которого соединен со вторыми входами группы 48 элементов И. Выход элемента 50 ИЛИ соединен с первым входом элемента 52 ИЛИ-НЕ, второй вход которого соединен с выходом инвертора 53, а выход - со вторыми входами группы 47 элементов ИЛИ. Второй вход элемента 51 ИЛИ и вход инвертора 53 соединены с шиной 41 знака.

Схема 33 сброса, например, может быть выполнена в виде последовательно соединенных резистора и конденсатора, причем второй вывод резистора присоединяется к шине питания, а второй вывод конденсатора - к общей шине. Вывод сопротивления, соединенный с конденсатором, является выходом схемы 33 сброса.

Цифровой модулятор для преобразователя частоты асинхронного электродвигателя работает следующим образом.

После включения напряжения питания схема 33 сброса формирует сигнал, который устанавливает в исходное состояние регистр 29. Этот же сигнал через элемент 15 И устанавливает в исходное состояние регистр 30, а через элемент 14 И устанавливает в исходное состояние триггеры 7 и 8, стробирует счетчики 3, 4 и 5 и далее через инвертор 13 стробирует триггер 6 знака. При этом входной сигнал, пройдя через схему 32 ограничения, записывается в прямом (при положительном знаке сигнала) или дополнительном (при отрицательном знаке сигнала) коде в счетчик 4, а код знака этого сигнала записывается в триггер 6 знака. В зависимости от знака входного сигнала импульсы генератора 1 с частотой f0 проходят либо через элемент 9 ИЛИ (знак положительный), либо элемент 10 ИЛИ (знак отрицательный) и поступают соответственно либо на вход обратного счета, либо на вход прямого счета счетчика 4. В зависимости от величины N мантиссы входного сигнала на выходах переноса счетчика 3 через промежуток времени

где n - количество разрядов двоичного счетчика;

N - мантисса входного числа,

после начальной установки (стробирования) появится отрицательный импульс (фиг. 4 а). Этот отрицательный импульс с выхода счетчика 4 поступает на вход установки триггера 8, на выходе которого при этом появляется сигнал высокого уровня (фиг. 4 б). Прямоугольные импульсы с генератора 1 поступают также на счетный вход счетчика 5. Поэтому на выходе переноса счетчика 5 через промежуток времени

после начальной установки появляется отрицательный импульс (фиг.4 в), который, пройдя через элемент 14 И, поступает на вход сброса триггера 8 и возвращает его в исходное состояние. Отрицательный импульс с выхода счетчика 5 через элемент 14 И стробирует счетчики 3, 4 и 5 и через инвертор 13 - триггер 6 знака, после чего процесс формирования выходных сигналов счетчиков 4 и 5 и триггера 8 повторяется. В результате на выходе триггера 8 (фиг.4б) формируется сигнал со скважностью

Одновременно с работой названных выше элементов входной сигнал через схему 32 ограничения поступает на вход сумматора 27 и суммируется с сигналом на выходе регистра 29. В первоначальный момент времени на выходе регистра 29 находится нулевой сигнал. По приходе импульса с генератора 1 в регистр 29 записывается сигнал с выхода сумматора 27 и далее процесс повторяется. В результате происходит нарастание сигнала на выходе сумматора 27 и регистра 29. Вследствие этого на старшем разряде выхода регистра 29 появляется сигнал высокого уровня с частотой f1, которая при наличии двойной разрядности сумматора 27 и регистра 29 линейно зависит от величины N входного сигнала:

Наряду с этим входной сигнал через схему 32 ограничения поступает на вход сумматора 28 со сдвигом вправо на k разрядов и суммируется с сигналом на выходе регистра 30. В первоначальный момент времени на выходе регистра 30 находится нулевой сигнал. По приходе импульса со старшего разряда регистра 29 в регистр 30 записывается сигнал с выхода сумматора 28 и далее процесс повторяется. В результате на выходе регистра 30 происходит линейное нарастание сигнала. Этот сигнал записывается при стробировании в счетчик 3, на выходе переноса которого появляется отрицательный импульс через интервал времени t3, зависящий от величины сигнала на входе счетчика 3. Этот отрицательный импульс поступает на вход установки триггера 7, на выходе которого появляется сигнал высокого уровня. По приходу на вход сброса триггера 7 отрицательного импульса с выхода элемента 14 И на выходе триггера 7 устанавливается сигнал низкого уровня. И далее процесс повторяется. В результате на прямом выходе триггера 7 формируется сигнал переменной скважности (при неизменном сигнале на входе цифрового модулятора)

и при положительном знаке входного сигнала эта скважность линейно возрастает (фиг. 4 г). На инверсном выходе триггера 7 также формируется сигнал переменной скважности

γИ = 1-γП.

Импульсы со старшего разряда выхода регистра 29 поступают на вход счетчика 2, имеющего k двоичных разрядов. На выходе переноса счетчика 2 появляются импульсы с частотой

Эти импульсы поступают на вход формирователя 25 импульсов и далее на формирователь 26 импульсов. Отрицательный импульс с выхода формирователя 26, пройдя через элемент 15 И, сбрасывает выходной сигнал регистра 30 на ноль. Затем процесс формирования линейно изменяющегося сигнала на выходе регистра 30 и переменной скважности на выходах триггера 7 повторяется.

Импульсы с формирователя 25 поступают в зависимости от знака входного сигнала либо на вход прямого счета, либо на вход обратного счета двоично-шестиричного счетчика 31. При этом на первом, втором и третьем выходах названного счетчика формируются периодические сигналы (фиг.4 д, е, ж соответственно), причем частота f появления одного и того же кодового сочетания на этих выходах

В зависимости от кодового сочетания сигналов выходов двоично-шестиричного счетчика 31 и сигналов с триггеров 7 и 8 дешифраторы 22, 23 и 24 через элементы 16, 17, 18, 19, 20 и 21 И-НЕ подают частотно-широтно-модулированный сигнал на выходные шины 34, 35, 36, 37, 38 и 39 (фиг.4 з, и, к, л, м, н) цифрового модулятора. При этом частота f смены сочетаний работающих выходов и скважности γ, γП и γИ меняются в функции входного сигнала, а форма фазных и линейного напряжений (с учетом усреднения широтно-модулированного сигнала) принимает вид, изображенный на фиг.5.

Сигнал с выхода формирователя 26 импульсов используется также для блокировки дешифраторов 22 и 23, что позволяет организовать раздвижки фронтов при смене кодовой комбинации на выходе двоично-шестиричного 31.

Схема 32 ограничения предназначена для ограничения на определенном уровне входного сигнала с целью исключения возможности опрокидывания широтно-импульсной модуляции.

Таким образом, предложенный цифровой модулятор для преобразователя частоты асинхронного электродвигателя позволяет получить выходной сигнал, который при управлении силовым трехфазным транзисторным мостом формирует на фазах асинхронного электродвигателя трехфазную квазисинусоидальную систему напряжений переменной частоты и амплитуды.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ УПРАВЛЕНИЯ СИНХРОННЫМ ЭЛЕКТРОДВИГАТЕЛЕМ | 2012 |

|

RU2517423C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ ДВУХФАЗНОГО АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 1997 |

|

RU2126198C1 |

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАНИЯ ЧАСТОТЫ | 2016 |

|

RU2644070C1 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ СИСТЕМЫ УПРАВЛЕНИЯ ЭЛЕКТРОМАГНИТНЫМ ПОДВЕСОМ РОТОРА | 2010 |

|

RU2433443C1 |

| Цифровой модулятор для преобразователя частоты | 2021 |

|

RU2762287C1 |

| Цифровой модулятор | 1991 |

|

SU1800604A1 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ СИСТЕМЫ УПРАВЛЕНИЯ ЭЛЕКТРОМАГНИТНЫМ ПОДВЕСОМ РОТОРА | 2009 |

|

RU2417390C2 |

| ЦИФРОВОЙ ИНТЕГРАЛЬНЫЙ РЕГУЛЯТОР | 2006 |

|

RU2325681C2 |

| Цифровой модулятор для преобразователя частоты | 2021 |

|

RU2774161C1 |

Изобретение относится к импульсной технике и может быть использовано в преобразователях систем управления асинхронными электродвигателями. Цифровой модулятор для преобразователя частоты асинхронного электродвигателя содержит генератор прямоугольных импульсов, счетчики, триггер знака, триггеры, элементы ИЛИ, инвертор, элементы И, элементы И-НЕ, дешифраторы, формирователь импульсов, сумматоры, регистры, двоично-шестиричный счетчик, схему ограничения, схему сброса, выходные шины, шину входного сигнала и шину знака. В результате цифровой модулятор для преобразователя частоты асинхронного электродвигателя позволяет получить выходной сигнал, который при управлении силовым трехфазным транзисторным мостом формирует на фазах асинхронного электродвигателя трехфазную квазисинусоидальную систему напряжений переменной частоты и амплитуды. 5 ил.

Цифровой модулятор для преобразователя частоты асинхронного электродвигателя, содержащий генератор прямоугольных импульсов, первый и второй счетчики, триггер знака, первый триггер, первый, второй, третий и четвертый элементы ИЛИ, инвертор, первый элемент И, первый, второй, третий, четвертый, пятый и шестой элементы И-НЕ, первый дешифратор, первый и второй формирователи импульсов, первый сумматор, первый регистр, двоично-шестиричный счетчик, схему ограничения и схему сброса, причем выход генератора прямоугольных импульсов соединен со счетным входом первого счетчика и первыми входами первого и второго элементов ИЛИ и первого регистра, вторые входы первого и второго элементов ИЛИ соединены соответственно с прямым и инверсным выходами триггера знака, первый вход которого соединен с шиной знака, а второй вход - с выходом инвертора, выходы первого и второго элементов ИЛИ соединены соответственно с входами обратного и прямого счета второго счетчика, разрядные входы которого соединены с выходом схемы ограничения, разрядные входы которой соединены с шиной входного сигнала, а знаковый вход - с шиной знака, разрядные входы первого счетчика соединены с общей шиной, а выход переноса - с первым входом первого элемента И, прямой и инверсный выходы триггера знака соединены соответственно с первыми входами третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходом первого формирователя импульсов, первый, второй и третий входы первого дешифратора соединены соответственно с первым, вторым и третьим выходами двоично-шестиричного счетчика, входы прямого и обратного счета которого соединены соответственно с выходами третьего и четвертого элементов ИЛИ, выход схемы ограничения соединен с первым входом первого сумматора, выход которого соединен с вторым входом первого регистра, выход которого соединен с вторым входом первого сумматора, выход схемы сброса соединен с вторым входом первого элемента И и третьим входом первого регистра, выход переноса второго счетчика соединен с первым входом первого триггера, выход которого соединен с четвертым входом первого дешифратора, выход первого элемента И соединен с вторым входом первого триггера, входами записи информации первого и второго счетчиков и входом инвертора, выход первого формирователя импульсов соединен с входом второго формирователя импульсов, первый, второй, третий, четвертый, пятый и шестой выходы первого дешифратора соединены соответственно с первыми входами пятого, первого, шестого, второго, четвертого и третьего элементов И-НЕ, выходы которых соединены с выходными шинами, отличающийся тем, что в него дополнительно введены третий и четвертый счетчики, второй триггер, второй элемент И, второй и третий дешифраторы, второй сумматор и второй регистр, причем выход схемы ограничения соединен с первым входом второго сумматора, выход которого соединен с первым входом второго регистра, выход второго регистра соединен с вторым входом второго сумматора и разрядными входами третьего счетчика, выход переноса которого соединен с первым входом второго триггера, старший разряд выхода первого регистра соединен с вторым входом второго регистра и счетным входом четвертого счетчика, выход переноса которого соединен с входом первого формирователя импульсов, первый, второй и третий выходы двоично-шестиричного счетчика соединены соответственно с первым, вторым и третьим входами второго и третьего дешифраторов, прямой и инверсный выходы второго триггера соединены соответственно с четвертыми входами второго и третьего дешифраторов, выход генератора прямоугольных импульсов соединен со счетным входом третьего счетчика, выход первого элемента И соединен с вторым входом второго триггера и входом записи информации третьего счетчика, выход первого триггера соединен с пятыми входами второго и третьего дешифраторов, выход второго формирователя импульсов соединен с шестыми входами второго и третьего дешифраторов и первым входом второго элемента И, выход которого соединен с третьим входом второго регистра, выход схемы сброса соединен с вторым входом второго элемента И, первый, второй, третий, четвертый, пятый и шестой выходы второго дешифратора соединены соответственно с вторыми входами первого, шестого, второго, четвертого, третьего и пятого элементов И-НЕ, а первый, второй, третий, четвертый, пятый и шестой выходы третьего дешифратора соединены соответственно с третьими входами третьего, пятого, первого, шестого, второго и четвертого элементов И-НЕ.

| ЦИФРОВОЙ МОДУЛЯТОР ДЛЯ ПРЕОБРАЗОВАТЕЛЯ ЧАСТОТЫ АСИНХРОННОГО ДВИГАТЕЛЯ | 1995 |

|

RU2111608C1 |

| ЦИФРОВОЙ ШИРОТНО-ИМПУЛЬСНЫЙ МОДУЛЯТОР | 1999 |

|

RU2172062C2 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ПОСТОЯННОГО НАПРЯЖЕНИЯ В КВАЗИСИНУСОИДАЛЬНОЕ С ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 1994 |

|

RU2071634C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ТРЕХФАЗНОЕ КВАЗИСИНУСОИДАЛЬНОЕ НАПРЯЖЕНИЕ | 1991 |

|

RU2014719C1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ЧАСТОТЫ ВРАЩЕНИЯ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 1993 |

|

RU2085018C1 |

| Цифровой широтно-импульсный модулятор | 1988 |

|

SU1647881A2 |

| US 4502024 А, 26.02.1985 | |||

| US 4931751 А, 05.06.1990 | |||

| УСТРОЙСТВО для ДОЗИРОВАНИЯ СЫПУЧИХ МАТЕРИАЛОВ | 0 |

|

SU352137A1 |

Авторы

Даты

2003-11-20—Публикация

2002-02-26—Подача