Изобретение относится к системам телекоммуникаций, а именно к системам вещания данных по радио и телевизионным каналам и преимущественно может быть использовано в системах с введением данных в течение длительности вертикального гасящего импульса телевизионного сигнала.

Известно устройство для приема данных цифровых вещательных систем, передаваемых во время кадрового гасящего интервала телевизионного видеосигнала [1] , содержащее схему выделения цифровых данных, вставленных в видеосигнал; средства для обнаружения ошибок в данных, передаваемых в течении периода строчной развертки; буферную память для временного хранения этих данных; средства исправления ошибок в данных.

Известное устройство позволяет исправлять многократные битовые ошибки в принимаемых пакетах данных путем использования мажоритарно-декодируемого кода.

Недостаток устройства - недостаточно высокая помехоустойчивость, обусловленная невозможностью исправления ошибок типа вставок или выпадений пакетов.

Известно устройство для приема данных из канала воспроизведения накопителя информации на магнитной ленте [2], содержащее усилитель воспроизведения, буферную память, схему формирования адреса записи, схему формирования адреса чтения, схему обнаружения синхронизирующих кодов блоков, схему определения адреса кода синхронизации, схему обнаружения/исправления ошибок, схему определения идентифицирующих данных блока, адресную арифметическую схему, схему определения адреса идентифицирующих данных сектора, схему чтения данных преамбулы.

Известное устройство позволяет исправлять с помощью помехоустойчивых кодов Рида-Соломона символьные ошибки в принимаемых блоках данных, составляющих сектор, и надежно определять начало сектора.

К недостаткам устройства можно отнести:

1) недостаточно высокая помехоустойчивость, обусловленная невозможностью исправления ошибок типа вставок или выпадений блоков данных в составе секторов;

2) устройство не может работать в мультиплексированных каналах с асинхронным появлением пакетов.

Наиболее близким по технической сущности к заявляемому решению является выбранное в качестве прототипа устройство оптической записи и воспроизведения данных [3] , обрабатывающее данные из канала воспроизведения оптических накопителей информации. Устройство-прототип содержит демодулятор, схему определения начала пакета, последовательно-параллельный преобразователь, регистр-защелку номера пакета, схему обнаружения и исправления ошибок в номерах пакетов, схему управления записью/считыванием, буферную память для блоков данных, схему обнаружения и исправления ошибок в блоках данных, буферную память данных. Кроме того, устройство-прототип содержит схему модуляции, мультиплексор адресов, ПЗУ для организации перемежения символов кодовых слов блока данных, схему воспроизведения тактовых импульсов, буферные элементы с тремя состояниями.

Устройство-прототип определяет начало пакета данных, выделяет записанный в начале пакета номер пакета, восстанавливает номер в случае искажения его ошибками, использует этот номер в качестве части адреса для последующей записи содержимого пакета в буферную память для блоков данных. Затем блок данных, собранный в этой буферной памяти, обрабатывается схемой обнаружения и коррекции ошибок и пересылается в буферную память для данных.

Использование записанных в начале пакета маркеров начала пакета позволяет ограничить распространение ошибок, вызванных вставками или выпадениями бит пределами текущего пакета. Применение записанных в начале пакета номеров для размещения пакета в буферной памяти ограничивает распространение ошибок, вызванных вставками или выпадениями пакетов блока данных. Схема обнаружения и коррекции ошибок на основе мощных помехоустойчивых блоковых кодов типа кодов Рида- Соломона с перемежением позволяет обеспечить высокую достоверность воспроизведения информации в каналах воспроизведения оптических накопителей.

Устройство-прототип предназначено для работы с немультиплексированными каналами с синхронным появлением пакетов. В таких каналах пакеты блока данных появляются последовательно, с фиксированными временными промежутками между ними. Блоки данных сменяют друг друга последовательно.

Недостатком рассмотренного устройства является невозможность работать с мультиплексированными каналами с асинхронным появлением пакетов, предусматривающими возможность организации нескольких виртуальных каналов в одном широковещательном, в которых каждый следующий пакет блока данных может появляться через произвольный интервал времени.

Технической задачей изобретения является расширение функциональных возможностей устройства для обеспечения помехоустойчивой сборки блоков информации из асинхронно принимаемых пакетов, передаваемых по мультиплексированным каналам передачи информации.

Поставленная техническая задача решается за счет того, что в известное устройство, содержащее выделитель данных, селектор начала пакета, схему выделения символов данных, регистр сдвига, буферный регистр, схему коррекции номеров каналов и пакетов, схему управления записью, счетчик номеров пакетов, счетчик символов данных пакета, буферную память блоков данных, декодер помехоустойчивого кода, буферную память данных, причем вход выделителя данных подключен к шине информационного сигнала, выход последовательных данных выделителя данных соединен с входом последовательных данных регистра сдвига, выход тактовой частоты данных выделителя данных соединен с входом синхронизации регистра сдвига и с первым входом схемы выделения символов данных, выходы регистра сдвига соединены m-разрядной шиной данных с входами данных буферного регистра и с первыми входами селектора начала пакета, вторые входы селектора начала пакета подключены к шине кода начала пакета, выход селектора начала пакета соединен с вторым входом схемы выделения символов данных, выход схемы выделения символов данных соединен с входом записи буферного регистра и с вторым входом схемы управления записью, четвертый вход которой подключен к шине тактовой частоты обработки символов данных пакета, выходы буферного регистра соединены m-разрядной шиной данных с входами схемы коррекции номеров каналов и пакетов и с входами данных буферной памяти блоков данных, первый вход схемы управления записью соединен с выходом признака ошибки декодирования схемы коррекции номеров каналов и пакетов, первые выходы схемы коррекции номеров каналов и пакетов соединены n-разрядной шиной номера пакета с входами данных счетчика номеров пакетов, третий выход схемы управления записью соединен со счетным входом счетчика номеров пакетов и с первым входом сброса счетчика символов данных пакета, четвертый выход схемы управления записью соединен с входом записи счетчика номеров пакетов и вторым входом сброса счетчика символов данных пакета, пятый выход схемы управления записью соединен со счетным входом счетчика символов данных пакета, выходы счетчика номеров пакетов n - разрядной шиной адреса пакета соединены с первыми входами адреса буферной памяти блоков данных, выходы счетчика символов данных пакета соединены n1 - разрядной шиной адреса символа данных пакета с третьими входами адреса ,блоков данных, выходы данных декодера помехоустойчивого кода соединены шиной данных с входами данных буферной памяти данных, входы адреса которой соединены шиной адреса с вторыми выходами адреса декодера помехоустойчивого кода, согласно изобретению введены селектор номера канала, триггер бита половины блока, схема обнаружения половин блока, первый элемент И, счетчик номера блока и сумматор, первые входы селектора номера канала соединены m1-разрядной шиной номера канала с четвертыми выходами схемы коррекции номеров каналов и пакетов, вторые входы селектора номера канала подключены к m1-разрядной шине кода номера канала, выход селектора номера канала соединен с третьим входом схемы управления записью, второй выход схемы коррекции номеров каналов и пакетов соединен с первым входом схемы обнаружения половин блоков и с входом данных триггера бита половины блока, первый выход схемы управления записью соединен с входом синхронизации триггера бита половины блока, второй выход схемы управления записью соединен с вторым входом схемы обнаружения половин блоков, инверсный выход триггера бита половины блока соединен с первым входом первого элемента И, второй вход которого соединен с первым выходом схемы обнаружения половин блока, второй выход которой соединен со счетным входом счетчика номера блока, выход первого элемента И соединен с входом переноса сумматора, входы данных счетчика номера блока подключены к n2 - разрядной шине начального адреса блоков данных в буферной памяти блоков данных, вход записи счетчика номера блока подключен к шине "Загрузка", выходы счетчика номера блока соединены n2 - разрядной шиной с первыми входами данных сумматора, вторые входы данных которого подключены к n2 - разрядной шине логического нуля, выходы сумматора соединены n2 - разрядной шиной адреса блока со вторыми входами адреса буферной памяти блоков данных, причем схема обнаружения половин блока содержит инвертор, второй и третий элементы И, первый, второй, третий и четвертый элементы И-НЕ, счетчик первой половины блока, счетчик второй половины блока, первый и второй дешифраторы и триггер половины блока, первый вход схемы обнаружения половин блока является входом инвертора и первым входом третьего элемента И, второй вход схемы обнаружения половин блока является вторым входом второго и третьего элементов И, выход инвертора соединен с первым входом второго элемента И, выход второго элемента И соединен с первым входом второго элемента И-НЕ и с вторым входом третьего элемента И-НЕ, выход третьего элемента И соединен c вторым входом первого элемента И-НЕ и с первым входом четвертого элемента И-НЕ, выход первого элемента И-НЕ соединен с входом декремента счетчика первой половины блока, вход инкремента которого соединен с выходом второго элемента И-НЕ, выход третьего элемента И-НЕ соединен с входом декремента счетчика второй половины блока, вход инкремента которого соединен с выходом четвертого элемента И-НЕ, выходы счетчика первой половины блока соединены k - разрядной шиной с входами первого дешифратора, выходы счетчика второй половины блока соединены k - разрядной шиной с входами второго дешифратора, первый инверсный выход первого дешифратора соединен с первым входом первого элемента И-НЕ, второй выход первого дешифратора соединен с входом установки S триггера половины блока, третий инверсный выход первого дешифратора соединен с вторым входом второго элемента И-НЕ, первый инверсный выход второго дешифратора соединен с первым входом третьего элемента И-НЕ, второй выход второго дешифратора соединен с входом сброса R триггера половины блока, третий инверсный выход второго дешифратора соединен с вторым входом четвертого элемента И-НЕ, инверсный выход триггера половины блока является первым выходом схемы обнаружения половин блока, прямой выход триггера половины блока является вторым выходом схемы обнаружения половин блока.

Сравнительный анализ с прототипом показывает, что заявленное устройство отличается наличием новых элементов: селектора номера канала 4, триггера бита половины блока 10, схемы обнаружения половин блока 11 (11-23), первого элемента И 25, счетчика номера блока 26 и сумматора 27 с соответствующими связями, и не известно из уровня техники. Таким образом изобретение соответствует критерию "Новизна".

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод, что введенные функциональные блоки известны. Однако введение их в известное устройство с указанными связями придает ему новые свойства. Взаимодействие введенных функциональных блоков обеспечивает возможность применения устройства приема информации из канала в мультиплексированных каналах с асинхронной передачей пакетов. Введение селектора номера канала 4 позволяет в одном широковещательном канале организовать множество виртуальных каналов. Введенная схема обнаружения половин блока 11 обеспечивает надежную фиксацию факта завершения сборки блока данных из асинхронно поступающих из канала пакетов. Эта схема вместе с введенным сумматором 27 управляет адресацией принимаемых пакетов в буферной памяти блоков данных и обеспечивает помехоустойчивую сборку блоков данных из принимаемых пакетов.

Предложенное устройство приема информации из канала для специалистов в этой и смежных областях техники явным образом не следует из уровня техники. Таким образом изобретение соответствует критерию "Изобретательский уровень".

Изобретение соответствует критерию "Промышленная применимость", так как оно может применяться в различных областях техники, например в системах телекоммуникаций, таких как системы распространения компьютерной информации по телевизионным каналам [4, 5].

Сущность изобретения состоит в том, что для функционирования устройства приема информации из канала в мультиплексированных каналах с асинхронной передачей пакетов и для обеспечения способности помехоустойчивой сборки блоков данных из этих пакетов в буферной памяти блоков данных используется схема обнаружения половин блока данных. Работа схемы обнаружения половин блока данных основана на использовании номеров пакетов. Место расположения пакета в буферной памяти блоков данных определяется значением номера пакета, содержимым счетчика номера блока и схемой обнаружения половин блока. Каждый из принимаемых пакетов в зависимости от значения старшего бита номера пакета относится к одной из двух половин блока данных. Схема обнаружения половин блока данных осуществляет подсчет числа принятых пакетов каждой из двух половин блока данных. При превышении числа обнаруженных пакетов половины блока заданного порога с высокой достоверностью принимается решение о завершении приема предыдущей половины блока. Завершение приема второй половины блока означает завершение приема пакетов всего текущего блока, при этом схема обнаружения половин блоков инкрементирует счетчик номера блока. Таким образом, решение о границах блоков принимается с высокой достоверностью на основе анализа множества номеров пакетов. Выпадения или вставки отдельных пакетов не приводят к неправильному определению границ блоков данных и дальнейшему распространению ошибок. Данные в отдельных выпавших и искаженных пакетах могут быть восстановлены с использованием помехоустойчивых кодов Рида-Соломона.

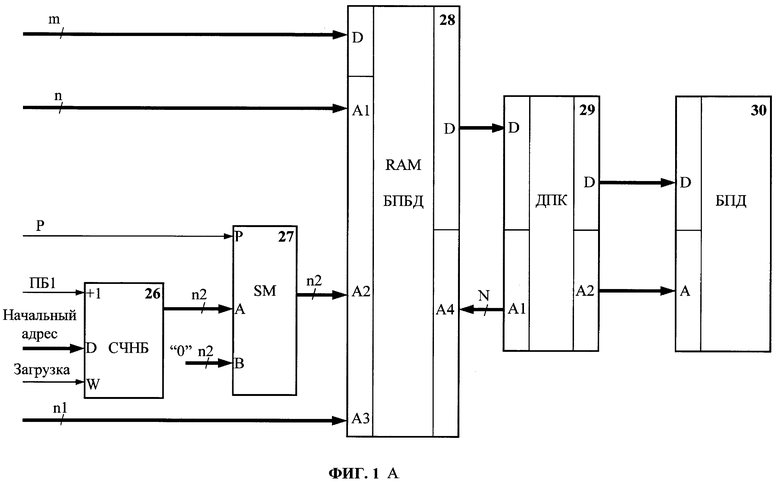

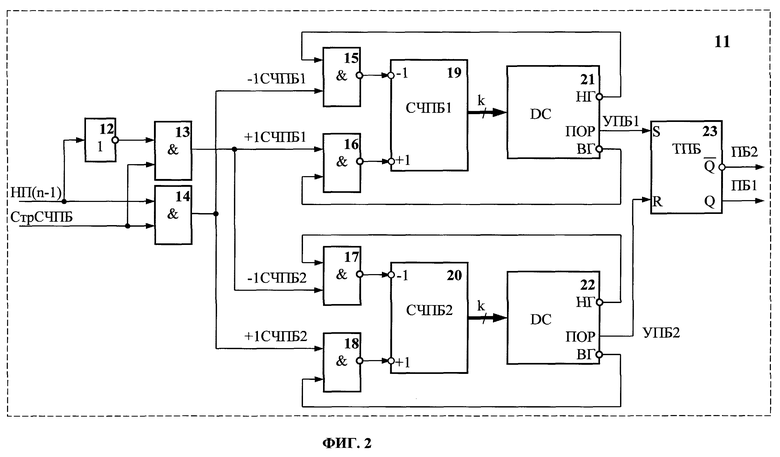

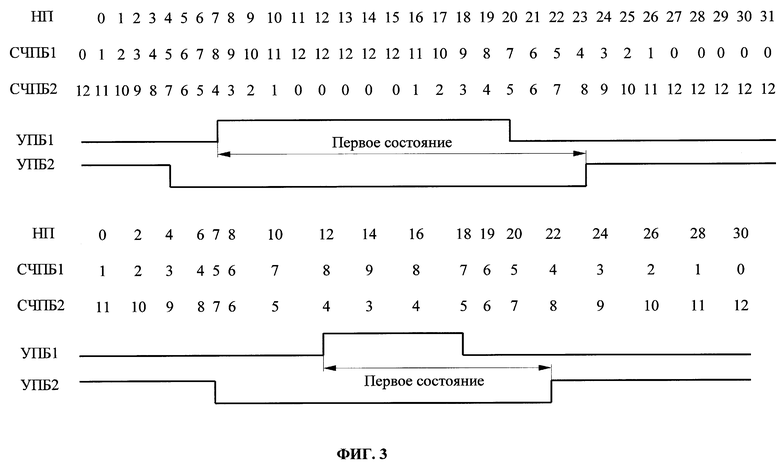

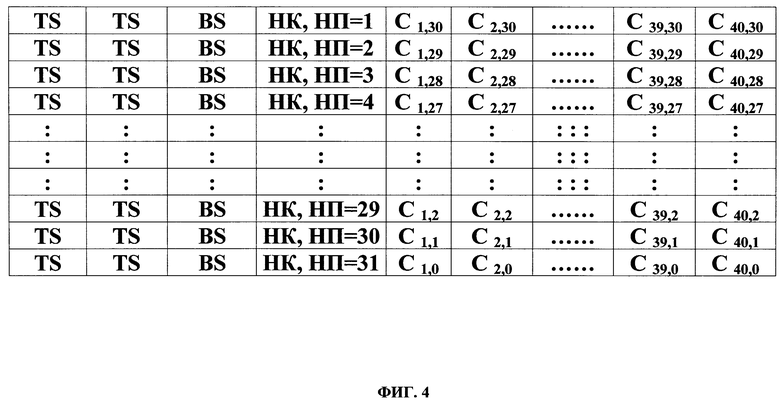

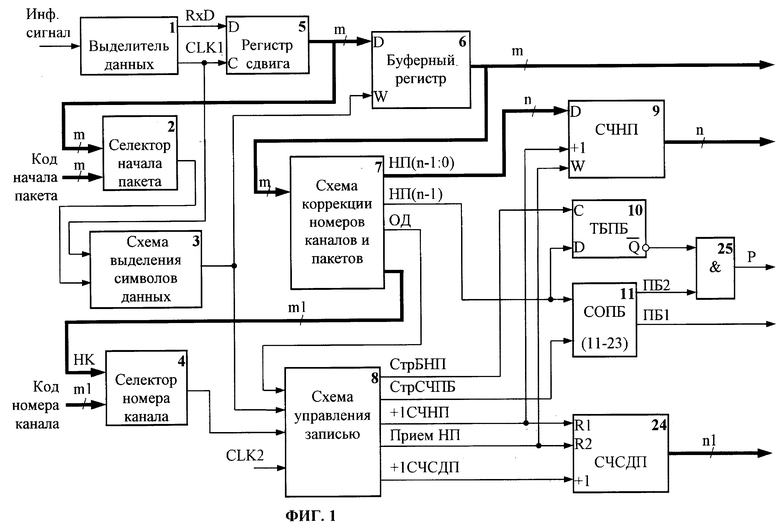

На фиг. 1 показана функциональная схема предлагаемого устройства приема информации из канала; на фиг. 2 - функциональная схема схемы обнаружения половин блока 11; на фиг. 3 - временные диаграммы работы схемы обнаружения половин блоков 11; на фиг. 4 - один из вариантов организации формата блока данных.

В описании устройства и на чертежах используются следующие обозначения:

RxD - последовательные данные, получаемые в выделителе данных 1 из принимаемого информационного сигнала;

CLK1 - тактовый сигнал последовательных данных RxD, получаемый в выделителе данных 1;

CLK2 - тактовая частота синхронизации обработки принимаемых символов данных пакета;

НП(n-1:0) - n - разрядный номер пакета;

НП(n-1) - старший бит номера пакета;

НК - m1 - разрядный номер канала;

ОД - признак ошибки при декодировании номера канала или пакета;

D - вход данных элемента;

C - вход синхронизации элемента;

W - вход разрешения записи элемента;

-1 - вход уменьшения значения счетчика на единицу;

+1 - вход увеличения значения счетчика на единицу;

R1, R2 - входы сброса счетчика символов данных пакета 24;

R - вход сброса триггера половины блока (ТПБ) 23;

S - вход установки триггера половины блока (ТПБ) 23;

Q - прямой выход состояния триггера;

СтрБНП - сигнал записи старшего бита номера пакета НП(n-1) (бита половины блока) в триггер бита половины блока 10;

СтрСЧПБ - сигнал, стробирующий изменение счетчиков 19, 20 половин блоков СЧПБ1 и СЧПБ2 схемы обнаружения половин блока 11;

+1СЧНП - сигнал, увеличивающий счетчик номеров пакетов СЧНП 9 на единицу;

Прием НП - сигнал, разрешающий запись номера принимаемого пакета в счетчик номеров пакетов СЧНП 9;

m - разрядность символов данных пакета;

m1 - разрядность номера канала;

n - разрядность номера пакета, счетчика номеров пакетов СЧНП 9 и адреса пакета в блоке данных;

n1 - разрядность адреса символа данных пакета в пакете и счетчика символов данных пакета СЧСДП 24;

n2 - разрядность адреса блока данных в буферной памяти блоков данных БПБД 28, счетчика номера блока СЧНБ 26 и сумматора SM 27;

N=n+n1+n2 - разрядность полного адреса буферной памяти блоков данных 28;

k - разрядность счетчиков 19, 20 половин блока СЧПБ1 и СЧПБ2, k=n-1;

+1СЧПБ1, +1СЧПБ2 - сигналы увеличения значений счетчиков 19, 20 половин блока СЧПБ1 и СЧПБ2 на единицу;

-1СЧПБ1, -1СЧПБ2 - сигналы уменьшения значений счетчиков 19, 20 половин блока СЧПБ1 и СЧПБ2 на единицу;

НГ - нижняя граница - это значение счетчиков 19, 20 половин блока СЧПБ1 и СЧПБ2, при котором блокируется их уменьшение;

ВГ - верхняя граница - это значение счетчиков 19, 20 половин блока СЧПБ1 и СЧПБ2, при котором блокируется их увеличение;

ПОР - порог - это значение счетчиков 19, 20 половин блока СЧПБ1 и СЧПБ2, при котором принимается решение о том, что достоверно обнаружена соответствующая половина блока данных и, следовательно, предыдущая половина блока данных полностью заполнена пакетами;

ПБ1 - признак перехода схемы обнаружения половин блока 11 в первое состояние, принимающий единичное значение, когда число принятых пакетов первой половины блока данных больше или равно значению ПОР;

ПБ2 -признак перехода схемы обнаружения половин блока 11 во второе состояние, принимающий единичное значение, когда число принятых пакетов второй половины блока данных больше или равно значению ПОР;

УПБ1 - сигнал установки признака ПБ1;

УПБ2 - сигнал установки признака ПБ2;

TS - символ тактовой синхронизации в пакете;

BS - символ байтовой синхронизации, код начала пакета;

Ci,j - символ при Xji - го кодового слова кода Рида-Соломона;

RS - код Рида-Соломона.

Устройство приема информации (фиг. 1) из канала содержит выделитель данных 1, селектор начала пакета 2, схему выделения символов данных 3, селектор номера канала 4, регистр сдвига 5, буферный регистр 6, схему коррекции номеров каналов и пакетов 7, схему управления записью 8, счетчик номеров пакетов (СЧНП) 9, триггер бита половины блока (ТБПБ) 10, схему обнаружения половин блока (СОПБ) 11 (11-23), счетчик символов данных пакета (СЧСДП) 24, первый элемент И 25, счетчик номера блока (СЧНБ) 26, сумматор (SM) 27, буферную память блоков данных (БПБД) 28, декодер помехоустойчивого кода (ДПК) 29, буферную память данных 30.

На вход выделителя данных 1 (фиг. 1) поступает принятый из канала связи информационный сигнал. Выделитель данных 1 выходом последовательных данных RxD соединен с входом последовательных данных D регистра сдвига 5, а выходом тактовой частоты данных CLK1 с входом синхронизации С регистра сдвига 5 и с первым входом схемы выделения символов данных 3. Выходы регистра сдвига 5 соединены m-разрядной шиной данных с входами данных D буферного регистра 6 и с первыми входами селектора начала пакетов 2. На вторые входы селектора начала пакетов 2 подается код начала пакета. Выход селектора начала пакетов 2 соединен с вторым входом схемы выделения символов данных 3. Выход схемы выделения символов данных 3 соединен с входом записи W буферного регистра 6 и с вторым входом схемы управления записью 8. Выходы буферного регистра 6 соединены m-разрядной шиной данных с входами схемы коррекции номеров каналов и пакетов 7 и с входами данных D буферной памяти блоков данных 28. Первые входы селектора номера канала 4 соединены m1 - разрядной шиной номера канала НК с четвертыми выходами схемы коррекции номеров каналов и пакетов 7. На вторые входы селектора номера канала 4 подается m1 - разрядный код номера канала. Выход селектора номера канала 4 соединен с третьим входом схемы управления записью 8, первый вход которой соединен с выходом признака ошибки декодирования ОД схемы коррекции номеров каналов и пакетов 7. На четвертый вход схемы управления записью 8 подается тактовая частота обработки символов данных пакета CLK2. Первые выходы схемы коррекции номеров каналов и пакетов 7 соединены n-разрядной шиной номера пакета НП(n-1:0) с входами данных D счетчика номеров пакетов 9, второй выход НП(n-1) схемы коррекции номеров каналов и пакетов 7 соединен с первым входом схемы обнаружения половин блоков 11 и c входом данных D триггера бита половины блока 10. Первый выход СтрБНП схемы управления записью 8 соединен c входом синхронизации С триггера бита половины блока 10, второй выход СтрСЧПБ схемы управления записью 8 соединен с вторым входом схемы обнаружения половин блоков 11, третий выход +1СЧНП схемы управления записью 8 соединен с входом +1 счетчика номеров пакетов 9 и с первым входом сброса R1 счетчика символов данных пакета 24, четвертый выход ПриемНП схемы управления записью 8 соединен с входом записи W счетчика номеров пакетов 9 и с вторым входом сброса R2 счетчика символов данных пакета 24, пятый выход +1СЧСДП схемы управления записью 8 соединен с входом +1 счетчика символов данных пакета 24. Инверсный выход триггера бита половины блока 10 соединен с первым входом первого элемента И 25, второй вход которого соединен с первым выходом ПБ2 схемы обнаружения половин блока 11, второй выход ПБ1 которой соединен с входом +1 счетчика номера блоков 26. Выход Р первого элемента И 25 соединен с входом переноса P сумматора 27. Входы данных D декодера 29 соединены шиной данных с выходами данных D буферной памяти блоков данных 28. Выходы данных D декодера 29 соединены шиной данных с входами данных D буферной памяти данных 30.

Полный адрес символа данных пакета в буферной памяти блоков данных 28 содержит N разрядов. Старшие n2 разряда полного адреса подаются на вторые входы адреса A2 буферной памяти блоков данных 28 из счетчика номера блока 26 через сумматор 27 и определяют адрес начала текущего блока данных в буферной памяти блоков данных 28. Начальный адрес блока данных может быть установлен в счетчике номера блока 26 по сигналу "Загрузка". Адрес пакета в текущем блоке данных задается n - разрядным номером пакета, следующим за старшими n2 разрядами номера блока, n - разрядный номер пакета подается на первые входы адреса A1 буферной памяти блоков данных 28 с выходов счетчика номеров пакетов 29. Младшие n1 разрядов полного адреса подаются на третьи входы адреса A3 буферной памяти блоков данных 28 из счетчика символов данных пакета 24 и определяют адрес символа данных в принимаемом пакете. Таким образом, полный адрес содержит N разрядов, причем N=n2+n+n1. На четвертые входы адреса A4 подается полный N - разрядный адрес от декодера помехоустойчивого кода 29.

Схема обнаружения половин блока 11 (фиг. 2) содержит инвертор 12, второй и третий элементы И 13, 14, первый, второй, третий и четвертый элементы И-НЕ 15, 16, 17, 18, счетчик первой половины блока (СЧПБ1) 19, счетчик второй половины блока (СЧПБ2) 20, первый и второй дешифраторы (DC) 21, 22 и триггер половины блока (ТПБ) 23.

Первый вход НП(n-1) схемы обнаружения половин блока 11 (фиг. 2) является входом инвертора 12 и первым входом третьего элемента И 14. Второй вход СтрСЧПБ схемы обнаружения половин блока 11 является вторым входом второго и третьего элементов И 13, 14. Выход инвертора 12 соединен с первым входом второго элемента И 13. Выход второго элемента И 13 соединен связью +1СЧПБ1 с первым входом второго элемента И-НЕ 16 и связью -1СЧПБ2 с вторым входом третьего элемента И-НЕ 17. Выход третьего элемента И 14 соединен связью -1СЧПБ1 с вторым входом первого элемента И-НЕ 15 и связью +1СЧПБ2 с первым входом четвертого элемента И-НЕ 18. Выход первого элемента И-НЕ 15 соединен с входом -1 счетчика первой половины блока 19, вход +1 которого соединен с выходом второго элемента И-НЕ 16. Выход третьего элемента И-НЕ 17 соединен с входом -1 счетчика второй половины блока 20, вход +1 которого соединен с выходом четвертого элемента И-НЕ 18. Выход счетчика первой половины блока 19 соединен k - разрядной шиной с входом первого дешифратора 21. Выход счетчика второй половины блока 20 соединен k - разрядной шиной с входом второго дешифратора 22. Первый инверсный выход НГ первого дешифратора 21 соединен с первым входом первого элемента И-НЕ 15, второй выход ПОР первого дешифратора 21 соединен связью УПБ1 с входом установки S триггера половины блока 23, третий инверсный выход ВГ первого дешифратора 21 соединен с вторым входом второго элемента И-НЕ 16. Первый инверсный выход НГ второго дешифратора 22 соединен с первым входом третьего элемента И-НЕ 17, второй выход ПОР второго дешифратора 22 соединен связью УПБ2 с входом сброса R триггера половины блока 23, третий инверсный выход ВГ второго дешифратора 22 соединен с вторым входом четвертого элемента И-НЕ 18. Инверсный выход триггера половины блока 23 является первым выходом ПБ2 схемы обнаружения половин блока 11, прямой выход триггера половины блока 23 является вторым выходом ПБ1 схемы обнаружения половин блока 11.

Устройство работает следующим образом.

Устройство приема информации из канала работает с блоками данных, имеющими формат, представленный на фиг. 4. Блок данных состоит из 31 пакета с номерами от 1 до 31. Каждый пакет содержит два байта тактовой синхронизации TS, символ байтовой синхронизации BS (код начала пакета); номер канала НК (3 бита); номер пакета НП, (5 бит); сорок символов данных пакета.

Номер канала и номер пакета защищены кодом Хемминга (8,4), исправляющего одну и обнаруживающего два ошибочных бита. Использование различных номеров каналов и BS различного вида предоставляет возможность организации нескольких виртуальных каналов в одном телевизионном канале. Формат передачи информации предусматривает использование для защиты от ошибок в канале помехоустойчивых кодов Рида-Соломона (RS-кодов), определенных над полем Галуа GF(256). Размер символа для этого поля равен байту. Блок данных содержит 40 кодовых слов, каждое из которых содержит 31 символ. На рисунке Cij - символ при Xj i-го кодового слова (при использовании многочленного представления последнего). Столбцы 6-45 содержат кодовые слова RS-кода. Глубокое перемежение символов кодовых слов в блоке данных позволяет эффективно исправлять как протяженные пакеты ошибок в телевизионной строке, так и пропадания целых пакетов данных, обусловленных искажениями заголовка пакета.

Высокая исправляющая способность кода Рида-Соломона может быть реализована при условии, что несмотря на наличие выпадений некоторых пакетов и приеме ложных пакетов, символы из пакетов с безошибочными заголовками будут собираться в кодовые слова без сдвигов, и границы между кодовыми словами будут правильно определены. Для этого необходимо реализовать помехоустойчивую сборку блоков данных из принимаемых пакетов.

Введение в устройство приема информации селектора номера канала 4 позволяет работать с мультиплексированными (виртуальными) каналами, которые различаются по номерам каналов. Дополнительные возможности мультиплексирования каналов предоставляет селектор начала пакета 2, в котором могут использоваться различные коды начала пакета. Мультиплексирование каналов предусматривает организацию нескольких виртуальных каналов в одном широковещательном канале. Временной интервал между передачей двух последовательных пакетов в одном виртуальном канале не определен - передача пакетов осуществляется асинхронно. В этом случае для обеспечения сборки блока данных невозможно использовать методы временной синхронизации (цикловой синхронизации). Естественным путем решения этой задачи является использование циклических номеров пакетов. Помехоустойчивость сборки блоков данных обеспечиваться в два этапа. На первом этапе исправляются ошибки в номерах каналов и пакетов. Исправление ошибок в устройстве приема информации из канала реализуется простой комбинационно - логической схемой коррекции номеров каналов и пакетов 7. На втором этапе используется схема обнаружения половин блока 11, триггер бита половины блока 10, первый элемент И 25, счетчик номера блока 26, сумматор 27, и счетчик номеров пакетов 9. Взаимодействие перечисленных блоков основывается на следующих принципах.

1) Каждый пакет блока данных относится к одной из двух половин блока данных. Пакет относится к первой половине блока данных, если старший бит номера принимаемого пакета НП(n-1) равен нулю. В противном случае пакет относится ко второй половине блока.

2) Принятый без ошибок номер пакета однозначно определяет адрес пакета для текущего блока данных в буферной памяти блоков данных 28. Необнаруженная ошибка в номере пакета в худшем случае приведет к искажению какого-то ранее принятого пакета в блоке данных. Все другие пакеты с неискаженными номерами будут правильно размещены в буферной памяти блоков данных 28 и их символы в кодовых словах RS-кода не будут смещены.

3) В случае обнаружения схемой коррекции номеров каналов и пакетов 7 неисправимых ошибок в номере пакета НП(n-1:0) предполагается, что принятый пакет имеет номер на единицу больше номера ранее принятого пакета.

4) На основании разделения пакетов по принадлежности к одной из двух половин блока данных для схемы обнаружения половин блока 11 определяются два состояния. В первое состояние схема обнаружения половин блока 11 переходит, когда устройство приема информации из канала приняло определенное число пакетов, принадлежащих первой половине блока данных. При этом принимается решение о том, что вторая половина предыдущего блока данных полностью заполнена пакетами. Во второе состояние схема обнаружения половин блока 11 переходит, когда устройство приема информации из канала приняло определенное число пакетов, принадлежащих второй половине блока данных. При этом принимается решение о том, что первая половина текущего блока данных полностью заполнена пакетами.

5) Если схема обнаружения половин блока 11 находится во втором состоянии, а на вход устройства приема информации из канала поступает пакет первой половины блока, предполагается, что это пакет из первой половины следующего блока данных. Если схема обнаружения половин блока 11 находится в первом состоянии, а на вход устройства приема информации из канала поступает пакет второй половины блока данных, то запись осуществляется в область текущего блока данных.

6) Адрес блока данных в буферной памяти блоков данных 28 увеличивается всякий раз при переходе схемы обнаружения половин блока 11 в первое состояние, которое означает, что предыдущий блок данных полностью заполнен пакетами.

Входной информационный сигнал, принятый из канала связи, поступает на вход выделителя данных 1 (фиг. 1), который производит выделение последовательных данных в виде сигнала RxD и тактовой частоты CLK1 этих данных. Последовательные выходные данные из выделителя данных 1 поступают на последовательный вход данных D регистра сдвига 5, в котором по фронту тактового импульса CLKI, поступающего от выделителя данных 1 на вход синхронизации С, осуществляется сдвиг последовательных данных. Таким образом, регистр сдвига 5 соответствующей разрядности выполняет последовательно-параллельное преобразование принимаемых данных. Параллельные m - разрядные данные с выходов регистра сдвига 5 поступают на входы данных D буферного регистра 6 и на первые входы селектора начала пакета 2. Селектор начала пакета 2 сравнивает данные на выходах регистра сдвига 6 с заданным кодом начала пакета. Равенство означает то, что устройство приема информации из канала обнаружило начало пакета, и символы данных этого пакета начинают поступать на вход устройства. Поэтому в случае равенства селектор начала пакета 2 вырабатывает сигнал, запускающий схему выделения символов данных 3.

Схема выделения символов данных 3 после запуска от селектора начала пакета 2 начинает подсчет количества принимаемых бит символов данных пакета, используя тактовую частоту CLK1 последовательных данных RxD с выхода выделителя данных 1. На основе этого подсчета осуществляется выделение всех m-разрядных символов данных пакета, т. е. управление последовательно-параллельным преобразованием, выполняемом на регистре сдвига 5. После приема в регистр сдвига 5 каждого m-разрядного символа данных пакета схема выделения символов данных 3 выдает строб записи на вход разрешения записи W буферного регистра 6, для сохранения в нем очередного символа данных пакета. Этот же сигнал при каждом выделении очередного символа данных пакета запускает схему управления записью 8.Символ данных пакета, сохраненный в буферном регистре 6, поступает на входы схемы коррекции номеров каналов и пакетов 7. После приема и записи в буферный регистр 6 символа данных пакета, соответствующего номеру канала, схема коррекции номеров каналов и пакетов 7 декодирует, выделяет и выдает m1 - разрядный номер канала НК и признак ошибки декодирования ОД, информирующий о наличии или отсутствии неисправимых ошибок в номере канала, действительные в течении приема бит следующего символа данных пакета до момента записи этого символа в буферный регистр 6. После приема и записи в буферный регистр 6 символа данных пакета, соответствующего номеру пакета, схема коррекции номеров каналов и пакетов 7 декодирует, выделяет и выдает n - разрядный номер пакета НП(n-1:0), старший разряд номера пакета НП(n-1) и признак ошибки декодирования ОД, информирующий о наличии или отсутствии неисправимых ошибок в номере пакета, действительные в течении приема бит следующего символа данных пакета до момента записи этого символа в буферный регистр 6. Номер канала НК с выходов схемы коррекции номеров каналов и пакетов 7 поступает на входы селектора номера канала 4. Селектор номера канала 4 сравнивает номер канала, к которому относится принимаемый пакет, с заданным кодом номера канала. В случае их совпадения селектор номера канала 4 формирует сигнал, который является признаком принадлежности принимаемого пакета к заданному в селекторе номера канала 4 каналу. Этот сигнал поступает на вход схемы управления записью 8.

Первый сигнал запуска от схемы выделения символов данных 3 активизирует управляющий автомат схемы управления записью 8. По каждому последующему сигналу запуска от схемы выделения символов данных 3 происходит переход этого автомата в определенное состояние. Каждое состояние этого автомата соответствует приему в буферный регистр 6 и обработке определенного символа данных пакета.

Первое состояние (состояние обработки номера канала) управляющего автомата схемы управления записью 8 после первого запуска от схемы выделения символов данных 3 соответствует приему в буферный регистр 6 и обработке символа данных пакета, содержащего номер канала. В этом состоянии схема управления записью 8 анализирует сигнал принадлежности принимаемого пакета к заданному каналу от селектора номера канала 4 и признак ошибки декодирования ОД, формируемый схемой коррекции номеров каналов и пакетов 7.

В результате анализа схема управления записью 8 формирует признак разрешения записи символов данных пакета в буферную память блоков данных 28. Признак формируется в слове состояния, которое находится в схеме управления записью 8.

Запись символов данных пакета, принимаемых устройством приема информации из канала, в буферную память блоков данных 28 осуществляется в двух случаях:

если принимаемый пакет принадлежит к заданному в селекторе номера канала 4 каналу и схема коррекции номеров каналов и пакетов 7 не обнаружила неисправимых ошибок в номере канала;

если схема коррекции номеров каналов и пакетов 7 обнаружила неисправимую ошибку в номере канала и сформировала сигнал ошибки декодирования ОД номера канала.

В случае запрещения записи символов данных принимаемого пакета схема управления записью 8 не формирует ни каких сигналов, управляющих адресацией и записью пакетов в буферную память блоков данных 28.

Следующее состояние управляющего автомата схемы управления записью 8 (состояние обработки номера пакета) после второго сигнала запуска от схемы выделения символов данных 3 соответствует приему в буферный регистр 6 и обработке символа данных пакета, содержащего номер принимаемого пакета. В этом состоянии схема управления записью 8 анализирует признак ошибки декодирования ОД схемы коррекции номеров каналов и пакетов 7, соответствующий наличию или отсутствию неисправимых ошибок в номере пакета. В случае разрешения записи символов данных принимаемого пакета на основе этого признака формируются сигналы, управляющие адресацией принимаемого пакета в буферной памяти блоков данных 28. К ним относятся: СтрБНП, СтрСЧПБ, +1СЧНП, ПриемНП.

После декодирования номера пакета НП(n-1:0) схемой коррекции номеров каналов и пакетов, старший бит номера принимаемого пакета НП(n-1) сохраняется в триггере бита половины блока (ТБПБ) 10. Запись осуществляется по сигналу СтрБНП, который формируется схемой управления записью 8.

При отсутствии неисправимых ошибок номер пакета НП(n-1:0) по сигналу ПриемНП записывается в счетчик номеров пакетов 9. Значение счетчика номеров пакетов 9 является относительным адресом принимаемого пакета в текущем блоке данных. Адрес начала текущего блока данных содержится в счетчике номера блока 26.

В случае обнаружения схемой коррекции номеров каналов и пакетов 7 неисправимых ошибок в номере пакета НП(n-1:0) предполагается, что принятый пакет имеет номер на единицу больше номера ранее принятого пакета. При этом схема управления записью 8 в состоянии обработки номера пакета на основе признака ошибки декодирования ОД формирует управляющий сигнал +1СЧНП, увеличивающий содержимое счетчика номеров пакетов 9 на единицу.

Когда схема управления записью находиться в состоянии обработки номера пакета, на основе состояния схемы обнаружения половин блока 11 и номера принимаемого пакета вычисляется его адрес в буферной памяти блоков данных 28.

В первом состоянии схемы обнаружения половин блока 11 триггер половины блока 23 установлен в единицу, признак ПБ1 на втором выходе схемы обнаружения половин блока 11 равен единице, а признак ПБ2 на первом выходе схемы обнаружения половин блока 11 равен нулю.

Во втором состоянии схемы обнаружения половин блока 11 триггер половины блока 23 сброшен, признак ПБ1 на втором выходе схемы обнаружения половин блока 11 равен нулю, а признак ПБ2 на первом выходе схемы обнаружения половин блока 11 равен единице.

Схема обнаружения половин блока 11 содержит два счетчика: счетчик первой половины блока 19 и счетчик второй половины блока 20. Эти счетчики подсчитывают число принятых пакетов каждой из половин принимаемого блока данных. Прием пакета, относящегося к одной половине блока данных, увеличивает на единицу значение счетчика соответствующей половины блока, содержащего число принятых пакетов этой половины блока данных, и уменьшает на единицу значение счетчика другой половины блока.

Управление счетчиками половин блоков 19, 20 осуществляется с помощью элемента НЕ 12 и второго и третьего элементов И 13, 14. Перечисленные элементы на основе значения старшего бита номера принимаемого пакета НП(n-1) по управляющему сигналу СтрСЧПБ формируют соответствующие управляющие воздействия -1СЧПБ1, +1СЧПБ1, -1СЧПБ2, +1СЧПБ2. Управляющий сигнал СтрСЧПБ формируется схемой управления записью 8 в состоянии обработки номера пакета в случае разрешения записи пакета в буферную память блоков данных 28.

Управляющие воздействия -1СЧПБ1, +1СЧПБ1, -1СЧПБ2, +1СЧПБ2 поступают на входы первого, второго, третьего и четвертого элементов И-HE 15, 16, 17 и 18. Данные элементы вместе с дешифраторами 21, 22 реализуют блокировку увеличения счетчиков половин блока 19, 20, при достижении ими значения ВГ и уменьшения - при достижении ими значения НГ. Значения ВГ и НГ задаются дешифраторами 21, 22. Значение ВГ выбирается в зависимости от числа пакетов в блоке данных, а НГ принимается равным нулю.

При достижении числа принятых пакетов, относящихся к первой половине блока данных, некоторого порогового значения ПОР, схема обнаружения половин блока 11 переходит в первое состояние. Переход в первое состояние означает, что во вторую половину предыдущего блока данных приняты все принадлежащие ей пакеты, с учетом возможных вставок и выпадений пакетов.

При достижении числа принятых пакетов, относящихся ко второй половине блока данных, некоторого порогового значения ПОР, схема обнаружения половин блока 11 переходит во второе состояние. Переход во второе состояние означает, что в первую половину текущего блока данных приняты все принадлежащие ей пакеты, с учетом возможных вставок и выпадений пакетов.

Пороговое значение ПОР числа принятых пакетов первой половины блока данных для счетчика первой половины блока 19 задает дешифратор 21. При достижении числа принятых пакетов первой половины блока данных на выходе счетчика первой половины блока 19 значения ПОР дешифратор 21 формирует сигнал УПБ1. Данный сигнал устанавливает триггер половины блока 23 в единицу. При этом схема обнаружения половин блока 11 переходит в первое состояние.

Пороговое значение ПОР числа принятых пакетов второй половины блока данных для счетчика второй половины блока 20 задает дешифратор 22. При достижении числа принятых пакетов второй половины блока данных на выходе счетчика первой половины блока 20 значения ПОР дешифратор 22 формирует сигнал УПБ2. Данный сигнал сбрасывает триггер половины блока 23 в ноль. При этом схема обнаружения половин блока 11 переходит во второе состояние.

Если схема обнаружения половин блока 11 находится во втором состоянии (ПБ1= 0, ПБ2=1), а на вход устройства приема информации из канала поступает пакет первой половины блока, предполагается, что это пакет из первой половины следующего блока данных. С помощью сумматора 27 вычисляется его адрес в буферной памяти блоков данных 28 и осуществляется запись данных пакета в соответствии с вычисленным адресом. Адрес вычисляется на основе значения счетчика номера блока 26, которое является базовой частью полного адреса для буферной памяти блоков данных 28 и адресует начала блоков данных в этой памяти. С помощью сумматора 27 к значению счетчика номера блока 26, которое подается на входы A первого слагаемого сумматора 27, временно прибавляется единица, подаваемая на вход P переноса сумматора 27. Единица на входе P переноса сумматора 27 временно формируется первым элементом И 25, когда признак ПБ2 на выходе схемы обнаружения половин блоков 11 и значение инверсного выхода триггера бита половины блока равны единице, что соответствует состоянию приема пакета, относящегося к первой половине следующего блока данных. Если схема обнаружения половин блока 11 находится в первом состоянии (ПБ1=1, ПБ2= 0), а на вход устройства приема информации из канала поступает пакет второй половины блока данных, то запись осуществляется в область текущего блока данных. При этом единица на входе переноса P сумматора 27 первым элементом И 25 не формируется, и временного увеличения адреса блока данных с помощью сумматора 27 не происходит.

Адрес блока данных в буферной памяти блоков данных 28 увеличивается всякий раз при переходе схемы обнаружения половин блока 11 в первое состояние, которое означает, что предыдущий блок данных полностью заполнен пакетами, за счет увеличения значения счетчика номера блока 26 на единицу по сигналу ПБ1 от схемы обнаружения половин блока 11. Сигнал ПБ1 формируется в момент перехода схемы обнаружения половин блока 11 в первое состояние.

Из состояния обработки номера пакета управляющий автомат схемы управления записью 8 по следующему сигналу запуска от схемы выделения символов данных 3 переходит в состояние записи принимаемых символов данных пакета в буферную память блоков данных 28. В этом состоянии схема управления записью 8 остается до завершения обработки последнего символа данных принимаемого пакета. Находясь в состоянии записи символов данных пакета схема управления записью 8 в случае разрешения записи формирует для каждого принятого символа данных пакета сигналы управления адресацией и сигналы записи. Сигналом управления адресацией символа данных пакета является сигнал +1СЧСДП, увеличивающий адрес символа данных в принимаемом пакете на единицу. Сигналы записи символа данных пакета в память зависят от выбора буферной памяти блоков данных 28 и на фиг. 1 не показаны. Для формирования всех управляющих сигналов схема управления записью 8 использует тактовую частоту CLK2, поступающую на ее вход. Таким образом, обработка и запись символов данных пакета в буферную память блоков данных 28 привязана к тактовой частоте CLK2, которая выбирается в зависимости от частоты CLKI, времени записи и организации режимов доступа к буферной памяти блоков данных 28.После приема последнего символа данных пакета схема управления записью 8 переходит в состояние ожидания первого сигнала запуска от схемы выделения символов данных 3, который соответствует выделению символа данных с номером канала следующего пакета.

После приема всех символов данных пакета схема выделения символов данных 3 возвращается в исходное состояние ожидания запуска от селектора начала пакета. При этом сбрасываются ее внутренние счетчики, подсчитывающие число принятых бит символов данных пакета. После окончания пакета устройство приема информации из канала переходит в исходное состояние ожидания начала следующего пакета.

Исправление ошибок в блоках данных с использованием RS-кодов выполняется после полного приема и записи блока данных в буферную память блоков данных 28 декодером помехоустойчивого кода 29. Декодер помехоустойчивого кода 29, считывает блок данных из буферной памяти блоков данных 28 и после исправления в нем ошибок записывает блок данных в буферную память данных 30.

На фиг. 3 приведены временные диаграммы работы схемы обнаружения половин блоков 11. В качестве единицы времени на временных диаграммах выбрано время приема одного пакета. На временных диаграммах НП соответствует номеру принимаемого пакета, СЧПБ1 - значению счетчика первой половины блока, СЧПБ2 - значению счетчика второй половины блока, УПБ1 - это сигнал установки первого состояния, т. е. сигнал установки триггера половины блока 23, УПБ2 - это сигнал установки второго состояния, т. е. сигнал сброса триггера половины блока 23. В качестве порогового ПОР числа пакетов выбрано значение 8, в качестве верхней границы - 12.

Верхняя диаграмма демонстрирует работу схемы обнаружения половин блоков 11 при отсутствии вставок и выпадений пакетов. В этом случае переход в первое состояние, при котором предыдущий блок данных считается полностью заполненным, происходит при приеме пакета с номером 7 (восьмого по счету, относящегося к первой половине блока данных, когда значение на выходе счетчика первой половины блока 19 СЧПБ1 равно 8) по переднему фронту сигнала УПБ1. При поступлении пакетов первой половины блока данных значение счетчика первой половины блока 19 СЧПБ1 инкрементируется до заданной верхней границы ВГ, равной 12, и фиксируется до прихода первого пакета, принадлежащего второй половине блока данных. С приходом каждого пакета второй половины блока данных происходит декремент счетчика первой половины блока данных 19 до нулевого значения. При достижении в процессе уменьшении значения счетчика первой половины блока данных 19 значения 7 снимается управляющий сигнал УПБ1, удерживающий схему обнаружения половин блоков 11 в первом состоянии.

Переход во второе состояние, при котором первая половина текущего блока данных считается полностью заполненной, происходит при приеме пакета с номером 23 (восьмого по счету, относящегося ко второй половине блока данных, когда значение на выходе счетчика второй половины блока 20 СЧПБ2 равно 8) по переднему фронту сигнала УПБ2.

При поступлении пакетов второй половины блока данных значение счетчика второй половины блока 20 СЧПБ2 инкрементируется до заданной верхней границы ВГ, равной 12, и фиксируется до прихода первого пакета, принадлежащего первой половине блока данных. С приходом каждого пакета первой половины блока данных происходит декремент счетчика второй половины блока данных 20 до нулевого значения. При достижении в процессе уменьшения значения счетчика второй половины блока данных 20 значения 7 снимается управляющий сигнал УПБ2, удерживающий схему обнаружения половин блоков 11 во втором состоянии.

Нижняя диаграмма демонстрирует работу схемы обнаружения половин блоков 11 при наличии выпадений пакетов. В этом случае переходы между состояниями происходят с некоторой задержкой из-за выпадения пакетов с номерами 1, 3, 5, 9, 11, 15, 17, 21, 23, 25, 27, 29. Переход в первое состояние, при котором предыдущий блок данных считается полностью заполненным, происходит при приеме пакета с номером 12. Переход во второе состояние происходит при приеме пакета с номером 22.

Таким образом, несмотря на выпадение пакетов, схема обнаружения половин блока 11 с высокой надежностью определяет момент полного заполнения пакетами предыдущего блока данных. Задержка определения не превышает времени передачи одной половины блока данных. Схема обнаружения половин блока 11 проста в реализации и позволяет с высокой надежностью осуществлять сборку блоков данных в устройстве приема информации из канала.

Предложенное устройство легко реализуется на серийно выпускаемых радиоэлементах. Рассмотрим пример реализации устройства приема информации из канала, работающего с представленным на фиг. 4 форматом блока данных. Выделитель данных 1 реализуется на микросхеме SAA5231 или ее отечественном аналоге КР1021ХА6 со схемами управления. Селектор начала пакета 2 реализуется на двух микросхемах К555СП1 и микросхеме К555ЛИ1, селектор номера канала 4 - на микросхеме К555СП1, регистр сдвига 5 - на микросхеме КМ555ИР8, буферный регистр 6 - на микросхеме К555ИР22, схема коррекции номеров каналов и пакетов 7 - на микросхеме КР556РТ5, счетчик номеров пакетов 9 - на микросхемах К555ИЕ10, К555ТМ2 и К555ЛП5, триггер бита половины блока - на микросхеме К555ТМ2, счетчик символов данных пакета 24 - на двух микросхемах К555ИЕ10, первый элемент И 25 - на микросхеме К555ЛИ1, счетчик номера блока 26 - на микросхеме К555ИЕ7, сумматор 27 - на микросхемах К555ИМ6 и К555ЛП5. Схема выделения символов данных реализуется на двух микросхемах К555ИЕ10, двух микросхемах К555СП1, микросхеме К555ТМ2, К555ТВ6, К555ИР22, К555ЛП5, К555ЛА2, К555ЛА3 и К555ЛН1. Схема управления записью реализуется на двух микросхемах К555ТМ2, микросхеме К555ИЕ10, К555ИД7, К555ТМ8, К555ЛА3, К555ЛН1, К555ЛЛ1.

Схема обнаружения половин блока 11 реализуется на следующих элементах. Счетчики половин блоков 19, 20 - на микросхемах К555ИЕ7, дешифраторы 21, 22 - на микросхемах К531ЛЕ7П, К555ЛН1, К555ЛА3 и К555ИД3, триггер половины блока 23 - на микросхеме К555ТМ2, элементы И-НЕ - на микросхеме К555ЛА3, элементы И 13 и 14 - на микросхеме К555ЛИ1, элемент НЕ 12 - на микросхеме К555ЛН1.

Декодер помехоустойчивого кода 29 может быть как аппаратным, так и программным, например если устройство приема информации из канала используется в составе ПЭВМ. В последнем случае буферная память блоков данных 28 и буферная память данных 30 могут представлять собой различные области системной памяти ПЭВМ, доступ к которым как со стороны устройства приема информации так и со стороны декодера помехоустойчивого кода 29 осуществляется по системной шине ПЭВМ в соответствии с протоколами обмена этой системной шины.

Альтернативой программной реализации декодера является его реализация в виде микропроцессорной системы [6] с аппаратным ускорителем [7]. При этом в качестве памяти возможно использование микросхем КР537РУ14.

Изобретение по сравнению с прототипом обладает тем преимуществом, что оно может работать с мультиплексированными каналами с асинхронной передачей пакетов информации. При приеме информации осуществляется помехоустойчивая сборка блоков данных из принимаемых пакетов. Устройство приема информации из канала позволяет обрабатывать вставки и выпадения асинхронно передаваемых пакетов. Это позволяет предотвратить распространение ошибок в блоке данных.

Источники информации:

1. Патент EP 0162612 A2 (EUROPEAN PATENT APPLICATION). МКИ4 H 04 N 7/087. Receiver for a character broadcasting system. / Shibasaki Takeshi (JP) - заявлено 26.04.85; приоритет 86826/84 JP от 27.04.84; опубл. 27.11.85, бюл. 85/48.

2. Патент 5185740 США. МКИ5 H 04 J 3/06, НКИ 370-106. Information transmitting device. / Yoshikazu Kurose, Shinji Aoki, Hideto Suzuki (JP) - заявлено 23.07.90, N 555769; приоритет 1-194769 от 26.07.89; опубл. 9.02.93.

3. Патент WO 84/03987 (PCT). МКИ3 G 11 В 7/00, G 11 В 5/09. Apparatus for recording and reprodusing optical data. / Заявлено 30.03.84, PCT /JP84/ 00156; опубл. 11.10.84.

4. Петров В. В., Додонов А.Г. Система распространения компьютерной информации "ВСЕ-ВСЕМ" // Электронное моделирование. - 1991, N 1.- с. 14-17. -рус.

5. VBI: Передача данных по каналам телевизионного вещания / Петрищевский С. // Компьютер пресс. - 1998 - N 3, с. 98-100.- рус.

6. Егоров С.И. О программно - аппаратной реализации декодеров кода Рида- Соломона для защиты от ошибок малогабаритных оптических на копителей / Курск. политехн. ин-т. - Курск, 1990. 39 с.: ил., табл. Библиогр. 26 назв. - Деп. в ИНФОРМПРИБОР N 4898 - пр 90.

7 . с. 1656689 СССР, МКИ4 Н 03 М 13/00, 13/02. Устройство кодирования и вычисления синдромов помехоустойчивых кодов для коррекции ошибок во внешней памяти ЭВМ / С. И. Егоров, А.П.Типикин, В.В.Петров, А.В.Гостев (СССР). N 4722202/24-24; Заявл. 26.06.89; Опубл. 15.06.91, Бюл. N 22, -7 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ОШИБОК В КАНАЛЕ | 2001 |

|

RU2192038C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2006 |

|

RU2314639C1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство межмашинной связи | 1987 |

|

SU1474666A1 |

| Адаптивное устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1532938A1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

Изобретение относится к системам телекоммуникаций и может быть использовано в системах для приема данных цифровых вещательных систем. Техническим результатом изобретения является повышение помехоустойчивости и расширение функциональных возможностей устройства за счет возможности совместного функционирования мультиплексированных каналов с асинхронно принимаемыми пакетами. Для этого устройство содержит выделитель данных, селектор начала пакета, схему выделения символов данных, селектор номера канала, регистр сдвига, буферный регистр, схему коррекции номеров каналов и пакетов, схему управления записью, счетчик номеров пакетов, триггер бита половины блока, схему обнаружения половин блока, счетчик символов данных пакета, элементы И, счетчик номера блока, сумматор, буферную память блоков данных, декодер помехоустойчивого кода, буферную память данных. 4 ил.

Устройство приема информации из канала, содержащее выделитель данных, селектор начала пакета, схему выделения символов данных, регистр сдвига, буферный регистр, схему коррекции номеров каналов и пакетов, схему управления записью, счетчик номеров пакетов, счетчик символов данных пакета, буферную память блоков данных, декодер помехоустойчивого хода, буферную память данных, причем вход выделителя данных подключен к шине информационного сигнала, выход последовательных данных выделителя данных соединен с входом последовательных данных регистра сдвига, выход тактовой частоты данных выделителя данных соединен с входом синхронизации регистра сдвига и с первым входом схемы выделения символов данных, выходы регистра сдвига соединены m - разрядной шиной данных с входами данных буферного регистра и с первыми входами селектора начала пакета, вторые входы селектора начала пакета подключены к шине кода начала пакета, выход селектора начала пакета соединен с вторым входом схемы выделения символов данных, выход схемы выделения символов данных соединен с входом записи буферного регистра и с вторым входом схемы управления записью, четвертый вход которой подключен к шине тактовой частоты обработки символов данных пакета, выходы буферного регистра соединены m - разрядной шиной данных с входами схемы коррекции номеров каналов и пакетов и с входами данных буферной памяти блоков данных, первый вход схемы управления записью соединен с выходом признака ошибки декодирования схемы коррекции номеров каналов и пакетов, первые выходы схемы коррекции номеров каналов и пакетов соединены n - разрядной шинoй номера пакета с входами данных счетчика номеров пакетов, третий выход схемы управления записью соединен со счетным входом счетчика номеров пакетов и с первым входом сброса счетчика символов данных пакета, четвертый выход схемы управления записью соединен с входом записи счетчика номеров пакетов и вторым входом сброса счетчика символов данных пакета, пятый выход схемы управления записью соединен со счетным входом счетчика символов данных пакета, выходы счетчика номеров пакетов n - разрядной шиной адреса пакета соединены с первыми входами адреса буферной памяти блоков данных, выходы счетчика символов данных пакета соединены n1 - разрядной шиной адреса символа данных пакета с третьими входами адреса буферной памяти блоков данных, четвертые входы адреса буферной памяти блоков данных соединены N - разрядной шиной адреса с первыми выходами адреса декодера помехоустойчивого кода, входы данных которого соединены шиной данных с выходами данных буферной памяти блоков данных, выходы данных декодера помехоустойчивого кода соединены шиной данных с входами данных буферной памяти данных, входы адреса которой соединены шиной адреса с вторыми выходами адреса декодера помехоустойчивого кода, отличающееся тем, что в устройство введены селектор номера канала, триггер бита половины блока данных, схема обнаружения половин блока данных, первый элемент И, счетчик номера блока данных и сумматор, первые входы селектора номера канала соединены m1 - разрядной шиной номера канала с четвертыми выходами схемы коррекции номеров каналов и пакетов, вторые входы селектора номера канала подключены к m1 - разрядной шине кода номера канала, выход селектора номера канала соединен с третьим входом схемы управления записью, второй выход схемы коррекции номеров каналов и пакетов соединен с первым входом схемы обнаружения половин блока данных и с входом данных триггера бита половины блока данных, первый выход схемы управления записью соединен с входом синхронизации триггера бита половины блока данных, второй выход схемы управления записью соединен с вторым входом схемы обнаружения половин блока данных, инверсный выход триггера бита половины блока данных соединен с первым входом первого элемента И, второй вход которого соединен с первым выходом схемы обнаружения половин блока данных, второй выход которой соединен со счетным входом счетчика номера блока данных, выход первого элемента И соединен с входом переноса сумматора, входы данных счетчика номера блока данных подключены к n2 -разрядной шине начального адреса блоков данных в буферной памяти блоков данных, вход записи счетчика номера блока данных подключен к шине "Загрузка", выходы счетчика номера блока данных соединены n2 - разрядной шиной с первыми входами данных сумматора, вторые входы данных которого подключены к n2 - разрядной шине логического нуля, выходы сумматора соединены n2 - разрядной шиной адреса блока данных с вторыми входами адреса буферной памяти блоков данных, причем схема обнаружения половин блока данных содержит инвертор, второй и третий элементы И, первый, второй, третий и четвертый элементы И-НЕ, счетчик первой половины блока данных, счетчик второй половины блока данных, первый и второй дешифраторы и триггер половины блока данных, первый вход схемы обнаружения половин блока данных является входом инвертора и первым входом третьего элемента И, второй вход схемы обнаружения половин блока данных является вторым входом второго и третьего элементов И, выход инвертора соединен с первым входом второго элемента И, выход второго элемента И соединен с первым входом второго элемента И-НЕ и с вторым входом третьего элемента И-НЕ, выход третьего элемента И соединен с вторым входом первого элемента И-НЕ и с первым входом четвертого элемента И-НЕ, выход первого элемента И-НЕ соединен с входом декремента счетчика первой половины блока данных, вход инкремента которого соединен с выходом второго элемента И-НЕ, выход третьего элемента И-НЕ соединен с входом декремента счетчика второй половины блока данных, вход инкремента которого соединен с выходом четвертого элемента И-НЕ, выходы счетчика первой половины блока данных соединены k - разрядной шиной с входами первого дешифратора, выходы счетчика второй половины блока данных соединены k - разрядной шиной с входами второго дешифратора, первый инверсный выход первого дешифратора соединен с первым входом первого элемента И-НЕ, второй выход первого дешифратора соединен с входом установки S триггера половины блока данных, третий инверсный выход первого дешифратора соединен с вторым входом второго элемента И-НЕ, первый инверсный выход второго дешифратора соединен с первым входом третьего элемента И-НЕ, второй выход второго дешифратора соединен с входом сброса R триггера половины блока данных, третий инверсный выход второго дешифратора соединен с вторым входом четвертого элемента И-НЕ, инверсный выход триггера половины блока данных является первым выходом схемы обнаружения половин блока данных, прямой выход триггера половины блока данных является вторым выходом схемы обнаружения половин блока данных.

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| US 5185740 A, 09.02.93, EP 0162612 A2, 27.11.85 | |||

| Устройство кодирования и вычисления синдромов помехоустойчивых кодов для коррекции ошибок во внешней памяти ЭВМ | 1989 |

|

SU1656689A1 |

| Петров В.В и др | |||

| Система распознавания компьютерной информации "ВСЕ-ВСЕМ" | |||

| - Электронное модeлиpовaние, 1991, N1, с | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Петрищевский С | |||

| Передача данных по каналам телевизионного вещания., - Компьютер пресс, 1998, N3, с | |||

| Дорожная спиртовая кухня | 1918 |

|

SU98A1 |

| ПРИБОР ДЛЯ СОЖИГАНИЯ НЕФТИ В ПЕЧНЫХ ТОПКАХ | 1923 |

|

SU1021A1 |

| Видеопроцессор телетекста | |||

| - Электронная промышленность, 1990, N9, с | |||

| Автоматический огнетушитель | 0 |

|

SU92A1 |

| Егоров С.И | |||

| О программно-аппаратной реализации декодеров кода Рида-Соломона для защиты от ошибок малогабаритных оптических накопителей | |||

| - Курск, Курский политехнический институт, 1990, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

Авторы

Даты

1999-09-10—Публикация

1998-06-11—Подача