входы, вырабатьшают импульсы, синхро- равления

iU Vf-,.-, ,.

25

30

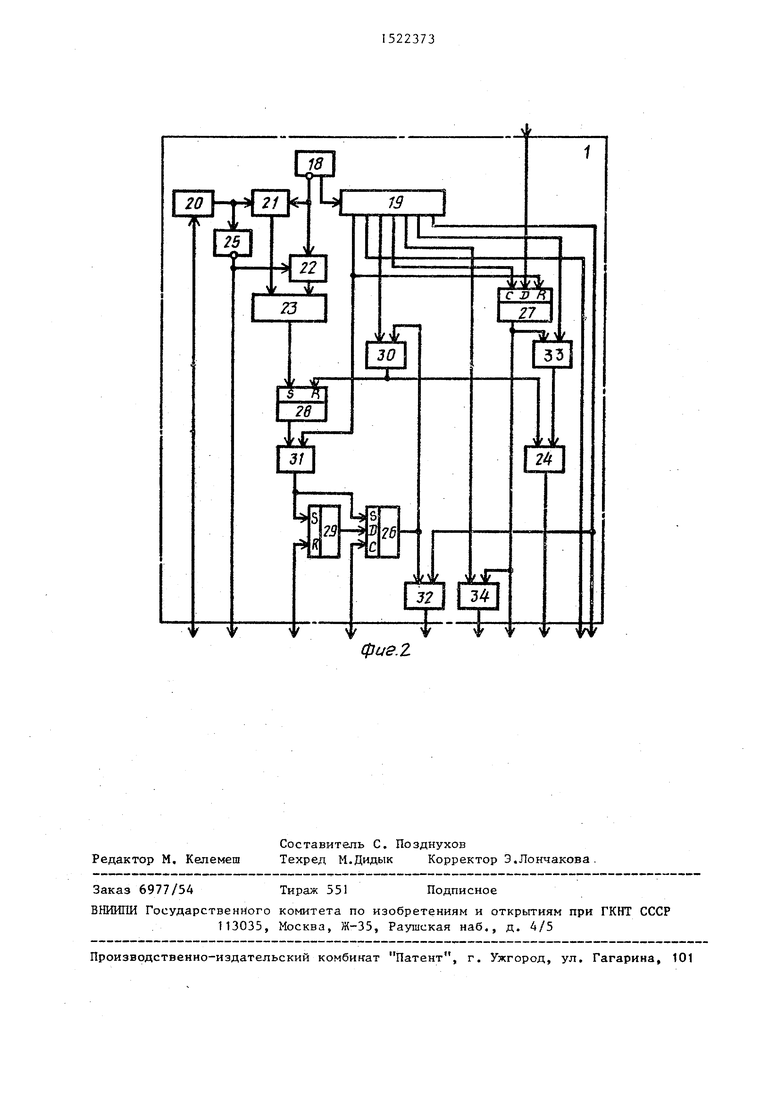

низироватше с последоват&льностью импульсов высокой частоты и поступающие па входы первого логического элемента 2tfflH 23, в момент перехода опорного на1тря7ке1шя V (t) через нуль проходят импульсы с частотой 2 fon на первьй вход (вход установки в 1) второго RS-триггера 28. По каждому из зтих импульсов второй КЗ- триггер 28 устанавливается в состояние 1, сигнал с выхода второго RS- триггёра 28 поступает на первый вход третьего логического элемента 2И 31, разрешая прохождение через этот элемент импульсов последовательности Тй1 с выхода распределителя 19 импуопьсов.

Импульсы с выхода третьего логического элемента 2И 31 устанавливают в состояние логической 1 третий RS-триггер 29 и первый D-триггер 26, следовательно, открываются второй и четвертьй логические элементы 2й 30 и 32. Импульс последовательности ТИ 3 проходит через второй логический элемент 2И 30 и устанавливает второй RS- триггер 28 ц О, при этом закрывается третий логический элемент 2И 31 и запрещается прохождение импульсов на входы установки в 1 третьего RS- триггера 29 и первого D-триггера 26.

Иг-шульсы последовательности ТИ 7 проходят через четвертьй логический элемент 2И 32 и поступают на счетный первьй вход второго двоичного Q-разрядного счетчика 3. Исходное состояние

40

45

50

Код номера управляемого электродвигателя с выхода второго коммутатора 9 поступает на Q первых входов четвертого дешифратора 7 и Q входов третьего дешифратора 6, с выхода которого 2 -разрядньй позиционньй код номера электродвигателя подается на первь1е входь второго накопителя 11.

Второй накопитель 1I работает в одном из двух режимов: запись информации со второго, третьего и четвертого входов и считывание информации. Выбор режима зависит, от состояния пятого входа второго накопителя 1i, подклю- че1Шого к четвертому вькоду блока управления,

Сигнал записи информации во второй накопитель И поступает с четвертого входа блока I управления на второй (информационньй) вход второго D-триггера 27. Импульсом последовательности та 4 с четвертого выхода распределителя 19 импульсов этот.си.гнал записывается во второй D-триггер 27 (сброс D-триггера 27 осуществл.яется импульсом последовательности ТИ I, поступающи - на его первьй вход). Сигнал с выхода

второго D-триггера 27 поступает на третий вход второго ком гутатора 9, обеспечивая выборку кода номера управляемого электродвигателя с второго входа второго коммутатора 9 при записи информации во второй накопитель 11. Запись во второй накопитель 11 осуществляется по имаульсу с выхов торого двоичного Q-разрядного счетчи - да шестого логического элемента 2И

ка 3 нулевое. Приведение в исходное34, которьй формируется на основе

состояние осуществляется с помощьюинформации с выхода второго D-триггесигнапа установки в исходное состоя-ра 27 и импульса последовательности

U Vf-,.-, ,.

5

0

0

45

50

Код номера управляемого электродвигателя с выхода второго коммутатора 9 поступает на Q первых входов четвертого дешифратора 7 и Q входов третьего дешифратора 6, с выхода которого 2 -разрядньй позиционньй код номера электродвигателя подается на первь1е входь второго накопителя 11.

Второй накопитель 1I работает в одном из двух режимов: запись информации со второго, третьего и четвертого входов и считывание информации. Выбор режима зависит, от состояния пятого входа второго накопителя 1i, подклю- че1Шого к четвертому вькоду блока управления,

Сигнал записи информации во второй накопитель И поступает с четвертого входа блока I управления на второй (информационньй) вход второго D-триггера 27. Импульсом последовательности та 4 с четвертого выхода распределителя 19 импульсов этот.си.гнал записывается во второй D-триггер 27 (сброс D-триггера 27 осуществл.яется импульсом последовательности ТИ I, поступающи - на его первьй вход). Сигнал с выхода

второго D-триггера 27 поступает на третий вход второго ком гутатора 9, обеспечивая выборку кода номера управляемого электродвигателя с второго входа второго коммутатора 9 при записи информации во второй накопитель 11. Запись во второй накопитель 11 осуществляется по имаульсу с выхо - да шестого логического элемента 2И

ТН 5, поступающего на второй вход ше- стого логического элемента 2И 34.

При считьшанин информации из второго накопителя 1I по коду адреса на его первых входах происходит выборка М-разрядного кода управления, К-раз- рядного кода признака регулировочной характеристики и знака сигнала управления, которые передаются соответственно на первые и вторые входы второго дешифратора 5 и третий вход первого коммутатора 8.

По мере поступления импульсов на первьй (счетньй) вход второго двоичного Q-разрядного счётчика 3 на его выходе последовательно формируется значения кода номера электродвигателя от О до 2 - 1,2 -и импульс возвращает счетчик 3 в нулевое состояние при этом также формируется сигнал переполнения, поступающий с (Q+l)-ro выхода второго двоичного Q-разрядного счетчика 3 на третий (счетный) вход первого двоичного N-разрядного счетчика 2.

На выходе первого двоичного N-разрядного счетчика 2 устанавливается новое значение кода номера подключения. Начальное значение кода на выходе первого счетчика 2-0...01. Запись исходного кода с второго входа счетчика 2 осуществляется по сигналу установки в исходное состояние, поступа ющему на первьй вход первого счетчика 2.

С выхода первого двоичного счетчика 2Ы разрядньй код номера подключения поступает на N входов первого дешифратора 4, на выходе которого .формируется 2 -разрядньй позиционный код номера подключения, поступающий на первые входы первого накопителя 10. На вторые входы первого накопителя 10 поступает 2 -разрядньй пози- ционньй код с выхода второго дешифратора 5, сформированньй на основе М- разрядного кода управления и К-разряд ного кода признака регулировочной характеристики.

Информация с выхода первого накопителя 10 поступает на второй вход первого коммутатора 8. Первьй коммутатор 8 формирует реверс электродвигателя на двух своих выходах на основе следующей информации на своих входах: второй вход - сигнал Z с выхода первого накопителя 10, первьй вход - сигнал фазы опорного напряжения ( с первого выхода блока I управления, третий вход - сигнал знака кода управления sign А с третьего выхода второго накопителя I.

Сигналы ОС, и t/ij. на первом и втором выходах первого коммутатора 8 связаны с сигналами на входах логическими зависимостями вида:

0

5

0

5

0

5

0

5

0

5

Ы, Z (( sign AV sign А);

г Z (Opon-sig А ,- sign А).

Информация с первого и второго выходов первого коммутатора 8 записьгоа- ется в один из двух первых регистров 15. Выбор первого регистра 15 осуществляется с помощью сигналов с выходов четвертого дешифратора 7, формирующего позиционньй код номера электродвигателя, обслуживаемого в текущий момент времени. Сигналы на выходе четвертого дешифратора 7 простробиро- ваны импульсами, поступаюш;ими на второй вход четвертого дешифратора 7 с пятого выхода блока 1 управления.

Стробирующие импульсы формируются на выходе второго логического элемента 21ШИ 24 и представляют собой сумму импульсов последовательности ТИ 3 (с выхода второго логического элемента 2 И 30) и импульсов последовательности ТИ 6, которые проходят с выхода пятого логического элемента 2И 33 только при наличии 1 на выходе второго D-триггера 27, т.е. в режиме записи информации во второй накопитель 1 }.

Появление импульса на 2-м выходе четвертого дешифратора 7 является. признаком наступления одного из двух событий: или произведена запись информации (кода управления, кода признака регулировочной характеристики, знака кода управления) во второй накопитель 11 для электродвигателя с номером 2 или закончено формирование сигналов управления для всех 2 двухфазных асинхронных электродвигателей,

В первом случае, сигнал на первом входе логического элемента НЕ-2И 12 запретит прохождение 2®-го импульса, синхронизированного импульсами последовательности ТИ 6 с выхода четвертого дешифратора 7 через логический элемент НЕ-2И 12 на вход установки в . 1 первого RS-триггера 13. При этом на выходе первого RS-триггера 13 ,

хранится состояние

установленное

и

импульсом последовательности ТИ 2, поступившим с шестого выхода блока управления на второй вход первого lRS-триггера 13. В этом случае по ;импульсу с 2 -ГО выхода четвертого. дешифратора 7 произойдет запись в первьй регистр 15 информации с |выхода первого коммутатора 8, пред1522373.12

писи о с выхода третьего RS-тригге- 1ра 29 в первый D-триггера 26. Четвертый логический элемент 2И 32 закроется, запрещая прохождение счетных им- пульсов на вход второго двоичного Q-разрядного счетчика 3.

Таким образом, в течение половины периода напряжения питания Uort(t)

|ставляющей собой сигнал управления, 1сформированньй дпя 2-го двухфазного асинхронного электродвигателя на основе кода и знака кода управления и признака регул1фовочной характеристики, записанных в.о второй накопитель 11 по предьщущему импульсу последовательности T1I 5. ...

Во втором случае, 2 -и импульс с выхода четвертого дешифратора 7,- син- хронизированньй импульсом последовательности ТИ 3, через логический элемент НЕ-2И 12 поступит на первьй вход I первого RS-триггера 13 и установит I его в состояние 1, откроется пер- 1 вьй логический элемент 2И 14, на вы- |ход которого пройдет-импупьс последо- 1вательности ТИ 7 с седьмого выхода I блока 1 управления. Этот инпзлпьс по- ступит на третьи входы всех вторых :регистров 16, обеспечив перепись ин- ;формации из всех 2 первых регистров ;15 в 2 вторых регистров 16. I .Сигналы управления с первого и вто- рого выходов каждого из вторых регистров 16 усиливаются с помощью соответствующего усилителя 17 мощности по току и .напряжению до величины, необходимой по условиям работы электродвигателей, и поступают на их обмотки управления.

2-й импульс переполнения с (Q+)- го выхода второго двошшого Q-разрядного счетчика 3 установит на выходе первого двоичного N-разрядного счетчика 2 нулевой код подключения, при этом будет сформирован сигнал переполнения первого, двоичного N-разрядного счетчика 2,.поступающий на третий вход блока Г управле1шя и устанавливающий в О третий RS-триггер 29.. После завершения вычисления сигнала управления для всех 2 электродвигателей при Нулевом коде подключения по импульсу переполнения второго двоичного Q-разрядного счетчика 3 код на вьзсоде первого двоичного 13-разрядного счетчика 2 примет значение 0...01, .Изменение информации в младшем разря- .де первого счетчика 2 приведет к за

0

5

0

5

30

55

35

45

50

формируются сигналы управления для каждого из 2 двухфазных асинхронных электродвигателей при всех значениях кодов номеров подключений (от О до 2).

Предложенное устройство обладает более широкой областью применения обеспечивая управление несколькими (К& 2) двухфазными аси1П5:ронньп.1и электродвигателями, при использовании устройства повьшшется надежность работы за счет снижения количества требуемого оборудования при управлении К электродвигателями по сравнению с суммарной надежност15Ю работы К устройств, выполненных в прототипе.

Формула изобретения

Устройство для управления асинхронным электроприводом, содержащее первьй й-разрядный двоичный счетчик, первьй и второй коммутаторы, первьй и второй дешифраторы, первьй накопитель, усилитель мощности, блок управления, составленньй из генератора импульсов, распределител:я импульсов, триггера Шмитта, первого и второго блоков синхронизации, первого и второго логических элементов 2ИЛИ, логического элемента НЕ, 2 выходов первого дешифратора соединены с 2 перАА4. С

выми входами первого накопителя, 2 вторых входов которого соединены с

11 1 (/

2 выходами второго дешифратора, первьй вход первого коммутатора соединен с первым выходом блока управления, силовой вход усилителя мощности соединен с первым входом блока управления и предназначен для под- к.гаочения к источнику питания переменного тока, выходы усилителя мощности предназначены для подключения к обмотке управления электродвигателя, прямой выход генератора импульсов соединен с входом распределителя импульсов, первый вход первого блока синхронизации соединен с входом логического элемента НЕ и с выходом триггера Шмитта, вход которого образует

131

первый вход блока управления, первый вход второго блока синхронизации со- еданен с выходом логического элемента НЕ и образует первый выход блока управления, выходы первого и второго блоков синхронизации соединены соответственно с входами первого логического элемента 2ИЛК, вторые входы первого и второго блоков синхронизации объединены, отличающееся тем, что, с целью расширения области применения за счет обеспечения управления как одним, так и п электродвигателями при минимуме аппаратурных затрат, в Hei o введены второй Q-раз- рядньй двоичньй счетчик, третий и че-увертьй дешифраторы, второй накопитель, 2 первых регистров, 2 вторых регистров, 2-1 усилителей мощности, логический элемент НЕ-2И, первьй логческий элемент 2И, первый RS-триггер в блок управления, выполненньй с четырьмя входами и семью выходами, вве деньг первьй и второй D-триггеры, вто рой и третий .RS-триггеры, второй, третий, четвертый, пятый и шестой логические элементы 2И, генератор импульсов снабжен инверсным-выходом а распределитель импульсов выполнен се миканальным, первый вход второго Q- разрЛдного.двоичного счетчика подключен к второму выходу блока управлени первьй вход первого N-разрядного двоичного счетчика и второй вход второго Q-разрядного двоичного счетчика объединены и предназначены для подач сигнала установки в исходное состояние, Ы вторых входов первого N-pas- рядкого двоичного счетчика предназначены для подачи кода исходного состония, Q выходов второго Q-разрядного двоичного счетчика соединены с Q первыми входами второго коммутатора, (р+)-й выход второго Q-разрядного двоичного счетчика соединен с третьим входом первого N-разрядного двоичного счетчика, N выходов которого соединены с N:входами первого дешифратора, первьй выход и (N+l)-й выход первого N-разрядного двоичного счетчика соединены соответственно с вторым и третьим входами блока управления, выход первого накопителя соединен с вторым входом первого коммутатора, Q вторых входов второго коммутатора предназначены для подачи кода номера управляемого электродвигателя, третий вход второго коммутатора и первый вход

0

5

0

2373

5

0

5

0

14

гического злгмента НЕ-2И объединены и подключены к третьему выходу блока управления, Q выходов второго коммутатора соединены с Q входами третьего дешифратора и Q первыми входами четвертого дешифратора, 2 выходов третьего дешифратора подключены к 2 первым входам второго накопителя, М вторых входов, К третьих входов и четвертьпЧ вход которого предназначены соотБвтственно для подачи кода управления, кода признака регулировочной характеристики и сигнала знака кода управления 5 пятьй вход второго накопителя соединен-с четвертым выходом блока управления, четвертьй вход которого предназначен для подачи сигнала управления записью информации во второй накопитель, М первых выходов, К вторых выходов и третий выход второго накопителя подключены соответственно к М первым входам, К вторьгм вхо-, дам второго дешифратора и третьему входу первого комм татора, первый и второй выходы которого подключены соответственно к первым и вторым входам каждого из 2 первых регистров, третий вход каждого из которых соединен с-соответствующим выходом четвертого дешифратора, второй вход которого подключен к пятому выходу блока управления, 2-й выход штвертого деюифратор 1 соединен с вторым входом логического элемента НЕ-2И, выход которого соединен с первым входом первого RS-тригге- ра, второй вход которого подключен к шестому выходу блока управления, выход первого RS-триггера соединен с первым входом первого логического элемента 2И,. второй вход которого подключен к седьмому выходу блока у равле- ния, первьй и второй выходы каждого ИЗ- 2 первых регистров соединены соот25

45

0

5

с первым и вторым входами соответствующего 2 вторых реветственнокаждого

гистров, выход первого логического элемента 2И соединен с объединенными третьими входами всех 2 вторых регистров, первый и второй выходы каждого из 2 вторых регистров соединены соответственно с первым и вторым управляющими входами соответствующих усилителей мощности, силовые входы 2 -1. усилителей мощности объединены и соединены с силовым входом первого усилителя мощности, выходы усилителей мощности предназначены дпя подключения к обмоткам управления соответствующих электродвигателей, выход первого логического элемента 2ИЛИ соединен с первым входом второго RS- триггера, второй вход которого объединен с первым входом второго логического элемента 2ИПИ и подключен к выходу второго логического элемента 211, выход второго RS-триггера соединен с первым входом третьего логиче- ского элемента 2И, второй вход которого о.бъединен с первым входом вто- рого D-триггера и подключен к первому выходу распределителя импульсов, вто- . рой выход которого образует шестой выход блока управления, третий выход распределителя импульсов соединен с первым входом второго логического элемента 2И, второй вход второго D- .триггера обра зует четвертый вход бло- ка управления, четвертый выход рас- пред елителя импульсов соединен с третьим входом второго D-триггера, выход которого соединен с первыми входами пятого и шестого логических элементов 2И и образует третий выход блока управления, пятый выход распределителя импульсов соединен с вторым входом шестого логического элемента 2И, выход которого образует четвертый

выход блока управления., гаестой вьгход распределителя импульсов соединен с вторым входом пятого логического элемента 2И, выход которого соединен с вторым входом второго логического элемента 2ИЛИ, выход которого образует пятый выход блока управления, седьмой выход распределителя импульсов образует седьмой выход блока управления и соединен с первым входом четвертого логического элемента 2И, выход которого образует второй выход блока управления, вторые входы второго и четвертого логических элементов 2И объединены и соединены с выходом первого D-триггера,, первый вход которого объединен с первым входом третьего RS-триггера и подключен к выходу третьего логического элемента 2И, второй вход первого D-триггера соединен с выходом третьего RS-триггера, второй вход которого образует третий вход блока управления, третий вход первого D-триггера образует второй вход блока управления, инверсный выход генератора импульсов соединен с объединенными вторыми входами первого и второго блоков синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1985 |

|

SU1283934A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для генерирования кодов заданного веса | 1985 |

|

SU1275413A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

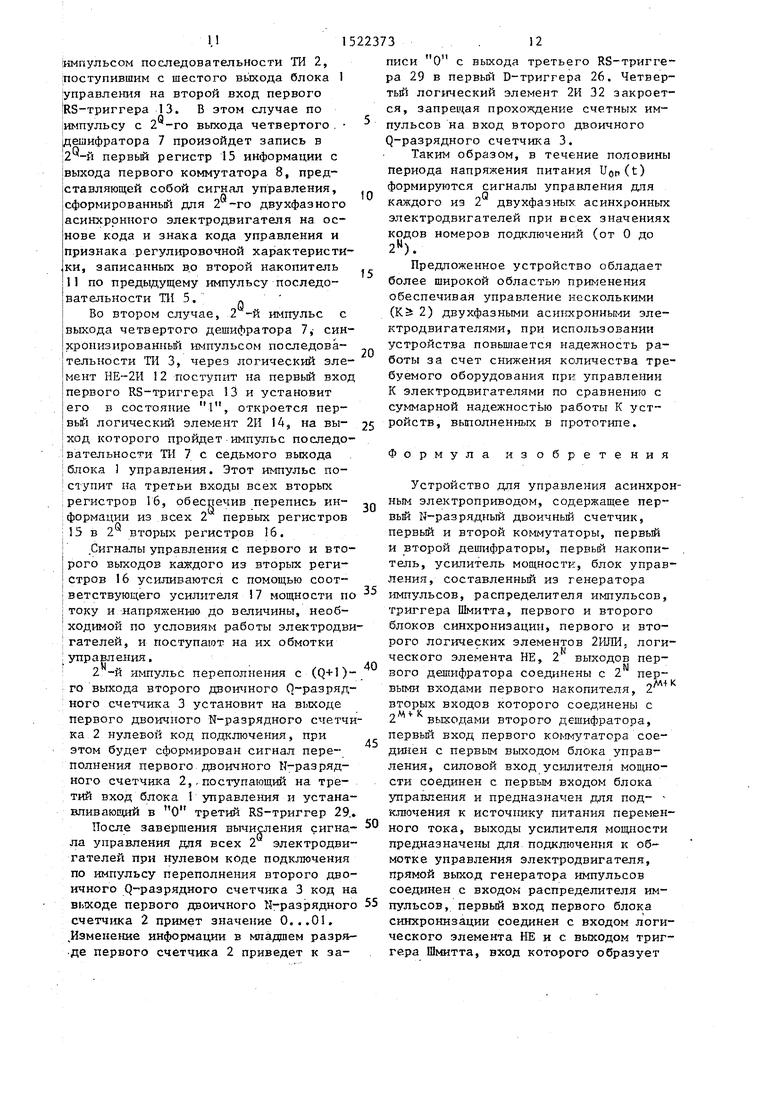

Изобретение относится к электротехнике и может быть использовано в многодвигательных электроприводах исполнительных механизмов цифровых систем автоматического регулирования. Целью изобретения является расширение области применения за счет обеспечения управления как одним, так и N электродвигателями при минимуме аппаратурных затрат. За счет введения в состав устройства второго Q-разрядного двоичного счетчика 3, третьего и четвертого дешифраторов 6, 7, второго накопителя 11, 2Q первых регистров 15, 2Q вторых регистров 16, 2Q - 1 усилителей мощности 17, логических элементов НЕ-2И 12, 2И 14 и RS-триггера 13 и введения в блок управления 1 дополнительно двух D-триггеров, двух RS-триггеров и шести логических элементов 2И данное устройство обладает более широкой областью применения, обеспечивая управление несколькими (K ≥ 2) двухфазными асинхронными электродвигателями, при этом повышается надежность работы устройства за счет снижения количества требуемого оборудования при управлении K электродвигателями по сравнению с суммарной надежностью работы K устройств в прототипе. 2 ил.

фае. 2.

| Устройство для управления двухфазным асинхронным электродвигателем | 1981 |

|

SU1056422A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1985 |

|

SU1283934A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1989-11-15—Публикация

1987-06-15—Подача