1

Изобретение относится к вычислительной технике и может быть использовано для построения регистров сдвига и устройств памяти в универсальных и специализированных электронных цифровых вычислительных машинах.

Известны триггеры на МОП-транзисторах, содержащие в каждом плече последователь-, но включенные ключевой и нагрузочный тран-. 3HCTOj)bi, блокировочный транзистор, соединенный истоком со стоком ключевого транзистора первого плеча, стоком - с затвором ключевого транзистора второго плеча, а затвором - с первой шиной тактовых импульсов, управляющий транзистор, у которого исток соединен с входной шиной, а затвор - со второй шиной тактовых импульсов.

Предлагаемое устройство отличается от известных тем, что в нем сток ключевого транзистора второго плеча соединен с затвором ключевого транзистора первого плеча, причем исток каждого ключевого транзистора подключен к затвору управляющего транзистора, сток которого соединен со стоком ключевого транзистора первого плеча триггера.

Это повышает надежность работы триггера.

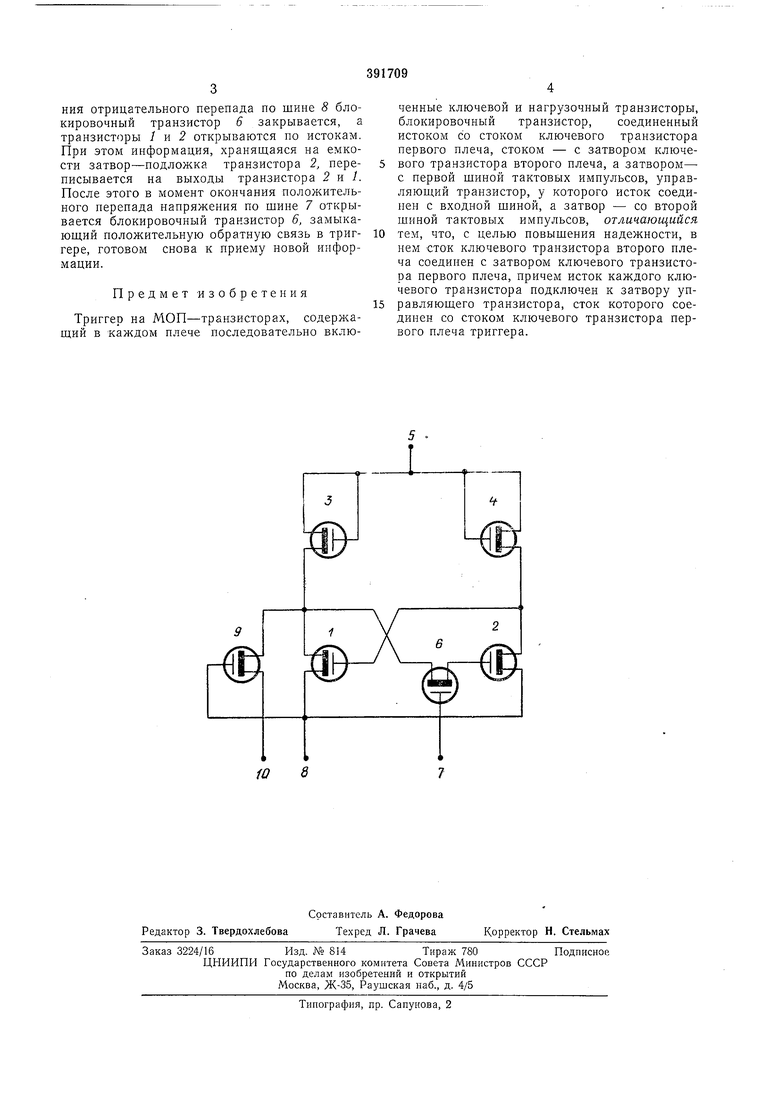

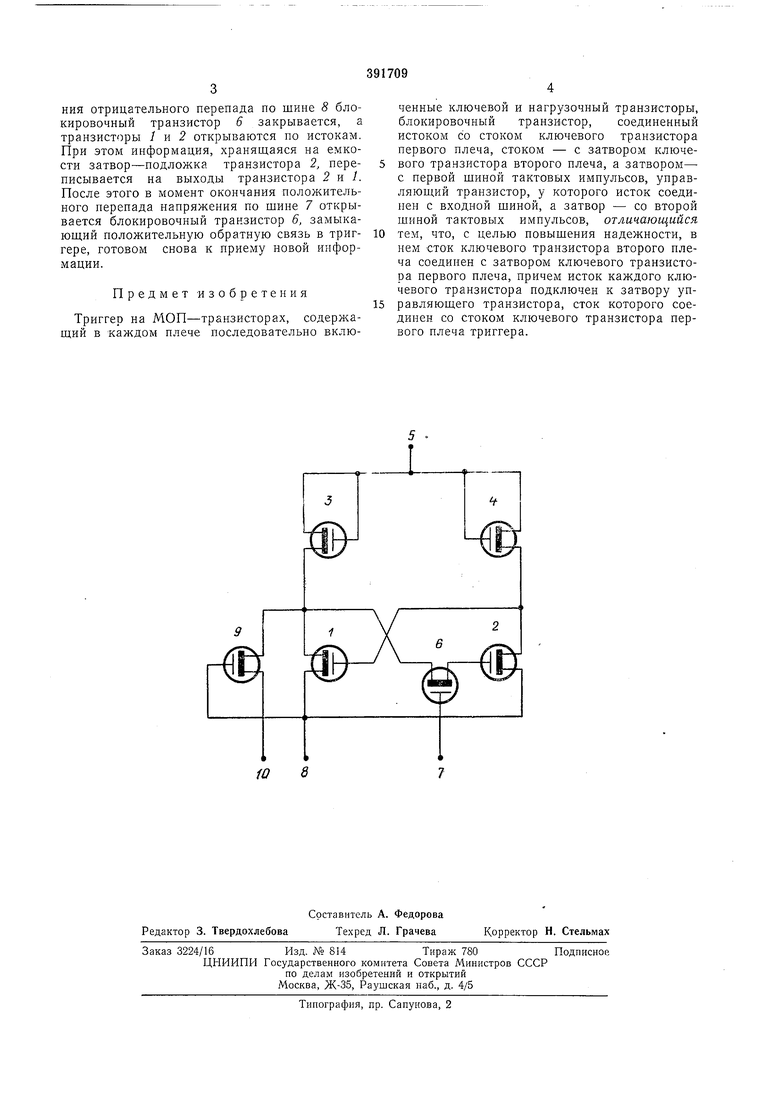

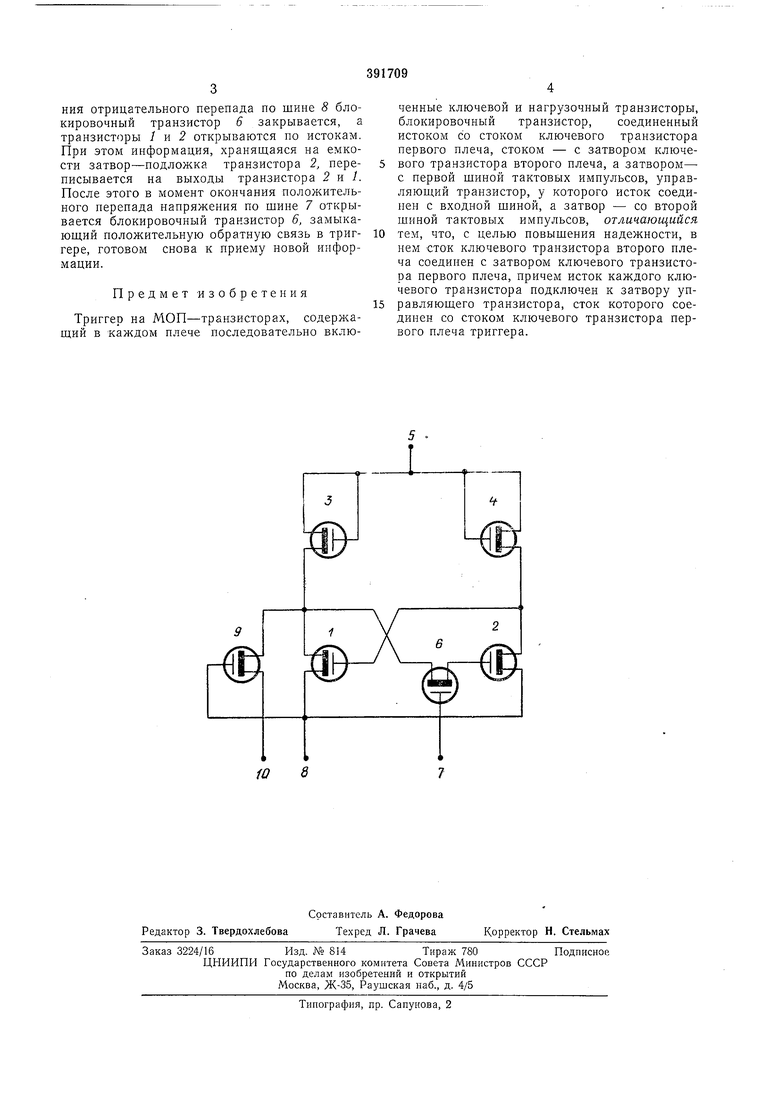

На чертеже представлена схема предлагаемого триггера.

Триггер содержит ключевые 1, 2 и нагрузочные 3, 4 транзисторы, источник 5 питания, блокировочный транзистор 6, шины 7 и S питания, управляющий транзистор 9, входную шину 10. В режиме хранения информации низкий уровень напряжения по шине 7 поддерживает блокировочный транзистор 6 в открытом состоянии, а высокий уровень напряжения по шине 8 поддерживает открытыми по истокам транзисторы / и 2 и закрытыми по затвору управляющий транзистор 9. Благодаря этому транзисторы 1 н 2 вместе с нагрузочными транзисторами 3 и 4 в режиме хранения информации представляют собой триггер с перекрестными связями и с двумя устойчивыми состояниями.

В режиме записи информации низкий уровень напряжения по шине 8 открывает управляющий транзистор 9 и закрывают транзисторы 1 и 2. В это время происходит запись новой информации через управляющий транзистор 9 и блокировочный транзистор 6 на емкости Сзп затвор-подложка транзистора 2. При этом новая информация с емкости затвор - подложка транзистора 2 не поступает на выход триггера, так как транзистор 2 закрыт по истоку отрицательным напряжением по шине 8. Далее при подаче положительного перепада напряжения по шине 7 закрывается блокировочный транзистор 6. После окончания отрицательного перепада по шине 8 блокировочный транзистор 6 закрывается, а транзисторы 1 и 2 открываются но истокам. При этом информация, хранящаяся на емкости затвор--подложка транзистора 2, переписывается на выходы транзистора 2 н 1. После этого в момент окончания положительного нерепада напряжения по шине 7 открывается блокировочный транзистор 6, замыкаюш,ий положительную обратную связь в триггере, готовом снова к приему новой информации.

Предмет изобретения

Триггер на МОП-транзисторах, содержащий в каждом нлече последовательно включенные ключевой и нагрузочный транзисторы, блокировочный транзистор, соединенный истоком со стоком ключевого транзистора первого плеча, стоком - с затвором ключевого транзистора второго плеча, а затвором- с первой шиной тактовых импульсов, унравЛЯЮШ.ИЙ транзистор, у которого исток соединен с входной шиной, а затвор - со второй шиной тактовых импульсов, отличающийся тем, что, с целью повышения надежности, в нем сток ключевого транзистора второго нлеча соединен с затвором ключевого транзистора первого плеча, причем исток каждого ключевого транзистора подключен к затвору управляющего транзистора, сток которого соединен со стоком ключевого транзистора первого плеча триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь суммы на мдп-транзисторах | 1972 |

|

SU516038A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

| Матрица постоянного запоминающего устройства | 1983 |

|

SU1348908A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

fO 8

Авторы

Даты

1973-01-01—Публикация