1

Изобретение otнoc.итcя к автоматике и Sbtчислителыюй технике, в частности может найти применение при построении статических регистров сдвига.

Р1звестиы ячейки регистра сДвига, содержащие триггер на МОП-транзисторах с непосредственными перекрестными связями и проходной МОП-трапзистор.

Цель изобретения - упростить схему.

Это достигается тем, что .в предлагаемую ячейку регистра сдвпга введен дополпительный МОП-транзистор, исток -которого соединен с затвором, затвор - со стоком проходного МОП-транзистора, а сток - со стоком МОП-транзистора нулевого плеча триггера, источником подключенного к шине дополнительных тактовых импульсов.

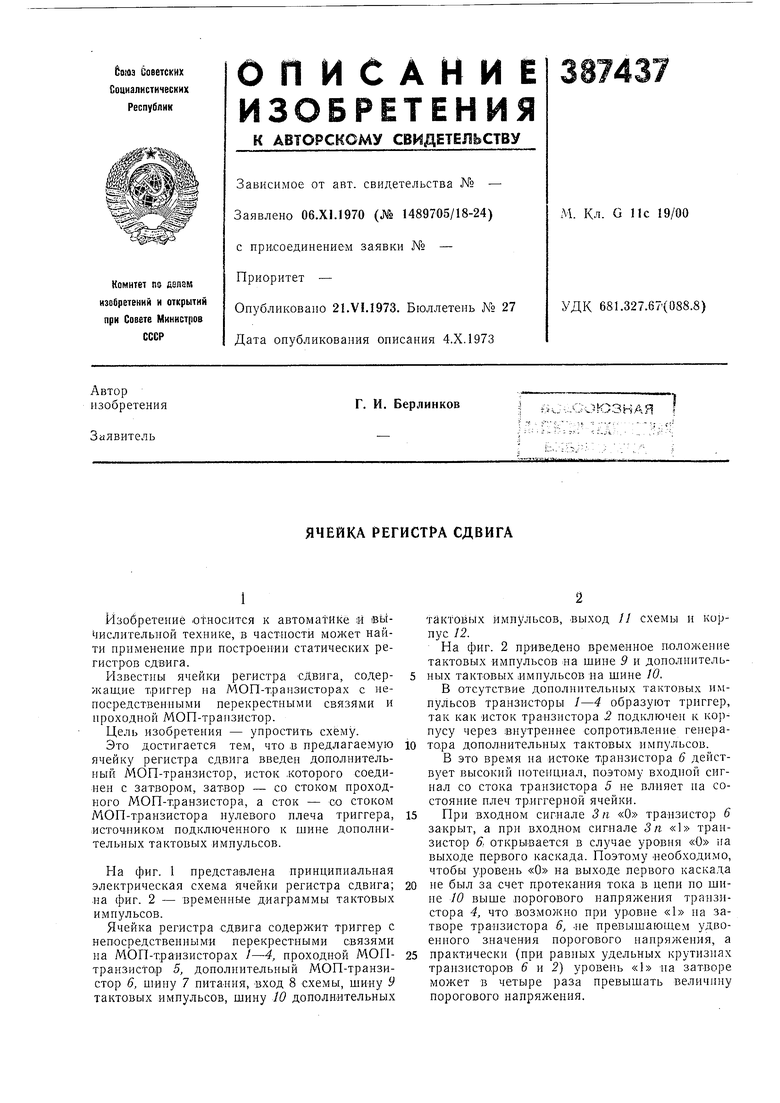

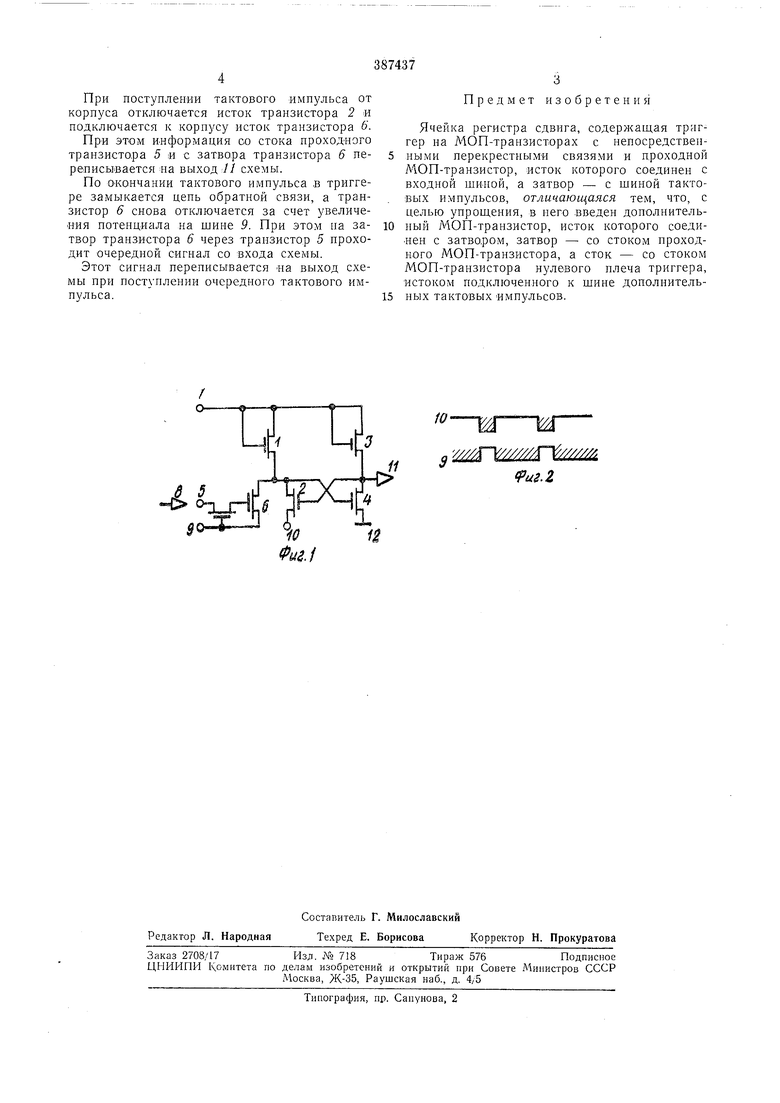

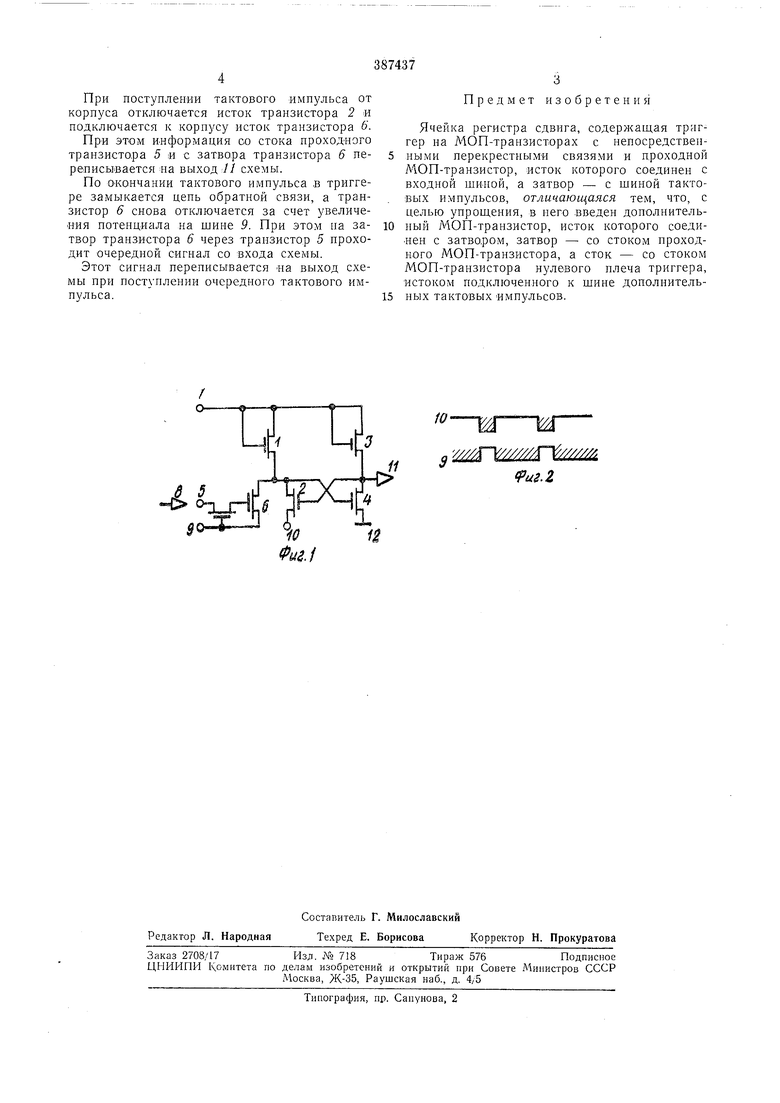

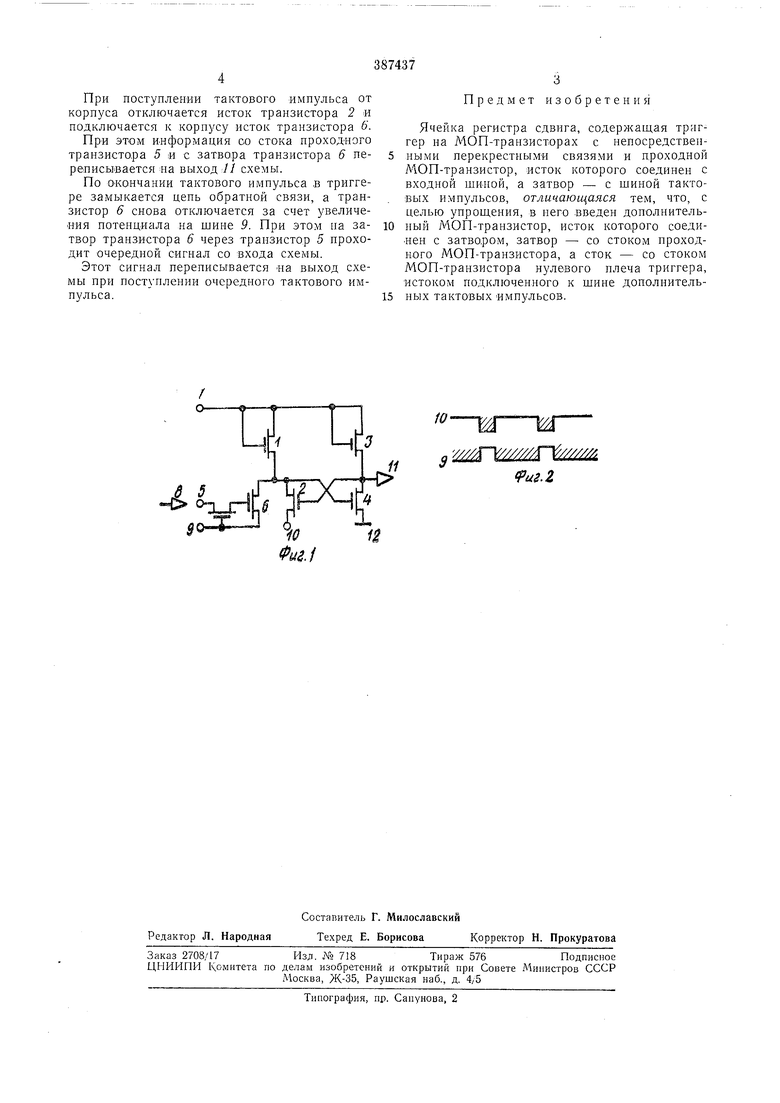

На фиг. 1 представлена принципиальная электрическая схема ячейки регистра сдвига; .на фиг. 2 - временные диаграммы тактовых имнульсов.

Ячейка регистра сдвига содержит триггер с непосредственными перекрестными связями на МОП-транзисторах /-4, проходной МОПтранзистор 5, дополнительный МОП-транзистор 6, шипу 7 питания, вход 8 схемы, шину 9 тактовых импульсов, шину 10 дополнительных

тактовых импульсов, выход /у схемы и корпус 12.

На фиг. 2 приведено временное положение тактовых импульсов иа шипе 9 и дополнительных тактовых имнульсов на шине W.

В отсутствие дополнительных тактовых импульсоЁ Транзисторы /-4 образуют триггер, так как исток транзистора 2 подключен к корпусу через внутреннее сопротивление генерато.ра дополнительных тактовых импульсов.

В это время на истоке транзистора 6 действует высокий потенциал, поэтому входиой сигнал со стока транзистора 5 не влияет на состояние плеч триггерной ячейки.

При входном сигнале 3 п «О транзистор 6 закрыт, а при входном сигнале 3 п «1 транзистор 6, открывается в случае уровня «О иа выходе нервого каскада. Поэтому необходимо, чтобы уровень «О на выходе первого каскада

не был за счет протекания тока в цепи по шнне 10 выше порогового напряжения транзистора 4, что возможно при уровне «1 па затворе транзистора 6, не превышаюш,ем удвоенного значения порогового папряжения, а

практически (при удельных крутизнах траизисторов б и 2) уровень «1 на затворе может в четыре раза превышать величину порогового напряжения.

При поступлении тактового импульса от корпуса отключается исток транзистора 2 и подключается к корпусу исток транзистора 6.

При этом информация со стока проходного транзистора 5 и с затвора транзистора 6 переписывается да ВЫХОД:// схемы.

По окончании тактового импульса .в триггере замыкается цепь обратной связи, а транзистор 6 снова отключается за счет увеличе«ия потенциала на шине 9. При этом на затвор транзистора 6 через транзистор 5 проходит очередной сигнал со входа схемы.

Этот сигнал переписывается «а выход схемы при поступлении очередного тактового импульса.

3 Предмет изобретения

Ячейка регистра сдвига, содержащая триггер на МОП-транзисторах с непосредственными перекрестными связями и проходной МОП-транзистор, исток которого соединен с входной шиной, а затвор - с шиной тактовых импульсов, отличающаяся тем, что, с целью упрош,ения, в него введен дополнительный МОП-транзистор, исток которого соединен с затвором, затвор - со стоком проходного МОП-транзистора, а сток - со стоком МОП-транзистора нулевого плеча триггера, истоком подключенного к шине дополнительных тактовых -импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕР НА МОП—ТРАНЗИСТОРАХ | 1973 |

|

SU391709A1 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2527188C1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| СДВИГОВЫЙ РЕГИСТР | 2013 |

|

RU2522306C1 |

| Ячейка памяти | 1981 |

|

SU972592A1 |

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| КРЕМНИЕВЫЙ МУЛЬТИПЛЕКСОР | 2015 |

|

RU2602373C1 |

| ДВУХТАКТНЫЙ ДИНАМИЧЕСКИЙ РЕГИСТР СДВИГА | 2014 |

|

RU2556437C1 |

| Преобразователь напряжения для кварцевых наручных часов | 1988 |

|

SU1497695A1 |

м ммт////

fpug-Z

Авторы

Даты

1973-01-01—Публикация