Изобретение относится к радиотехнике и может быть использовано в системах связи и радиолокации для построения систем синхронизации в составе радиотехнических комплексов.

Наиболее близким по технической сущности и достигаемому результату (прототипом) является устройство фазовой автоподстройки частоты (авторское свидетельство СССР SU 1663768 А1 «Устройство фазовой автоподстройки частоты», В.Е. Мартиросов, А.П. Гуськов). Достоинства указанной схемы заключаются в повышенной помехоустойчивости (в улучшенных фильтрующих свойствах) и в расширенных полосах захвата и удержания синхронного режима работы, что достигается использованием специальной дополнительной цифровой ветви управления частотой подстраиваемого генератора. Ширина полос захвата и удержания синхронного режима работы устройства при этом ограничивается только разрядностью реверсивного счетчика и частотой дискретизации, на которой работает цифровая часть схемы.

Существенной особенностью данного устройства является необходимость предварительного выравнивания удвоенного значения коэффициента петлевого усиления (определяемого для аналоговой ветви управления частотой подстраиваемого генератора) с дискретом напряжения, соответствующего значению младшего разряда на выходе ЦАП (для цифровой ветви управления частотой подстраиваемого генератора).

Недостаток прототипа заключается в некорректной работе при возникновении изменений и флуктуации амплитуды входного сигнала устройства или изменении коэффициента передачи второго фазового детектора, от которых зависит значение коэффициента петлевого усиления системы. При возникновении изменений или флуктуаций амплитуды входного сигнала устройства или изменении коэффициента передачи второго фазового детектора происходит нарушение описанного выше согласования коэффициента петлевого усиления и минимального дискрета напряжения с выхода ЦАП, что нарушает корректность работы устройства в целом.

Технический результат изобретения заключается в комплексном (одновременном) улучшении основных параметров системы синхронизации, а именно: в повышении помехоустойчивости (в улучшении фильтрующих свойств системы), в расширении полос захвата и удержания синхронного режима работы, в сокращении времени вхождения в синхронный режим работы, в обеспечении нулевой статической ошибки по фазе и в обеспечении корректной работы устройства в условиях наличия изменений и флуктуаций амплитуды входного сигнала устройства или изменений коэффициентов передачи фазовых детекторов. Указанный результат достигается введением в состав устройства блока установки и стабилизации петлевого усиления - БУСПУ. В БУСПУ в текущем масштабе времени осуществляется оценка уровня амплитуды входного сигнала с учетом его прохождения через фазовые детекторы и вычисляется корректирующий множитель коэффициента петлевого усиления, который далее подается на перемножитель сигналов, размещенный в аналоговой ветви управления после коммутатора полярности. За счет этого достигается: автоматическая установка и стабилизация требуемого значения коэффициента петлевого усиления; сопряжение коэффициентов передач по аналоговой и цифровой ветвям управления частотой подстраиваемого генератора в процессе работы, что и обеспечивает корректную работу устройства при наличии изменений и флуктуациях амплитуды входного сигнала или изменении коэффициентов передачи фазовых детекторов.

Вторым отличительным признаком системы (по отношению к прототипу) является замена низкочастотного петлевого фильтра интегратором. При этом система ГЛСС переходит в разряд астатических систем (систем второго идеального порядка), что обеспечивает нулевую фазовую ошибку синхронизации во всем диапазоне начальных частотных расстроек входного сигнала и подстраиваемого генератора.

На фиг. 1 представлена структурная схема глобально линеаризованной системы синхронизации с автоматической установкой и стабилизацией коэффициента петлевого усиления; на фиг. 2 и 3 - эпюры напряжений в различных точках системы, иллюстрирующие ее работу при положительном и отрицательном начальном частотном рассогласовании.

ГЛСС содержит подстраиваемый генератор (ПГ) 1, фазовращатель 2 на π/2, первый и второй фазовые детекторы 3 и 4, первый и второй компараторы напряжений 5 и 6, коммутатор 7 полярности сигнала, реверсивный счетчик 8, цифроаналоговый преобразователь (ЦАП) 9, первый сумматор 10, линию 11 временной задержки, интегратор 12, логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ» 13, формирователь импульсов 14, перемножитель сигналов 15, первый и второй блоки возведения текущего значения напряжения во вторую степень 16 и 17, второй сумматор 18, блок возведения текущего значения напряжения в 1/2 степень 19, первый делитель напряжений 20 и второй масштабирующий делитель напряжения 21.

Устройство работает следующим образом. При появлении входного сигнала на выходах первого 3 и второго 4 фазовых детекторов возникают квадратурные составляющие биений с частотой, соответствующей начальной частотной расстройке Δω=ωс-ω0, где ωс - частота входного сигнала, ω0 - частота колебаний подстраиваемого генератора 1 при исходном значении управляющего напряжения Up (p - регулирующее). Выход первого фазового детектора показан на фиг. 2а, фиг. 3а, а выход второго фазового детектора на фиг. 2б, фиг. 3б для случаев ωс больше ω0 и ωс меньше ω0 соответственно. Первый 5 и второй 6 компараторы напряжений из выходных сигналов первого 3 и второго 4 фазовых детекторов формируют логические сигналы, показанные на фиг. 2в, д и фиг. 3в, д (фиг. 2в соответствует выходному сигналу первого компаратора 5, фиг. 2д - выходному сигналу второго компаратора 6 при ωс больше ω0; аналогично на фиг. 3в и фиг. 3д для выходных сигналов первого 5 и второго 6 компараторов при ωс меньше ω0). Формирователь импульсов 14 формирует короткие импульсы в моменты времени, соответствующие заднему фронту выходного сигнала первого компаратора 5. На фиг. 2г и фиг. 3г показаны эти импульсы, прошедшие через линию 11 временной задержки. Выходной сигнал логической схемы «ИСКЛЮЧАЮЩЕЕ ИЛИ» 13 при ωс больше ω0 показан на фиг. 2е, а при ωс меньше ω0 - на фиг. 3е. Из эпюр фиг. 2г, е и фиг. 3г, е следует, что код, записанный в реверсивном счетчике 8, и, следовательно, выходное напряжение ЦАП 9 возрастают при ωс больше ω0 и уменьшаются при ωс меньше ω0. Эпюры выходного напряжения ЦАП 9 показаны на фиг. 2ж (при ωс больше ω0) и 3ж (при ωс меньше ω0).

Таким образом, при появлении сигнала на входе системы выходное напряжение ЦАП 9 ступенчато нарастает (при ωс больше ω0) или ступенчато уменьшается (при ωс меньше ω0), в результате чего частота подстраиваемого генератора 1 изменяется в сторону уменьшения текущего частотного рассогласования Δω).

При снижении текущего частотного рассогласования Δω до величины, соответствующей полосе захвата аналоговой ветви управления частотой ПГ, включающей в себя второй фазовый детектор 4, коммутатор полярности сигнала 7, перемножитель сигналов 15, интегратор 12, первый сумматор 10 и подстраиваемый генератор 1, происходит установление синхронного режима работы ГЛСС.

Выходной сигнал коммутатора 7 полярности сигнала для случая ωс больше ω0 показан на фиг. 2л, а для случая ωс меньше ω0 показан на фиг. 3л.

Выходной сигнал первого сумматора 10 для случая ωс больше ω0 показан на фиг. 2з, а для случая ωс меньше ω0 показан на фиг. 3з.

Наличие квадратурных каналов для формирования сигналов фазового рассогласования входного и опорного колебаний ГЛСС позволяет создать дополнительную цифровую ветвь управления частотой ПГ (включающую блоки 5, 6, 8, 9, 11, 13 и 14), что приводит комплексному (одновременному) улучшению основных параметров системы синхронизации, а именно: к повышению помехоустойчивости (улучшению фильтрующих свойств системы в синхронном режиме работы), к расширению полос захвата и удержания синхронного режима работы системы и к значительному сокращению времени вхождения в синхронный режим работы системы.

Для корректного функционирования устройства необходимо обеспечить согласование локальных дискриминационных характеристик цифровой и аналоговой ветвей управления частотой ПГ. Единичный дискрет амплитуды ΔUЦАП, формируемого на выходе ЦАП ступенчатого напряжения, должен соответствовать полному размаху амплитуды сигнала на выходе коммутатора полярности, равному 2А0. Для этой цели опорное напряжение Uоп цифро-аналогового преобразователя используется для формирования единичных аналоговых ступеней напряжения с выхода ЦАП (ΔUЦАП=Uоп/2q, где q - разрядность ЦАП) и для вычисления во втором масштабирующем делителе напряжения 21 нормализованного (требуемого) значения амплитуды сигнала фазового рассогласования с выхода фазового детектора (А0=Uоп/2q+1). Далее с помощью блока установки и стабилизации петлевого усиления реально возникающее значение амплитуды сигнала фазового рассогласования приводится к нормализованному (требуемому) значению (А0=Uоп/2q+1).

Установка и стабилизация требуемого коэффициента петлевого усиления аналоговой ветви управления происходит следующим образом. Квадратурные составляющие биений с частотой Δω с выходов первого и второго фазовых детекторов 3 и 4 подаются на входы первого и второго блоков возведения текущего значения напряжения во вторую степень 16 и 17 соответственно. На фиг. 2а, б и фиг. 3а, б соответственно для случаев ωс больше ω0 и ωс меньше ω0 показаны сигналы с выходов фазовых детекторов с непостоянным значением амплитуды входного сигнала устройства. Выходные сигналы блоков 16 и 17 подаются на первый и второй входы второго сумматора 18. Сигнал с выхода второго сумматора 18 поступает на вход блока возведения текущего значения напряжения в 1/2 степень 19, с выхода которого напряжение Ареал (реал - реальное) поступает на первый вход (вход знаменателя дроби деления) первого делителя напряжений 20. На второй вход (вход числителя дроби деления) первого делителя напряжений 20 поступает постоянное напряжение А0, уровень которого соответствует номинальному (требуемому) значению амплитуды входного сигнала. Сигнал на выходе первого делителя напряжений 20 (показанный на фиг. 2к и фиг. 3к соответственно для случаев ωс больше ω0 и ωс меньше ω0) соответствует мгновенному текущему отклонению значения амплитуды входного сигнала от номинального значения А0 и представляет собой корректирующий коэффициент, подаваемый на второй вход перемножителя 15. Выходной сигнал перемножителя 15 для случая ωс больше ω0 показан на фиг. 2л, а для случая ωс меньше ω0 показан на фиг. 3л.

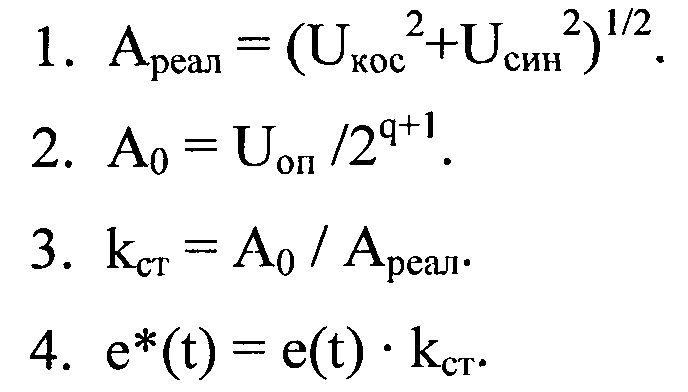

Если ввести обозначения: Uкос, Uсин - напряжение на выходе первого и второго фазовых детекторов соответственно (кос - косинусное, син - синусное), Ареал - мгновенное текущее значение амплитуды входного сигнала с учетом его прохождения через фазовые детекторы, Uоп - опорное напряжение ЦАП, А0 - номинальное (требуемое) значение амплитуды входного сигнала с учетом его прохождения через фазовые детекторы, kст - коэффициент коррекции значения коэффициента петлевого усиления (ст - стабилизации), e(t) - напряжение на выходе компаратора напряжений 7, e*(t) - сигнал на выходе блока 15, то выполняемую в БУСПУ процедуру коррекции значения коэффициента петлевого усиления системы можно описать следующими соотношениями:

Таким образом, реализуется сопряжение коэффициентов передачи аналоговой ветви управления частотой ПГ (ее локальная дискриминационная характеристика приведена на фиг. 2л, фиг. 3л) и цифровой ветви управления (ее локальная дискриминационная характеристика приведена на фиг. 2ж, фиг. 3ж). Это обеспечивает «сшивание» и «линеаризацию» (см. эпюры фиг. 2з, фиг. 3з) глобальной дискриминационной характеристики заявляемого устройства и обеспечивает корректную работу ГЛСС в условиях наличия изменений и флуктуаций амплитуды входного сигнала или изменений коэффициента передачи фазовых детекторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2566813C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ СИГНАЛОВ ПО СЕТИ ЭЛЕКТРОПИТАНИЯ | 2001 |

|

RU2178952C1 |

| Демодулятор сигналов частотной телеграфии | 1987 |

|

SU1497756A1 |

| Демодулятор сигналов фазовой телеграфии | 1986 |

|

SU1392631A1 |

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

| Модулятор сигналов фазовой телеграфии | 1986 |

|

SU1392628A1 |

Изобретение относится к технике связи. Технический результат заключается в комплексном улучшении основных параметров системы синхронизации, а именно: в повышении помехоустойчивости, в улучшении фильтрующих свойств системы, в расширении полос захвата и удержании синхронного режима работы, в уменьшении времени вхождения в синхронный режим работы, в обеспечении нулевой статической ошибки по фазе и в обеспечении корректной работы устройства в условиях наличия изменений и флуктуаций амплитуды входного сигнала или изменений коэффициента передачи фазовых детекторов. Устройство содержит подстраиваемый генератор 1, фазовращатель 2 на π/2, первый и второй фазовые детекторы 3 и 4, первый и второй компараторы напряжений 5 и 6, коммутатор 7 полярности сигнала, реверсивный счетчик 8, цифроаналоговый преобразователь 9, первый сумматор 10, линию 11 временной задержки, интегратор 12, логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ» 13, формирователь импульсов 14, перемножитель сигналов 15, первый и второй блоки возведения текущего значения напряжения во вторую степень 16 и 17, второй сумматор 18, блок возведения текущего значения напряжения в 1/2 степень 19, первый делитель напряжений 20 и второй масштабирующий делитель напряжения 21. 3 ил.

Глобально линеаризованная система синхронизации, содержащая последовательно соединенные подстраиваемый генератор, фазовращатель на π/2, первый фазовый детектор, второй вход которого является входом устройства, первый компаратор напряжений, второй вход которого соединен с общей шиной, формирователь импульсов, линию временной задержки, реверсивный счетчик, счетный вход которой соединен с выходом линии временной задержки, цифроаналоговый преобразователь, первый сумматор, первый вход которого соединен с выходом цифроаналогового преобразователя, а выход соединен с управляющим входом подстраиваемого генератора, а также последовательно соединенные второй фазовый детектор, первый вход которого соединен с выходом подстраиваемого генератора, а второй вход соединен с входом устройства, второй компаратор напряжений, первый вход которого соединен с выходом второго фазового детектора, а второй вход подключен к общей шине, логическую схему «исключающее или», второй вход которой соединен с выходом первого компаратора напряжений, а выход подключен к управляющему входу реверсивного счетчика, а также коммутатор полярности сигнала, управляющий вход которого подключен к выходу первого компаратора напряжений, а информационный вход соединен с выходом второго фазового детектора, отличающаяся тем, что в устройство введены последовательно соединенные первый блок возведения текущего значения напряжения во вторую степень, вход которого соединен с выходом первого фазового детектора, второй сумматор, блок возведения текущего значения напряжения в 1/2 степень, соединенный по первому входу первый делитель напряжений и перемножитель сигналов, второй вход которого подключен к выходу коммутатора полярности, а выход подключен ко второму входу первого сумматора, а также введены второй блок возведения текущего значения напряжения во вторую степень, вход которого соединен с выходом второго фазового детектора, а выход подключен ко второму входу второго сумматора, а также введен второй масштабирующий делитель напряжения, выход которого подключен ко второму входу первого делителя напряжений и на вход которого подается опорное напряжение цифроаналогового преобразователя, а также введен интегратор, вход которого подключен к выходу перемножителя сигналов, а выход подключен к третьему входу первого сумматора.

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| А.А.КОСТЫРЯ и др | |||

| ИССЛЕДОВАНИЕ ФИЛЬТРУЮЩИХ СВОЙСТВ СИСТЕМЫ ФАЗОВОЙ АВТОПОДСТРОЙКИ ПРИМЕНИТЕЛЬНО К ЗАДАЧЕ СИНХРОНИЗАЦИИ ВРЕМЕНИ И ЧАСТОТЫ | |||

| Прибор для автоматического контроля скорости поездов | 1923 |

|

SU485A1 |

| Изложница с суживающимся книзу сечением и с вертикально перемещающимся днищем | 1924 |

|

SU2012A1 |

| Универсальный двойной гаечный ключ | 1920 |

|

SU169A1 |

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

2015-06-27—Публикация

2014-06-17—Подача