Изобретение относится к радиотехнике и может быть использовано в системах телекоммуникации и цифровой передачи данных в составе радиотехнических комплексов.

Наиболее близким по технической сущности и достигаемому результату (прототипом) является модулятор сигналов двукратной фазовой телеграфии (авторское свидетельство СССР SU 1390811 A1 «Модулятор сигналов двукратной фазовой телеграфии», Московский авиационный институт им. Серго Орджоникидзе, В.Е. Мартиросов). Достоинства указанной схемы заключаются в повышенной скорости модуляции и в достаточной точности и стабильности установа дискретов фазы в условиях постоянного значения коэффициента петлевого усиления устройства, что достигается использованием специальной дополнительной цифровой ветви управления (блок 19 прототипа) частотой подстраиваемого генератора. Устройство работает в двух режимах: режим настройки частоты и фазы колебания подстраиваемого генератора и режим синхронной работы модулятора. В режиме настройки частоты и фазы выходной сигнал цифроаналогового преобразователя (ЦАП), имеющий вид периодического линейно изменяющегося ступенчатого напряжения, нарастает со скоростью, определяемой частотой следования импульсов формируемых генератором счетных импульсов (ГСИ). При наличии рассогласования по частоте между колебанием опорного генератора (ОГ) и колебанием с выхода подстраиваемого генератора (ПГ) цифровая ветвь управления осуществляет монотонное и равномерное изменение частоты ПГ до момента синхронизации устройства по частоте. Далее осуществляется установка фазы выходного сигнала модулятора, которая определяется уровнем опорного напряжения. Таким образом, цифровая ветвь управления обеспечивает вхождение устройства в синхронный режим работы по частоте и определяет дискретную установку фазы в синхронном режиме работы. При этом старшие разряды реверсивного счетчика определяют полосу захвата синхронного режима работы квазикогерентного модулятора по частоте, а младшие разряды реверсивного счетчика регламентируют точность установа дискрета фазы модулятора. Время синхронизации устройства по частоте определяется частотой следования импульсов с ГСИ и значением начальной частотной расстройки. После завершения процедур настройки частоты и фазы устройство переходит в режим синхронной работы.

В режиме синхронной работы первая логическая схема «ИСКЛЮЧАЮЩЕЕ ИЛИ» (блок 9 прототипа) управляет коммутатором сигнала (блок 8 прототипа), подключая на его выход выходной сигнал первого коммутатора полярности (блок 6 прототипа) при совпадении логических сигналах на своих входах, либо выходной сигнал второго коммутатора полярности (блок 7 прототипа) в противном случае. В результате напряжение на выходе коммутатора сигналов всегда положительно, в первом и третьем квадранте фазового рассогласования между колебаниями опорного генератора и подстраиваемого генератора оно подается с выхода фазового детектора с синусоидальной дискриминационной характеристикой (блок 2 прототипа), во втором и четвертом квадрантах - с выхода фазового детектора с косинусоидальной дискриминационной характеристикой (блок 3 прототипа). Таким образом, ближайшие точки устойчивого равновесия на фазовом портрете системы будут располагаться на расстоянии π, в случаях, когда и исходное, и конечное состояния фазы модулированного сигнала принадлежат к квадрантам фазового рассогласования с четными номерами, либо когда и исходное, и конечное состояния фазы принадлежат к квадрантам с нечетными номерами. В случаях, когда происходит переход между состояниями фазы модулированного сигнала, одно из которых принадлежит к квадранту с четным номером, а другое принадлежит к квадранту с нечетным номерам, ближайшие точки устойчивого равновесия на фазовом портрете системы будут располагаться на расстоянии π/2.

Вторая и третья логические схемы «ИСКЛЮЧАЮЩЕЕ ИЛИ» (блоки 10 и 11 прототипа) вырабатывают на своих выходах логические нули при совпадении логических сигналов на их входах, либо логические единицы в ином случае. На выходе логической схемы «ИЛИ» (блок 14 прототипа) будет нулевое напряжение при наличии логических нулей на обоих ее входах, т.е. на выходах логических схем «ИСКЛЮЧАЮЩЕЕ ИЛИ», либо напряжение фиксированного уровня при наличии хотя бы одной логической единицы на ее входе. После установления синхронного режима работы логические сигналы на входах каждой логической схемы «ИСКЛЮЧАЮЩЕЕ ИЛИ» совпадают и на выходе логической схемы «ИЛИ» напряжение равно нулю. При изменении логического уровня на любом из управляющих входов (выводы 27, 28 прототипа) устройства (или на обоих одновременно), на выходе логической схемы «ИЛИ» происходит изменение логического уровня сигнала на противоположный. При этом скачком изменяется величина управляющего частотой подстраиваемого генератора напряжения и синхронный режим работы устройства временно нарушается. В модуляторе заново начинается процесс синхронизации по фазе с опорным колебанием, что приводит к установлению изображающей точки на фазовом портрете устройства в положение, соответствующее соседней точке устойчивого равновесия, которая отстоит от исходной точки равновесия на π/2 либо на π радиан, в зависимости от комбинации установившихся на управляющих входах устройства сигналов. Этот процесс повторяется при каждой смене логического уровня на любом из управляющих входов модулятора. Таким образом осуществляется квадратурная фазовая манипуляция выходного колебания устройства.

В качестве недостатка схемы прототипа можно отметить неэффективное использование разрядности ЦАП. Младшие разряды ЦАП предназначены для установки дискретных (ненулевых) уровней манипулируемой фазы выходного колебания модулятора. При этом полосы захвата и удержания синхронного режима работы устройства определяются воздействием только старших разрядов ЦАП. Это ограничивает значения полос захвата и удержания синхронного режима работы устройства и снижает точность установа дискретов фазы в процессе модуляции выходного колебания.

Вторым существенным недостатком устройства является длительное время вхождения в синхронный режим работы при значительной начальной частотной расстройке, которое определяется фиксированной и ограниченной по значению сверху частотой следования счетных импульсов ЦАП.

Кроме того, у данного устройства точность и стабильность установа значений дискретов манипулируемой фазы снижается при наличии дестабилизирующих факторов, воздействующих на коэффициент петлевого усиления устройства, таких как паразитные изменения амплитуд колебаний опорного и подстраиваемого генераторов или изменение коэффициентов передач фазовых детекторов (ФД), что характерно при использовании устройства на повышенных рабочих частотах.

Предлагаемая схема квазикогерентного модулятора сигналов квадратурной фазовой манипуляции обладает следующими достоинствами:

- Все разряды ЦАП используются для синхронизации устройства по частоте. При этом минимальный дискрет напряжения с выхода ЦАП соответствует полному размаху напряжения сигнала с выхода ФД. Это обеспечивает расширение полос захвата и удержания синхронного режима работы устройства при заданной разрядности ЦАП.

- Скорость вхождения в синхронный режим работы зависит от текущего значения частоты биений на выходах ФД и соответственно тем выше, чем выше частотное рассогласование. Это обеспечивает минимальное и практически фиксированное значение времени вхождения в синхронный режим работы при любых значениях начальной частотной расстройки.

- Устройство защищено от воздействия дестабилизирующих факторов на коэффициент петлевого усиления, так как производится его установка и стабилизация с помощью блока установки и стабилизации петлевого усиления БУСПУ.

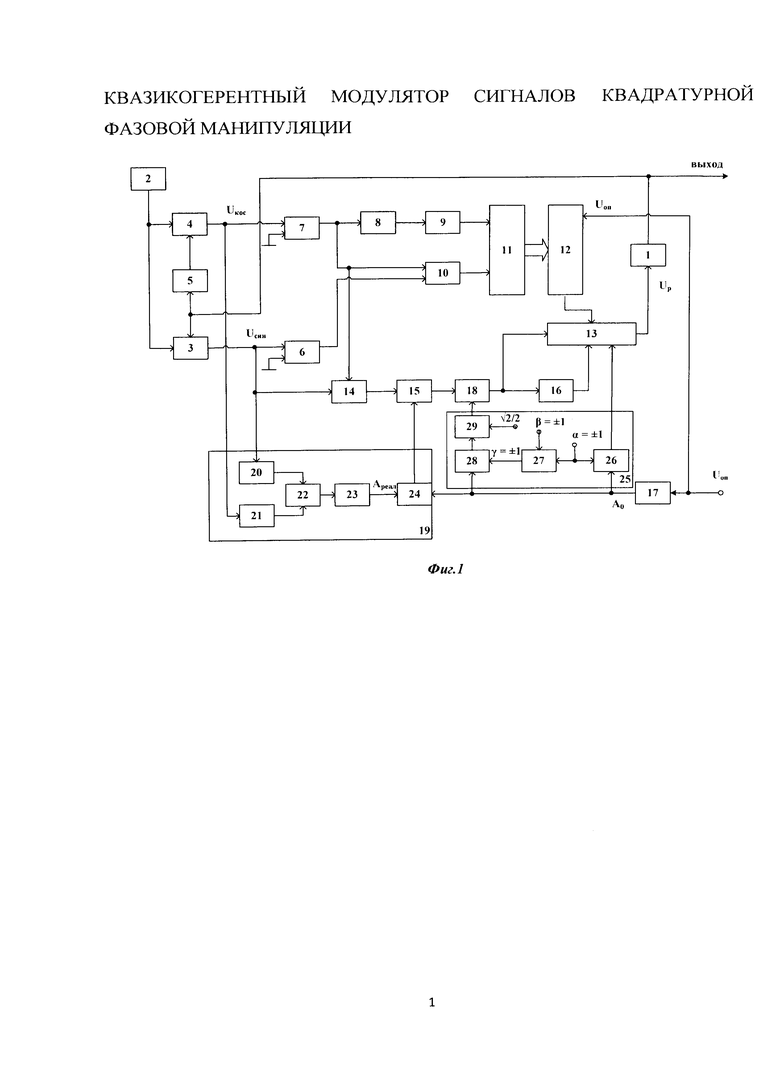

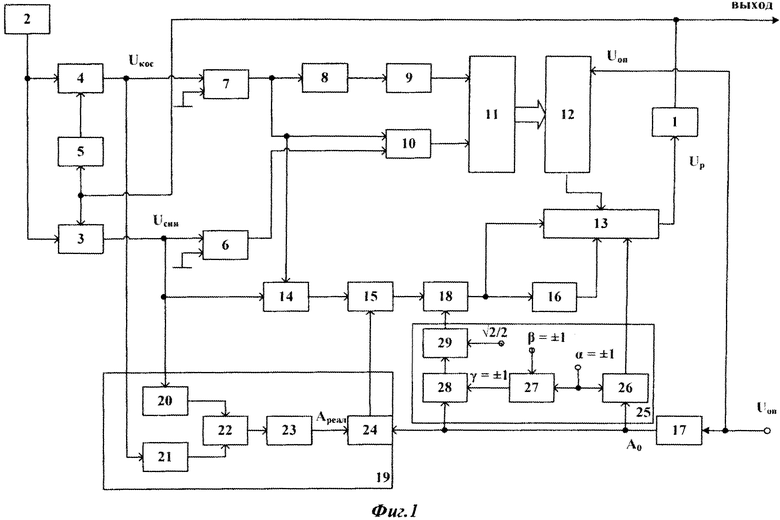

Квазикогерентный модулятор сигналов квадратурной фазовой манипуляции содержит подстраиваемый генератор 1, генератор эталонного колебания 2, первый и второй фазовые детекторы 3 и 4, фазовращатель 5 на π/2, первый и второй компараторы напряжений 6 и 7, формирователь импульсов 8, линию 9 временной задержки, логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10, реверсивный счетчик 11, цифроаналоговый преобразователь (ЦАП) 12, первый сумматор 13, коммутатор 14 полярности сигнала, первый перемножитель сигналов 15, интегратор 16, первый масштабирующий делитель напряжения 17, второй сумматор 18 и блок 19 установки и стабилизации петлевого усиления (БУСПУ), содержащий первый и второй блоки возведения текущего значения напряжения во вторую степень 20 и 21, третий сумматор 22, блок возведения текущего значения напряжения в ½ степень 23 и второй делитель напряжений 24, а также содержит блок 25 управления манипуляцией (БУМ), включающий в себя второй, третий, четвертый и пятый перемножители сигналов 26, 27, 28 и 29.

Устройство работает в двух режимах: режим первоначальной синхронизации и режим синхронной работы.

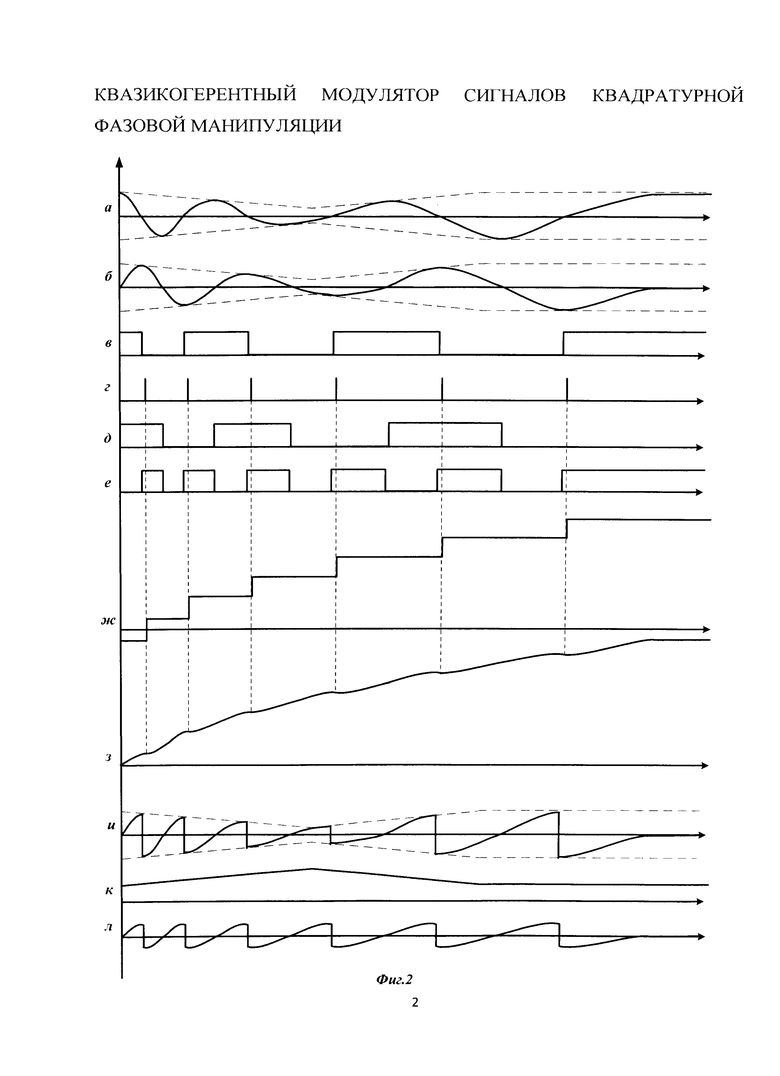

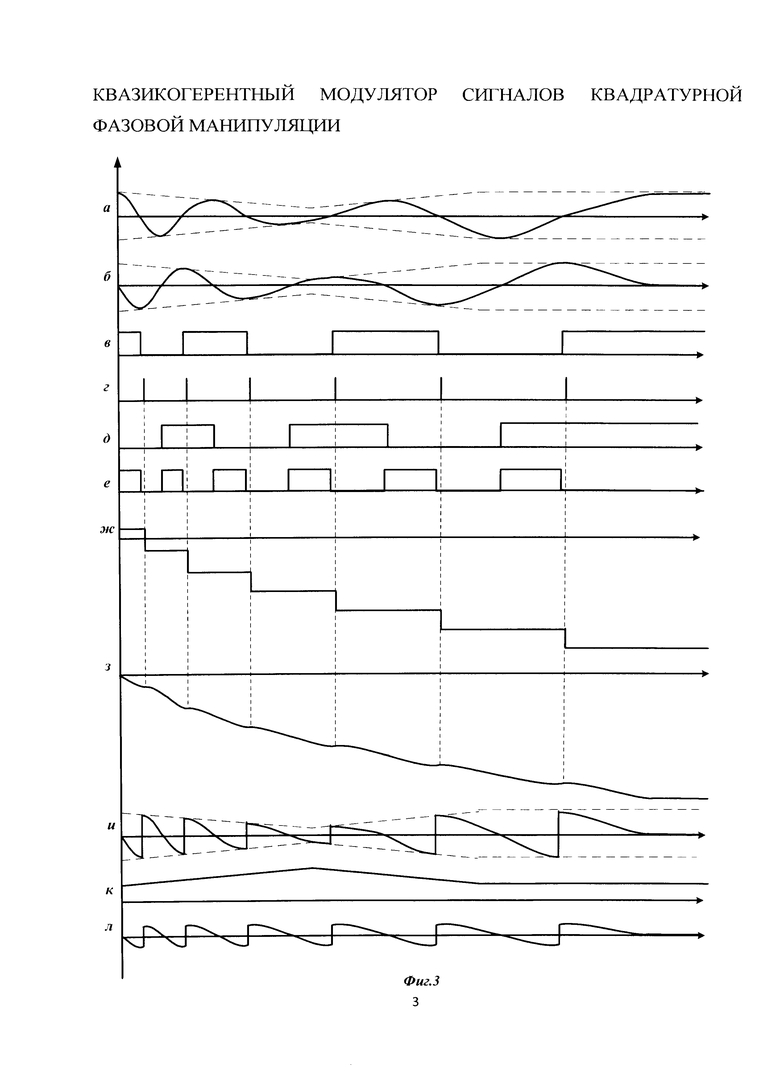

1. В режиме первоначальной синхронизации при включении устройства на выходах первого 3 и второго 4 фазовых детекторов возникают квадратурные составляющие биений с частотой, соответствующей начальной частотной расстройке Δω=ωЭ - ω0, где ωЭ - частота колебаний эталонного генератора 2 (ЭГ), ω0 - частота колебаний подстраиваемого генератора 1 при исходном значении управляющего напряжения Uр (р - регулирующее). На фиг. 2, 3 показаны эпюры напряжений в точках схемы устройства.

Выходной сигнал второго фазового детектора 4 показан на фиг. 2а, фиг. 3а, а выходной сигнал первого фазового детектора 3 на фиг. 2б, фиг. 3б для случаев ωЭ больше ω0 и ωЭ меньше ω0 соответственно. Первый 6 и второй 7 компараторы напряжений из выходных сигналов фазовых детекторов формируют логические сигналы, показанные на фиг. 2в, д и фиг. 3в, д. Фиг. 2в соответствует выходному сигналу второго компаратора 7, фиг. 2д - выходному сигналу первого компаратора 6 при ωЭ больше ω0; аналогично на фиг. 3в и фиг. 3д для выходных сигналов второго 7 и первого 6 компараторов при ωЭ меньше ω0. Формирователь импульсов 8 формирует короткие импульсы в моменты времени, соответствующие заднему фронту выходного импульсного сигнала второго компаратора 7. На фиг. 2г и фиг. 3г показаны эти импульсы, прошедшие через линию 9 временной задержки. Выходной сигнал логической схемы «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10 при ωЭ больше ω0 показан на фиг. 2е, а при ωЭ меньше ω0 - на фиг. 3е. Из эпюр фиг.2г, е и фиг. 3г, е следует, что код, записанный в реверсивном счетчике 11, и, следовательно, выходное напряжение ЦАП 12 возрастают при ωЭ больше ω0 и уменьшаются при ωЭ меньше ω0. Эпюры выходного напряжения ЦАП 12 показаны на фиг. 2ж (при ωЭ больше ω0) и 3ж (при ωЭ меньше ω0).

Таким образом, при появлении сигнала на входе системы выходное напряжение ЦАП 12 ступенчато нарастает (при ωЭ больше ω0) или ступенчато уменьшается (при ωЭ меньше ω0), в результате чего частота подстраиваемого генератора 1 изменяется в сторону уменьшения текущего частотного рассогласования Δω).

При снижении текущего частотного рассогласования Δω до величины, соответствующей полосе захвата аналоговой ветви управления частотой ПГ, включающей в себя первый фазовый детектор 3, коммутатор полярности сигнала 14, первый перемножитель сигналов 15, второй сумматор 18, интегратор 16 и первый сумматор 13 происходит установление синхронного режима работы модулятора.

Выходной сигнал коммутатора 14 полярности сигнала для случая ωЭ больше ω0 показан на фиг. 2л, а для случая ωЭ меньше ω0 показан на фиг. 3л.

Выходной сигнал первого сумматора 13 для случая ωЭ больше ω0 показан на фиг. 2з, а для случая ωЭ меньше ω0 показан на фиг. 3з.

Формирование счетных импульсов для реверсивного счетчика на основе колебаний разностной частоты с выхода фазовых детекторов внутри цифровой ветви управления частотой ПГ (включающей блоки 6, 7, 8, 9, 10, 11, 12 и 13) приводит к значительному сокращению времени вхождения в синхронный режим работы квазикогерентного модулятора. При этом использование всей разрядности реверсивного счетчика в процессе синхронизации устройства по частоте приводит к расширению полос захвата и удержания синхронного режима работы устройства.

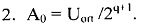

Для корректного функционирования устройства и повышения точности и стабильности установа дискретов манипулированной фазы выходного сигнала модулятора необходимо обеспечить согласование локальных дискриминационных характеристик цифровой и аналоговой ветвей управления частотой ПГ. Единичный дискрет ΔUЦАП формируемого на выходе ЦАП ступенчатого напряжения должен соответствовать полному размаху напряжения сигнала на выходе коммутатора полярности, равному 2A0. Для этой цели опорное напряжение Uоп цифроаналогового преобразователя используется для формирования единичных аналоговых ступеней напряжения с выхода ЦАП (ΔUЦАП=Uоп/2q, где q - разрядность ЦАП) и для вычисления в первом масштабирующем делителе напряжения 17 нормализованного (требуемого) значения амплитуды сигнала фазового рассогласования с выхода фазового детектора (A0=Uоп/2q+1). Далее с помощью блока установки и стабилизации петлевого усиления реально возникающее значение амплитуды сигнала фазового рассогласования приводится к нормализованному (требуемому) значению (A0=Uоп/2q+1).

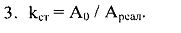

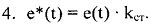

Установка и стабилизация требуемого коэффициента петлевого усиления аналоговой ветви управления осуществляется в текущем масштабе времени и происходит следующим образом. Квадратурные составляющие биений с частотой Δω с выходов первого и второго фазовых детекторов 3 и 4 подаются на входы первого и второго блоков возведения текущего значения напряжения во вторую степень 20 и 21 соответственно. На фиг. 2а, б и фиг. 3а, б соответственно для случаев ωЭ больше ω0 и ωЭ меньше ω0 показаны сигналы с выходов фазовых детекторов при изменяющихся амплитудах сигналов ЭГ и ПГ или изменяющихся коэффициентах передачи фазовых детекторов. Выходные сигналы блоков 20 и 21 подаются на первый и второй входы третьего сумматора 22. Сигнал с выхода третьего сумматора 22 поступает на вход блока возведения текущего значения напряжения в ½ степень 23, с выхода которого напряжение Aреал (реал - реальное) поступает на первый вход (вход знаменателя дроби деления) второго делителя напряжений 24. На второй вход (вход числителя дроби деления) второго делителя напряжений 24 поступает постоянное напряжение A0, уровень которого соответствует номинальному (требуемому) значению амплитуды выходных сигналов фазовых детекторов. Сигнал на выходе второго делителя напряжений 24 (показанный на фиг. 2к и фиг. 3к соответственно для случаев ωЭ больше ω0 и ωЭ меньше ω0) соответствует мгновенному текущему отклонению значения амплитуды выходных сигналов фазовых детекторов от номинального значения A0 и представляет собой корректирующий коэффициент, подаваемый на второй вход первого перемножителя 15. Выходной сигнал первого перемножителя 15 для случая ωЭ больше ω0 показан на фиг. 2л, а для случая ωЭ меньше ω0 показан на фиг. 3л.

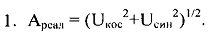

Если ввести обозначения: Uкос, Uсин - напряжение на выходе второго и первого фазовых детекторов соответственно (кос - косинусное, син - синусное), Ареал - мгновенное текущее значение амплитуды выходного сигнала первого фазового детектора, Uоп - опорное напряжение ЦАП, A0 - номинальное (требуемое) значение амплитуды с выхода первого фазового детектора, kст - коэффициент коррекции значения коэффициента петлевого усиления (ст - стабилизации), e(t) - напряжение на выходе коммутатора полярности 14, e*(t) - сигнал на выходе блока 15, то выполняемую в БУСПУ процедуру коррекции значения коэффициента петлевого усиления системы можно описать следующими соотношениями:

Вследствие изложенного реализуется сопряжение коэффициентов передачи аналоговой ветви управления частотой ПГ (ее локальная дискриминационная характеристика приведена на фиг. 2л, фиг. 3л) и цифровой ветви управления (ее локальная дискриминационная характеристика приведена на фиг. 2ж, фиг. 3ж). Это обеспечивает «сшивание» и «линеаризацию» (см. эпюры фиг. 2з, фиг. 3з) глобальной дискриминационной характеристики заявляемого устройства, что обеспечивает корректную работу модулятора в условиях наличия изменений и флуктуации амплитуд колебаний ЭГ и ПГ или при изменении коэффициентов передачи фазовых детекторов. При этом повышается точность и стабильность установа дискретов манипулируемой фазы при наличии дестабилизирующих факторов, воздействующих на коэффициент петлевого усиления устройства.

После завершения процесса синхронизации устройство переходит в режим синхронной работы.

2. В режиме синхронной работы устройства осуществляется процесс манипуляции фазы колебания подстраиваемого генератора на четыре положения - -π/4, π/4, 3π/4 и 5π/4 радиан в соответствии со значениями символов двух входных модулирующих последовательностей α=±1 и β=±1. Для достижения этой цели в первом сумматоре 13 предусмотрен четвертый вход, на который подается формируемая перемножителем 26 первая специальная подставка напряжения, абсолютной величиной равная A0 и манипулированная по полярности потоком символов модулирующей последовательности α=±1. Кроме того, в устройство введен второй сумматор 18, на второй вход которого подается формируемая перемножителями 28 и 29 вторая специальная подставка напряжения абсолютной величиной, равная (√2/2)A0 и манипулированная по полярности потоком символов формируемой в перемножителе 27 модулирующей последовательности γ=α·β=±1. Использование вспомогательной последовательности γ=α·β=±1 необходимо для обеспечения корректной работы модулятора на интервале значений фазовых рассогласований (π/2; 3π/2), на котором вследствие использования в структуре демодулятора коммутатора полярности происходит инверсия знака сигнала фазового рассогласования в ветви аналогового управления частотой подстраиваемого генератора.

Таким образом в блоке управления манипуляцией (БУМ) реализуются процедуры формирования абсолютных значений и манипуляции полярности двух специальных подставок напряжений управляющих дискретными положениями фазы выходного колебания модулятора. Процесс модуляции фазы выходного колебания в предложенном устройстве проиллюстрируем с привлечением его фазового портрета, приведенного на фиг. 4.

В данном устройстве точки устойчивого равновесия фазового портрета (соответствующие синхронному режиму работы) располагаются с периодом π. Это обусловлено использованием в аналоговой ветви управления частотой ПГ коммутатора полярности и наличием в схеме устройства интегратора. Фазовый портрет системы при положительной и отрицательной полярности первой специальной подставки напряжения показан соответственно на фиг. 4в и фиг. 4г. Фазовый портрет системы при устранении из структуры коммутатора полярности для случаев положительной и отрицательной полярности первой специальной подставки напряжения изображен на фиг. 4а и фиг. 4б соответственно. С помощью первой специальной подставки напряжения в качестве точек устойчивого равновесия системы устанавливаются точки, соответствующие фазовым рассогласованиям между колебанием ПГ и колебанием ЭГ величиной -45°, 135° (точки A1 и A1 * на фиг. 4в) либо 45°, 225° (точки A2 и A2 * на фиг. 4г).

В исходном состоянии при работе модулятора в синхронном режиме полярности символов входных модулирующих последовательностей положительны (α=1 и β=1), и соответственно первая и вторая специальные подставки напряжения также имеют положительную полярность. В качестве начального положения процесса манипуляции фазы выбирается точка устойчивого равновесия A1, соответствующая введенному ранее фазовому рассогласованию, равному минус 45°. Точка A1 фазового портрета устройства будет соответствовать опережению фазы колебания с выхода ПГ фазы колебания ЭГ на 45°.

Путем изменения знака первой специальной подставки напряжения, поступающей на четвертый вход первого сумматора, осуществляется манипуляция фазы выходного колебания устройства на π радиан. Она производится следующим образом: при изменении полярности символа модулирующей последовательности α на выходе первого сумматора возникает бросок управляющего частотой ПГ напряжения, вследствие чего устройство будет выбито из данной точки устойчивого равновесия (синхронный режим работы устройства временно нарушается). Далее квазикогерентный модулятор заново синхронизируется в следующей ближайшей точке устойчивого равновесия A1*, которая отстоит от исходной точки равновесия на π радиан.

Путем изменения полярности второй специальной подставки напряжения осуществляется манипуляция фазы выходного колебания устройства на π/2 радиан. При изменении полярности символа модулирующей последовательности β на выходе первого сумматора возникает бросок управляющего частотой ПГ напряжения, вследствие чего устройство также будет выбито из данной точки устойчивого равновесия. Поскольку изменилась полярность второй специальной подставки напряжения, на фазовом портрете устройства произойдет смена положения точек устойчивого равновесия, их местам размещения будут соответствовать положения точек A2 и A2* (произойдет смещение фазового портрета по оси ординат на величину √2A0). Вследствие этого квазикогерентный модулятор заново синхронизируется в ближайшей точке устойчивого равновесия A2, которая отстоит от исходной точки равновесия A1 на π/2 радиан.

Перестройка фазы выходного колебания устройства на 3π/2 происходит при одновременной смене полярности символов в обеих модулирующих последовательностях α=±1 и β=±1.

При манипулировании полярности второй специальной подставки напряжения происходит перестройка синхронного режима работы между точками устойчивого равновесия, которые соответствуют фазе выходного колебания модулятора -45° и 45° либо 135° и 225°. При манипулировании полярности первой специальной подставки напряжения происходит переход между точками устойчивого равновесия, которые соответствуют фазовым позициям модулятора -45° и 135° либо между 45° и 225°. Этот процесс многократно повторяется в соответствии с изменением полярности символов модулирующих последовательностей α=±1 и β=±1.

Таким образом, в предложенном устройстве осуществляется первоначальная синхронизация подстраиваемого генератора и квадратурная манипуляция фазы его колебания по значениям: -π/4, π/4, 3π/4 и 5π/4 радиан относительно фазы колебания эталонного генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| ГЛОБАЛЬНО ЛИНЕАРИЗОВАННАЯ СИСТЕМА СИНХРОНИЗАЦИИ | 2014 |

|

RU2554535C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2566813C1 |

| Модулятор сигналов фазовой телеграфии | 1986 |

|

SU1392628A1 |

| Модулятор сигналов двукратной фазовой телеграфии | 1986 |

|

SU1390811A1 |

| Демодулятор сигналов фазовой телеграфии | 1986 |

|

SU1392631A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ СИГНАЛОВ ПО СЕТИ ЭЛЕКТРОПИТАНИЯ | 2001 |

|

RU2178952C1 |

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

Изобретение относится к радиотехнике и может быть использовано в системах телекоммуникации и цифровой передачи данных в составе радиотехнических комплексов. Цель изобретения - комплексное (одновременное) улучшение основных параметров квазикогерентного модулятора, а именно: расширение полос захвата и удержания синхронного режима работы, сокращение времени вхождения в синхронный режим работы, повышение точности и стабильности установа дискретов манипулируемой фазы при наличии дестабилизирующих факторов, воздействующих на коэффициент петлевого усиления устройства. Устройство содержит подстраиваемый генератор 1, генератор эталонного колебания 2, первый и второй фазовые детекторы 3 и 4, фазовращатель 5 на π/2, первый и второй компараторы напряжений 6 и 7, формирователь импульсов 8, линию 9 временной задержки, логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10, реверсивный счетчик 11, цифроаналоговый преобразователь (ЦАП) 12, первый сумматор 13, коммутатор 14 полярности сигнала, первый перемножитель сигналов 15, интегратор 16, первый масштабирующий делитель напряжения 17, второй сумматор 18 и блок 19 установки и стабилизации петлевого усиления (БУСПУ), содержащий первый и второй блоки возведения текущего значения напряжения во вторую степень 20 и 21, третий сумматор 22, блок возведения текущего значения напряжения в ½ степень 23 и второй делитель напряжений 24, а также содержит блок 25 управления манипуляцией (БУМ), включающий в себя второй, третий, четвертый и пятый перемножители сигналов 26, 27, 28 и 29. 1 з.п. ф-лы, 4 ил.

1. Квазикогерентный модулятор сигналов квадратурной фазовой манипуляции, содержащий эталонный генератор, а также последовательно включенные реверсивный счетчик, цифроаналоговый преобразователь, первый сумматор, подстраиваемый генератор, выход которого также является выходом устройства, первый фазовый детектор, второй вход которого соединен с выходом эталонного генератора, и коммутатор полярности, а также последовательно включенные фазовращатель на π/2, вход которого соединен с выходом подстраиваемого генератора, и второй фазовый детектор, второй вход которого соединен с выходом эталонного генератора, отличающийся тем, что в устройство введены последовательно соединенные второй компаратор напряжений, первый вход которого подключен к выходу второго фазового детектора, а второй вход соединен с общей шиной, формирователь импульсов и линия временной задержки, выход которой соединен со счетным входом реверсивного счетчика, а также последовательно соединенные первый компаратор напряжений, первый вход которого подключен к выходу первого фазового детектора, а второй вход соединен с общей шиной, и логическая схема «ИСКЛЮЧАЮЩЕЕ ИЛИ», второй вход которой соединен с выходом второго компаратора напряжений, а выход подключен к управляющему входу реверсивного счетчика, а также введены последовательно включенные блок установки и стабилизации петлевого усиления (БУСПУ), первый перемножитель сигналов, второй вход которого соединен с выходом коммутатора полярности сигнала, второй сумматор, выход которого, кроме того, подключен ко второму входу первого сумматора, и интегратор, выход которого подключен к третьему входу первого сумматора, а также введены первый масштабирующий делитель напряжения, на вход которого подается опорное напряжение цифроаналогового преобразователя, и блок управления манипуляцией (БУМ), содержащий второй перемножитель сигналов, первый вход которого соединен с выходом первого масштабирующего делителя напряжения, и на второй вход которого поступает входная модулирующая последовательность α=±1, а выход соединен с четвертым входом первого сумматора, а также содержащий последовательно соединенные третий перемножитель сигналов, на входы которого поступают входные модулирующие последовательности α=±1 и β=±1, четвертый перемножитель сигналов, второй вход которого подключен к выходу первого масштабирующего делителя напряжения и пятый перемножитель сигналов, на второй вход которого поступает постоянное напряжение, соответствующее фазовому рассогласованию, равному π/4, и выход которого подключен ко второму входу второго сумматора.

2. Модулятор по п. 1, отличающийся тем, что блок установки и стабилизации петлевого усиления (БУСПУ) содержит последовательно включенные первый блок возведения текущего значения напряжения во вторую степень, вход которого соединен с выходом первого фазового детектора, третий сумматор, блок возведения текущего значения напряжения в ½ степень и соединенный по входу знаменателя дроби деления второй делитель напряжений, выход которого является выходом БУСПУ и второй вход которого, являющийся числителем дроби деления, подключен к выходу первого масштабирующего делителя напряжения, и, кроме того, содержит второй блок возведения текущего значения напряжения во вторую степень, вход которого соединен с выходом второго фазового детектор, а выход подключен ко второму входу третьего сумматора.

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

| Устройство дискретной задержки | 1984 |

|

SU1234956A1 |

| US 6909331 B2, 21.06.2005 | |||

| ШАХГИЛЬДЯН В.В | |||

| и др Системы фазовой автоподстройки частоты, Москва,"Связь", 1972, гл.1,3. | |||

Авторы

Даты

2016-04-20—Публикация

2014-10-10—Подача