Изобретение относится к радиотехнике и может быть использовано в системах телекоммуникации и цифровой передачи данных в составе радиотехнических комплексов.

Наиболее близким по технической сущности и достигаемому результату (прототипом) является демодулятор сигналов фазовой телеграфии (авторское свидетельство СССР SU 1392631 А1. «Демодулятор сигналов фазовой телеграфии». Московский авиационный институт им. Серго Орджоникидзе, В.Е. Мартиросов). Достоинства указанной схемы заключаются в повышенной помехоустойчивости при значительных скоростях передачи информации и больших диапазонах начальных частотных расстроек в условиях постоянного значения коэффициента петлевого усиления устройства, что достигается использованием специальной дополнительной цифровой ветви управления (блок 7 прототипа) частотой подстраиваемого генератора.

Устройство работает следующим образом.

При отсутствии входного сигнала демодулятора на вход блока поиска и фиксации фазового рассогласования (блок 7 прототипа) поступает нулевое напряжение, реверсивный счетчик включен на счет в одном направлении, и на выходе ЦАП формируется непрерывно повторяющееся линейно нарастающее напряжение, которое через сумматор модулирует частоту подстраиваемого генератора, осуществляя таким образом поиск входного сигнала демодулятора по частоте.

При появлении сигнала на входе демодулятора на выходе фазового детектора появляется напряжение биений с линейно изменяющейся частотой. Первый амплитудный компаратор (блок 2 прототипа) совместно с коммутатором полярности осуществляет выпрямление напряжений биений. При сближении частот входного и опорного колебаний биения прекращаются, на выходе фазового детектора и, соответственно, коммутатора полярности возникает изменяющееся по уровню постоянное напряжение. В момент превышения этого напряжения над опорным уровнем, задаваемым источником опорного напряжения (блок 9 прототипа), осуществляется останов однонаправленного счета реверсивного счетчика, прекращается режим поиска, и демодулятор переходит в режим синхронной работы.

В данном устройстве происходит фиксация фазового рассогласования колебаний на входах фазового детектора на уровне, соответствующем задаваемому напряжению с выхода источника опорного напряжения (блок 9 прототипа).

При манипуляции фазы на 180° входного сигнала демодулятора, находящегося в синхронном режиме работы, напряжение на выходе фазового детектора сохраняет свое значение, но изменяет свою полярность на противоположную, что приводит к изменению состояния логического выхода первого амплитудного компаратора (блок 2 прототипа). Сигнал на выходе коммутатора полярности остается неизменным за счет управляющегося воздействия с выхода первого амплитудного компаратора, т.е. таким образом, обеспечивается нечувствительность подстраиваемого генератора к информационной манипуляции фазы входного сигнала демодулятора.

В качестве недостатка схемы прототипа можно отметить неэффективное использование разрядности ЦАП. Младшие разряды ЦАП предназначены для установки дискретных (ненулевых) уровней фазы выходного колебания подстраиваемого генератора относительно фазы входного сигнала. При этом полосы захвата и удержания синхронного режима работы устройства определяются воздействием только старших разрядов ЦАП. Это ограничивает значения полос захвата и удержания синхронного режима работы устройства и снижает точность установа дискретов фазы при задании фиксированного фазового рассогласования в процессе демодуляции входного сигнала.

Вторым существенным недостатком устройства является длительное время вхождения в синхронный режим работы при значительной начальной частотной расстройке, которое определяется фиксированной и ограниченной по значению сверху частотой следования счетных импульсов ЦАП.

Кроме того, у данного устройства точность и стабильность установа значений дискретов фазы снижается при наличии дестабилизирующих факторов, воздействующих на коэффициент петлевого усиления устройства, таких как паразитные изменения амплитуд входного колебания и колебания с выхода подстраиваемого генератора или изменение коэффициентов передач фазовых детекторов (ФД), что характерно при использовании устройства на повышенных рабочих частотах.

Предлагаемая схема квазикогерентного демодулятора сигналов бинарной фазовой манипуляции обладает следующими достоинствами:

- все разряды ЦАП используются для синхронизации устройства по частоте. При этом минимальный дискрет напряжения с выхода ЦАП соответствует полному размаху напряжения сигнала с выхода ФД. Это обеспечивает расширение полос захвата и удержания синхронного режима работы устройства при заданной разрядности ЦАП;

- скорость вхождения в синхронный режим работы зависит от текущего значения частоты биений на выходах ФД и, соответственно, тем выше, чем больше частотное рассогласование. Это обеспечивает минимальное и практически фиксированное значение времени вхождения в синхронный режим работы при любых значениях начальной частотной расстройки;

- устройство защищено от воздействия дестабилизирующих факторов на коэффициент петлевого усиления, так как производится его установка и стабилизация с помощью блока установки и стабилизации петлевого усиления БУСПУ.

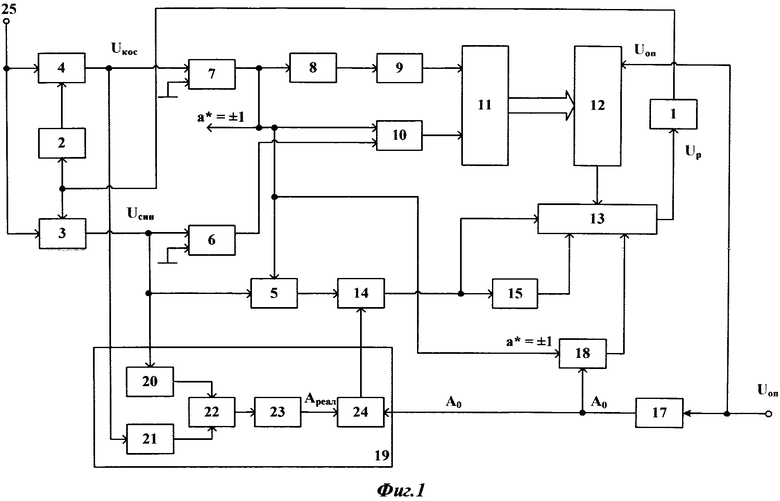

Квазикогерентный демодулятор сигналов бинарной фазовой манипуляции содержит подстраиваемый генератор 1, фазовращатель 2 на π/2, первый и второй фазовые детекторы 3 и 4, коммутатор 5 полярности сигнала, первый и второй компараторы напряжений 6 и 7, формирователь импульсов 8, линию 9 временной задержки, логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10, реверсивный счетчик 11, цифроаналоговый преобразователь (ЦАП) 12, первый сумматор 13, первый перемножитель сигналов 14, интегратор 15, первый масштабирующий делитель напряжения 17, второй перемножитель сигналов 18 и блок 19 установки и стабилизации петлевого усиления (БУСПУ), содержащий первый и второй блоки возведения текущего значения напряжения во вторую степень 20 и 21, второй сумматор 22, блок возведения текущего значения напряжения в

Устройство работает в двух режимах: режим первоначальной синхронизации и режим синхронной работы.

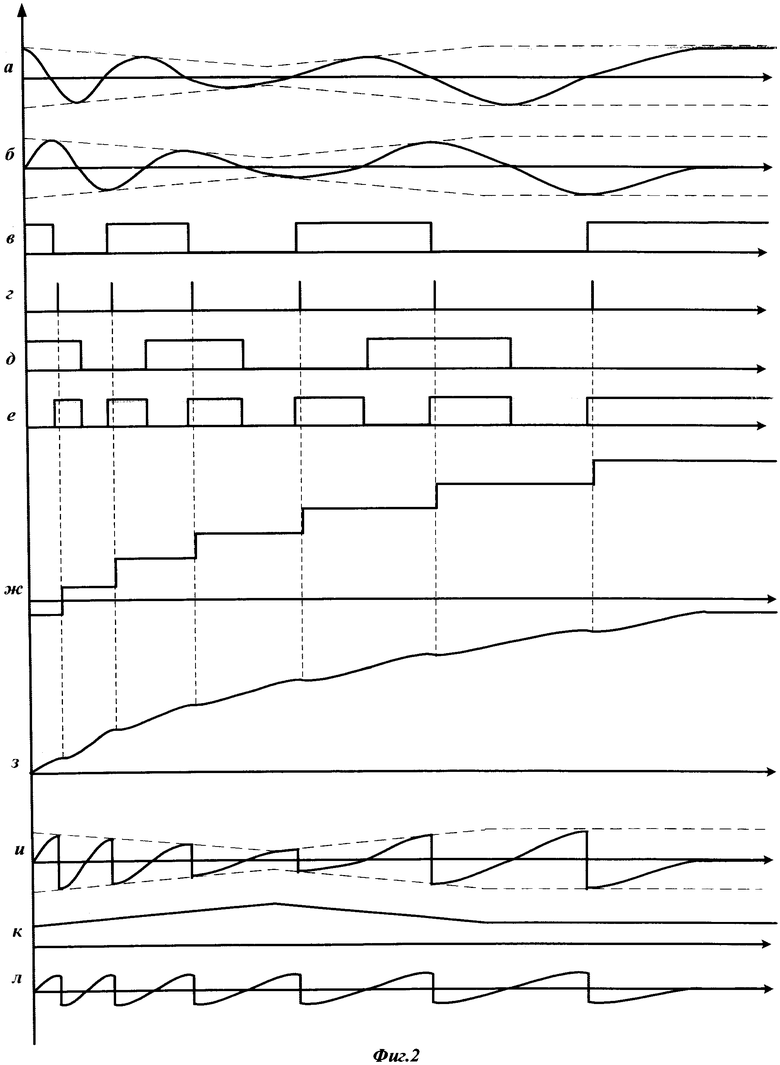

1. В режиме первоначальной синхронизации при включении устройства на выходах первого 3 и второго 4 фазовых детекторов возникают квадратурные составляющие биений с частотой, соответствующей начальной частотной расстройке Δω=ωс-ω0, где ωс - частота колебаний входного сигнала, ω0 - частота колебаний подстраиваемого генератора 1 при исходном значении управляющего напряжения Up (p - регулирующее). На фиг. 2, 3 показаны эпюры напряжений в точках схемы устройства.

Выходной сигнал второго фазового детектора 4 показан на фиг. 2,а, фиг. 3,а, а выходной сигнал первого фазового детектора 3 на фиг. 2,б, фиг. 3,б для случаев ωс больше ω0 и ωс меньше ω0 соответственно. Первый 6 и второй 7 компараторы напряжений (КН) из выходных сигналов фазовых детекторов формируют логические сигналы, показанные на фиг. 2,в, д и фиг. 3,в, д. Фиг. 2,в соответствует выходному сигналу второго компаратора 7, фиг. 2,д - выходному сигналу первого компаратора 6 при ωс больше ω0; аналогично на фиг. 3,в и фиг. 3,д для выходных сигналов второго 7 и первого 6 компараторов при ωс меньше ω0. Формирователь импульсов 8 формирует короткие импульсы в моменты времени, соответствующие заднему фронту выходного импульсного сигнала второго компаратора 7. На фиг. 2,г и фиг. 3,г показаны эти импульсы, прошедшие через линию 9 временной задержки. Выходной сигнал логической схемы «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10 при ωс больше ω0 показан на фиг. 2,е, а при ωс меньше ω0 - на фиг. 3,е. Из эпюр фиг. 2,г, е и фиг. 3,г, е следует, что код, записанный в реверсивном счетчике 11, и, следовательно, выходное напряжение ЦАП 12 возрастают при ωс больше ω0 и уменьшаются при ωс меньше ω0. Эпюры выходного напряжения ЦАП 12 показаны на фиг. 2,ж (при ωс больше ω0) и 3,ж (при ωс меньше ω0).

Таким образом, при появлении сигнала на входе системы выходное напряжение ЦАП 12 ступенчато нарастает (при ωс больше ω0) или ступенчато уменьшается (при ωс меньше ω0), в результате чего частота подстраиваемого генератора 1 изменяется в сторону уменьшения текущего частотного рассогласования Δω.

При снижении текущего частотного рассогласования Δω до величины, соответствующей полосе захвата аналоговой ветви управления частотой ПГ, включающей в себя первый фазовый детектор 3, коммутатор полярности сигнала 5, первый перемножитель сигналов 14, интегратор 15 и первый сумматор 13, происходит установление синхронного режима работы демодулятора.

Выходной сигнал коммутатора 5 полярности сигнала для случая ωс больше ω0 показан на фиг. 2,л, а для случая ωс меньше ω0 показан на фиг. 3,л.

Выходной сигнал первого сумматора 13 для случая ωс больше ω0 показан на фиг. 2,з, а для случая ωс меньше ω0 показан на фиг. 3,з.

Формирование счетных импульсов для реверсивного счетчика на основе колебаний разностной частоты с выхода фазовых детекторов внутри цифровой ветви управления частотой ПГ (включающей блоки 6, 7, 8, 9, 10, 11, 12 и 13) приводит к значительному сокращению времени вхождения в синхронный режим работы квазикогерентного демодулятора. При этом использование всей разрядности реверсивного счетчика в процессе синхронизации устройства по частоте приводит к расширению полос захвата и удержанию синхронного режима работы устройства.

Для корректного функционирования устройства и повышения точности и стабильности демодуляции входного сигнала демодулятором необходимо обеспечить согласование локальных дискриминационных характеристик цифровой и аналоговой ветвей управления частотой ПГ. Единичный дискрет ΔUЦАП, формируемого на выходе ЦАП ступенчатого напряжения, должен соответствовать полному размаху напряжения сигнала на выходе коммутатора полярности, равному 2А0. Для этой цели опорное напряжение Uoп цифроаналогового преобразователя используется для формирования единичных аналоговых ступеней напряжения с выхода ЦАП (ΔUЦАП=Uoп/2q, где q - разрядность ЦАП) и для вычисления в первом масштабирующем делителе напряжения 17 нормализованного (требуемого) значения амплитуды сигнала фазового рассогласования с выхода фазового детектора (A0=Uoп /2q+1). Далее с помощью блока установки и стабилизации петлевого усиления 19 реально возникающее значение амплитуды сигнала фазового рассогласования приводится к нормализованному (требуемому) значению (A0=Uoп/2q+1).

Установка и стабилизация требуемого коэффициента петлевого усиления аналоговой ветви управления осуществляется в текущем масштабе времени и происходит следующим образом.

Квадратурные составляющие биений с частотой Δω с выходов первого и второго фазовых детекторов 3 и 4 подаются на входы первого и второго блоков возведения текущего значения напряжения во вторую степень 20 и 21 соответственно. На фиг. 2,а, б и фиг. 3,а, б соответственно для случаев ωс больше ω0 и ωс меньше ω0 показаны сигналы с выходов фазовых детекторов при изменяющихся амплитудах сигналов на входе устройства и с выхода ПГ или изменяющихся коэффициентах передачи фазовых детекторов. Выходные сигналы блоков 20 и 21 подаются на первый и второй входы второго сумматора 22. Сигнал с выхода второго сумматора 22 поступает на вход блока возведения текущего значения напряжения в

Если ввести обозначения: Uкос, Uсин - напряжение на выходе второго и первого фазовых детекторов соответственно (кос - косинусное, син - синусное), Ареал - мгновенное текущее значение амплитуды выходного сигнала первого фазового детектора, Uoп - опорное напряжение ЦАП, А0 - номинальное (требуемое) значение амплитуды с выхода первого фазового детектора, kcт - коэффициент коррекции значения коэффициента петлевого усиления (ст - стабилизации), e(t) - амплитуда напряжения на выходе коммутатора полярности 5, e*(t) - сигнал на выходе блока 14, то выполняемую в БУСПУ процедуру коррекции значения коэффициента петлевого усиления системы можно описать следующими соотношениями:

1

2. А0=Uоп/2q+1

3. kст=А0/Ареал

4. e*(t)=e(t)·kст

Вследствие изложенного, реализуется сопряжение коэффициентов передачи аналоговой ветви управления частотой ПГ (ее локальная дискриминационная характеристика приведена на фиг. 2,л, фиг. 3,л) и цифровой ветви управления (ее локальная дискриминационная характеристика приведена на фиг. 2,ж, фиг. 3,ж). Это обеспечивает «сшивание» и «линеаризацию» (см. эпюры фиг. 2,з, фиг. 3,з) глобальной дискриминационной характеристики заявляемого устройства, что обеспечивает корректную работу демодулятора в условиях наличия изменений и флуктуации амплитуд колебаний входного сигнала и сигнала ПГ или при изменении коэффициентов передачи фазовых детекторов, то есть при наличии дестабилизирующих факторов, воздействующих на коэффициент петлевого усиления устройства.

После завершения процесса синхронизации устройство переходит в режим синхронной работы.

2. В режиме синхронной работы устройства осуществляется процесс демодуляции входного колебания, в результате которого получаются оценки α* значений символов переданной информационной последовательности α. Для устранения влияния манипуляции фазы входного сигнала на формируемое в демодуляторе опорное колебание подстраиваемого генератора в первом сумматоре 13 предусмотрен четвертый вход, на который подается специальная подставка напряжения, абсолютной величиной равная А0 и манипулированная по полярности во втором перемножителе 18 потоком демодулируемых оценок символов входного сигнала α*=±1.

В данном устройстве точки устойчивого равновесия фазового портрета (соответствующие синхронному режиму работы) располагаются с периодом π, как показано на фиг. 4,в. Такой вид фазового портрета обусловлен использованием в аналоговой ветви управления частотой ПГ коммутатора полярности и наличием в схеме устройства интегратора. Фазовый портрет при устранении из структуры коммутатора полярности показан на фиг. 4,а. На управляющий вход коммутатора полярности подается сигнал с выхода первого компаратора напряжения, показанный на фиг. 4,б (импульсный сигнал), где также показан сигнал с выхода второго ФД 4 (косину соидальный сигнал).

При включении устройства происходит первоначальная синхронизация демодулятора, по окончании которой колебание с выхода ПГ и входное колебание являются синфазными либо находятся в противофазе. Установившемуся положению соответствует одна из точек устойчивого равновесия А или А* на фазовом портрете устройства (см. фиг. 4,в). Допустим в результате синхронизации устройство оказалось в точке А (колебания синфазные). При манипуляции фазы на 180° входного сигнала демодулятора, находящегося в синхронном режиме работы, напряжение на выходе второго фазового детектора сохраняет свое значение, но изменяет свою полярность на противоположную, что приводит к изменению состояния логического выхода второго компаратора напряжений 7. Возникает бросок управляющего частотой ПГ напряжения, вследствие чего устройство будет выбито из точки устойчивого равновесия. Поскольку изменится полярность логического сигнала на выходе второго компаратора напряжения, изображающая точка С переместится на интервал фазового портрета, где ближайшей точкой устойчивого равновесия является А* (см. фиг. 4,в). То есть фаза сигнала с выхода ПГ меняется на 180°, подстраиваясь под изменение фазы во входном сигнале. Чтобы избежать пересинхронизации ПГ в положении со сдвигом фазы колебания в 180°, используется специальная подставка напряжения, подаваемая на четвертый вход первого сумматора, которая сдвигает изображающую точку системы обратно на интервал с ближайшей точкой устойчивого равновесия А. Данная подставка манипулируется по полярности сигналом с выхода второго компаратора напряжения, полярность сигнала на выходе которого будет меняться каждый раз при манипулировании фазы входного сигнала и оставаться постоянной на интервале передачи символа. Оценки переданных символов α*=±1 берутся с выхода второго компаратора напряжения.

Таким образом, осуществляется и сохраняется синхронизация подстраиваемого генератора квазикогерентного демодулятора бинарной фазовой манипуляции и демодуляция в нем входного сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| КВАЗИКОГЕРЕНТНЫЙ ДЕМОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2582331C1 |

| ГЛОБАЛЬНО ЛИНЕАРИЗОВАННАЯ СИСТЕМА СИНХРОНИЗАЦИИ | 2014 |

|

RU2554535C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2595629C1 |

| Демодулятор сигналов частотной телеграфии | 1986 |

|

SU1392627A1 |

| Демодулятор сигналов фазовой телеграфии | 1986 |

|

SU1392631A1 |

| Демодулятор сигналов частотной телеграфии | 1987 |

|

SU1497756A1 |

| Модулятор сигналов фазовой телеграфии | 1986 |

|

SU1392628A1 |

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

Изобретение относится к радиотехнике и может быть использовано в системах телекоммуникации и цифровой передачи данных в составе радиотехнических комплексов. Технический результат - комплексное улучшение основных параметров квазикогерентного модулятора, а именно: расширение полос захвата и удержание синхронного режима работы, сокращение времени вхождения в синхронный режим работы, повышение точности и стабильности установа дискретов манипулируемой фазы при наличии дестабилизирующих факторов, воздействующих на коэффициент петлевого усиления устройства. Устройство содержит подстраиваемый генератор 1, генератор эталонного колебания 2, первый и второй фазовые детекторы 3 и 4, фазовращатель 5 на π/2, первый и второй компараторы напряжений 6 и 7, формирователь импульсов 8, линию 9 временной задержки, логическую схему «ИСКЛЮЧАЮЩЕЕ ИЛИ» 10, реверсивный счетчик 11, цифро-аналоговый преобразователь (ЦАГТ) 12, первый сумматор 13, коммутатор 14 полярности сигнала, первый перемножитель сигналов 15, интегратор 16, первый масштабирующий делитель напряжения 17, второй сумматор 18 и блок 19 установки и стабилизации петлевого усиления (БУСПУ), содержащий первый и второй блоки возведения текущего значения напряжения во вторую степень 20 и 21, третий сумматор 22, блок возведения текущего значения напряжения в

1. Квазикогерентный демодулятор сигналов бинарной фазовой манипуляции, содержащий последовательно включенные реверсивный счетчик, цифроаналоговый преобразователь, первый сумматор, подстраиваемый генератор, первый фазовый детектор, второй вход которого соединен с входом демодулятора, и коммутатор полярности сигнала, отличающийся тем, что с целью комплексного (одновременного) улучшения основных параметров квазикогерентного демодулятора, а именно: расширения полос захвата и удержания синхронного режима работы, сокращения времени вхождения в синхронный режим работы, повышения помехоустойчивости при наличии дестабилизирующих факторов, воздействующих на коэффициент петлевого усиления устройства, в устройство введены последовательно соединенные фазовращатель на π/2, вход которого соединен с выходом подстраиваемого генератора, второй фазовый детектор, второй вход которого соединен с входом демодулятора, второй компаратор напряжений, второй вход которого соединен с общей шиной, формирователь импульсов и линия временной задержки, выход которой соединен со счетным входом реверсивного счетчика, а также введены последовательно включенные первый компаратор напряжений, первый вход которого соединен с выходом первого фазового детектора, а второй вход подключен к общей шине, и логическая схема «ИСКЛЮЧАЮЩЕЕ ИЛИ», второй вход которой соединен с выходом второго компаратора напряжений, а выход подключен к управляющему полярностью счета входу реверсивного счетчика, а также введены последовательно включенные блок установки и стабилизации петлевого усиления (БУСПУ), первый перемножитель сигналов, второй вход которого подключен к выходу коммутатора полярности сигнала, а выход дополнительно соединен со вторым входом первого сумматора, и интегратор, выход которого подключен к третьему входу первого сумматора, а также введены последовательно соединенные первый масштабирующий делитель напряжения, на вход которого подается опорное напряжение цифроаналогового преобразователя, и второй перемножитель сигналов, выход которого подключен к четвертому входу первого сумматора и второй вход которого подключен к выходу второго компаратора напряжения.

2. Демодулятор по п. 1, отличающийся тем, что блок установки и стабилизации петлевого усиления (БУСПУ) содержит последовательно включенные первый блок возведения текущего значения напряжения во вторую степень, вход которого соединен с выходом первого фазового детектора, второй сумматор, блок возведения текущего значения напряжения в

| Устройство фазовой автоподстройки частоты | 1988 |

|

SU1663768A1 |

| Устройство дискретной задержки | 1984 |

|

SU1234956A1 |

| US 6909331 B2, 21.06.2005 | |||

Авторы

Даты

2015-10-27—Публикация

2014-10-10—Подача