Изобретение относится к способам цифроаналогового преобразования и может быть использовано в устройствах преобразования цифрового кода в аналоговое напряжение.

Известны типы цифроаналоговых преобразователей (ЦАП) [Федорков Б.Г., Телец В.А. Микросхемы ЦАП и АЦП: функционирование, параметры, применение. - М.: Энергоатомиздат, 1990. - 320 с.], построенные как на резистивных матрицах различного типа, так и на основе преобразования частоты в напряжение, которые используют для регулирования уровня выходного напряжения цифроаналогового преобразователя.

К недостаткам известных ЦАП можно отнести технологическую сложность и дороговизну изготовления прецизионных резистивных матриц, а второго типа ЦАП - недостаточную точность и линейность характеристики преобразования. Известно, что прецизионные резистивные матрицы можно изготовить только по тонкопленочной технологии, включающей функциональную подгонку сопротивлений резисторов, а не по полупроводниковой, что и определяет указанные недостатки.

Наиболее близким по технической сущности является способ цифроаналогового преобразования, который реализован в ЦИФРОАНАЛОГОВОМ ПРЕОБРАЗОВАТЕЛЕ [патент РФ на полезную модель №146932], содержащем две N-разрядные резистивные R-2R матрицы, к входам которых подключены контакты опорного напряжения, выходные контакты резистивных матриц с напряжениями, соответствующими значениям разрядов N-разрядного цифрового кода, подключены к соответствующим контактам N-разрядных регистров, при этом для цифроаналогового преобразования N-разрядного цифрового кода суммируют напряжение выходных контактов резистивных матриц, порядковые номера которых соответствуют единичным значениям преобразуемого цифрового кода.

Недостатком прототипа является невысокая точность цифроаналогового преобразования, которая обусловлена большим количеством слагаемых опорных напряжений, а также большим диапазоном их значений.

Технический результат изобретения заключается в повышении точности цифроаналогового преобразования, в уменьшении количества слагаемых опорных напряжений, в уменьшении диапазона значений опорных напряжений.

Технический результат достигается за счет того, что заявлен способ цифроаналогового преобразования, при котором задают значения напряжений контактам опорного напряжения, которые в зависимости от значений разрядов цифрового кода XL…X1 суммируют, отличающийся тем, что характеризуется использованием K коммутаторов с DKN…DK1 информационными входами и AKM…ΑK1 адресными входами, 2M-1 контактов с опорными напряжениями, а также K-1 усилителей и сумматора напряжений, при котором для цифроаналогового преобразования цифрового кода XL…X1 задают 2М-1 опорных напряжений, соответствующих комбинациям старших разрядов XL…XL-M+1 цифрового кода XL…X1, при которых остальные разряды XL-M…X1 равны «0», после чего контакты опорных напряжений последовательно подключают к информационным входам DKN…DK2 коммутаторов таким образом, что контакт с наибольшим напряжением подключают к старшим информационным входам DKN коммутаторов, выходы коммутаторов K-1, …, 1 соединяют с усилителями, которым задают соответствующие коэффициенты передачи 1/2М, 1/22М, …, 1/2M(K-1), при этом выход первого коммутатора, а также выходы усилителей соединяют с сумматором напряжений, после этого разделяют входную шину FL…F1 на K групп контактов FKL…FKL-M+1, FK-1L-M…FK-1L-2M+1, …, F1M…F11, которые последовательно подключают к адресным входам коммутаторов K, K-1, …, 1 таким образом, что контакт старшего разряда цифрового кода группы подключают к старшему адресному входу соответствующего коммутатора, после этого на контакты входной шины FL…F1 подают напряжения, соответствующие значениям разрядов цифрового кода XL…X1, при этом на адресные входы коммутаторов поступают комбинации XKL…XKL-M+1, XK-1L-M…XK-1L-2M+1, …, Χ1Μ…Χ11 групп разрядов цифрового кода, которые подключают к выходам коммутаторов соответствующие их значениям входы, после этого напряжение с выхода старшего коммутатора подают на сумматор напряжений, а напряжения с других коммутаторов K-1, …, 1 подают на усилители, которые в соответствии с коэффициентами передачи изменяют значения напряжений, после этого суммируют напряжение со старшего коммутатора и напряжения с усилителей, при этом на выходе сумматора образуется напряжение, значение которого соответствует значению цифрового кода XL…X1.

В частности, если общее количество адресных входов коммутаторов M⋅K больше количества контактов входной шины L, тогда младшему усилителю задают коэффициент усиления 1/(2M(K-1)+M⋅K-L).

Способ может быть реализован, например, с использованием цифроаналогового преобразователя, содержащего контакты опорных напряжений и контакты входной шины. Цифроаналоговый преобразователь содержит K коммутаторов с DKN…DK1 информационными входами и ΑKΜ…ΑΚ1 адресными входами, K-1 усилителей, сумматор напряжений, а также 2М-1 контактов с опорными напряжениями, которые подключены к источникам тока, напряжения которых соответствуют комбинациям старших разрядов XL…XL-M+1 цифрового кода цифрового кода XL…X1, при которых остальные разряды XL-M…X1 равны «0», контакты с опорными напряжениями подключены к информационным входам DKN…DK2 коммутаторов K, K-1, …, 1 таким образом, что контакт с наибольшим напряжением, подключен к старшим информационным входам DKN коммутаторов, контакты входной шины FL…F1 последовательно подключены к адресным входам коммутаторов ΑΚM…ΑΚ1, ΑK-1M…ΑK-11, …, A1M…A11, выход старшего коммутатора соединен с сумматором напряжений, при этом выходы остальных коммутаторов K-1, K-2, …, 1 подключены к усилителям с коэффициентами передачи 1/2М, 1/22М, …, 1/2M(K-1), выходы усилителей соединены с входами сумматора напряжений, выход которого является выходом цифроаналогового преобразователя.

Краткое описание чертежей

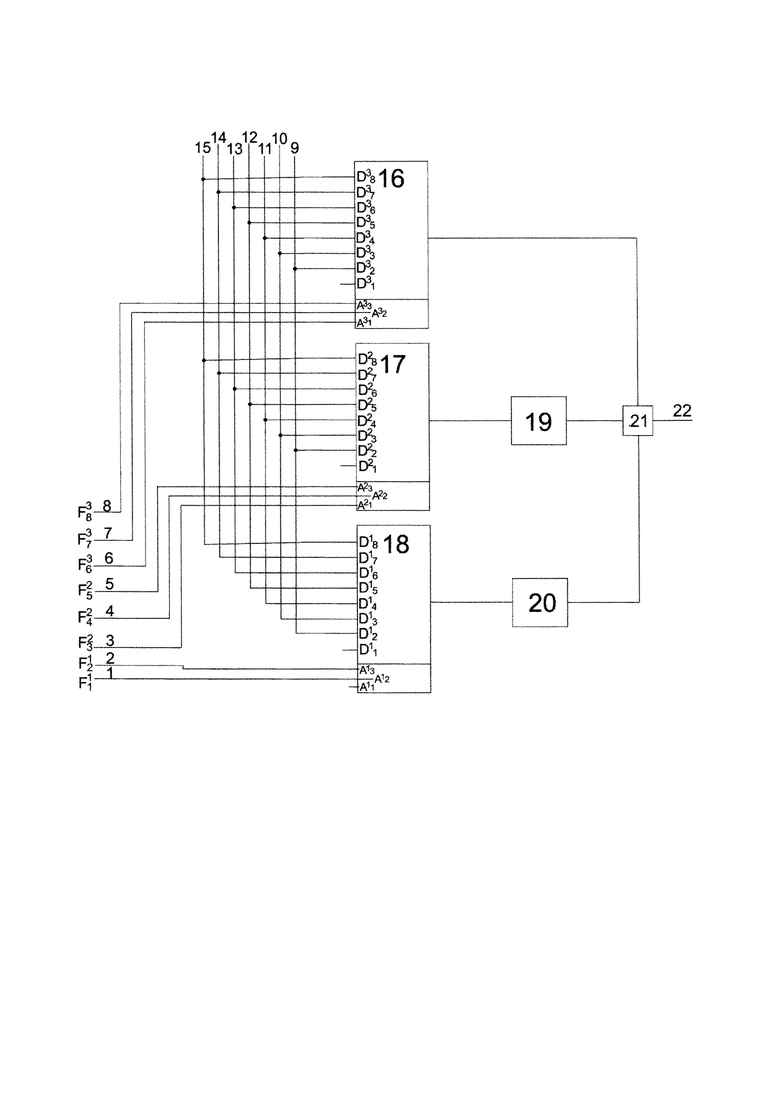

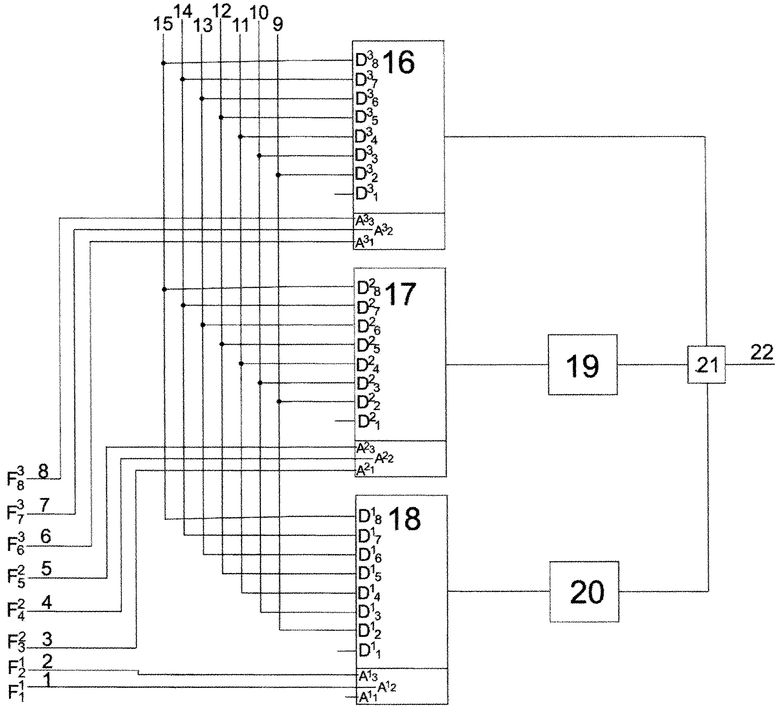

На чертеже представлено схематичное изображение варианта реализации 8-разрядного цифроаналогового преобразователя, на которой изображено: 1-8 - контакты входной шины, 9-15 - контакты с опорными напряжениями, 16-18 - коммутаторы, 19 и 20 - усилители, 21 - сумматор напряжений, 22 - выходной контакт цифроаналогового преобразователя.

Осуществление изобретения

Способ может быть реализован, например, с использованием цифроаналогового преобразователя, содержащего (см. чертеж) группу из трех коммутаторов 16, 17 и 18, имеющих сквозную нумерацию элементов цифроаналогового преобразователя. Контакты с опорными напряжениями 15, 14, …, 9 подключены к соответствующим информационным входам D38…D32, D28…D22, D18…D12 коммутаторов 16, 17 и 18. Верхний индекс наименования информационного контакта показывает порядковый номер коммутатора в группе, а нижний индекс показывает порядковый номер входного информационного контакта.

Контакты входной шины 8, 7, …, 1 разделены по числу коммутаторов на 3 подгруппы F38…F36, F25…F23, F12-F11 и подключены к соответствующим адресным входам А33…А31, Α23…Α221, А13-А12 коммутаторов 16, 17 и 18.

Коммутатор 16 подключен к сумматору напряжений 21. Коммутаторы 17 и 18 подключены к усилителям 19 и 20, которые также подключены к сумматору напряжения 21, выход которого 22 является выходом цифроаналогового преобразователя.

Усилителю 19 задан коэффициент передачи 1/23, где 3 - количество адресных входов коммутаторов.

Усилителю 20 задан коэффициент передачи 1/23⋅2+1=1/27, где 3 - количество адресных входов коммутаторов, 2 - групповой порядковый номер коммутатора 18, подключенного к указанному усилителю, уменьшенный на единицу, 1 - разница между общим количеством адресных входов коммутаторов 9 и количеством контактов входной шины 8.

Цифроаналоговый преобразователь работает следующим образом.

Первоначально для цифроаналогового преобразования, например, 8-разрядного цифрового кода задают опорные напряжения на контактах 15, 14, …, 9 таким образом, что напряжения контактов соответствуют следующим значениям 8-разрядного цифрового кода: [11100000], [11000000], [10100000], [10000000], [1100000], [1000000] и [100000], т.е. опорные напряжения соответствуют всем комбинациям первых 3 разрядов 8-разрядного цифрового кода, 3 выбрано по числу адресных входов коммутаторов.

После этого на контакты входной шины 8, 7, …, 1 подают напряжения, которые соответствуют значениям цифрового кода, например [10111010], при этом на адресные входы коммутаторов 16, 17 и 18 поступают следующие комбинации цифрового кода: на адресные входы Α33…Α31 коммутатора 16 - [101], на адресные входы Α23…Α21 коммутатора 17 - [110], на адресные входы А13 и А12 коммутатора 18 - [10], при этом указанные комбинации подключают: к выходу коммутатора 16 - вход D36, к выходу коммутатора 17 - вход D27, к выходу коммутатора 18 - вход D15.

При этом на сумматор 21 с коммутатора 16 поступает опорное напряжение, соответствующее цифровому коду [10100000].

С коммутатора 17 опорное напряжение, соответствующее цифровому коду [11000000], поступает на усилитель 19 с коэффициентом передачи 1/23, при этом напряжение на его выходе будет соответствовать значению цифрового кода [11000].

Коэффициент передачи усилителя 19 - 1/23 означает, что выходное напряжение усилителя 19 будет уменьшено в 8 раз в сравнении с входным или для аналогии с напряжениями, соответствующими какому-либо цифровому коду, например [11000000], означает сдвиг цифрового кода вправо на 3 разряда.

С коммутатора 18 опорное напряжение, соответствующее цифровому коду [10000000], поступает на усилитель 20 с коэффициентом передачи 1/27, при этом напряжение на его выходе будет соответствовать значению цифрового кода [10].

Сумматор 21 интегрирует аналоговое напряжение с выхода коммутатора 16, которое соответствует цифровому коду [10100000], а также аналоговое напряжение с выхода усилителя 19, которое соответствует значению цифрового кода [11000], и аналоговое напряжение с выхода усилителя 20, которое соответствует значению цифрового кода [01].

После суммирования аналоговое напряжение на выходе 22 соответствует значению цифрового кода [10111010].

При подаче других комбинаций цифрового кода на вход цифроаналогового преобразователя он будет работать аналогичным образом.

Технический результат изобретения - уменьшение диапазона используемых значений опорных напряжений и уменьшение количества слагаемых опорных напряжений - достигается за счет того, что задают 7 опорных напряжений, соответствующих комбинациям старших разрядов Х8, Х7, Х6 цифрового кода Х8, Х7, …, Χ1, при которых остальные его разряды Х5, Х4, …, Χ1 равны «0», после чего контакты опорных напряжений 15, 14, …, 9 последовательно подключают к информационным входам D38, D37, …, D32 коммутаторов 16, 17 и 18, при этом выходы коммутаторов 17 и 18 соединяют с усилителями 19 и 20, которым задают коэффициенты передачи 1/23 и 1/27, при этом выход первого коммутатора 16, а также выходы усилителей 19 и 20 соединяют с сумматором напряжений 21, после этого разделяют входную шину F8…F1 на K групп контактов F38…F36, F25…F23, F12…F11, которые последовательно подключают к адресным входам коммутаторов 16, 17 и 18 таким образом, что контакт старшего разряда цифрового кода группы подключают к старшему адресному входу соответствующего коммутатора.

Поясним достижение указанного выше технического результата на примере цифроаналогового преобразования кода [11111111] прототипом и заявленным решением.

Для преобразования указанного цифрового кода прототипом необходимо задание 8 опорных напряжений, соответствующих следующим значениям цифровых кодов [10000000], [1000000], [100000], [10000], [1000], [100], [10], [1], при этом значение самого большого напряжения в 128 раз больше значения меньшего напряжения. После задания указанных напряжений для получения выходного значения необходимо сложить все 8 опорных напряжений.

Для преобразования указанного цифрового кода заявленным техническим решением необходимо задание 7 опорных напряжений, соответствующих следующим значениям цифрового кода [11100000], [11000000], [10100000], [10000000], [1100000], [1000000], [100000], при этом значение самого большого напряжения всего в 7 раз больше значения меньшего напряжения. После задания указанных напряжений для получения выходного значения необходимо сложить всего 3 опорных напряжения.

Технический результат изобретения - повышение точности цифроаналогового преобразования - достигается за счет того, что при реализации заявленного технического решения значительно уменьшается динамический диапазон используемых опорных напряжений, а также уменьшается количество слагаемых опорных напряжений для получения напряжения, соответствующего значению входного цифрового кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Скважинный инклинометр | 1990 |

|

SU1721225A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство аналого-цифрового преобразования | 1984 |

|

SU1295514A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2399156C1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| ИМИТАТОР РЕАЛИЗАЦИИ СЛУЧАЙНЫХ ИЗМЕНЕНИЙ ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1995 |

|

RU2099863C1 |

| Устройство для измерения спектральной плотности мощности шумов аналого-цифровых преобразователей | 1987 |

|

SU1531218A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

Изобретение относится к области цифроаналогового преобразования и может быть использовано в устройствах преобразования цифрового кода в аналоговое напряжение. Техническим результатом является повышение точности цифроаналогового преобразования, уменьшение количества слагаемых опорных напряжений, уменьшение диапазона значений опорных напряжений. Способ достигается за счет того, что используют K коммутаторов с DKN…DK1 информационными входами и ΑKΜ…ΑΚ1 адресными входами, 2M-1 контактов с опорными напряжениями, а также K-1 усилителей и сумматор напряжений, при котором для цифроаналогового преобразования цифрового кода XL…X1 задают 2М-1 опорных напряжений, соответствующих комбинациям старших разрядов XL…XL-M+1 цифрового кода XL…X1, при которых остальные разряды XL-M…X1 равны «0», после чего контакты опорных напряжений последовательно подключают к информационным входам DKN…DK2 коммутаторов таким образом, что контакт с наибольшим напряжением подключают к старшим информационным входам DKN коммутаторов, выходы коммутаторов K-1, …, 1 соединяют с усилителями, которым задают соответствующие коэффициенты передачи 1/2М, 1/22М, …, 1/2М(K-1), при этом выход первого коммутатора, а также выходы усилителей соединяют с сумматором напряжений, после этого разделяют входную шину FL…F1 на K групп контактов FKL…FKL-M+1, FK-1L-M…FK-1L-2M+1, …, F1M…F11, которые последовательно подключают к адресным входам коммутаторов K, K-1, …, 1 таким образом, что контакт старшего разряда цифрового кода группы подключают к старшему адресному входу соответствующего коммутатора. 1 з.п. ф-лы, 1 ил.

1. Способ цифроаналогового преобразования, при котором задают значения напряжений контактам опорного напряжения, которые в зависимости от значений разрядов цифрового кода XL…X1 суммируют, отличающийся тем, что характеризуется использованием K коммутаторов с DKN…DK1 информационными входами и AKM…AK1 адресными входами, 2M-1 контактов с опорными напряжениями, а также K-1 усилителей и сумматора напряжений, при котором для цифроаналогового преобразования цифрового кода XL…X1 задают 2M-1 опорных напряжений, соответствующих комбинациям старших разрядов XL…XL-M+1 цифрового кода XL…X1, при которых остальные разряды XL-M…X1 равны «0», после чего контакты опорных напряжений последовательно подключают к информационным входам DKN…DK2 коммутаторов таким образом, что контакт с наибольшим напряжением подключают к старшим информационным входам DKN коммутаторов, выходы коммутаторов K-1, …, 1 соединяют с усилителями, которым задают соответствующие коэффициенты передачи 1/2M, 1/22M, …, 1/2M(K-1), при этом выход первого коммутатора, а также выходы усилителей соединяют с сумматором напряжений, после этого разделяют входную шину FL…F1 на K групп контактов FKL…FKL-M+1, FK-1L-M…FK-1L-2M+1, …, F1M…F11, которые последовательно подключают к адресным входам коммутаторов K, K-1, …, 1 таким образом, что контакт старшего разряда цифрового кода группы подключают к старшему адресному входу соответствующего коммутатора, после этого на контакты входной шины FL…F1 подают напряжения, соответствующие значениям разрядов цифрового кода XL…X1, при этом на адресные входы коммутаторов поступают комбинации XKL…XKL-M+1, XK-1L-M…XK-1L-2M+1, …, X1M…X11 групп разрядов цифрового кода, которые подключают к выходам коммутаторов соответствующие их значениям входы, после этого напряжение с выхода старшего коммутатора подают на сумматор напряжений, а напряжения с других коммутаторов K-1, …, 1 подают на усилители, которые в соответствии с коэффициентами передачи изменяют значения напряжений, после этого суммируют напряжение со старшего коммутатора и напряжения с усилителей, при этом на выходе сумматора образуется напряжение, значение которого соответствует значению цифрового кода XL…X1.

2. Способ по п. 1, отличающийся тем, что если общее количество адресных входов коммутаторов М⋅K больше количества контактов входной шины L, тогда младшему усилителю задают коэффициент усиления 1/(2M(K-1)+M⋅K-L).

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ЭЛЕКТРИЧЕСКИМ ГРЕЙФЕРНЫМ КРАНОМ ТРЕХФАЗНОГО ТОКА | 1960 |

|

SU146932A1 |

| Цифроаналоговый преобразователь с коммутацией тока | 1982 |

|

SU1084983A1 |

| US 2002125928 A1, 12.09.2002 | |||

| US 2006066463 A1, 30.03.2006 | |||

| US 5889484 A, 30.03.1999. | |||

Авторы

Даты

2017-06-16—Публикация

2015-12-24—Подача