сд

UD

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| Устройство для сопряжения ЦВМ с группой абонентов | 1988 |

|

SU1559349A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1983 |

|

SU1140125A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| Устройство для сопряжения | 1983 |

|

SU1129603A1 |

Изобретение относится к области вычислительной техники и может быть пьзовано в сетевых системах со пряжения абонентов кольцевой структуры. Целью изобретения является расширение области применения за счет организации буферизации данных, преобразования и контроля данных. Устройство содержит приемник 1, передатчик 2, элемент И 3, элемент ИЛИ А, счетчик 5,. первый 6, второй 7 и тре- ТИЙ.8 триггеры, блок 9 синхронизации, блок 10 памяти, блок 11 дешифраторов, четвертый триггер 12, первый 13, второй 14, третий 15 и четвертый 16 сдвиговые регистры, блок 17 удаления бит-стаффинга и блок 18 контроля. Устройство осуществляет сопряжение абонентов кольцевой сети по бит-Ориентированному протоколу синхронной связи. 2 . ф-лы, 7 ил. (Л

л л1онеиту .t

Изобретение относится к вьмисли- тельной технике и может быть использовано в сетевых системах сопряжения абонентов кольцевой структуры.

Цель изобретения расширение об лаСти применения за счет организации буферизации данных,, преобразования и контроля данных,

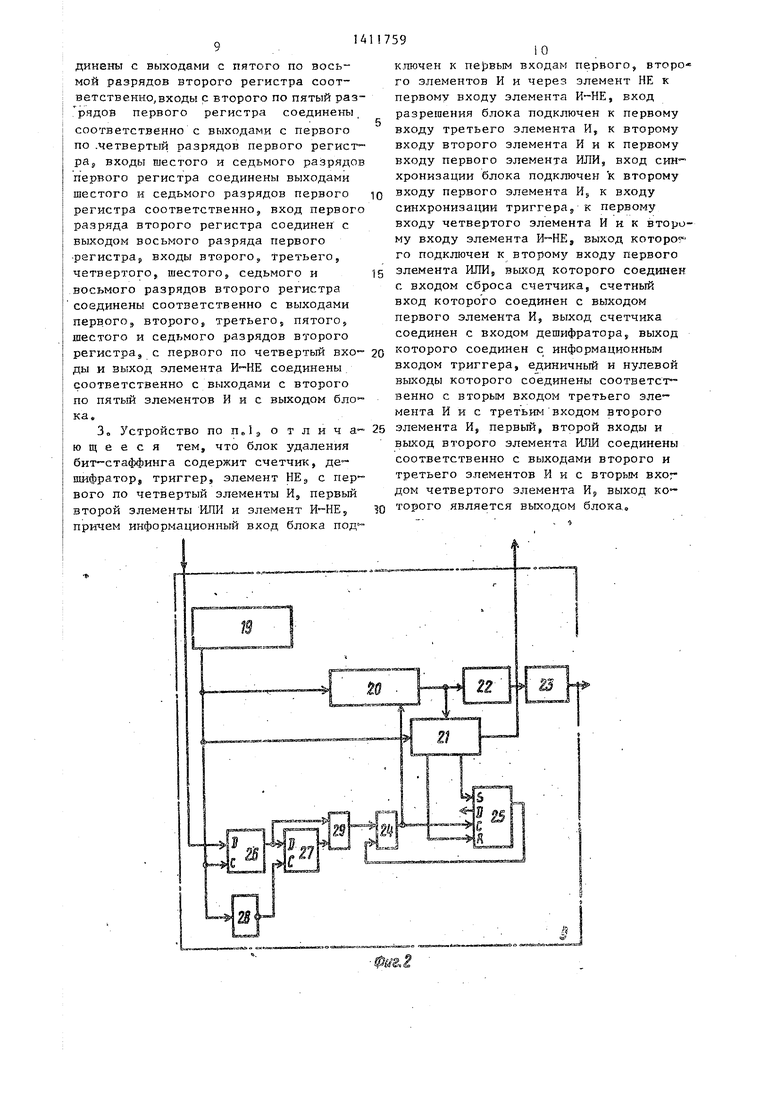

На фиг, представлена блок схема Q устройства; на фиг.2 схема блока синхронизации; на фиг.З схема блока памятй| на фиг,4 схема блока детиф ратора; на фиг,5 - схема блока удале ния бит-стаффинга; на фиг.6 схема 5 блока контроля; на фиг.7 - структура информационного кадра.

Устройство содержит приемник 1, передатчик 2, элементы И 3 и ИЛИ 4, счетчик 5, первый 6, второй 7 и тре 20 тий 8 триггеры, блок 9 синхронизации, блок 10 памяти, блок 11 дешифраторов, четвертый триггер 12, первьш 13, вто™ рой 14, третий 15 и четвертый 16 сдвиговые регистры, .блок 17 удаления 25 бит стаффинга и блок 18 контроля.

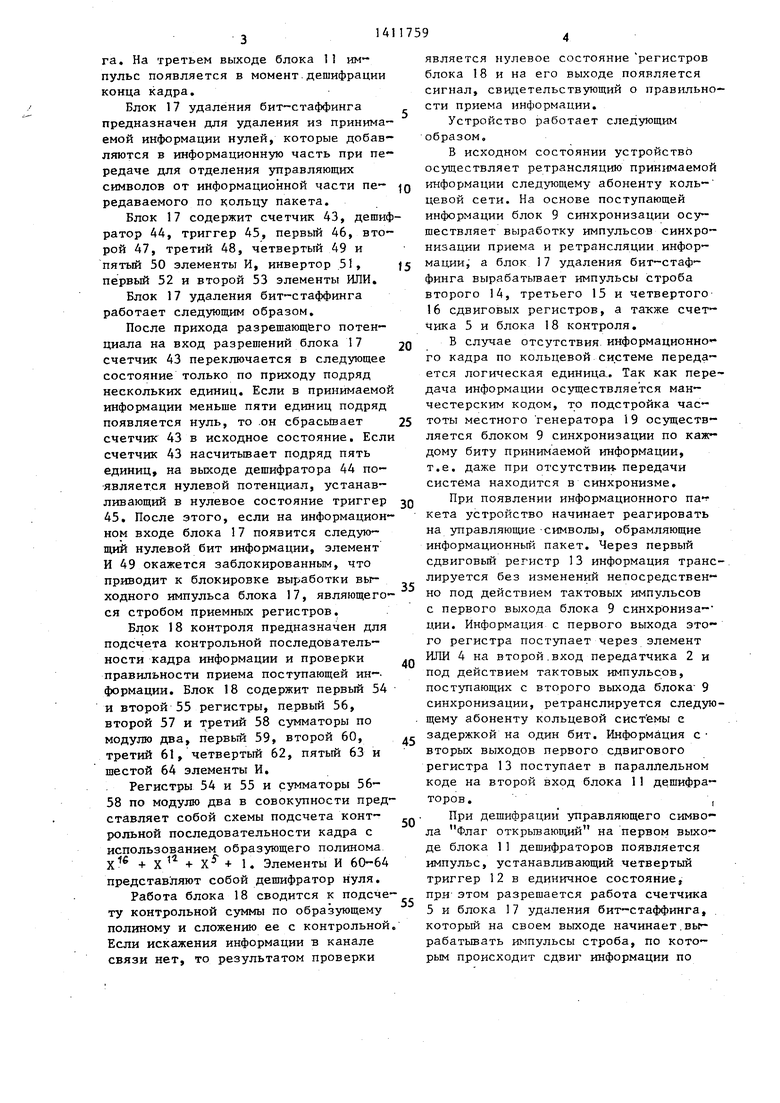

Блок 9 синхронизации (фиг.2) предназначен для обеспечения битовой синх ррнизацин принимаемой и ретранслируБлок 10 памяти (см, фиг.З) предна начен для буферизации принимаемого и сети информационного кадра и содержи блок 30 микросхем статической оперативной памяти типа К 565 РУ2, дешифр тор 31, реверсивный счетчик 32 адрес памяти и элемент И 33„

Адресные входы всех микросхем пам ти соединены между собой поразрядно подключены к выходу счетчика 32 адре са и входу дешифратора 31. Выход дешифратора 31 является выходом переполнения блока 10 памяти, Информацио ные выходы микросхем поступают на информационный выход блока 10 памяти Через вход синхронизации на элемент 33 поступает один из импульсов непе- рекрьшающейся серии, С входа разрешения на элемент И 33 и сбросовый вх счетчика 32 поступает разрешающий потенциал,

С входа записи блока IО памяти на вход элемента И 33 поступают импульг сы, сопровождающие каждый байт инфор мации. На выходе элемента И 33 фор- миру ется импульс записи, но которому производится запись информации в мик росхемы блока 30 памяти, а по заднем

емой информации и для выработки серии 30 Фронту этого импульса, поступающего

неперекрьгвающихся импульсов фаз, обес печивающей синхронизацию работы всех блоков устройства. Блок 9 содержит задающий генератор 19, делитель 20 частоты, дешифратор 21, фильтр 22, формирователь 23 импульсов, элемент И 24, первый 25,.второй 26 и третий 27 триггеры, инвертор 28 и сумматор 29 по модулю два .

Второй 26 и третий 27 триггеры, инвертор 28 и сумматор 29 по модулю два в совокупности предназначены для вьщеления значащего момента входного сигнала из информационной последовательности, поступающей на вход блока 9 синхронизации 9, Эти значащие моменты воздействуют на делитель 20 частоты синхронизируя фазу местного генератора 19 с фазой принимаемой информации. Серия неперекрьшающихся импульсов фаз с выходов дешифратора 21 поступает на первый выход блока .9 синхронизации и используется для синхронизации работы блоков устройства, а тактовая частота, прогаедшая через фильтр 22 и формирователь 23 импульсов 23 на вто,рой вьисод блока .9 син хронизации, используется для тактирования передатчика 2,

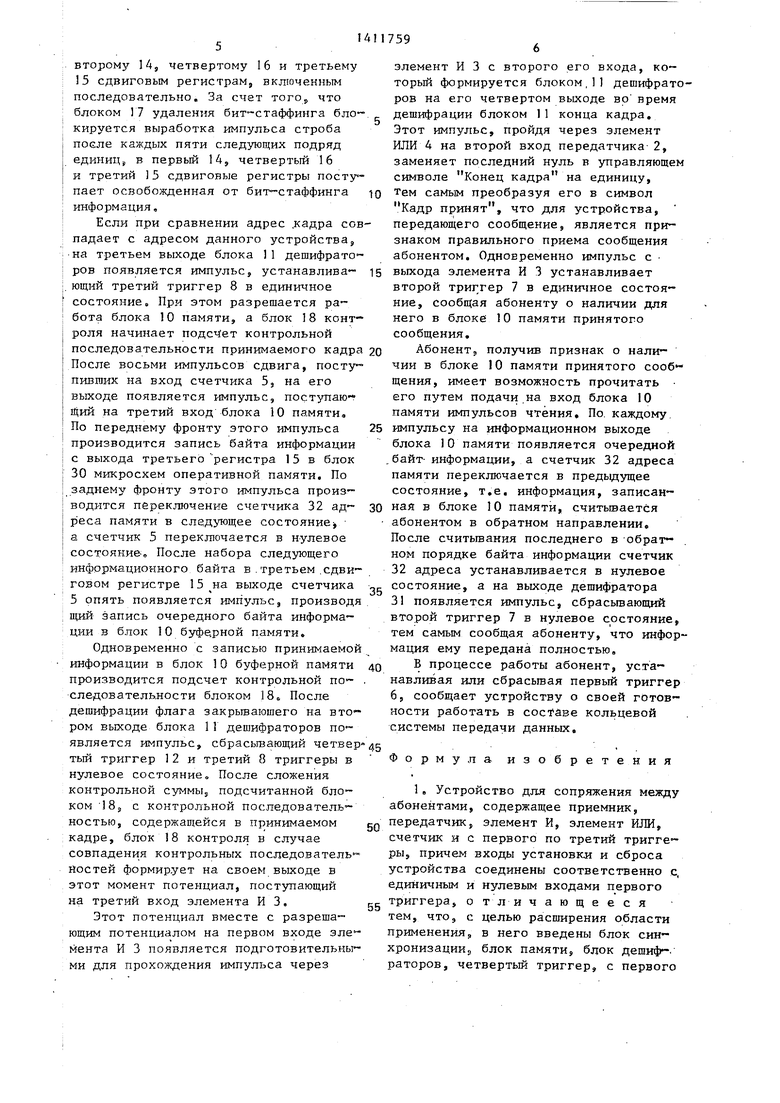

Блок 10 памяти (см, фиг.З) предназ- начен для буферизации принимаемого из сети информационного кадра и содержит блок 30 микросхем статической оперативной памяти типа К 565 РУ2, дешифратор 31, реверсивный счетчик 32 адреса памяти и элемент И 33„

Адресные входы всех микросхем памя ти соединены между собой поразрядно и подключены к выходу счетчика 32 са и входу дешифратора 31. Выход дешифратора 31 является выходом переполнения блока 10 памяти, Информацион ные выходы микросхем поступают на информационный выход блока 10 памяти. Через вход синхронизации на элемент И 33 поступает один из импульсов непе- рекрьшающейся серии, С входа разрешения на элемент И 33 и сбросовый вход счетчика 32 поступает разрешающий потенциал,

С входа записи блока IО памяти на вход элемента И 33 поступают импульг сы, сопровождающие каждый байт информации. На выходе элемента И 33 фор- миру ется импульс записи, но которому производится запись информации в микросхемы блока 30 памяти, а по заднему

5

0

на суммирующий вход счетчика 32, происходит переключение счетчика 32 ад- реса в следующее состояние. Через вход чтения блока 10 памяти .поступают импульсы на вычитающий вход реверсивного счетчика 32 адреса. Четвертый вход является информационным входом блока 10 памяти, .

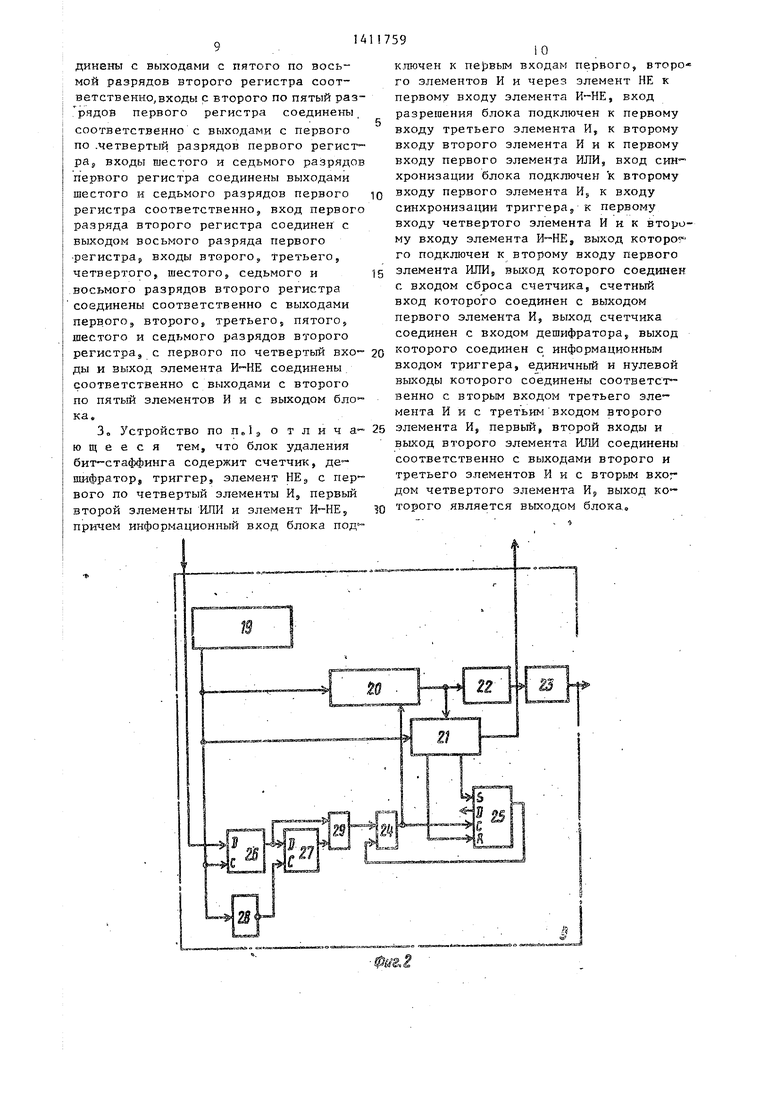

Блок 11 дешифраторов предназначен длядешифрации служебной и управляющей информации обрамляющей информаци онный кадр и содержит дешифратор 34 единиц четвертого регистра, дешифратор 35 флага четвертого регистра, с дешифратор 36 адреса абонента, дещиф ратор 37 единиц третьего регистра, дешифратор 38 флага первого регистра, дешифратор 39 конца кадра, первый 40, второй 41 и третий 42 элементы И,

Через первый вход блока I1 дешифраторов постзтае.т один из импульсов неперекрьшающейся серии фаз строби- рующий первый 40, второй 4 и третий 42 элементы И, На выходе элемента И 42 появляется- импульс при дешифрации адреса абонента и поступает на первый выход блока 11 дешифраторов. На втором выходе блока 1 1 появляется им« пульс при дешифрации открьшающего фла0

5

га. На третьем выходе блока 1 им пульс появляется в момент.дешифрации конца кадра.

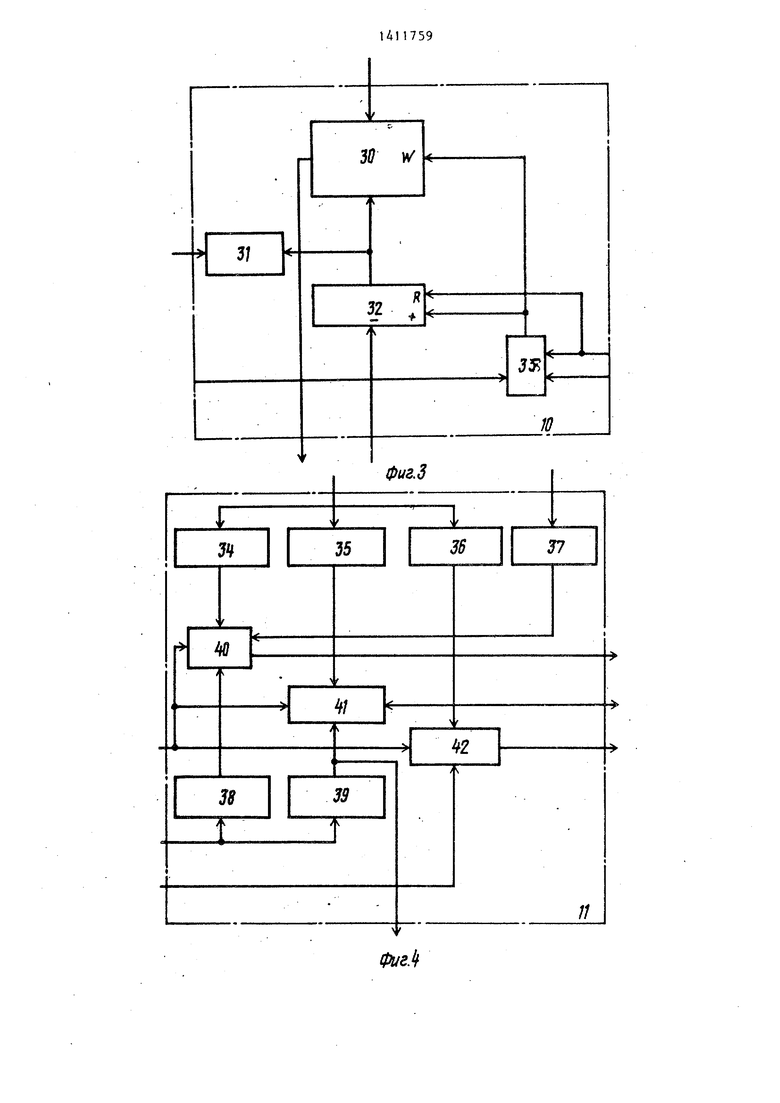

Блок 17 удаления бит-стаффинга предназначен для удаления из принимаемой информации нулей, которые добав ляются в информационную часть при передаче для отделения управляющих символов от информационной части передаваемого по кольцу пакета.

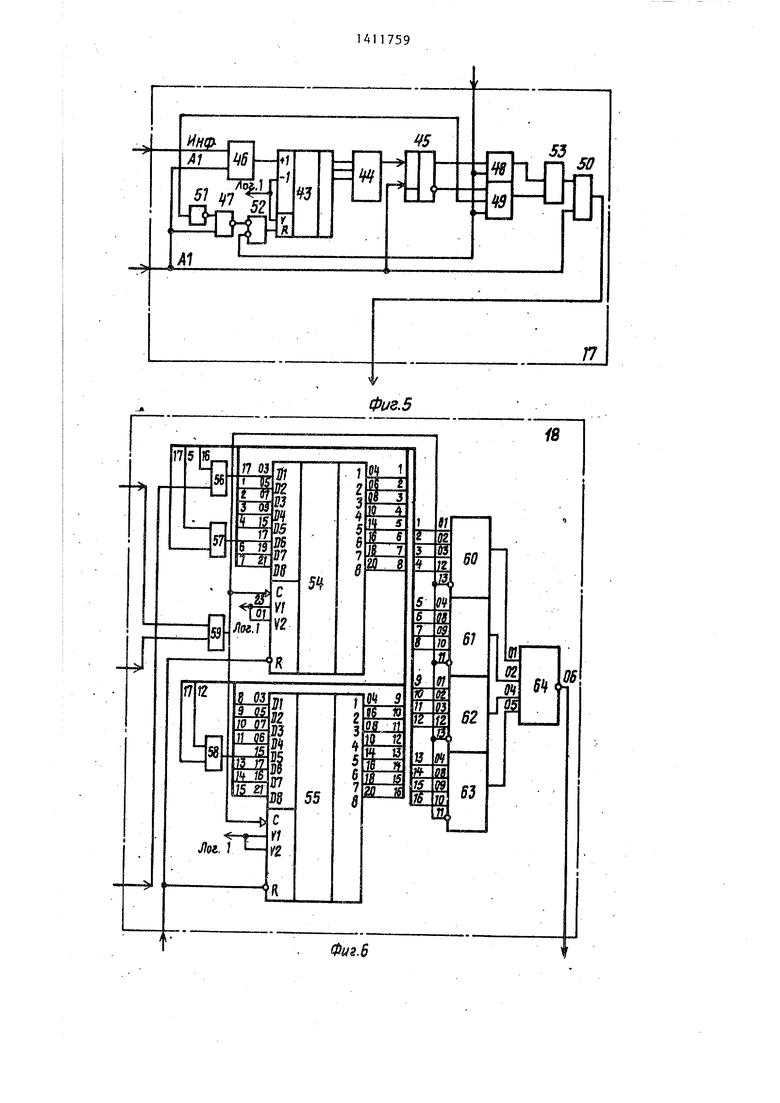

Блок 17 содержит счетчик 43, дешифратор 44, триггер 45, первый 46, вто рой 47, третий 48, четвертый 49 и пятый 50 элементы И, инвертор 51, первьй 52 и второй 53 элементы ИЛИ.

Блок 17 удаления бит -стаффинга работает следующим образом.

После прихода разрешающЁго потенциала на вход разрешений блока 17 счетчик 43 переключается в следующее состояние только по приходу подряд нескольких единиц. Если в принимаемой информации меньше пяти единиц подряд появляется нуль, то .он сбрась1вает счетчик 43 в исходное состояние. Если счетчик 43 насчитывает подряд пять единиц, на выходе дешифратора 44 появляется нулевой потенциал, устанавливающий в нулевое состояние триггер 45. После этого, если на информационном входе блока 17 появится следующий нулевой бит информации, элемент И 49 окажется заблокированным, что приводит к блокировке выработки выходного импульса блока 17, являющегося стробом приемных регистров.

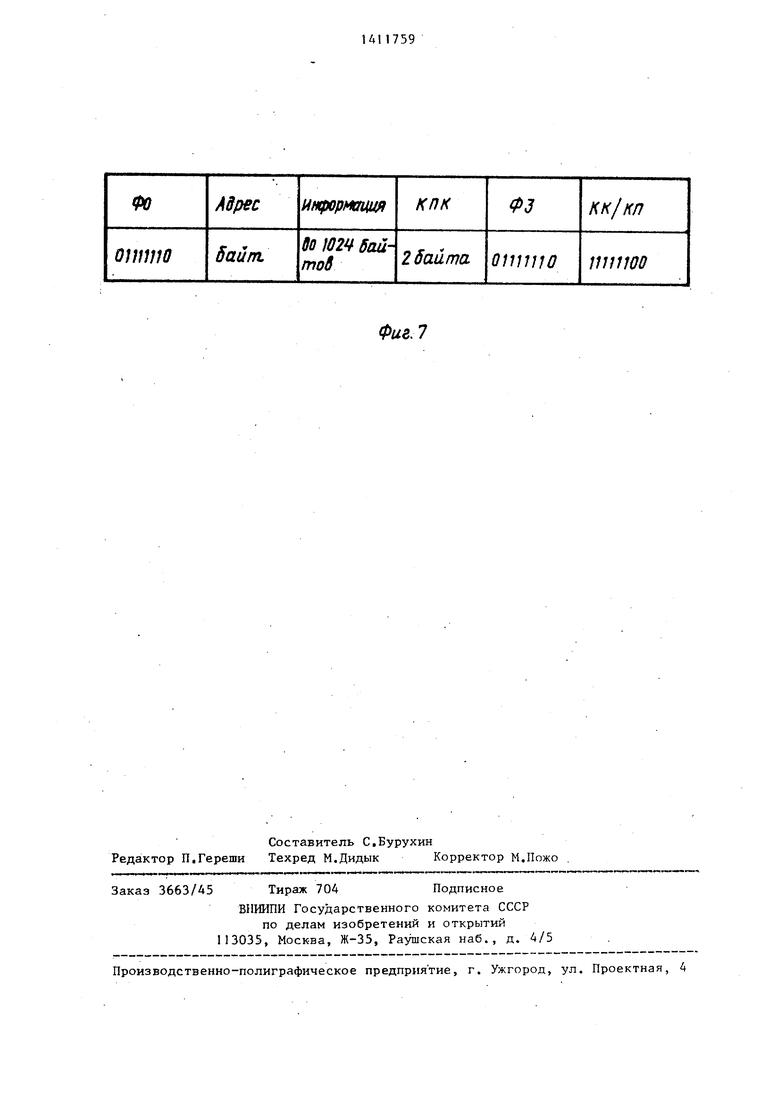

Блок 18 контроля предназначен для подсчета контрольной последовательности кадра информации и проверки правильности приема поступающей ин-. формации. Блок 18 содержит первый 54 и второй 55 регистры, первый 56, второй 57 и третий 58 сумматоры по модулю два, первый 59, второй 60, третий 61, четвертый 62, пятый 63 и шестой 64 элементы И.

Регистры 54 и 55 и сумматоры 56- 58 по модулю два в совокупности представляет собой схемы подсчета контрольной последовательности кадра с использованием образующего полинома + . Элементы И 60-64 представляют собой дешифратор нуля.

Работа блока 18 сводится к подсчету контрольной суммы по образующему полиному и сложению ее с контрольной Если искажения информации в канале связи нет, то результатом проверки

0

5

0

5

0

5

0

5

является нулевое состояние регистров блока 18 и на его выходе появляется сигнал, свидетельствующий о правильности приема информации.

Устройство работает следующим образом,

В исходном состоянии устройство осуществляет ретрансляцию принимаемой информации следующему абоненту коль- цевой сети. На основе поступающей информации блок 9 синхронизации осуществляет выработку импульсов синхронизации приема и ретрансляции информации а блок 17 удаления бит-стаф- финга вырабатьгоает импульсы строба второго 14, третьего 15 и четвертого 16 сдвиговых регистров, а также счетчика 5 и блока 18 контроля.

В случае отсутствия информационно го кадра по кольцевой системе передается логическая единица.. Так как передача информации осуществляется манчестерским кодом, то подстройка частоты местного генератора 19 осуществляется блоком 9 синхронизации по каждому биту принимаемой информации, т,е, даже при отсутствии, передачи система находится в синхронизме.

При появлении информационного кета устройство начинает реагировать на управляющие -символы, обрамляющие информационный пакет. Через первый сдвиговый регистр 13 информация транслируется без изменений непосредственно под действием тактовых импульсов с первого выхода блока 9 синхрониза- ции. Информация с первого выхода это го регистра поступает через элемент ИЛИ 4 на второй.вход передатчика 2 и под действием тактовых импульсов, поступающих с второго выхода блока- 9 синхронизации, ретранслируется следующему абоненту кольцевой сист емы е задержкой на один бит. Информация с вторых выходов первого сдвигового регистра 13 поступает в параллельном коде на второй вход блока 11 дешифраторов. I

При дешифрации управляющего символа Флаг открьгоаювщй на первом выходе блока 11 дешифраторов появляется импульс, устанавливающий четвертый триггер 12 в единичное состояние, при этом разрешается работа счетчика 5 и блока 17 удаления бит-стаффинга, который на своем выходе начинает.вырабатывать импульсы строба, по которым происходит сдвиг информации по

BTOpoMj 14j четвертому 16 и третьему 15 сдвиговым регистрам, включенным последовательно. За счет тогОр что блоком 17 удаления бит-стаффиига бло кируется выработка импульса строба после каждых пяти следующих подряд единицS в первый 14, четвертый 16 и третий 15 сдвиговые регистры посту i пает освобожденная от бит стаффинга ; информация,

; Если при сравнении адрес .кадра совпадает с адресом данного устройстваj :-на третьем выходе блока 11 дешифраторов появляется импульс, устанавлива - |. ющий третий триггер 8 в единичное I состояние При этом разрешается ра I бота блока 10 памяти, а блок 18 конт- I роля начинает подсчет контрольной последовательности принимаемого кадра После восьми импульсов сдвига, посту i nHBraiix на вход счетчика 5, на его выходе появляется импульс, поступаю 1й;ий на третий вход блока 10 памяти. По переднему фронту этого импульса : производится запись байта информации с выхода третьего регистра 15 в блок 30 микросхем оперативной памяти. По заднему фронту этого импульса произ™ водится переключение счетчика 32 ад I реса памяти в следующее состояниеj j а счетчик 5 переключается в нулевое состояние. После набора следзшщего информационного байта в.третьем .сдви говом регистре 15 на выходе счетчика 5 опять появляется импульс, производя щий запись очередного байта информа - дни в блок 10 буферной памяти.

Одновременно с записью принимаемой информации в блок 10 буферной памяти производится подсчет контрольной по- следовательности блоком 18 После дешифрации флага закрьшаюшего на втором выходе блока 11 дешифраторов появляется импульс, сбрасьшающий четвер тый триггер 12 и третий 8 триггеры в нулевое состояние После сложения контрольной суммы, подсчитанной блоком с контрольной последовательностью, содержащейся в принимаемом кадре, блок 18 контроля в случае совпадения контрольных последовательностей формирует на своем выходе в этот момент потенциал, поступающий на третий вход элемента ИЗ,

Этот потенциал вместе с разреша™ ющим потенциалом на первом входе элемента И 3 появляется подготовительными для прохождения импульса через

элемент И 3 с второго его входа, который формируется блоком,11 дешифраторов на его четвертом выходе во время дешифрации блоком 11 конца кадра. Этот импульс, пройдя через элемент ИЛИ 4 на второй вход передатчика-2, заменяет последний нуль в управляющем символе Конец кадра на единицу. Тем преобразуя его в символ Кадр принят, что для устройства, передающего сообщение, является признаком правильного приема сообщения абонентом. Одновременно импульс с выхода элемента И 3 устанавливает второй триггер 7 в единшшое состояние, сообщая абоненту о наличии для него в блоке 10 памяти принятого сообщения.

Абонент, получив признак о наличии в блоке 10 памяти принятого сооб щения, имеет возможность прочитать его путем подачи на вход блока 10 памяти импульсов чтения. По. каждому, импульсу на информационном выходе блока 10 памяти появляется очередной байт- информации, а счетчик 32 адреса памяти переключается в предыдущее состояние, т.е, информация, записанная в блоке 10 памяти, считьшается абонентом в обратном направлении. После считьшания последнего в -обратном порядке байта информации счетчик 32 адреса устанавливается в нулевое состояние, а на выходе дешифратора 31 появляется импульс, сбрасьшающий второй триггер 7 в нулевое состояние, тем самым сообщая абоненту, что информация ему передана полностью,

В процессе работы абонент, устанавливая или сбрасьтая первый триггер 6, сообщает устройству о своей готовности работать в составе кольцевой системы передачи данных,

Формула изобретения

1, Устройство для сопряжения между абонентами, содержащее приемник, передатчик, элемент И, элемент ИЛИ, счетчик и с первого по третий триггеры, причем входы установки и сброса устройства соединены соответственно с единичным и нулевым входами первого триггера, отличающееся тем, что, с целью расширения области применения, в него введены блок син- хронизацииа блок памяти, блок дешиф-. раторов, четвертый триггер, с первого

по четвертый сдвиговые регистры, блок удаления бит-стаффинга и блок контроля, причем вход приемника подключен к входу устройства для подключения информационного выхода первого абонента, выход приемника соединен с информационными входами блока удале ния бит-стаффинга, первого, второго сдвиговых регистров и с входом запус- ка блока синхронизации, первый выход которого соединен с входами синхронизации блока удаления бит-стаффинга первого сдвигового регистра, блока контроля, блока дешифраторов и блока памяти, второй выход блока синхронизации подключен к синхровходу передатчика, инфор мационньш вход и выход которого соединены соответственно с выходом элемента ИЛИ и с выходом устройства для подключения информационного входа первого абонента, первый вход элемента ИЛИ соединен с последовательным выходом первого сдвигового регистра, второй вход эле- мента ИЛИ соединен с выходом элемента И и с единичным входом второго триггера, выход которого соединен с выходом готовности устройства, нулевой вход второго триггера соединен с выхо дом переполнения блока памяти, информационные вход и выход которого являются входом и выходом устройства для подключения соответственно входа и выхода данных второго абонента, вход записи блока памяти соединен с выходом счетчика, выход третьего триггера соединен с входами разрешения . блока контроля и блока памяти и с первым входом элемента И, выход третьего сдвигового регистра соединен с первым информационным входом блока дешифраторов и с входом чтения блока памяти, выход четвертого триггера соединен с нулевым входом треть- его триггера и с входами разрешения счетчика и блока удаления бит-стаффинга, выход которого соединен с входами синхронизации второго, третьего, четвертого регистров сдвига, со счетным входом счетчика и с управляющим входом блока контроля, выход второго регистра- сдвига соединен с информационным входом четвертого регистра сдвига, последовательный выхОд кото- рого соединен с информационными входами третьего регистра сдвига и блока контроля, второй, третий, четвертый информационные входы блока дешифра

5 О 0 5 Q g

5

торов соединены соответственно с параллельными выходами первого, четвертого регистров и первого триггера, с первого по четвертый выходы блока дешифраторов соединены соответственно с единичным и нулевым входами четвертого триггера, с единичным входом третьего триггера и с вторым входом элемента И, третий вход которого соединен с выходом блока контроля.

соответственно с выходами с первого по .четвертый разрядов первого регист- paj входы шестого и седьмого разрядов первого регистра соединены выходами шестого и седьмого разрядов первого регистра соответственно, вход первого разряда второго регистра соединен с выходом восьмого разряда первого регистрар входы второго Третьего, четвертого, шестого седьмого и восьмого разрядов второго регистра соединены соответственно с выходами перв.ого, второгоS третьего, пятого, шестого и седьмого разрядов второго регистра, с первого по четвертый вхо- ды и выход элемента соединены . соответственно с выходами с второго по пятый элементов И и с выходом бло ка.

Зо Устройство поп„)эОтлича ю щ е е с я тем, что блок удаления бит стаффинга содержит счетчик, де-

пшфратор, триггер, элемент НЕд с пер вого по четвертый элементы И, первый второй элементы И.ПИ и элемент И-НЕ, причем информационный вход блока под 5 0

клгочен к первым входам первого, второго элементов И и через элемент НЕ к первому входу элемента И-НЕ, вход разрешения блока подключен к первому входу третьего элемента И, к второму входу второго элемента И и к первому входу первого элемента ИЛИ, вход син хронизации блока подключен к второму входу первого элемента И к входу синхронизации триггераj к первог-гу входу четвертого элемента И и к второму входу элемента И-НЕ, выход которое го подключен к второму входу первого элемента ИЛИ, выход которого соединен с входом сброса счетчика, счетный вход которого соединен с выходом первого элемента И, выход счетчика соединен с входом дешифратораs выход которого соединен с информационным входом триггера, единичный и нулевой выходы которого соединены соответст венно с вторым входом третьего элемента Икс третьим входом второго 5 элемента И, первый, второй входы и выход второго элемента ИЛИ соединены соответственно с выходами второго и третьего элементов Икс вторым вхог дом четвертого элемента И, выход ко торого является выходом блока.

0

г

34

35

39

39

Т

30 W

;

фиг.З

36

37

Фиг, 5

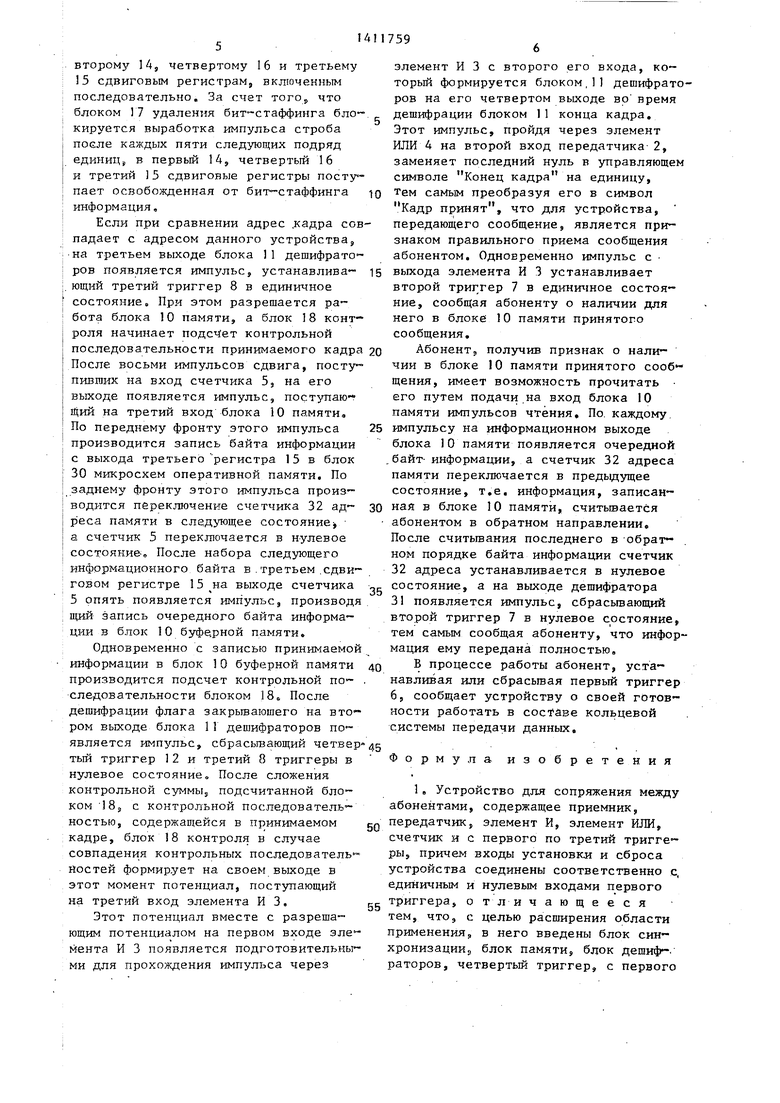

Фиг. 7

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1129599A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Двухканальное устройство сопряжения | 1981 |

|

SU993238A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-07-23—Публикация

1987-01-21—Подача