Область техники

Настоящее изобретение относится в целом к связи по общей последовательной шине и, в частности, к способу и системе опроса адресов для осуществления связи по общей линии связи с открытым коллектором.

Уровень техники

Существует некоторое количество протоколов интерфейсов интегральных схем, в которых главное устройство (master) осуществляет связь с подчиненным устройством (slave) с использованием назначенного для этого адреса. В случае общей шины, по которой более чем одно подчиненное устройство может осуществлять связь с главным устройством, каждое подчиненное устройство имеет уникальный адрес для использования при связи с главным устройством. Адрес подчиненного устройства может быть запрограммирован при помощи внешнего ввода таким образом, что подчиненное устройство получает адрес при включении подчиненного устройства. Альтернативно, адрес подчиненного устройства сохраняется в энергонезависимой памяти подчиненного устройства и может быть изменен в любое время. Интерфейсный протокол l2C является примером интерфейсного протокола, по которому главное устройство осуществляет связь с одним или более подчиненными устройствами, каждое из которых имеет назначенный ему уникальный адрес подчиненного устройства.

Во время или сразу после включения главное устройство не может знать адреса подчиненных устройств, которые подключены к общей шине и способны осуществлять связь с главным устройством. Например, замена устройства или технологические изменения могут вводить в систему различные подчиненные устройства. Печатающие устройства могут содержать контроллер, который функционирует как главное устройство, соединенное с возможностью связи с одним или более подчиненным устройством, соединенным с картриджами, чернильницами и т.п. Такие картриджи и чернильницы могут быть заменены, когда в них будут израсходованы тонер или чернила, и новый картридж или чернильница вставлены на их место в печатающее устройство. В связи с тем, что каждый новый картридж/чернильница имеют различные подчиненные устройства с уникальным адресом подчиненного устройства, обычно при включении или после включения выполняются операции для того, чтобы главное устройство узнало о подчиненных устройствах, соединенных с ним в текущий момент времени.

Существует подход, в котором главное устройство может узнать уникальные адреса подчиненных устройств, которые способны осуществлять связь с главным устройством. В протоколе l2C главное устройство может попытаться получить адреса подчиненных устройств путем отправки запроса, содержащего уникальный адрес подчиненного устройства, и ожидания ответа. Если есть ответ от подчиненного устройства, имеющего указанный адрес подчиненного устройства, главное устройство узнает о существовании указанного подчиненного устройства. С другой стороны, если ответа нет, то главное устройство узнает, что не существует подчиненных устройств, имеющих указанный уникальный адрес. Как можно видеть, главному устройству приходится отправлять запрос для каждого возможного адреса подчиненного устройства для того, чтобы узнать о каждом подчиненном устройстве, соединенном с l2C шиной. Для систем, в которых адреса подчиненных устройств могут быть длиной несколько битов или байтов, этот подход может привести к неэффективному количеству времени, потраченному на узнавание главным устройством всех соединенных с ним подчиненных устройств.

Исходя из вышеизложенного, существует потребность в более эффективном подходе к получению главным устройством информации об адресах подчиненных устройств, соединенных с ним с возможностью связи.

Раскрытие изобретения

Варианты осуществления настоящего изобретения устраняют недостатки систем связи известного уровня техники и, тем самым, удовлетворяют существенную потребность в протоколе для сообщения адресов подчиненных устройств в главное устройство по общей шине.

В соответствии с примерным вариантом осуществления настоящего изобретения здесь представлен способ осуществления связи с главным устройством по общей шине, имеющей линию данных, включающий: прием от главного устройства сигнала запроса, запрашивающего отправку адреса подчиненного устройства в главное устройство от каждого подчиненного устройства, связанного с линией данных; обеспечение установки последовательным образом линии данных в логические состояния, соответствующие значениям битов в первом адресе подчиненного устройства; и, при установке линии данных в логическое состояние, отличное от соответствующего значения бита первого адреса подчиненного устройства, временный вход в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство.

Другой примерный вариант осуществления настоящего изобретения содержит подчиненное устройство, имеющее интерфейсный порт для соединения с общей шиной, имеющей линию тактового сигнала и линию данных; энергонезависимую память для хранения первого адреса подчиненного устройства, соответствующего подчиненному устройству; и контроллер, соединенный с возможностью связи с интерфейсным портом и энергонезависимой памятью. При приеме от главного устройства интерфейсным портом сигнала запроса, запрашивающего отправку в главное устройство адреса каждого подчиненного устройства, соединенного с общей шиной, контроллер управляет интерфейсным портом для обеспечения установки последовательным образом линии данных в логические состояния, соответствующие значениям битов первого адреса подчиненного устройства. При установке линии данных в логическое состояние, отличное от соответствующего значения бита первого адреса подчиненного устройства, контроллер управляет интерфейсным портом для временного входа в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство.

Краткое описание чертежей

Вышеупомянутые и другие признаки и преимущества различных вариантов осуществления настоящего изобретения и способ их достижения станут более очевидными и будут лучше понятны путем ссылки на сопроводительные чертежи, где:

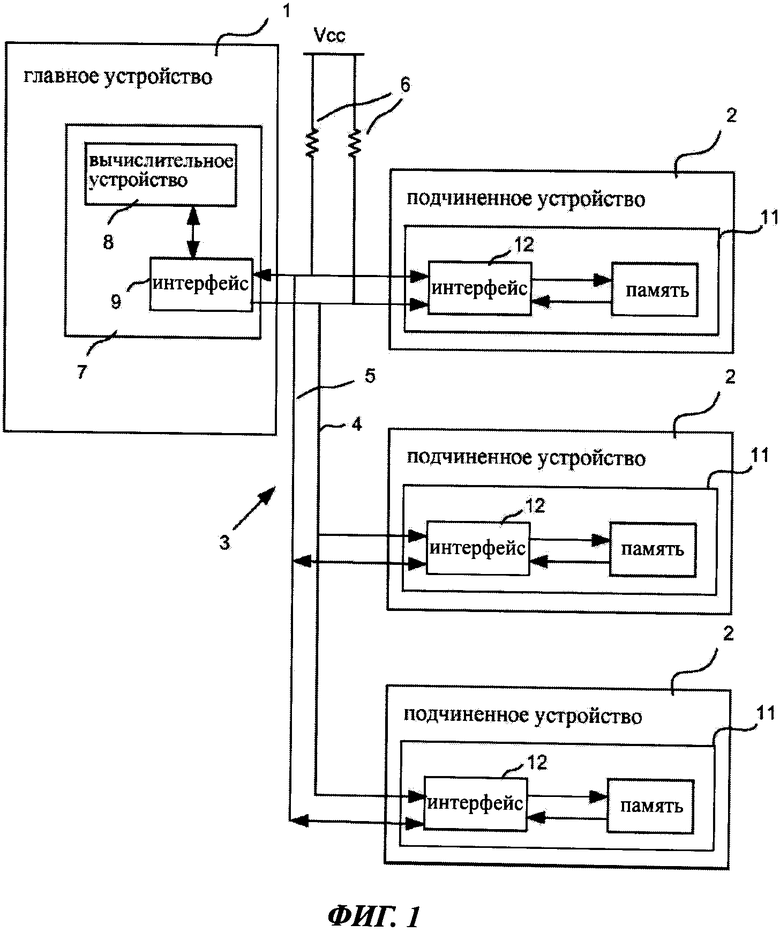

Фиг.1 представляет собой схематическую диаграмму системы связи согласно примерному варианту осуществления настоящего изобретения;

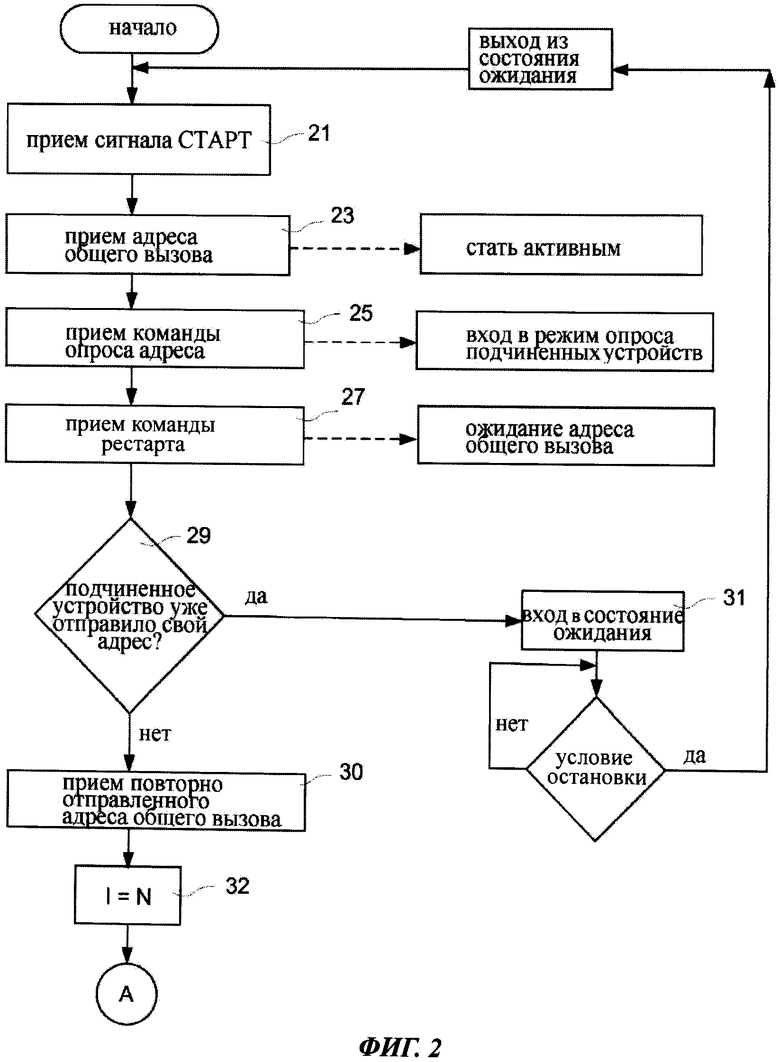

Фиг.2 представляет собой диаграмму, иллюстрирующую операции, выполняемые одним или более устройствами согласно примерному варианту осуществления настоящего изобретения; и

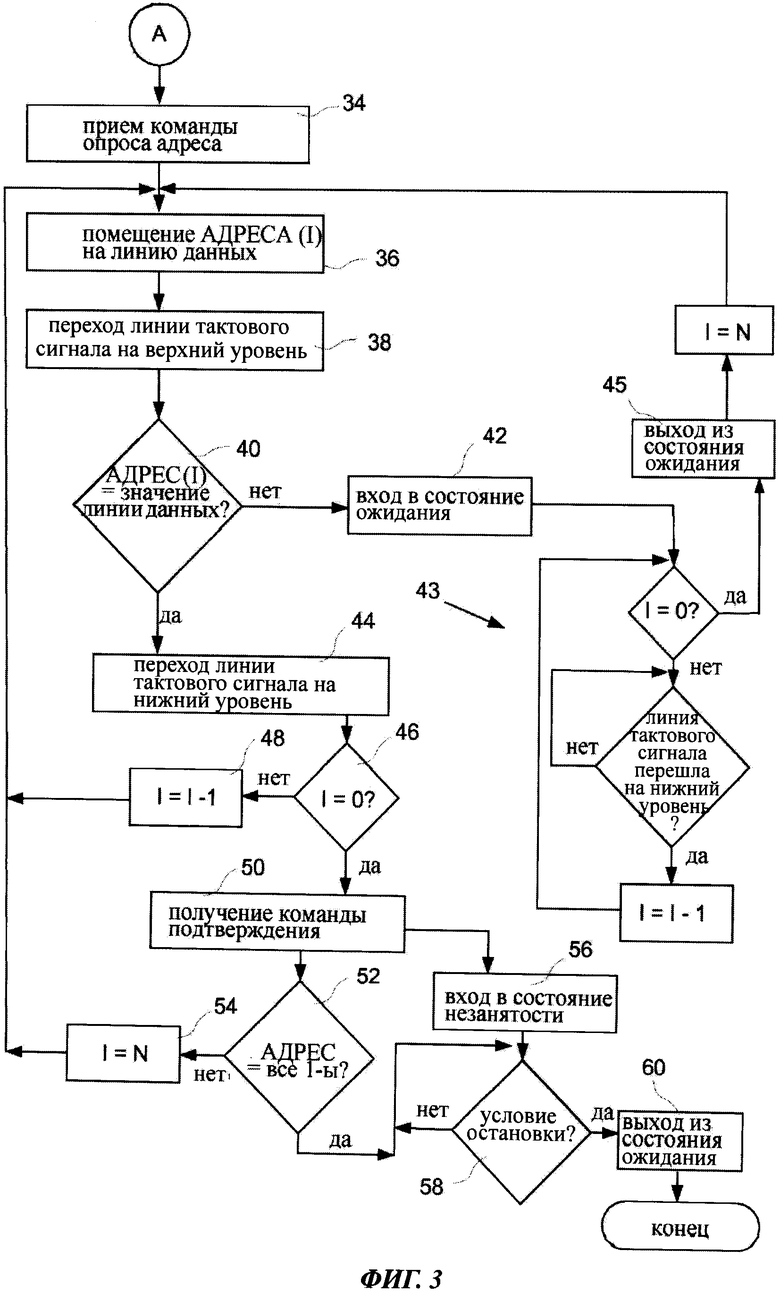

Фиг.3 представляет собой диаграмму, иллюстрирующую операции, выполняемые одним или более устройствами согласно примерному варианту осуществления настоящего изобретения.

Осуществление изобретения

Следует понимать, что настоящее изобретение не ограничивается в своих применениях деталями конструкции и расположением компонентов, изложенными в последующем описании или показанными на чертежах. Изобретение является эффективным в других вариантах осуществления и при практической реализации или выполнении различными путями. Также следует понимать, что используемые в документе формулировки и терминология используются в целях описания, и не должны рассматриваться в качестве ограничения. Использование терминов «включающий», «содержащий» или «имеющий» и их вариаций, используемых в настоящем документе, охватывает элементы, перечисленные в дальнейшем, и их эквиваленты, а также дополнительные предметы. Если не ограничено иным образом, термины «подключенный», «соединенный» и «установленный» и их вариации, использованные в данном документе, используются в широком их смысле и охватывают прямые и непрямые подключения, соединения и установки. Дополнительно, термины «подключенный», «соединенный» и их вариации, использованные в данном документе, не ограничиваются физическими или механическими подключениями или соединениями.

Дополнительно, следует понимать, что варианты осуществления настоящего изобретения включают как аппаратное обеспечение, так и электронные компоненты или модули, которые в целях пояснения могут быть показаны и описаны так, как будто большинство компонентов реализованы исключительно с помощью аппаратного обеспечения. Однако, специалистам в данной области техники на основании чтения этого подробного описания должно быть очевидно, что в по меньшей мере одном варианте осуществления аспекты настоящего изобретения, относящиеся к электронике, могут быть реализованы с помощью программного обеспечения. В этой связи следует заметить, что для реализации настоящего изобретения могут применяться множество устройств на основании аппаратного и программного обеспечения, также как и множество различных конструктивных компонентов. Кроме того, как описано в последующих параграфах, конкретные механические конфигурации, изображенные на чертежах, имеют целью служить примером вариантов осуществления настоящего изобретения, и возможны другие альтернативные механические конфигурации.

На фиг.1 показана система для осуществления связи между главным устройством 1 и одним или более подчиненным устройством 2 в соответствии с примерным вариантом осуществления настоящего изобретения. Главное устройство 1 и одно или более подчиненное устройство 2 осуществляют связь с друг другом по общей шине 3. Общая шина 3 может являться шиной, по которой между главным устройством 1 и подчиненным устройством 2 передается информация. Как изображено на фиг.1, более чем одно подчиненное устройство 2 может быть соединено с общей шиной 3 для осуществления связи с главным устройством 1. В примерном варианте осуществления настоящего изобретения общая шина 3 может содержать линию 4 тактового сигнала и линию 5 данных. Линия 4 тактового сигнала может использоваться для синхронизации связи между главным устройством 1 и подчиненным(и) устройством(ами) 2. В частности, главное устройство 1 может обеспечивать тактовый или другой синхронизирующий (временной) сигнал в линии 4 тактового сигнала для синхронизации связи между устройствами. Линия 5 данных может использоваться для передачи информации между главным устройством 1 и подчиненным(и) устройством(ами) 2. В примерном варианте осуществления настоящего изобретения линия 5 данных может быть одиночной линией, так что информация передается между устройствами последовательным образом. Альтернативно, линия 5 данных может быть более чем одной линией для отправки информации параллельно. С линией 4 тактового сигнала и с линией 5 данных может быть соединено подтягивающее устройство, которое служит для относительно небольшой подтяжки напряжения в соответствующей линии к напряжению Vcc питания, соответствующему уровню напряжения логической единицы, в отсутствие каких-либо устройств (главного устройства 1 или подчиненного устройства 2), приводящих линию к земле, соответствующей уровню напряжения логического нуля. Подтягивающее устройство 6 может быть резистивным элементом. Таким образом, линия 5 данных может рассматриваться, как структура монтажного ИЛИ, выполненная с открытым коллектором, в которой уровень логического нуля появляется в линии 5 данных вследствие привода линии 5 данных одним или более устройствами к потенциалу земли, а уровень логической единицы появляется в линии 5 данных, когда ни одно из устройств, соединенных с линией 5 данных, не приводит линию 5 данных к потенциалу земли, тем самым позволяя подтягивающему устройству 6 подтянуть линию 5 данных к напряжению Vcc питания. Конфигурации шины с открытым коллектором, монтажным ИЛИ хорошо известны, поэтому для простоты не предлагается дальнейшее их описание.

В соответствии с примерным вариантом осуществления настоящего изобретения главное устройство 1 может инициировать связь между главным устройством 1 и подчиненным(и) устройством(ами) 2. Главное устройство 1 может содержать контроллер 7 для, среди прочего, управления связью с подчиненными устройствами 2, которые соединены с общей шиной 3. Контроллер 7 может содержать вычислительное устройство (процессор) 8 с энергонезависимой памятью для хранения встроенного программного обеспечения, исполняемого вычислительным устройством 8 для осуществления связи с подчиненными устройствами 2. Контроллер 6 может дополнительно содержать главный интерфейс 9 для передачи и приема сигналов по общей шине 3 в соответствии с необходимым протоколом связи. Контроллер 7 может быть реализован в виде интегральной схемы, такой как специализированная интегральная схема (ASIC, application specific integrated circuit).

Подчиненное устройство 2 может содержать подчиненный контроллер 11 для осуществления связи с главным устройством 1 по общей шине 3. Контроллер 11 может содержать подчиненный интерфейс 12 для передачи и приема сигналов по общей шине 3 в соответствии с необходимым протоколом связи. Контроллер 11 может содержать энергонезависимую память для хранения информации об адресе подчиненного устройства, который является уникальным для индивидуального подчиненного устройства 2 и используется главным устройством 1 для осуществления связи с подчиненным устройством. Контроллер 11 может исполнять встроенное программное обеспечение, хранящееся в его энергонезависимой памяти для осуществления связи с главным устройством 1. Контролер 11 может быть реализован в виде интегральной схемы, такой как специализированная интегральная схема (ASIC).

Как упомянуто выше, главное устройство 1 и подчиненные устройства 2 осуществляют связь друг с другом по общей шине 3. Главное устройство 1 и подчиненные устройства 2 могут следовать конкретному протоколу для осуществления связи по общей шине 3. Например, главное устройство 1 и подчиненные устройства 2 могут использовать протокол связи l2C. Понятно, однако, что главное устройство 1 и подчиненные устройства 2 могут осуществлять связь друг с другом, используя другие протоколы связи. Главное устройство 1 и подчиненные устройства 2 могут осуществлять связь друг с другом, используя протоколы для конфигураций с открытым коллектором типа шины управления системой (SMB, System Management Bus) и шины компьютерных систем фирмы Apple (ADB, Apple Desktop Bus).

Как упомянуто выше, при включении главное устройство 1 не может знать адреса подчиненных устройств 2, которые подключены к общей шине 3 и способны осуществлять связь с главным устройством 1. Это может быть обусловлено, по меньшей мере частично, тем фактом, что подчиненные устройства 2, связанные с главным устройством 1, могут время от времени заменяться на новые подчиненные устройства 2, имеющие отличные назначенные им адреса подчиненного устройства. Варианты осуществления настоящего изобретения обеспечивают технологию опроса адресов для эффективного сообщения уникальных адресов подчиненных устройств в главное устройство 1. Способ опроса адресов будет описан ниже в отношении протокола связи l2C, но, как упомянуто выше, должно быть понятно, что способ не ограничен конкретным протоколом и применим для любого из ряда других протоколов связи.

На фиг.2 и 3 показан способ опроса адресов для главного устройства 1 и подчиненных устройств 2 в соответствии с примерными вариантами осуществления настоящего изобретения. Для простоты на фиг.2 и фиг.3 главным образом показан способ опроса адресов с точки зрения подчиненного устройства 2. Сначала главное устройство 1 посылает стартовую команду подчиненным устройствам 2, которая принимается на шаге 21. Прием стартовой команды вызывает подготовку подчиненных устройств 2 к приему адреса устройства. Главное устройство 1 отправляет адрес общего вызова в подчиненные устройства 2, который, когда принят на шаге 23, обеспечивает переход к активности каждого подчиненного устройства 2. Главное устройство 1 может затем отправить команду опроса адреса, которая, когда принята на шаге 25, обеспечивает вход подчиненных устройств 2 в режим опроса подчиненных устройств и их ожидание команды рестарта от главного устройства 1, согласно протоколу связи l2C. Главное устройство 1 может затем отправить команду рестарта подчиненным устройствам 2, которая, когда принята на шаге 27, обеспечивает ожидание подчиненными устройствами 2 повторной отправки команды адреса общего вызова от главного устройства 1.

После этого каждое подчиненное устройство 2 определяет на шаге 29, был ли уже отправлен его уникальный адрес подчиненного устройства в главное устройство 1. Если подчиненное устройство 2 определяет, что его адрес подчиненного устройства уже отправлен в главное устройство 1, то подчиненное устройство 2 входит в режим ожидания на шаге 31 до появления условия остановки, которое указывает, что операция опроса адресов завершена. Подчиненные устройства 2, которые еще не отправили свои соответствующие адреса подчиненного устройства в главное устройство 1, остаются активными.

Главное устройство 1 повторно отправляет адрес общего вызова подчиненным устройствам 2 и освобождает линию 5 данных для того, чтобы позволить подчиненным устройствам 2 контролировать линию 5 данных и размещать информацию на ней после приема адреса общего вызова на шаге 30. Переменной I присваивается значение N на шаге 32, где N соответствует количеству битов в адресах подчиненного устройства. Обращаясь к фиг.3, главное устройство 1 может оправлять команду изменения адреса в подчиненные устройства 2, которая, при ее приеме на шаге 34, обеспечивает одновременную установку в линии 5 данных наиболее значимого бита (MSB), т.е. 1-го бита соответствующего адреса подчиненного устройства 2, каждым подчиненным устройством 2, не находящимся в ожидании. Подчиненные устройства 2, имеющие адрес подчиненного устройства с MSB, равным логическому нулю, переводят линию 5 данных в состояние логического нуля. Подчиненные устройства 2, имеющие адрес подчиненного устройства с MSB, равным логической единице, с другой стороны, освободят (т.е. не переведут) линию 5 данных вследствие конфигурации линии 5 данных с открытым коллектором, монтажным ИЛИ, и вместо того позволят подтягивающему устройству 6 подтянуть линию 5 данных к состоянию логической единицы в отсутствие какого-либо другого подчиненного устройства 2, переводящего линию 5 данных в состояние логического нуля. После этого главное устройство 1 может перевести линию 4 тактового сигнала в состояние логической единицы на шаге 38.

На шаге 40 каждое подчиненное устройство 2, не находящееся в ожидании, определяет, соответствует ли значение на линии 5 данных MSB адреса подчиненного устройства 2. Если соответствия нет, это означает, что подчиненное устройство 2, которое освободило и/или позволило подтянуть линию 5 данных к состоянию логической единицы (при помощи подтягивающего устройства 6) вместо этого обнаружила перевод линии 5 данных в состояние логического нуля, осуществленный по меньшей мере одним подчиненным устройством 2, что указывает, что по меньшей мере одно другое подчиненное устройство 2 имеет адрес подчиненного устройства с MSB равным логическому нулю. Подчиненное устройство 2, которое освободило линию 5 данных, таким образом определяет, что по меньшей мере одно другое подчиненное устройство 2 имеет адрес подчиненного устройства с более низким значением адреса подчиненного устройства, чем его собственный адрес подчиненного устройства, и подчиненное устройство 2, имеющее более высокое значение адреса подчиненного устройства входит в состояние ожидания на шаге 42 для того, чтобы позволить по меньшей мере одному другому подчиненному устройству 2, имеющему более низкое значение адреса подчиненного устройства, передать оставшуюся часть соответствующего адреса подчиненного устройства с более низким значением в главное устройство 1. Подчиненное устройство 2, имеющее адрес подчиненного устройства с более высоким значением и временно остающееся в состоянии ожидания, может быть проиллюстрировано блоками 43, где значение переменной I уменьшается с каждым появлением заднего фронта на линии 4 тактового сигнала, до тех пор, пока переменная I не станет равна нулю. При равенстве нулю переменной I, указывающем, что другое подчиненное устройство 2 завершило передачу своего адреса подчиненного устройства в главное устройство 1, ожидающее подчиненное устройство 2 выходит из состояния ожидания на шаге 45, повторно устанавливает переменную I равной N на шаге 47 и начинает снова устанавливать MSB своего адреса подчиненного устройства в линии 5 данных на шаге 36.

После этого главное устройство 1 переводит линию тактового сигнала на нижний уровень на шаге 44, что фиксирует логическое значение, появившееся в линии 5 данных. На шаге 46 определяется, равна ли переменная I нулю. Если переменная I не равна нулю, то на шаге 48 переменная I уменьшается, и способ возвращается к блоку 36, приводя к тому, что каждое активное подчиненное устройство 2 устанавливает линию 5 данных в значение следующего самого значимого бита, 1-го бита, соответствующего подчиненному устройству адреса подчиненного устройства. Шаги 36-46 повторяются в отношении следующего самого значимого (1-го) бита адресов подчиненного устройства, размещаемых в линии 5 данных, при этом каждое подчиненное устройство 2 имеет больший адрес подчиненного устройства, нежели чем другое подчиненное устройство 2, снова помещенное в состояние ожидания на шаге 42. Путем подобного повторения блоков 36-48 для каждого бита адреса подчиненного устройства, все подчиненные устройства 2 за исключением подчиненного устройства 2, имеющего наименьший адрес подчиненного устройства, входят в состояние ожидания, а подчиненное устройство 2, имеющее наименьший адрес подчиненного устройства, устанавливает в линии 5 данных значение каждого бита своего адреса подчиненного устройства для их сбора главным устройством 1. Когда все биты подчиненного устройства 2, имеющего наименьший адрес подчиненного устройства, собраны главным устройством 1, главное устройство 1 отправляет подтверждение подчиненным устройствам на шаге 50. Подчиненное устройство 2, имеющее наименьший адрес подчиненного устройства, затем входит в состояние ожидания на шаге 56 и остается там до тех пор, пока на шаге 58 не появится условие остановки.

На шаге 52 главное устройство 1 определяет, является ли каждый бит принятого таким образом адреса подчиненного устройства значением логической единицы, указывая тем самым, что все адреса подчиненных устройств были приняты ранее, после чего главное устройство 1 подает состояние остановки в подчиненные устройства 2 для окончания опроса адресов. После подачи главным устройством 1 условия остановки, все подчиненные устройства 2 в состоянии ожидания становятся активными на шаге 60 и ждут следующего сообщения из главного устройства 1. Если определение на шаге 52 имеет отрицательный результат, на шаге 54 переменной I повторно присваивается значение N, и блоки 36-56 повторяются для главного устройства 1 для приема следующего наименьшего адреса подчиненного устройства от оставшихся подчиненных устройств 2, которым еще нужно передать свои адреса подчиненного устройства в главное устройство 1. Блоки 36-56 повторяются таким образом для отправки в главное устройство 1 адреса подчиненного устройства для каждого подчиненного устройства, соединенного с общей шиной 3.

В одном примерном варианте осуществления MSB каждого адреса подчиненного устройства может быть значением логического нуля, так что если значение линии 5 данных когда-либо примет значение логической единицы, когда подчиненные устройства 2 устанавливают свои MSB в линии 5 данных, главное устройство 1 может легко определить, что каждое подчиненное устройство 2 уже передало свой адрес подчиненного устройства в главное устройство 1, после чего главное устройство 1 может подать условие остановки для окончания опроса адресов.

Как можно видеть, способ опроса адресов согласно примерным вариантам осуществления настоящего изобретения предусматривает относительно быстрый способ эффективного информирования главного устройства 1 об адресах подчиненных устройств каждого подчиненного устройства 2, связанного с общей шиной 3.

В примерном варианте осуществления настоящего изобретения главное устройство 1 может являться устройством формирования изображений, таким как принтер, а подчиненные устройства 2 могут быть заменяемыми картриджами, резервуарами и т.п.для тонера или чернил. В этом варианте осуществления изобретения главное устройство 1 может содержать некоторое количество дополнительных компонентов и модулей, таких как печатающий механизм для нанесения тонера или чернил на лист носителя; механизм подачи носителя для захвата листа носителя из стопы листов носителя и перемещения захваченного листа к печатающему механизму и впоследствии к выходному лотку носителя; пользовательский интерфейс для приема пользовательских команд и обеспечения пользователя относящейся к работе информацией; и интерфейс для осуществления связи с компьютерным устройством. Такие компоненты и модули устройств формирования изображений известны из уровня техники и для простоты не будут описаны дополнительно. В альтернативном варианте должно быть понятно, что главное устройство 1 может быть любым устройством для, среди прочего, осуществления связи с подчиненными устройствами 2, которые соединены с общей шиной 3.

Вышеизложенное описание нескольких способов и варианта осуществления настоящего изобретения были представлены в иллюстративных целях. Оно не предполагается исчерпывающим или ограничивающим настоящее изобретение раскрытыми точными шагами и/или формами, и в свете вышеизложенной идеи возможны многие очевидные модификации и изменения. Например, понятно, что переменная I может быть первоначально установлена в нуль в блоке 32 и увеличиваться в блоке 48 так, чтобы значения адресов подчиненного устройства могли устанавливаться в линии 5 данных последовательно от наименее значимого бита до MSB.

Предполагается, что объем охраны настоящего изобретения определяется прилагаемой формулой изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| СОВМЕСТИМОСТЬ ОДНОПРОВОДНОЙ И ТРЕХПРОВОДНОЙ ШИН | 2005 |

|

RU2352980C2 |

| МНОГОКОЛЬЦЕВАЯ СЕТЬ ETHERNET И СПОСОБ ЕЕ ЗАЩИТЫ | 2011 |

|

RU2587407C2 |

| ЛОГИЧЕСКАЯ СХЕМА | 2018 |

|

RU2774795C1 |

| АРХИТЕКТУРА ЗАПОМИНАЮЩЕГО УСТРОЙСТВА С ЭКОНОМИЕЙ ДИНАМИЧЕСКОЙ МОЩНОСТИ | 2009 |

|

RU2471259C2 |

| СИСТЕМА СВЯЗИ С ГЛАВНОЙ СТАНЦИЕЙ И ПО МЕНЬШЕЙ МЕРЕ ОДНОЙ ПОДЧИНЕННОЙ СТАНЦИЕЙ | 1997 |

|

RU2146065C1 |

| Способ тестирования микросхем энергонезависимой памяти и устройство для его осуществления | 2023 |

|

RU2821349C1 |

| ЛОГИЧЕСКАЯ СХЕМА | 2019 |

|

RU2779569C1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| СПОСОБ ДВУХТАКТНОЙ АССОЦИАТИВНОЙ МАРШРУТИЗАЦИИ | 1999 |

|

RU2140132C1 |

| ШЛЮЗ ДЛЯ АВТОМАТИЧЕСКОЙ МАРШРУТИЗАЦИИ СООБЩЕНИЙ МЕЖДУ ШИНАМИ | 2007 |

|

RU2415511C2 |

Изобретение относится к средствам связи из нескольких подчиненных устройств с главным устройством по общей шине осуществления для опроса адресов с целью сообщения значений уникального адреса подчиненного устройства в главное устройство по общей шине. Технический результат заключается в уменьшении времени обнаружения подчиненных устройств. Принимают от главного устройства сигнала запроса, запрашивающего отправку адреса подчиненного устройства в главное устройство от каждого подчиненного устройства, соединенного с линией данных. Обеспечивают последовательную установку линии данных в логические состояния, соответствующие значениям битов в первом адресе подчиненного устройства. При установке линии данных в логическое состояние, отличное от соответствующего значения бита первого адреса подчиненного устройства, временный вход в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство. 3 н. и 10 з.п. ф-лы, 3 ил.

1. Способ осуществления связи каждым из нескольких подчиненных устройств с главным устройством по общей шине, имеющей линию данных, при этом каждое из нескольких подчиненных устройств имеет соответствующий адрес подчиненного устройства, включающий следующие шаги, выполняемые каждым из подчиненных устройств:

а) прием переданного от главного устройства во все несколько подчиненных устройств сигнала запроса, запрашивающего отправку соответствующего адреса подчиненного устройства в главное устройство от каждого из нескольких подчиненных устройств, соединенных с линией данных;

б) установка в линии данных логического состояния, соответствующего первому значению битов в адресе подчиненного устройства, соответствующем подчиненному устройству, так что линия данных либо переводится к первому значению, отражающему первое логическое состояние, одним или более подчиненными устройствами, либо, в случае, если она не переводится к первому значению одним или более подчиненными устройствами, освобождается ко второму значению, отражающему второе логическое состояние;

в) определение, соответствует ли значение линии данных первому значению битов; и

г) либо, при определении того, что значение линии данных отлично от первого значения битов адреса подчиненного устройства, временный вход в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство,

д) либо, при определении того, что значение линии данных соответствует первому значению битов адреса подчиненного устройства, повторение шагов б) и в) для дальнейших значений битов адреса подчиненного устройства до тех пор:

д1) пока не будет определено, что значение линии данных отлично от текущего значения битов адреса подчиненного устройства, осуществляя при этом временный вход в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство, или

д2) пока в линии данных не будет осуществлена установка всех битов адреса подчиненного устройства.

2. Способ по п. 1, отличающийся тем, что дополнительно включает вход в состояние ожидания, когда в линии данных была осуществлена установка всех битов адреса подчиненного устройства.

3. Способ по п. 1, отличающийся тем, что первое логическое состояние является состоянием логического нуля, а второе логическое состояние является состоянием логической единицы.

4. Способ по п. 1, отличающийся тем, что шаг в) дополнительно включает отслеживание логического состояния линии данных, причем вход в состояние ожидания основан на указанном определении.

5. Способ по п. 1, отличающийся тем, что повторения шага б) выполняют последовательным образом от наиболее значимого бита адреса подчиненного устройства до его наименее значимого бита.

6. Способ по п. 1, отличающийся тем, что дополнительно включает подсчет первого количества тактовых циклов с момента времени, когда начинается шаг б), причем шаг г) включает вход в состояние незанятости на второе количество тактовых циклов, при этом второе количество тактовых циклов соответствует количеству битов адреса подчиненного устройства, меньшему первого количества тактовых циклов.

7. Способ по п. 6, отличающийся тем, что шаг г) дополнительно включает выход из состояния ожидания по окончании второго количества тактовых циклов и повторение шагов б)-д).

8. Способ по п. 7, отличающийся тем, что дополнительно включает, при завершении шага е2), вход в состояние ожидания до тех пор, пока от главного устройства не будет принято указание, что таким образом приняты все адреса подчиненного устройства.

9. Подчиненное устройство, содержащее

интерфейсный порт для соединения с общей шиной, имеющей линию тактового сигнала и линию данных;

контроллер, соединенный с возможностью осуществления связи с интерфейсным портом, включающий энергонезависимую память для хранения адреса подчиненного устройства с целью осуществления связи с главным устройством по общей шине и выполненный с возможностью:

а) при приеме интерфейсным портом переданного от главного устройства во все несколько связанных с главным устройством несколько подчиненных устройств сигнала запроса, запрашивающего отправку в главное устройство соответствующего адреса каждого подчиненного устройства, соединенного с общей шиной,

б) управления интерфейсным портом для установки в линии данных логического состояния, соответствующего первому значению битов в адресе подчиненного устройства, соответствующем подчиненному устройству, так что линия данных либо переводится к первому значению, отражающему первое логическое состояние, одним или более подчиненными устройствами, либо, в случае, если она не переводится к первому значению одним или более подчиненными устройствами, освобождается ко второму значению, отражающему второе логическое состояние;

в) определения, соответствует ли значение линии данных первому значению битов; и

г) либо, при определении того, что значение линии данных отлично от первого значения битов адреса подчиненного устройства, управления интерфейсным портом для временного входа в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство,

д) либо, при определении того, что значение линии данных соответствует первому значению битов адреса подчиненного устройства, повторения действий б) и в) для дальнейших значений битов адреса подчиненного устройства до тех пор:

д1) пока не будет определено, что значение линии данных отлично от текущего значения битов адреса подчиненного устройства, осуществляя при этом временный вход в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство, или

д2) пока в линии данных не будет осуществлена установка всех битов адреса подчиненного устройства.

10. Устройство по п. 9, отличающееся тем, что интерфейсный порт входит в состояние ожидания по окончании установки адреса подчиненного устройства в линии данных.

11. Устройство по п. 9, отличающееся тем, что после действия г) контроллер повторяет действия б)-д).

12. Устройство по п. 9, отличающееся тем, что интерфейсный порт обеспечивает последовательную установку адреса подчиненного устройства в линии данных от наиболее значимого бита до наименее значимого бита.

13. Схема подчиненного устройства, соединенная с возможностью осуществления связи с интерфейсным портом, включающая энергонезависимую память для хранения адреса подчиненного устройства с целью осуществления связи с главным устройством по общей шине и выполненная с возможностью:

а) при приеме интерфейсным портом переданного от главного устройства во все несколько связанных с главным устройством несколько подчиненных устройств сигнала запроса, запрашивающего отправку в главное устройство соответствующего адреса каждого подчиненного устройства, соединенного с общей шиной,

б) управления интерфейсным портом для установки в линии данных логического состояния, соответствующего первому значению битов в адресе подчиненного устройства, соответствующем подчиненному устройству, так что линия данных либо переводится к первому значению, отражающему первое логическое состояние, одним или более подчиненными устройствами, либо, в случае, если она не переводится к первому значению одним или более подчиненными устройствами, освобождается ко второму значению, отражающему второе логическое состояние;

в) определения, соответствует ли значение линии данных первому значению битов; и

г) либо, при определении того, что значение линии данных отлично от первого значения битов адреса подчиненного устройства, управления интерфейсным портом для временного входа в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство,

д) либо, при определении того, что значение линии данных соответствует первому значению битов адреса подчиненного устройства, повторения действий б) и в) для дальнейших значений битов адреса подчиненного устройства до тех пор:

д1) пока не будет определено, что значение линии данных отлично от текущего значения битов адреса подчиненного устройства, осуществляя при этом временный вход в состояние ожидания до тех пор, пока другое подчиненное устройство не завершит отправку своего адреса подчиненного устройства в главное устройство, или

д2) пока в линии данных не будет осуществлена установка всех битов адреса подчиненного устройства.

| Камнерезная машина | 1984 |

|

SU1209878A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| US 7013355 B2, 14.03.2006 | |||

| US 7565470 B2, 21.07.2009 | |||

| RU 2001102787 A, 20.01.2003. | |||

Авторы

Даты

2015-12-20—Публикация

2010-11-11—Подача