ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится, в целом, к архитектуре запоминающего устройства (памяти), а более конкретно к архитектуре запоминающего устройства, которая снижает потребление динамической мощности.

УРОВЕНЬ ТЕХНИКИ

Запоминающее устройство представляет собой одну из вспомогательных инфраструктур современного компьютера и электронных устройств. Поскольку объем запоминающего устройства и плотность на единицу площади увеличиваются, меньшие по размеру устройства повсеместно становятся более пригодными к сложной и энергоемкой обработке, такой как обработка звука, видео, графики и т.п. Многие из таких небольших по размеру устройств существуют как независимые, карманные устройства, такие как мобильные телефоны, персональные цифровые помощники (PDA) и т.п. Поскольку большинство, если не все, из карманных устройств работают от аккумулятора, чтобы предоставлять основную мощность устройству, управление энергопотреблением имеет высокий приоритет в процессе проектирования карманного устройства, включающем в себя проектирование запоминающего устройства, которое будет использоваться в таких устройствах.

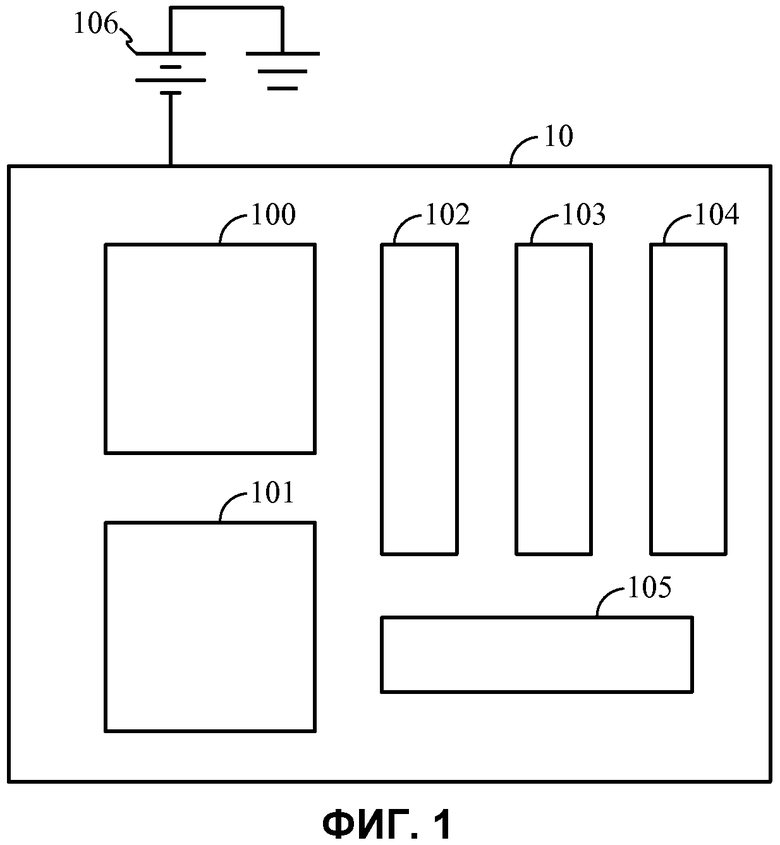

Фиг. 1 является схемой, иллюстрирующей стандартное полупроводниковое устройство 10. Полупроводниковое устройство 10 является устройством на интегральной микросхеме, содержащим сдвоенные процессоры, процессоры 100 и 101, и внутрикристальное запоминающее устройство 102-105. При проектировании полупроводникового устройства 10 расположение различных вентильных схем и компонентов зачастую сначала планируется в среде автоматизированного проектирования. Топографические и литографические планы формируются до того, как производитель полупроводников начинает фактическое изготовление полупроводникового устройства 10. Одним фактором, важным для проектирования, является физический контур или площадь покрытия в полупроводниковом материале для каждого компонента. Этот фактор влияет на размер и общий компоновочный план полупроводникового устройства 10. Компоновочный план, как правило, рассматривается как примерный план или общая площадь покрытия, занятая объединенными компонентами полупроводникового устройства 10.

Полупроводниковое устройство 10 питается от аккумулятора 106. Таким образом, полупроводниковое устройство 10 может быть множеством различных, специализированных процессорных систем в ряде различных устройств, таких как мобильные телефоны, PDA, карманные устройства или т.п. Другим фактором, как упомянуто выше, при проектировании полупроводникового устройства 10 являются характеристики энергопотребления каждого встроенного составляющего компонента, в том числе запоминающие устройства 102-105.

Мощность, потребляемая такими встроенными запоминающими устройствами, типично измеряется как комбинация динамической или активной мощности и мощности в режиме ожидания или статической мощности. Мощность в режиме ожидания/статическая мощность, как правило, считается током утечки в закрытом состоянии, который возникает, даже когда устройство считается выключенным. Используемая статическая мощность является проблемой в отрасли карманных или мобильных устройств, однако она, как правило, управляется посредством использования предварительных переключателей и оконечных переключателей. Динамическая мощность, однако, которая является потреблением мощности на основе взаимодействия приложения с запоминающим устройством, все еще считается областью, где может быть достигнута экономия энергии. Поскольку динамическая мощность относится к тому, как конкретное приложение осуществляет доступ к запоминающему устройству, зачастую рекомендуются точная настройка и управление для того, чтобы повлечь за собой уменьшение расхода энергии.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Различные характерные варианты осуществления изобретения относятся к компонентам запоминающего устройства, сконфигурированным, чтобы уменьшать потребление динамической мощности. Компонент запоминающего устройства включает в себя интерфейс запоминающего устройства для входных/выходных соединений, декодер, соединенный с интерфейсом запоминающего устройства, по меньшей мере, две подматрицы запоминающего устройства, которые включают в себя ячейки запоминающего устройства, разрядные шины и числовые шины и несколько мультиплексоров, соединенных с интерфейсом запоминающего устройства. Чтобы достигать уменьшения мощности, архитектура запоминающего устройства модифицируется так, что каждая подматрица включает в себя экземпляр всех разрядных шин, предназначенных для этого компонента запоминающего устройства, и часть из всех числовых шин, предназначенных для запоминающего устройства. Поскольку на длину разрядных шин влияет число числовых шин в каждой подматрице, разрядные шины оказываются короче, когда меньшее, чем полное число числовых шин, включено в каждую подматрицу. Укороченные разрядные шины уменьшают электрическую емкость, что уменьшает потребление динамической мощности. Мультиплексоры используются, чтобы способствовать выбору правильной подматрицы на основе, по меньшей мере, части адреса, полученного в интерфейсе запоминающего устройства.

Характерные варианты осуществления настоящего изобретения относятся к запоминающим устройствам, которые включают в себя множество интерфейсных портов и, по меньшей мере, две подматрицы, каждая из которых имеет экземпляр всех разрядных шин запоминающего устройства и часть из всех числовых шин запоминающего устройства. Запоминающее устройство также включает в себя декодер, соединенный с подматрицами и который выполнен с возможностью управлять числовыми шинами. Запоминающее устройство имеет мультиплексоры, соединенные с каждым из множества интерфейсных портов и декодером. Мультиплексоры функционируют, чтобы осуществлять выбор соответствующей подматрицы на основе, по меньшей мере, части принятого адреса ячейки запоминающего устройства.

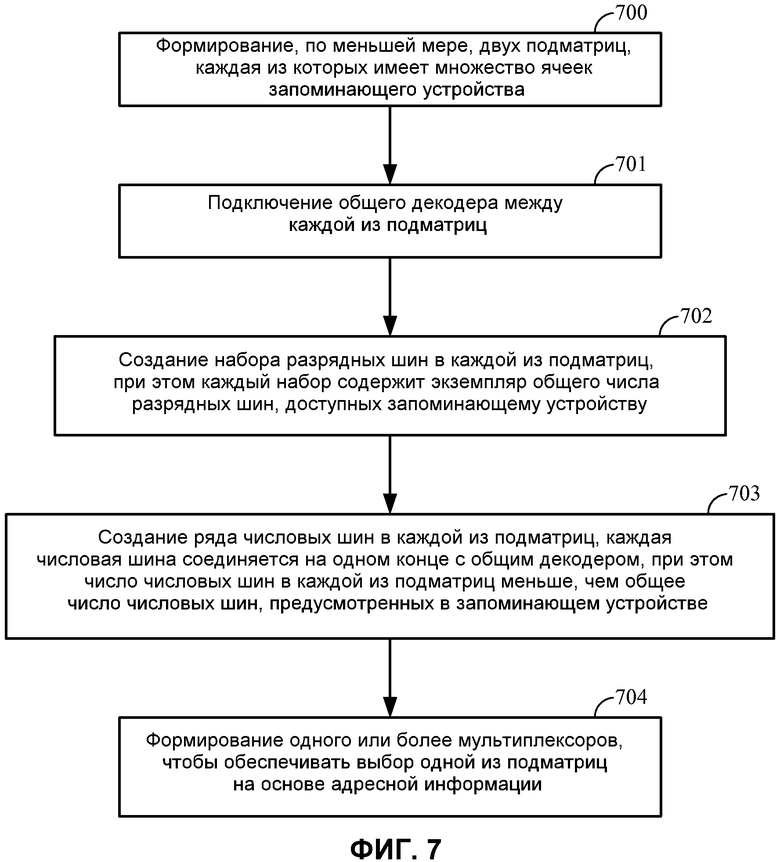

Дополнительные характерные варианты осуществления настоящего изобретения относятся к способам изготовления запоминающего устройства, которые включают в себя формирование, по меньшей мере, двух подматриц, каждая из которых имеет множество ячеек запоминающего устройства, подключение декодера между каждой из подматриц, создание набора разрядных шин в каждой из подматриц, при этом каждый набор имеет экземпляр из общего числа разрядных шин, доступных запоминающему устройству, и создание ряда числовых шин в каждой из подматриц, соединенных с одного конца с декодером. Число числовых шин в каждой подматрице меньше, чем общее число числовых шин, предусмотренных в запоминающем устройстве. Способ также включает в себя формирование одного или более мультиплексоров, соединенных с декодером и выполненных с возможностью обеспечивать выбор соответствующей подматрицы на основе информации об адресе запоминающего устройства.

Дополнительные характерные варианты осуществления настоящего изобретения относятся к запоминающим устройствам, которые состоят из интерфейса запоминающего устройства, декодера, соединенного с интерфейсом запоминающего устройства, первого блока запоминающего устройства, соединенного с декодером и включающего в себя первый экземпляр всех разрядных шин запоминающего устройства и первую часть набора из всех числовых шин запоминающего устройства, и второго блока запоминающего устройства, соединенного с декодером и включающего в себя второй экземпляр всех разрядных шин и вторую часть набора из всех числовых шин. Запоминающее устройство также включает в себя селектор, соединенный с интерфейсом запоминающего устройства и выполненный с возможностью обеспечивать выбор одного из первого или второго блоков запоминающего устройства в ответ на информацию, принятую в интерфейсе запоминающего устройства.

Вышеприведенное описание скорее широко очерчивает признаки и технические преимущества настоящего изобретения для того, чтобы последующее подробное описание изобретения могло быть лучше понято. Дополнительные признаки и преимущества изобретения будут описаны далее в данном документе, что формирует предмет изучения формулы изобретения. Специалистам в данной области техники должно быть понятно, что концепция и конкретный раскрытый вариант осуществления могут быть легко реализованы как основа для модификации или проектирования других структур для осуществления тех же целей настоящего изобретения. Также специалистам в данной области техники должно быть понятно, что такие эквивалентные конструкции не отступают от духа и рамок изобретения, которые изложены в прилагаемой формуле. Новые признаки, которые, как предполагается, будут характеристикой изобретения как для его организации, так и способа работы, вместе с дополнительными объектами изучения и преимуществами будут лучше понятны из последующего описания, когда рассматриваются совместно с сопровождающими чертежами. Должно быть определенно понятно, однако, что каждый из чертежей предоставлен только с целью иллюстрации и описания и не подразумевает определения ограничений настоящего изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Для более полного понимания настоящего изобретения сейчас дается ссылка на последующие подробные описания, взятые вместе с сопровождающими чертежами, на которых:

Фиг. 1 является схемой, иллюстрирующей стандартное полупроводниковое устройство;

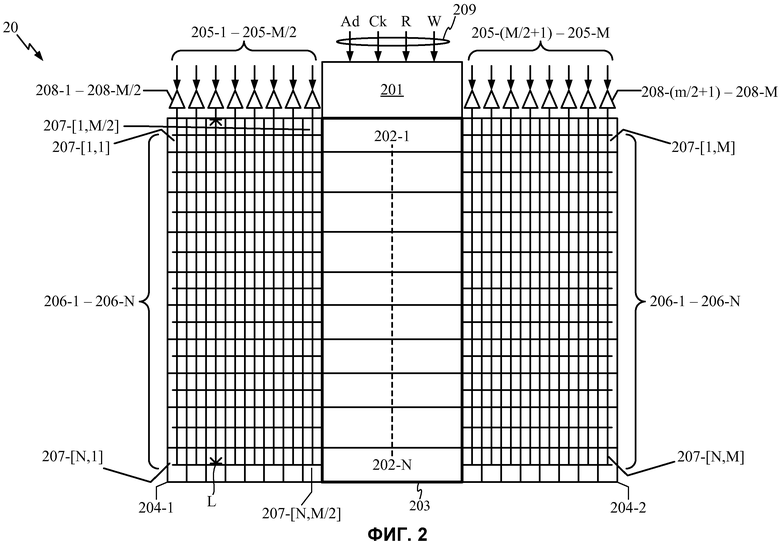

Фиг. 2 является блок-схемой, иллюстрирующей стандартное запоминающее устройство;

Фиг. 3 является блок-схемой, иллюстрирующей другое стандартное запоминающее устройство;

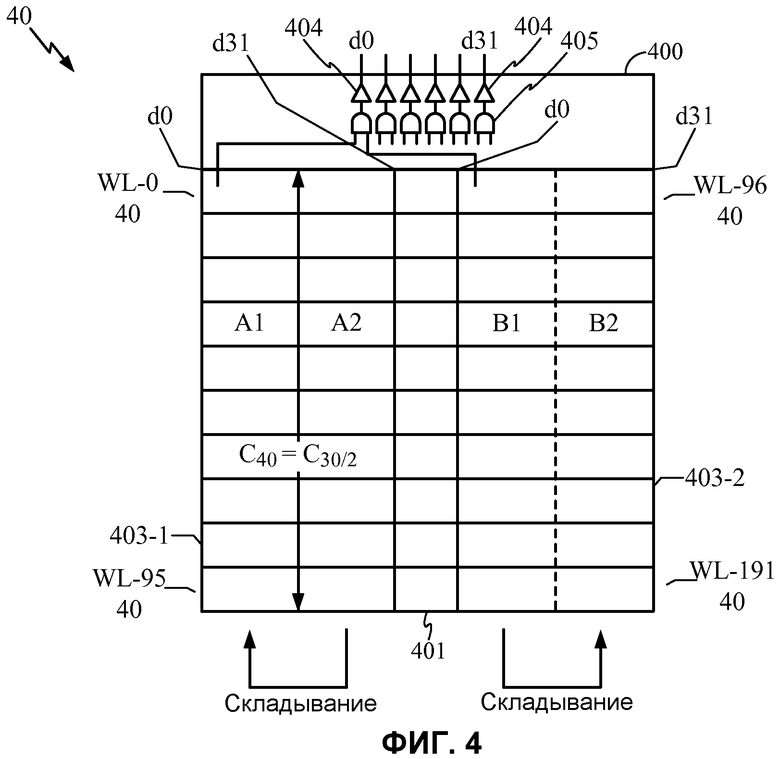

Фиг. 4 является блок-схемой, иллюстрирующей запоминающее устройство, сконфигурированное согласно принципам этого изобретения;

Фиг. 5 является блок-схемой, иллюстрирующей другое запоминающее устройство, сконфигурированное согласно принципам этого изобретения;

Фиг. 6 является графиком, сравнивающим динамическую мощность стандартного запоминающего устройства и одного варианта осуществления запоминающего устройства, сконфигурированного согласно принципам этого изобретения; и

Фиг. 7 является блок-схемой последовательности операций, иллюстрирующей пример блоков для реализации одного варианта осуществления принципов этого изобретения.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Динамическая мощность в запоминающем устройстве измеряется как комбинация емкости разрядной шины, переключаемой с некоторой скоростью, напряжения электропитания или размаха сигнала напряжения запоминающего устройства и частоты операций, т.е. частоты, с которой разрядная шина фактически переключается. Динамическая мощность запоминающего устройства может быть представлена следующей формулой:

где 'C' является общей электрической емкостью, переключаемой со скоростью 'α', 'ƒ' является частотой операции, а 'V' является напряжением электропитания структуры запоминающего устройства. Таким образом, для того, чтобы уменьшать динамическую мощность в структуре запоминающего устройства, любое из C, V, ƒ или α может быть уменьшено.

Уменьшение напряжения, частоты или скорости будет уменьшать динамическую мощность. Однако, уменьшение напряжения, частоты или скорости также уменьшает производительность. По существу, уменьшение электрической емкости рассматривается как более выгодное решение. Поскольку длина разрядной шины определяет электрическую емкость этой разрядной шины, электрическая емкость может быть уменьшена посредством укорачивания разрядной шины.

Обращаясь теперь к фиг. 2, показана блок-схема, иллюстрирующая стандартное запоминающее устройство 20. Запоминающее устройство 20 содержит предварительный декодер 201, декодер 203 и подматрицы 204-1 и 204-2. Подматрица 204-1 имеет разрядные шины 205-1 - 205-M/2 и числовые шины 206-1 - 206-N. На пересечении каждой из разрядных шин 205-1 - 205-M/2 и числовых шин 206-1 - 206-N находятся ячейки 207-[1,1] - 207-[N, M/2] запоминающего устройства. Аналогичным образом, подматрица 204-2 содержит ячейки 207-[1, (M/2 +1)] - 207-[N, M] запоминающего устройства, расположенные на пересечении разрядных шин 205-(M/2+1) - 205-M и числовых шин 206-1 - 206-N. Декодер 203 включает в себя драйверы 202-1 -202-N числовых шин, которые будут управлять выбранной одной из числовых шин 206-1 - 206-N в течение процедуры считывания и записи. Аналогичным образом, драйверы 208-1 - 208-M/2 разрядных шин и 208-(M/2+1) - 208-M управляют разрядными шинами 205-1 - 205-M/2 и 205-(M/2+1) - 205-M во время процедуры считывания и записи. Каждая из разрядных шин 205-1 - 205-M имеет длину 'L'.

Предварительный декодер 201 принимает входные данные из входного интерфейса 209, который, в примерном варианте осуществления, изображенном на фиг. 2, включает в себя входные порты Ad (адрес), Ck (тактовый сигнал), R (сигнал считывания) и W (сигнал записи). Предварительный декодер 201 обеспечивает первоначальное декодирование для входных данных. Декодер 203 использует первоначально декодированные выходные данные предварительного декодера 201. На основе принятых входных данных адреса декодер 203 находит и активирует соответствующую числовую шину посредством активации соответствующего из драйверов 202-1 - 202-N числовых шин. Это будет активировать каждую из ячеек запоминающего устройства на активированной числовой шине. Адрес будет дополнительно использоваться, чтобы идентифицировать соответствующую разрядную шину, чтобы активировать ее с помощью соответствующего одного из драйверов 208-1 -208-M/2 или 208-(M/2+1) - 208-M разрядных шин. В зависимости от того, выполняется ли чтение или запись, разрядная шина будет вызывать либо считывание данных из ячейки запоминающего устройства, либо запись в ячейку.

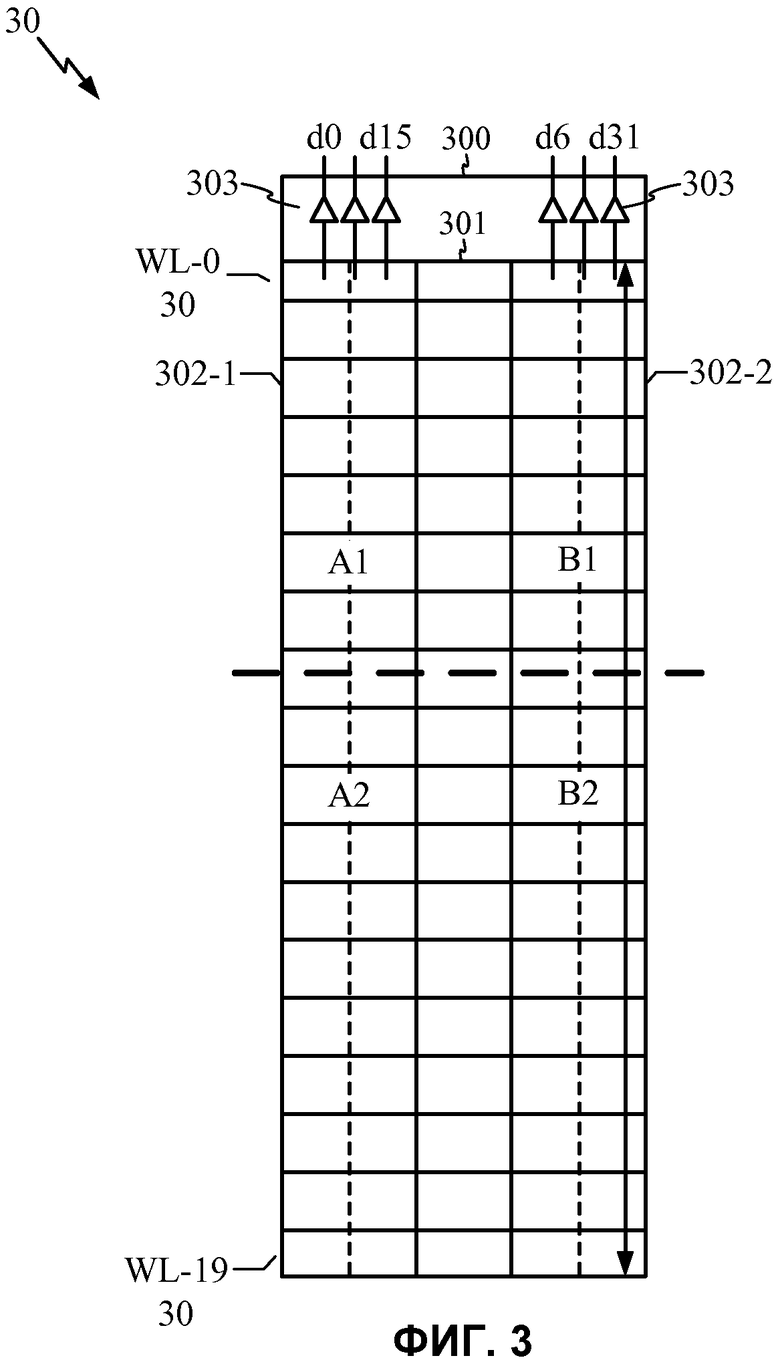

Фиг. 3 является блок-схемой, иллюстрирующей стандартное запоминающее устройство 30. Запоминающее устройство 30 аналогично по структуре запоминающему устройству 20 (фиг. 2) и включает в себя ячейки запоминающего устройства на пересечениях разрядных шин d0-d15, в подматрице 302-1, и разрядных шин d16-d31, в подматрице 302-2, с числовыми шинами WL30-0 - WL30-191. Конкретный вариант осуществления запоминающего устройства 30 имеет 32 разрядных шины. Длина адреса будет обычно определять максимальное число числовых шин, которые должны быть включены в устройство. Запоминающее устройство 30 использует 8-битный адрес и иллюстрирует 32 разрядные шины. 8-битный адрес достаточен, чтобы определять адресное пространство вплоть до 256 числовых шин. Однако не всегда необходимо использовать все числовые шины в максимальном адресном пространстве. Запоминающее устройство 30 иллюстрировано со 192 числовыми шинами в подматрицах 302-1 и 302-2.

Контур запоминающего устройства 30, которым является величина пространства или площади, взятой на полупроводниковом материале, формирует высокую прямоугольную форму. Эта форма создается посредством ряда числовых шин WL30-0 - WL30-191, по существу, превышающих число разрядных шин d0-d31. Это типичное соотношение размеров производимых в настоящее время запоминающих устройств создает длинные разрядные шины, которые, в свою очередь, имеют в результате большие электрические емкости (C30), которые повышают расход динамической мощности. Кроме того, с "высоким и тонким" прямоугольным контуром маршрутизация сигнала в другие части или блоки на полупроводниковой микросхеме может стать проблематичной, поскольку такая прямоугольная форма не максимизирует площадь покрытия на микросхеме. Такое запоминающее устройство может потенциально блокировать прохождение информационного сигнала по прямой возможной линии между двумя точками.

Прямоугольные контуры имеют дополнительные недостатки, относящиеся к физическим ограничениям производства при масштабировании таких устройств. При разработке в среде автоматизированного проектирования углы могут выглядеть очень острыми в графических пределах экрана компьютера. Более того, среда автоматизированного проектирования может позволять "искривление" компонентов или придание формы, чтобы соответствовать неоднородным открытым зонам полупроводниковой области. Однако когда настает время печати или литографии этих остроконечных или необычных форм на фактическом полупроводниковом материале, углы становятся закругленными. Просто очень трудно, если не невозможно, для современной технологии литографии создавать точно острые углы или сложные формы. Со спроектированной прямоугольной или неправильной формой, поскольку она становится все меньше и меньше в полупроводниковом материале, закругление в конечном счете создает объект, который вероятно не будет пригоден для печати и/или протравливания на полупроводниковом материале.

Фиг. 4 является блок-схемой, иллюстрирующей запоминающее устройство 40, сконфигурированное согласно одному варианту осуществления изобретения. Запоминающее устройство 40 имеет то же общее число разрядных шин (d0-d31) и числовых шин (WL21-0 - WL21-191), что и запоминающее устройство 30 (фиг. 3). Для того, чтобы уменьшать электрическую емкость разрядной шины в запоминающем устройстве 40, запоминающее устройство 40 образно "складывается" пополам. Обращаясь к запоминающему устройству 30 (фиг. 3), подматрица 302-1 может быть показана в двух половинах, A1 и A2. Когда запоминающее устройство "складывается" пополам, вместо A1 и A2, находящихся один поверх другого в высоком и тонком прямоугольнике с половиной разрядных шин и всеми числовыми шинами, подматрица 403-1 запоминающего устройства 40 конфигурируется с A1 рядом с A2 в более коротком прямоугольнике, имеющем экземпляр всех разрядных шин (d0-d31) и половину числовых шин (WL40-0 - WL40-95). Подматрица 403-2, аналогичным образом, конфигурирует B1 рядом с B2 с другим экземпляром всех разрядных шин (d0-d31) и другой половиной числовых шин (WL40-96 - WL40-191). Поскольку каждая из подматриц 403-1 и 403-2 имеет половину числовых шин, длина разрядных шин d0-d31 равна половине длины числовой шины запоминающего устройства 30 (фиг. 3). Половина длины разрядной шины соответствует половине электрической емкости, C40=C30/2, что соответствует половине динамической мощности. Более того, новый контур запоминающего устройства 40 имеет в результате, по существу, квадратную форму, которая гораздо более выгодна для разработки компонентов.

Следует отметить, что различные варианты осуществления настоящего изобретения могут также концептуально рассматриваться как имеющие подматрицу 403-1, содержащую A1 рядом с B1. Обе области A1 и B1 совместно используют одинаковые адреса числовых шин, но различные - в разрядных шинах. Аналогичным образом, области A2 и B2 совместно используют одинаковые адреса числовых шин, но имеют различные разрядные шины, таким образом, они могут также быть представлены себе как находящиеся рядом друг с другом в подматрице 403-2.

Предварительный декодер 400 включает в себя драйверы 404 разрядных шин и мультиплексоры 405. Мультиплексоры 405 используются при определении того, к какой подматрице осуществлять доступ, когда инициируется процесс считывания или записи. С помощью ввода идентификатора разрядной шины и, по меньшей мере, части адреса ячейки запоминающего устройства мультиплексоры 405 будут определять, осуществлять ли доступ к подматрице 403-1 или к 403-2. Например, разрядная шина d0, в зависимости от диапазона адресов, может быть либо в подматрице 403-1, либо в 403-2. Рассматривая конфигурацию, иллюстрированную на фиг. 4, если диапазон адресов равен 95 или менее, тогда подматрица 403-1 будет выбрана мультиплексорами 405. Иначе, если диапазон адресов равен 96 или больше, тогда подматрица 403-2 будет выбрана мультиплексорами 405.

Для того, чтобы осуществлять логику для мультиплексоров 405, рассматривается деление запоминающего устройства 40. Со 192 числовыми шинами в варианте осуществления, изображенном на фиг. 4, используется 8-битный адрес (биты "A0-A7", где 7 является старшим значащим битом (MSB)). Деление запоминающего устройства 40 имеет место в середине общего числа числовых шин, предусмотренного для запоминающего устройства 40, или по числу 95. Следовательно, сначала выполняется определение относительно того, сколько MSB из 8-битного адреса будут позволять постоянное прерывание в точке перехода между числовой шиной 95, WL40-95, в подматрице 403-1, и числовой шиной 96, WL40-96, в подматрице 403-2. Один MSB не может использоваться для запоминающего устройства 40, чтобы определять, к какой подматрице осуществлять доступ. Как отмечено выше, поскольку запоминающее устройство 40 использует 8-битный адрес, общее возможное адресное пространство равно 256. Если один MSB, A7, был использован, вычисленный переход от доступа к подматрице 403-1 к доступу к подматрице 403-2 будет происходить в 128-й числовой шине, WL40-127 (т.е. 27) вместо 95, как сконфигурировано запоминающее устройство 40. Таким образом, рассматриваемый MSB будет вызывать неправильное сопоставление подматриц 403-1 и 403-2. Мультиплексоры 405 будут продолжать осуществлять прямой доступ в подматрицу 403-1 для числовых шин 96-128 (WL40-95 - WL40-127), даже если физическое местоположение этих числовых шин находится в подматрице 403-2 в запоминающем устройстве 40. Для того, чтобы получать точный переход в числовой шине 95 в конкретном примере, иллюстрированном на фиг. 4, следующая логическая формула управляет выбором посредством мультиплексоров 405:

Следовательно, мультиплексоры 405 будут подавать сигнал выбора подматрицы 206-1 до тех пор, пока они не обнаружат, что три (3) MSB адреса - это 0-1-1 или два (2) MSB - это 1-0. Когда встречается любая из этих двух комбинаций, мультиплексоры 405 будут подавать сигнал выбора подматрицы 206-2.

Следует отметить, что в различных дополнительных и/или альтернативных вариантах осуществления настоящего изобретения конкретная логическая формула, используемая мультиплексорами, будет отражать разделение, выбранное между подматрицами, и общее число числовых шин, используемых конкретным запоминающим устройством. Например, если запоминающее устройство использует 256 числовых шин и 8-битный адрес, и выбираются две подматрицы, каждая из которых имеет точно половину общего числа числовых шин, тогда только MSB, A7, будет рассматриваться. В таком варианте осуществления, если A7 равен 0, тогда требуемая разрядная шина будет в первой подматрице, иначе требуемая разрядная шина будет во второй подматрице.

На практике не весь доступный объем запоминающего устройства может быть необходим. Во втором примере, где используется 8-битный адрес, и только 128 числовых шин необходимы, чтобы обеспечивать достаточный объем запоминающего устройства, мультиплексоры будут следить за последними двумя MSB, A7 и A6, с помощью логической функции:

Следует дополнительно отметить, что длина разрядных шин в любой конкретной подматрице в различных дополнительных и/или альтернативных вариантах осуществления настоящего изобретения может быть дополнительно уменьшена посредством дополнительного "складывания" или конфигурирования. Варианты осуществления настоящего изобретения не ограничиваются исключительно конфигурацией, изображенной на фиг. 4.

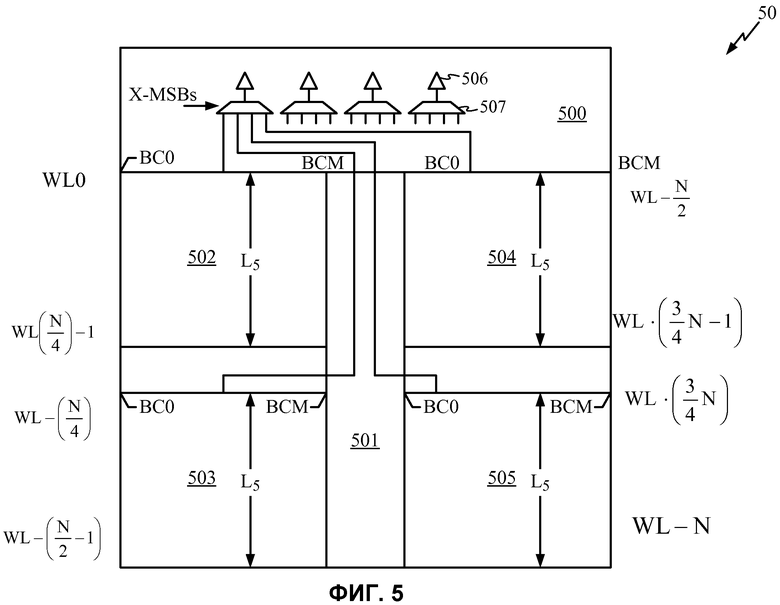

Фиг. 5 является блок-схемой, иллюстрирующей запоминающее устройство 50, сконфигурированное согласно одному варианту осуществления изобретения. Запоминающее устройство 50 состоит из предварительного декодера 500, включающего в себя драйверы 506 разрядных шин и мультиплексоры 507, общий декодер 501 и подматрицы 502-505. Вместо "складывания" подматриц запоминающего устройства один раз, как показано на фиг. 4, запоминающее устройство 50 конфигурируется со своими подматрицами, "сложенными" множество раз, например дважды, получая в результате четыре подматрицы, подматрицы 502-505. Как отмечено ранее, "складывание" фактически означает конфигурирование каждой из подматриц 502-505, чтобы они имели полный набор разрядных шин, BL-0 - BL-M, но только часть общего числа адресуемых числовых шин, WL-0 - WL-N. Как иллюстрировано на фиг. 5, подматрица 502 имеет числовые шины WL-0 - WL-(N/4 - 1), подматрица 503 имеет числовые шины WL-(N/4) - WL-(N/2-1), подматрица 504 имеет числовые шины WL-(N/2) - WL-(3/4 N - 1), а подматрица 505 имеет числовые шины WL-(3/4 N - 1) - WL-N.

Дополнительно разделяя число числовых шин в каждой из подматриц 502-505, соответствующие разрядные шины, BL-0 - BL-M, являются более короткими, т.е. длиной L5. В сравнении с запоминающим устройством 20 (фиг. 2) L5=L/4. Таким образом, для запоминающего устройства 50 будет требоваться одна четверть электрической емкости и одна четверть динамической мощности по сравнению с запоминающим устройством 20 (фиг. 2). По сравнению с запоминающим устройством 40 (фиг. 4), если каждая из переменных является такой же, электрическая емкость запоминающего устройства 50 на основе длины L5 будет равна 1/2 C40.

Предварительный декодер 500 управляет доступом к дополнительным подматрицам через мультиплексоры 507. С помощью входных данных о числе разрядных шин и адреса числовой шины мультиплексоры 507 способны точно выбирать правильную одну из подматриц 502-505. Мультиплексоры 507 рассматривают данный набор MSB из адреса числовой шины. Конкретное число MSB, которое должно быть рассмотрено, будет определяться на основе числа числовых шин, запланированных для запоминающего устройства, а также точек разделения, запланированных для каждой подматрицы.

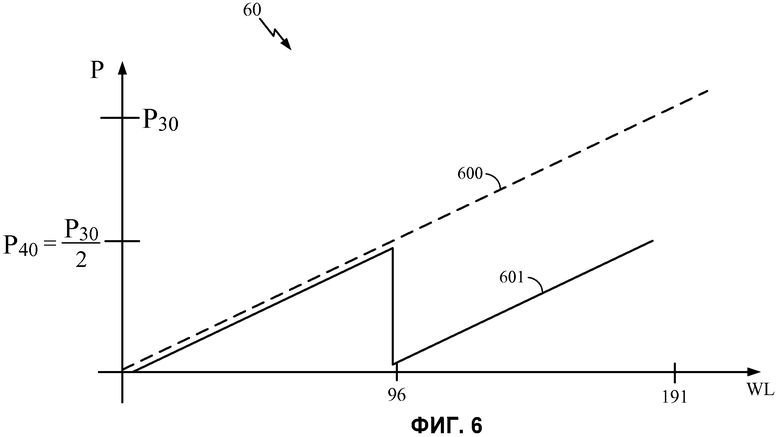

Фиг. 6 является графиком, представляющим динамическую мощность запоминающего устройства 30 на фиг. 3 по сравнению с динамической мощностью запоминающего устройства 40 на фиг. 4. График 600 представляет динамическую мощность, когда к ячейкам запоминающего устройства с увеличивающимися числовыми шинами осуществляется доступ в запоминающем устройстве 30. Когда адрес числовой шины становится больше для ячейки запоминающего устройства, к которой осуществляется доступ в запоминающем устройстве 30, длина разрядных шин d0-d15 становится больше, что в результате приводит по существу к линейному потреблению динамической мощности от 0 до P30. График 601 представляет потребление динамической мощности, когда к ячейкам запоминающего устройства осуществляется доступ с увеличивающимися числовыми шинами в запоминающем устройстве 40. Как можно увидеть на графике 601, потребление динамической мощности запоминающего устройства 40 начинает увеличиваться, по существу, линейно тем же образом, что и график 600. Однако, когда достигается числовая шина 96, динамическая мощность падает опять до уровня, аналогичного числовой шине 0, поскольку длина разрядной шины падает непосредственно до первоначальной длины. Максимальная мощность для запоминающего устройства 40 показана как P40, которая эквивалентна P30/2 перед падением в числовой шине 96. График 601 затем дополнительно показывает, что динамическая мощность устойчиво увеличивается опять до достижения последней числовой шины, числовой шины 191. Здесь опять, в числовой шине 191, потребление динамической мощности запоминающего устройства 40 равно P40 или P30/2. Таким образом, общая динамическая мощность для запоминающего устройства 40, сконфигурированного согласно одному варианту осуществления настоящего изобретения, равна приблизительно половине динамической мощности запоминающего устройства 30.

Фиг. 7 является блок-схемой последовательности операций, иллюстрирующей примерные блоки, реализованные для создания структуры запоминающего устройства, сконфигурированного согласно одному варианту осуществления настоящего изобретения. На этапе 700 формируются, по меньшей мере, две подматрицы, каждая из которых имеет множественные ячейки запоминающего устройства. Общий декодер подключается, на этапе 701, между каждой из подматриц. На этапе 702 набор разрядных шин создается в каждой из подматриц, при этом каждый набор содержит экземпляр общего числа разрядных шин, доступных запоминающему устройству. Ряд числовых шин создается в каждой из подматриц на этапе 703. Каждая числовая шина соединяется на одном конце с общим декодером. Число числовых шин в каждой подматрице меньше, чем общее число числовых шин, предусмотренных в запоминающем устройстве. На этапе 704 один или более мультиплексоров формируется и конфигурируется, чтобы осуществлять выбор одной из подматриц на основе адресной информации.

Хотя настоящее изобретение и его преимущества были описаны подробно, следует понимать, что различные изменения, замены и переделки могут быть выполнены в нем без отступления от духа и рамок изобретения, которые определены в прилагаемой формуле. Более того, рамки настоящей заявки не подразумевают ограничение конкретными вариантами осуществления процесса, машины, производства, химического соединения, средства, способов и этапов, описанных в спецификации. Как обычный специалист в данной области техники легко поймет из раскрытия настоящего изобретения, процессы, машины, производство, химические соединения, средства, способы или этапы, существующие в настоящее время, или которые будут разработаны позже, которые выполняют, по существу, ту же функцию или достигают, по существу, того же результата, что и соответствующие варианты осуществления, описанные в данном документе, могут быть использованы согласно настоящему изобретению. Соответственно, прилагаемая формула подразумевает включение в свои рамки таких процессов, машин, производства, химических соединений, средств, способов или этапов.

Изобретение относится к вычислительной технике. Технический результат заключается в снижении потребления динамической мощности. Запоминающее устройство, содержащее множество интерфейсных портов; множество драйверов разрядных шин; множество разрядных шин соответствующих множеству драйверов разрядных шин; по меньшей мере, две подматрицы, причем каждая из упомянутых, по меньшей мере, двух подматриц содержит экземпляр из множества разрядных шин упомянутого запоминающего устройства и часть из множества числовых шин упомянутого запоминающего устройства; декодер, соединенный с упомянутыми, по меньшей мере, двумя подматрицами и упомянутым множеством портов ввода/вывода, причем упомянутый декодер выполнен с возможностью управлять упомянутым множеством числовых шин; и множество мультиплексоров, соответствующих множеству разрядных шин; при этом каждый мультиплексор функционирует, чтобы связывать с его соответствующей разрядной шиной только один экземпляр из его соответствующей разрядной шины на основе адреса ячейки запоминающего устройства, принятого в одном или более из упомянутого множества интерфейсных портов. 2 н. и 8 з.п. ф-лы, 7 ил.

1. Запоминающее устройство, содержащее:

множество интерфейсных портов;

множество драйверов разрядных шин;

множество разрядных шин, соответствующих множеству драйверов разрядных шин;

по меньшей мере, две подматрицы, причем каждая из упомянутых, по меньшей мере, двух подматриц содержит экземпляр из множества разрядных шин упомянутого запоминающего устройства и часть из множества числовых шин упомянутого запоминающего устройства;

декодер, соединенный с упомянутыми, по меньшей мере, двумя подматрицами и упомянутым множеством портов ввода/вывода, причем упомянутый декодер выполнен с возможностью управлять упомянутым множеством числовых шин; и

множество мультиплексоров, соответствующих множеству разрядных шин;

при этом каждый мультиплексор функционирует, чтобы связывать с его соответствующей разрядной шиной только один экземпляр из его соответствующей разрядной шины на основе адреса ячейки запоминающего устройства, принятого в одном или более из упомянутого множества интерфейсных портов.

2. Запоминающее устройство по п.1, в котором упомянутая часть содержит одну половину упомянутого множества числовых шин упомянутого запоминающего устройства.

3. Запоминающее устройство по п.1, дополнительно содержащее: предварительный декодер, подключенный между упомянутым множеством интерфейсных портов и упомянутым декодером, при этом упомянутый предварительный декодер обрабатывает упомянутую информацию для работы упомянутого декодера.

4. Запоминающее устройство по п.1, в котором каждый из упомянутого одного или более из упомянутого множества интерфейсных портов содержит, по меньшей мере, два из порта адреса, порта тактовых сигналов, порта считывания и порта записи.

5. Запоминающее устройство по п.1, в котором физическая конфигурация упомянутых, по меньшей мере, двух подматриц, упомянутого декодера и упомянутого мультиплексора обеспечивает контур упомянутого запоминающего устройства, который, по существу, является прямоугольным.

6. Запоминающее устройство по п.1, в котором упомянутое множество числовых шин меньше, чем общее число числовых шин, адресуемых посредством упомянутого запоминающего устройства.

7. Запоминающее устройство по п.1, в котором набор старших значащих битов (MSB) упомянутого адреса используется упомянутым мультиплексором, чтобы выбирать упомянутую одну из упомянутых, по меньшей мере, двух подматриц.

8. Запоминающее устройство по п.7, в котором упомянутый набор MSB выбирается на основе упомянутой части из упомянутого множества числовых шин в упомянутых, по меньшей мере, двух подматрицах.

9. Запоминающее устройство по п.7, в котором упомянутый набор MSB содержит минимальное число MSB, которые конкретно идентифицируют точку перехода между упомянутыми, по меньшей мере, двумя подматрицами.

10. Запоминающее устройство, содержащее:

множество интерфейсных портов;

множество драйверов разрядных шин;

множество разрядных шин, соответствующих множеству драйверов разрядных шин;

по меньшей мере, две подматрицы, причем каждая из упомянутых, по меньшей мере, двух подматриц содержит экземпляр из множества разрядных шин упомянутого запоминающего устройства и часть из множества числовых шин упомянутого запоминающего устройства;

декодер, соединенный с упомянутыми, по меньшей мере, двумя подматрицами и упомянутым множеством портов ввода/вывода, причем упомянутый декодер выполнен с возможностью управлять упомянутым множеством числовых шин; и

средство для связи только одного экземпляра разрядной шины с его соответствующей разрядной шиной на основе адреса ячейки запоминающего устройства, принятого в одном или более из упомянутого множества интерфейсных портов.

| US 5898637 А, 27.04.1999 | |||

| US 4590588 А, 20.05.1986 | |||

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

| US 4739497 A, 19.04.1988 | |||

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1990 |

|

RU2089943C1 |

Авторы

Даты

2012-12-27—Публикация

2009-06-19—Подача