УРОВЕНЬ ТЕХНИКИ

[0001] Протоколы последовательной шины данных, например, протокол межинтегральных схем (I2C или I2C, и это обозначение принято здесь) и протокол последовательного периферийного интерфейса (SPI) позволяют по меньшей мере одной ‘ведущей’ интегральной схеме (IC) осуществлять связь с по меньшей мере одной ‘подчиненной’ IC, например, через шину. I2C и другие протоколы связи передают данные согласно периоду тактового сигнала. Например, может генерироваться сигнал напряжения, где значение напряжения ассоциировано с данными. Например, значение напряжения выше x вольт может указывать логическую “1”, тогда как значение напряжения ниже x вольт может указывать логическую “0”, где x является заранее определенным численным значением. Благодаря генерированию надлежащего напряжения в каждом из нескольких периодов тактового сигнала, данные могут передаваться через шину или другую линию связи.

[0002] Некоторые системы 2D и 3D печати включают в себя один или более сменных компонентов устройства печати, например, контейнеров для материала печати (например, картриджей для струйной печати, картриджей для тонера, чернильниц, источников строительного материала и т.д.), головок струйной печати в сборе, и пр. В некоторых примерах, логическая схема, ассоциированная со сменным(и) компонентом(ами) устройства печати, осуществляет связь с логической схемой устройства печати, в котором они установлены, например, передавая информацию, например, их идентификатора, возможностей, статуса и пр.

[0003] В некоторых примерах эти передачи используют передачи I2C. В таких примерах, ведущая IC в общем случае может обеспечиваться как часть устройства печати (которая может именоваться ‘главной’), и сменный компонент устройства печати будет содержать ‘подчиненную’ IC, хотя это справедливо не во всех примерах. Может существовать множество подчиненных IC, подключенных к линии связи I2C (например, контейнеров разных цветов агента печати). Подчиненная(ые) IC может/могут содержать логическую схему для осуществления операций с данными до ответа на запросы от логической схемы системы печати.

[0004] В некоторых примерах это может предназначаться для обнаружения физического положения подчиненных устройств, которые присоединены вдоль последовательной шины. Например, можно предположить, что устройства, например, сменные компоненты устройства печати, занимают некоторую указанную физическую позицию в устройстве печати. Например, в устройстве печати с устройствами подачи чернил, присоединенными к последовательной шине, может существовать ожидаемая позиция, например, для черного картриджа, желтого картриджа, голубого картриджа и малинового картриджа, каждый из которых может иметь конкретный адрес согласно протоколу связи. Путем обнаружения, были ли чернильные картриджи конкретного цвета неправильно установлены или обменялись местами, можно предотвращать печать неверными или предназначенными цветами. Предыдущим патентным раскрытием является патентная заявка US за номером публикации US 2011/0029705.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0005] Неограничительные примеры будут описано ниже со ссылкой на прилагаемые чертежи, в которых:

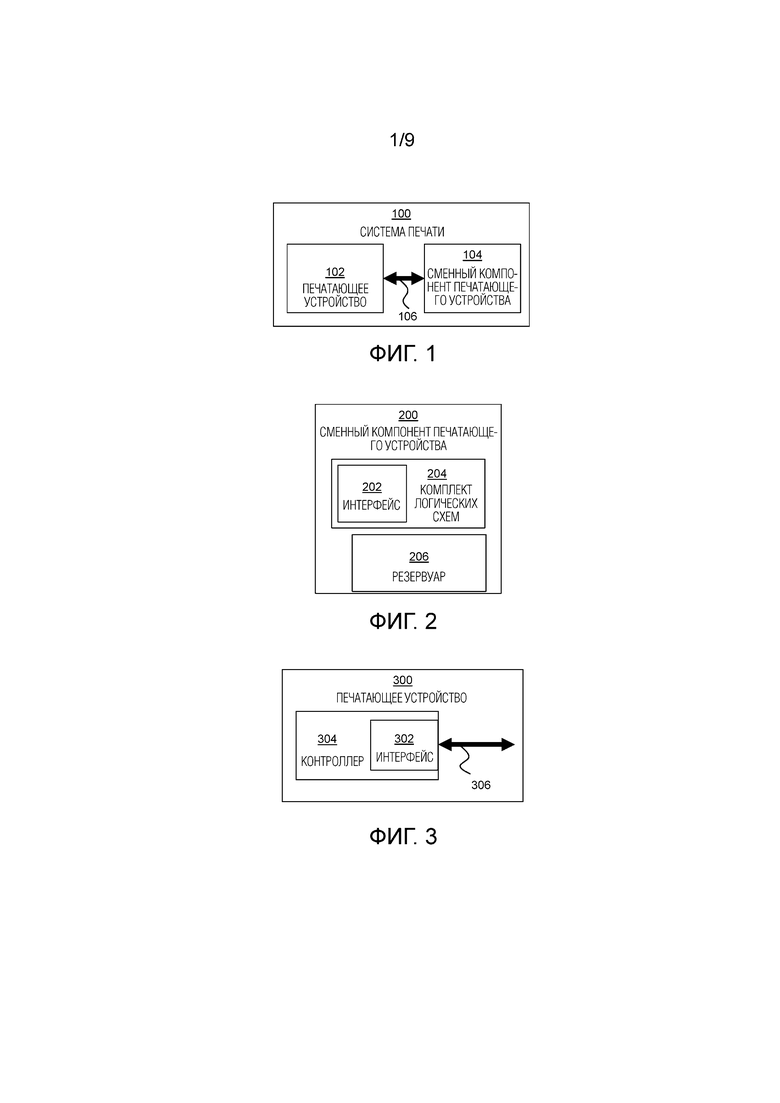

[0006] фиг. 1 - пример системы печати;

[0007] фиг. 2 - пример сменного компонента устройства печати;

[0008] фиг. 3 - пример устройства печати;

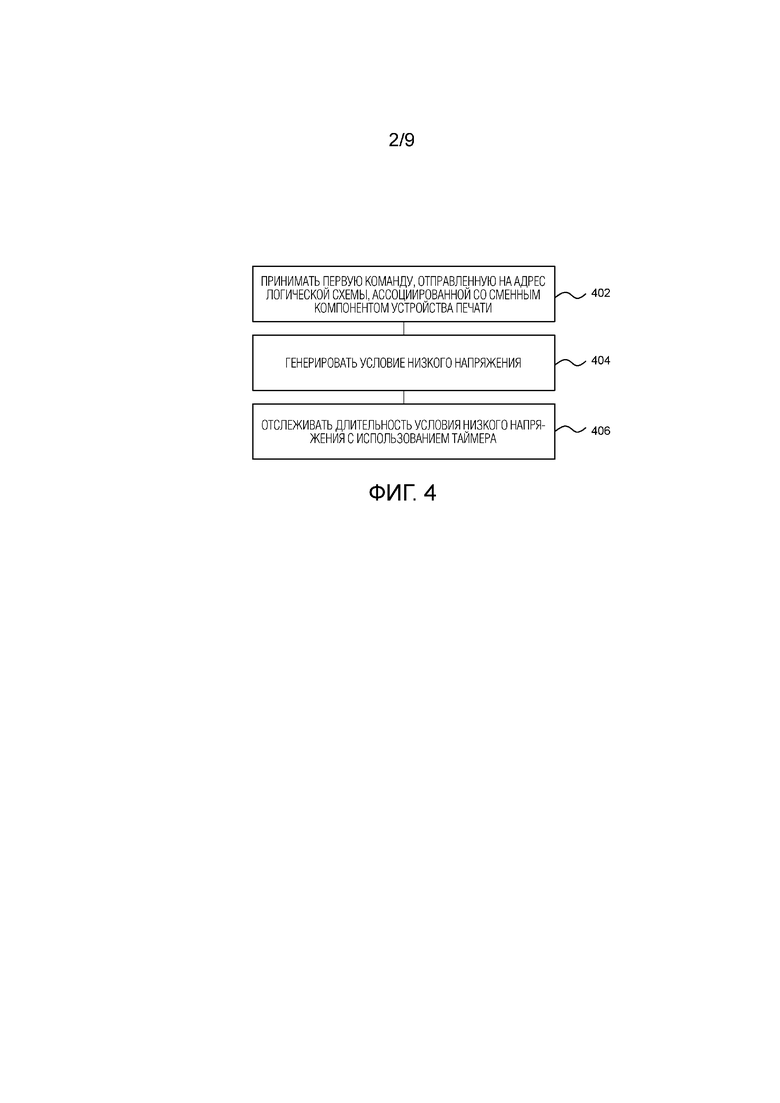

[0009] фиг. 4 - пример способа эксплуатации логической схемы, ассоциированной со сменным компонентом устройства печати;

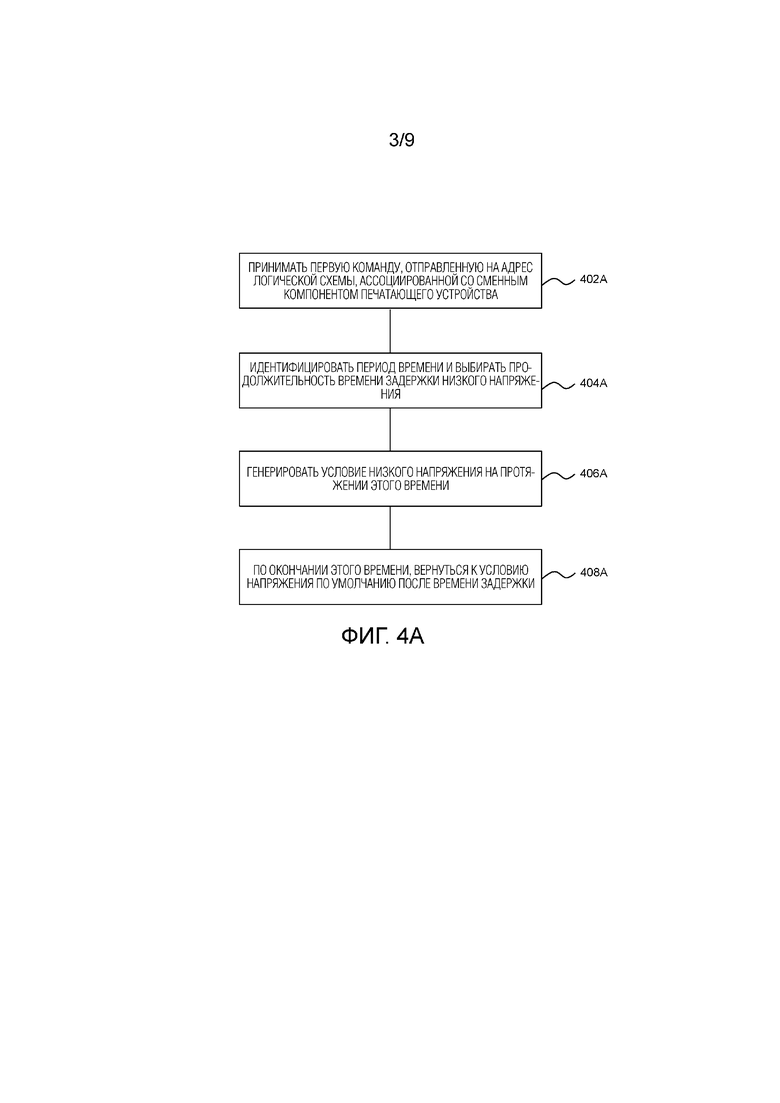

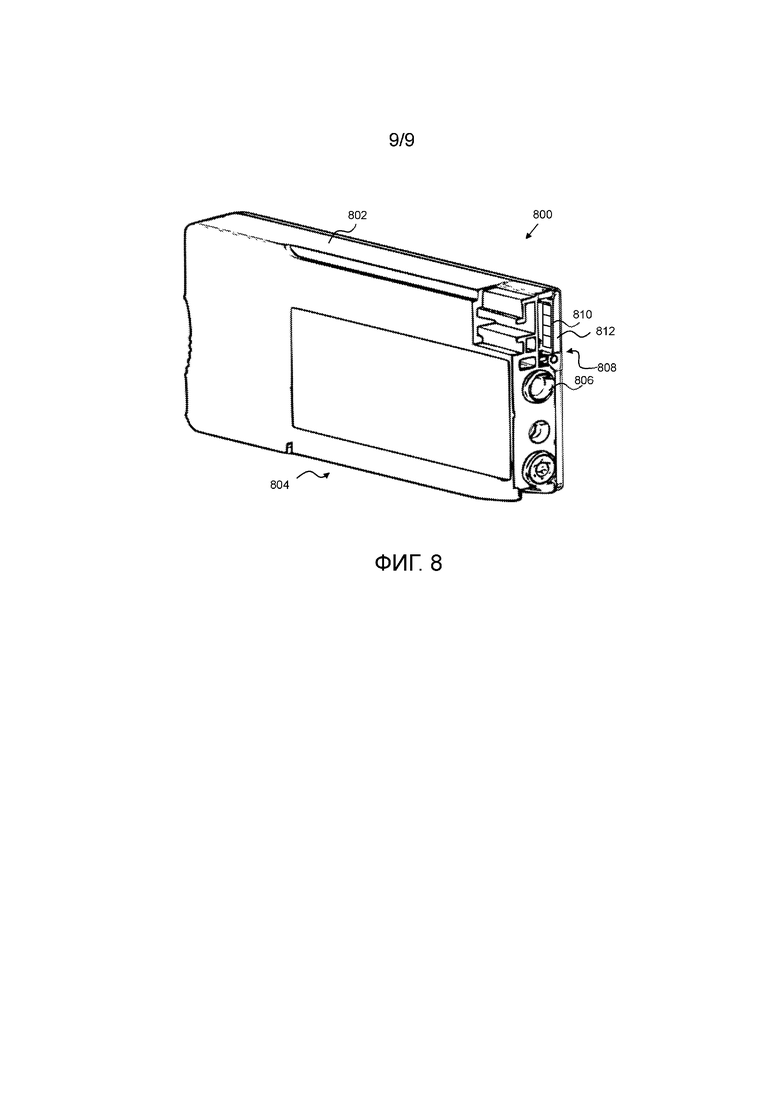

[0010] фиг. 4A - другой пример способа работы логической схемы, ассоциированной со сменным компонентом печатающего устройства;

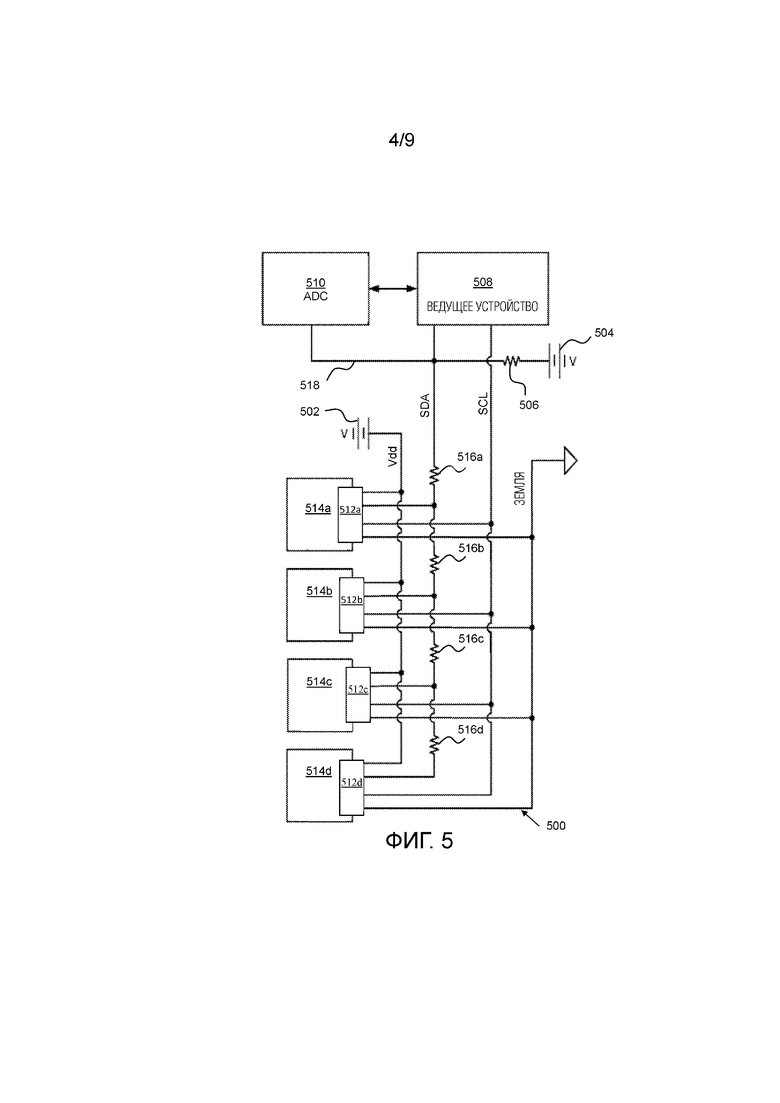

[0011] фиг. 5 - схематический пример логической схемы устройства печати и логической схемы, ассоциированной со сменными компонентами устройства печати, подключенными к последовательной шине;

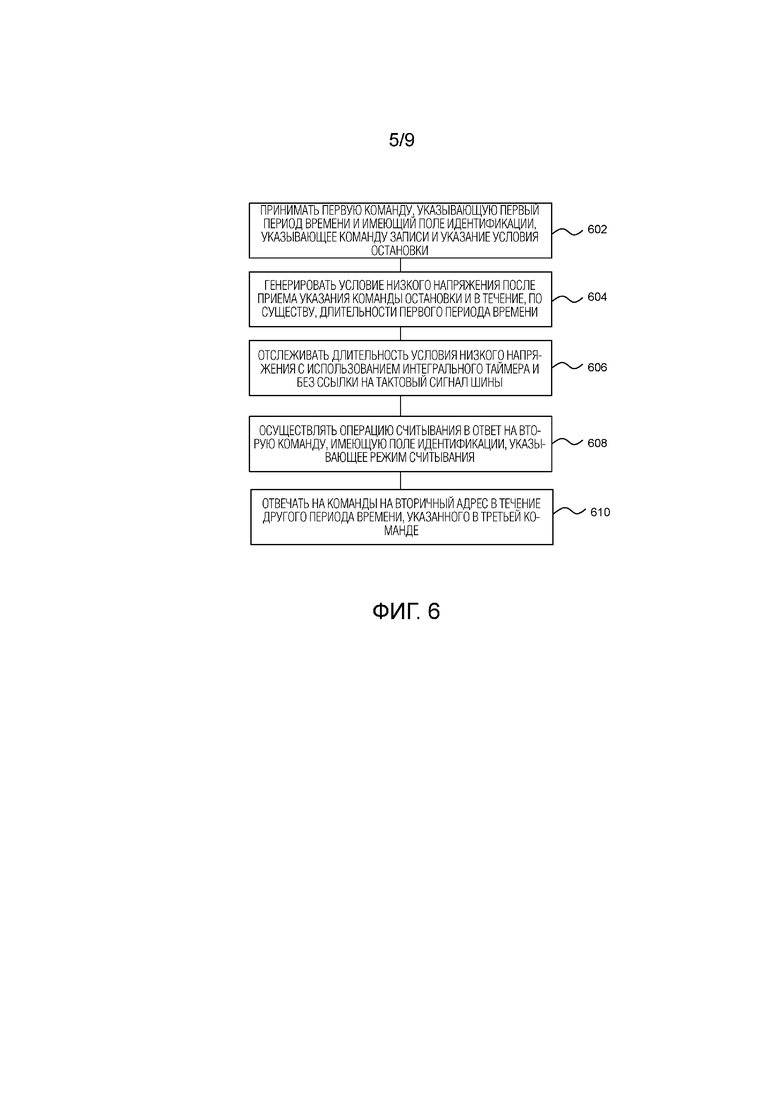

[0012] фиг. 6 - пример другого способа операции логической схемы, ассоциированной со сменным компонентом устройства печати;

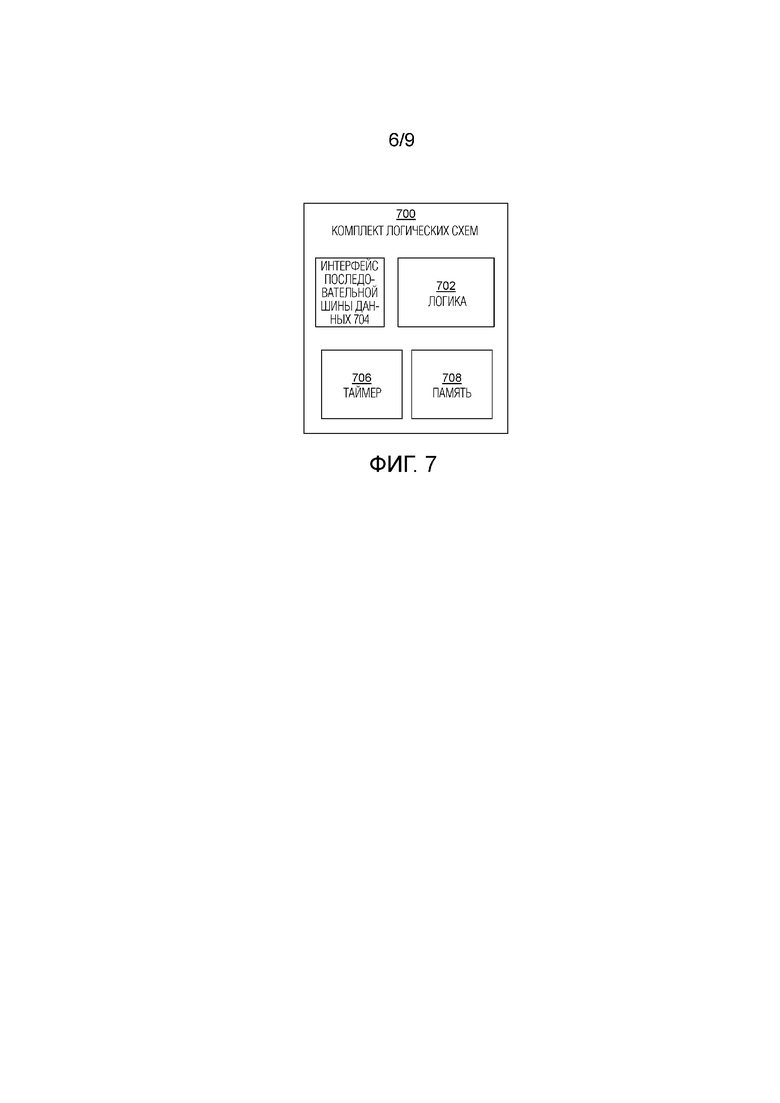

[0013] фиг. 7 - пример комплекта логических схем;

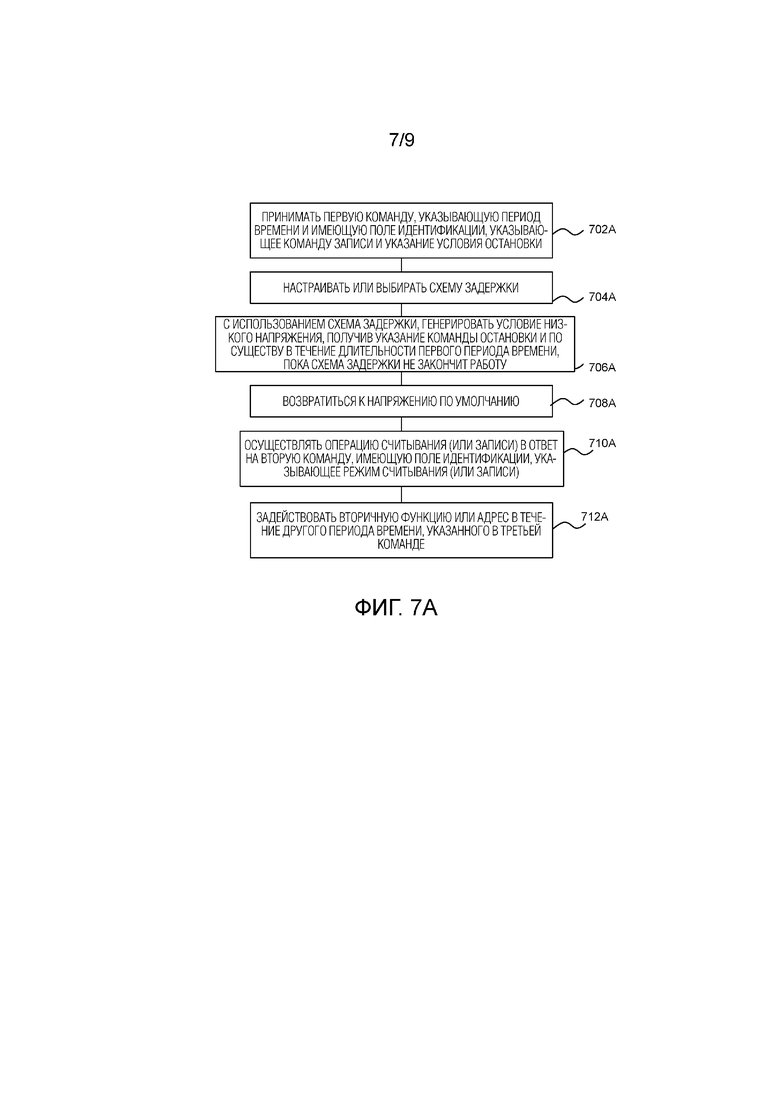

[0014] фиг. 7A - другой пример способа работы логической схемы, ассоциированной со сменным компонентом печатающего устройства;

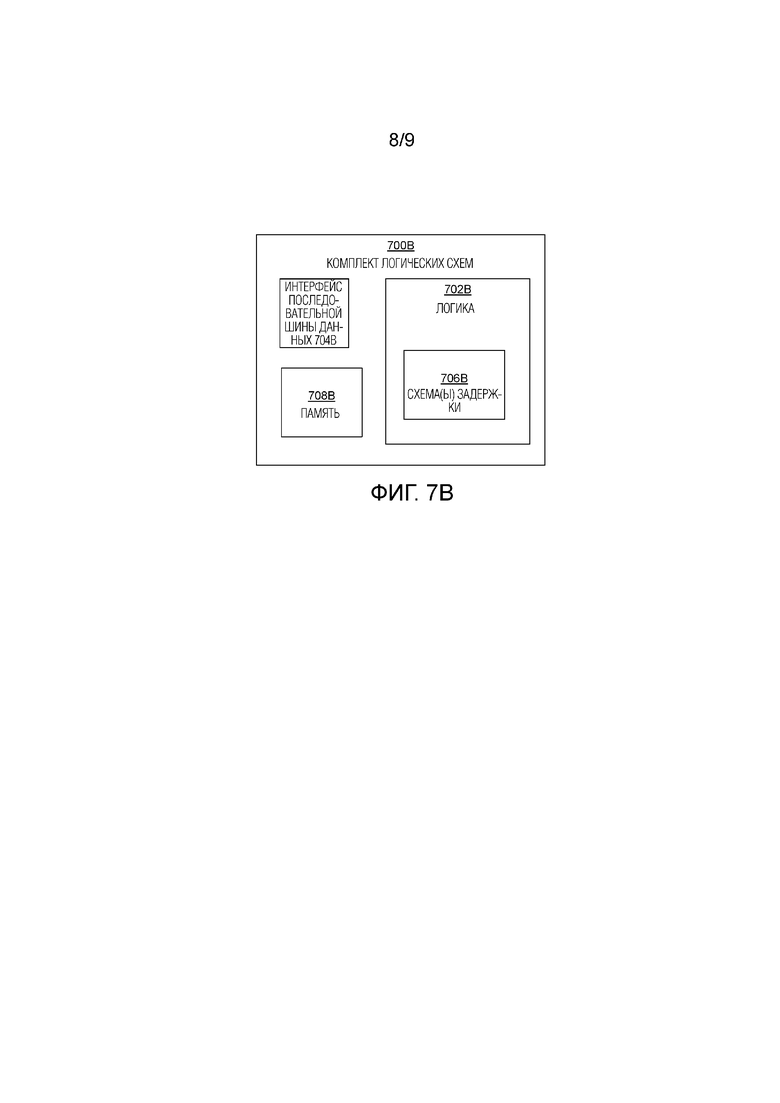

[0015] фиг. 7B - другой пример комплекта логических схем; и

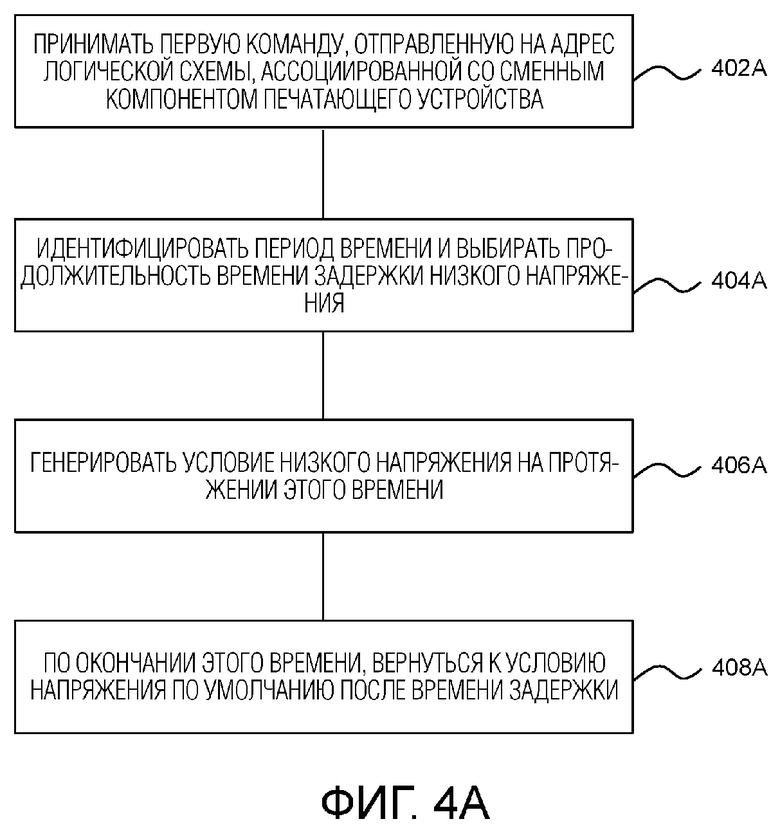

[0016] фиг. 8 - пример сменного компонента устройства печати, содержащего комплект логических схем.

ПОДРОБНОЕ ОПИСАНИЕ

[0017] Некоторые примеры применений передач I2C описаны здесь в контексте устройства печати. Однако не все примеры ограничиваются такими применениями, и по меньшей мере некоторые из установленных здесь принципов можно использовать в других контекстах.

[0018] В некоторых примерах логическая схема в устройстве печати может принимать информацию от логической схемы, ассоциированной со сменным компонентом устройства печати, через интерфейс связи и/или может отправлять команды на сменный компонент устройства печати. Иллюстративные устройства печати включают в себя устройство формирования двухмерных изображений и устройство трехмерного аддитивного производства, например, струйные принтеры, принтеры на сухом тонере, принтеры на жидком тонере, струйные 3D принтеры с порошковой подушкой и т.д. Иллюстративные компоненты устройства печати включают в себя чернильницы; бутылки для чернил; печатающие головки; картриджи для струйной печатающей головки; резервуары для сухого тонера; картриджи для сухого тонера; фотопроводниковые картриджи; картриджи обработки; резервуары для жидкого тонера; агенты трехмерной печати, включающие в себя чернила, стимулирующие агенты, адгезивы, ингибиторы и т.д.; строительный материал для трехмерной печати; служебные компоненты устройства печати; и/или любой другой компонент, который может быть сменным в отношении главного устройства печати и может содержать или не содержать материал печати. В этом изобретении, материал печати или агент печати может включать в себя чернила, сухой или жидкий тонер, агенты трехмерной печати, трехмерный строительный материал (пластик, металл и т.д.), волокна и т.д. Вышеупомянутые резервуары могут содержать окрашенный материал печати.

[0019] Передачи между устройством печати и сменными компонентами устройства печати, установленными в устройстве, могут обеспечивать различные функции. Например, идентификатор, функциональные возможности и/или статус сменного компонента устройства печати и/или логической схемы, ассоциированной с ними, могут передаваться на логическую схему устройства печати через интерфейс связи. Например, логическая схема, ассоциированная с (или обеспеченная на или в) контейнером для агента печати может передавать идентификатор, например, серийный номер и/или бренд продукта, и/или идентификационные характеристики, например, цвет, карту цветов, рецепт реконструкции карты цветов, максимальный объем агента печати или функциональные возможности на устройство печати, в котором она установлена, см., например, международные патентные заявки №№ WO2016028272, WO2018/009235 или WO2015016860 или европейский патент № EP0941856. Статус, например, уровень заполнения, может обеспечиваться через интерфейс связи, например, таким образом, что устройство печати может генерировать указание уровня заполнения пользователю. В некоторых примерах процесс удостоверения может осуществляться устройством печати. Например, устройство печати может удостоверяться в том, что сменный компонент устройства печати исходит из авторизованного источника, чтобы гарантировать его качество. Например, логическая схема, ассоциированная со сменным компонентом устройства печати может сохранять секретные ключи и может быть выполнена с возможностью генерации сеансовых ключей, идентификаторов сеансовых ключей и/или кодов аутентификации сообщений для генерирования аутентифицированных криптографических ответов на принтер, см., например, патент США № 9619663. Логика также может включать в себя дополнительные механизмы аутентификации, например, специализированное оборудование для вычисления ответов в заранее заданных, относительно коротких, временных окнах, см., например, патент США № 9561662. В некоторых примерах процесс удостоверения может включать в себя контроль целостности, чтобы гарантировать, что сменный компонент устройства печати и/или логическая схема, ассоциированная с ним, функционирует ожидаемым образом.

[0020] В свою очередь, инструкции для осуществления задания могут отправляться на логическую схему компонента устройства печати от логической схемы, ассоциированной с устройством печати, через интерфейс связи. Например, они могут включать в себя инструкции для осуществления функции аутентификации или шифрования, функции регистрации уровня материала печати, заданий на печать или других заданий.

[0021] В по меньшей мере некоторых из описанных ниже примеров описан комплект логических схем. Комплект логических схем может быть ассоциирован со сменным компонентом устройства печати, например, присоединен к нему, или располагаться по меньшей мере частично в его корпусе, и выполнен с возможностью обмениваться данными с контроллером устройства печати через шину, обеспеченную как часть устройства печати.

[0022] Используемый здесь термин ‘комплект логических схем’ относится к одной или более логическим схемам, которые могут быть соединены между собой или связаны друг с другом с возможностью обмена данными. Когда обеспечено более одной логической схемы, они могут быть инкапсулированы как единый блок, или могут быть инкапсулированы по отдельности, или могут не быть инкапсулированы, или возможна некоторая комбинация вышеперечисленных вариантов. Каждый комплект может быть выполнен с возможностью осуществления связи через интерфейс последовательной шины.

[0023] В некоторых примерах каждый комплект логических схем снабжен по меньшей мере одним процессором и памятью. В одном примере комплект логических схем может представлять собой, или может функционировать как, микроконтроллер или защищенный микроконтроллер. В ходе эксплуатации комплект логических схем может присоединяться к сменному компоненту устройства печати или объединяться с ним.

[0024] В некоторых примерах комплект логических схем может отвечать на запросы (или команды) различных типов от главного устройства (например, устройства печати). Запрос может содержать запрос данных, например, идентификационной и/или аутентификационной информации (например, запрос ‘чтение’). В других примерах запрос может содержать запрос ‘запись’. Другой запрос от главного устройства может быть запросом на осуществление действия, например, осуществление по меньшей мере одного измерения или выполнение задания на печать и т.п. Запрос другого типа может быть запросом действия обработки данных.

[0025] В примере взаимодействия главное устройство может отправлять команду на комплект логических схем, ассоциированный со сменным компонентом устройства печати, который может выполнять команду и загружать полученные данные в память (В некоторых примерах в буфер и/или конкретный регистр памяти). Главное устройство может отправлять дополнительную команду для считывания ответа, так что ответ передается в виде последовательных данных по соединенной шине. Такой процесс можно использовать, например, для получения данных, хранящихся в памяти комплекта логических схем. Например, первый запрос может быть запросом идентификатора этого комплекта, и может приводить к загрузке идентификатора комплекта в буфер памяти. Последующий запрос ‘чтение’ может приводить к чтению данных из буфера и их передаче как последовательного сигнала данных.

[0026] В по меньшей мере некоторых примерах множество таких комплектов логических схем (каждый из которых может быть ассоциирован с тем или иным сменным компонентом устройства печати) может быть подключено к шине I2C.

[0027] На фиг. 1 приведен пример системы 100 печати. Система 100 печати содержит устройство 102 печати, ассоциированное со сменным компонентом 104 устройства печати по линии 106 связи. Хотя для наглядности, сменный компонент 104 устройства печати показан внешним по отношении к устройству 102 печати, в некоторых примерах сменный компонент 104 устройства печати может быть заключен в устройстве печати. Устройством 102 печати может быть устройство 2D печати или устройство 3D печати любого типа.

[0028] Сменный компонент 104 устройства печати может, например, содержать расходный ресурс устройства 102 печати или компонент, срок службы которого, вероятно, меньше (в некоторых примерах значительно меньше), чем у устройства 102 печати. Например, в компоненте 104 устройства печати могут физически храниться чернила, тонер, агент 3D печати или строительный порошок 3D печати, и он может предназначаться для замены после существенного расходования. Сменный компонент 104 устройства печати может, например, содержать контейнер или картридж материала печати (который может быть контейнером строительного материала для 3D печати, или контейнером для жидкого агента печати для 2D или 3D печати). В некоторых примерах сменный компонент 104 устройства печати может содержать печатающую головку или другой раздаточный компонент. Хотя в этом примере показан единый сменный компонент 104 устройства печати, В других примерах может существовать множество сменных компонентов устройства печати, например, содержащих контейнеры для агентов печати разных цветов, печатающие головки (которые могут быть объединены с контейнерами), и т.п.

[0029] В некоторых примерах линия 106 связи может содержать последовательную шину, например шину с возможностями I2C или совместимую (далее именуемую шиной I2C).

[0030] На фиг. 2 показан пример сменного компонента 200 устройства печати, который может обеспечивать сменный компонент 104 устройства печати, показанный на фиг. 1. Сменный компонент 200 устройства печати содержит интерфейс 202 данных, интегрированный в комплект 204 логических схем. В ходе эксплуатации сменного компонента 200 устройства печати, комплект 204 логических схем декодирует данные, принятые через интерфейс 202 данных. Интерфейс 202 данных может содержать интерфейс I2C.

[0031] В некоторых примерах комплект 204 логических схем может быть дополнительно выполнен с возможностью кодировать данные для передачи через интерфейс 202 данных. В некоторых примерах может существовать более чем один интерфейс 202 данных, обеспеченный для единого компонента 200.

[0032] В некоторых примерах комплект 204 логических схем может быть выполнен с возможностью действовать как ‘подчиненный’ в передачах I2C.

[0033] Сменный компонент 200 устройства печати в этом примере содержит резервуар 206 материала печати, который может содержать любой из примеров материалов печати, рассмотренных выше.

[0034] На фиг. 3 показан пример устройства 300 печати. Устройство 300 печати может обеспечивать устройство 102 печати, показанное на фиг. 1. Устройство 300 печати содержит контроллер 304, который содержит интерфейс 302 для ассоциирования со сменным компонентом устройства печати и шиной 306 связи. Контроллер 304 содержит логическую схему. В некоторых примерах интерфейс 302 является интерфейсом I2C, и шина 306 связи является шиной связи с возможностями I2C.

[0035] В некоторых примерах контроллер 304 может быть выполнен с возможностью действовать как главное или ведущее устройство в передачах I2C. Контроллер 304 может генерировать и отправлять команды на по меньшей мере один сменный компонент 200 устройства печати, и может принимать и декодировать принятые оттуда ответы.

[0036] Такое устройство 102, 300 печати и сменный(е) компонент(ы) устройства печати 104, 200 и/или их комплект логических схем могут изготавливаться и/или продаваться по отдельности. В примере пользователь может получать устройство 102, 300 печати и владеть устройством 102, 300 несколько лет, тогда как в эти годы может приобретаться множество сменных компонентов 104, 200 устройства печати, например, по мере использования агента печати при создании печатной продукции. Поэтому может существовать по меньшей мере степень прямой и/или обратной совместимости между устройством 102, 300 печати и сменными компонентами 104, 200 устройства печати.

[0037] На фиг. 4 и 4A приведен пример способа, который может осуществляться комплектом логических схем, ассоциированный со сменным компонентом устройства печати. В некоторых примерах этот способ может осуществляться таким образом, что устройство печати, в котором установлен сменный компонент устройства печати, может определять физическое положение сменного компонента устройства печати. Тогда как предусмотренные здесь способы могут использоваться с протоколами связи, отличными от I2C, например, протоколом последовательного периферийного интерфейса (SPI), можно отметить, что в протоколах I2C, множество устройств соединены последовательно на единой шине без какого-либо средства немедленного определения или объявления их физического положения или порядка. Однако, при рассмотрении, например, SPI, существуют две конфигурации проводки, параллельные и последовательно подключенные. В конфигурации параллельной проводки, существует отдельная линия, предназначенная для каждой ‘подчиненной’ логической схемы и в конфигурации последовательного подключения, устройства последовательно соединены проводами в конкретном порядке, поэтому их относительная позиция может удостоверяться некоторым другим способом. Поэтому предусмотренный здесь способ может иметь конкретную выгоду с протоколами, в которых в противном случае трудно проверять физическое положение устройства, например, I2C. Однако это не является ограничением.

[0038] В примере, приведенном на фиг. 4, блок 402 содержит прием первой команды, отправленной на адрес логической схемы, ассоциированной со сменным компонентом устройства печати, через последовательную шину данных, например, шину I2C. В некоторых примерах первая команда может указывать рабочий режим. В некоторых примерах первая команда может указывать период времени. Адрес может быть адресом шинного интерфейса I2C, хранящимся и/или зашитым в логической схеме/ комплекте логических схем. Первая команда может отправляться по адресу контроллером устройства печати. Первая команда может быть заранее определенной командой.

[0039] Блок 404 содержит генерирование, логической схемой, условия низкого напряжения на последовательной шине данных. Как описано более подробно ниже, это может содержать, по сути дела, обеспечение соединения между последовательной шиной данных (и, в частности, линией данных последовательной шины данных) и землей. В одном примере низкое напряжение является номинальной землей или опорным напряжением, например, приблизительно 0 В. Как будет также описано ниже, низкое напряжение ниже, чем в состоянии или при условии высокого или принятого по умолчанию напряжения.

[0040] Блок 406 содержит отслеживание длительности условия низкого напряжения с использованием таймера логической схемы. Таймер может содержать интегральный таймер, внутренний по отношению к логической схеме, например, содержащий схему сопротивление-емкость (RC), выполненную с возможностью действовать как таймер, логические вентили, снабженные счетчиком, кристаллическим или кольцевым генератором, схему фазовой автоматической подстройки частоты (также известную как контур фазовой синхронизации) и т.п., или любой таймер, который логически образует часть логической схемы, обеспеченную совместно со сменным компонентом устройства печати. Таймер может обеспечивать внутренний тактовый сигнал, который обеспечивается даже в отсутствие тактового сигнала на последовательной шине данных. Таймер может считать и, таким образом позволяет определять длительность периода таймера, указанного в первой команде.

[0041] Таймер может предназначаться для измерения периода времени команды. В ряде случаев таймер предназначается для измерения времени независимо от других, общего назначения, циклов в действующем комплекте логических схем I2C, например, тактов I2C и/или циклов обработки центрального процессора главного устройства или логической схемы. Например, таймер может быть выполнен с возможностью считать быстрее тактовой частоты и может начинать и останавливать отсчет независимо от хронирования тактового сигнала. Таймер может быть выполнен с возможностью считать независимо от быстродействия центрального процессора логической схемы/главного устройства, например, имеющей/го номинальные спецификации, не связанные с центральным процессором.

[0042] В других примерах логическая схема/ комплект логических схем может отслеживать период времени на основании отслеживания внешнего таймера, например, внешнего тактового генератора, или путем отслеживания внешних или внутренних волновых сигналов, осциллирующих сигналов и т.д., которые в ряде случаев могут быть пригодны для определения длительности периода времени. В одном примере таймер комплекта логических схем может быть таймером, имеющим беспроводную связь с логической схемой (и таким образом, один таймер может совместно использоваться более чем одной логической схемой).

[0043] Способ может содержать освобождение шины, или удаление условия низкого напряжения, в конце периода времени таким образом, что последовательная шина данных предполагает другое, высокое и/или по умолчанию, состояние или условие напряжения). Это может, например, содержать прерывание соединения с землей. За пределами периода времени, например, до и после длительности периода времени, инициированного в ответ на первую команду, логическая схема/ комплект логических схем может генерировать условие высокого напряжения. Альтернативно, такое условие высокого напряжения может быть условием по умолчанию, созданным путем включения ‘нагрузочного повышающего’ резистора на шине, как описано ниже.

[0044] Для рассмотрения, например, шины данных I2C, она содержит две линии связи: последовательную линию данных (SDA) и последовательную линию тактового сигнала (SCL). SDA и SCL могут быть двусторонними линиями, подключенными к положительному напряжению питания через источник тока или нагрузочный повышающий резистор.

[0045] В отсутствие сигнала на линии (т.е. в отсутствие тактового сигнала на SCL и/или в отсутствие сигнала данных на линии данных) обе линии могут по умолчанию находиться в состоянии высокого напряжения. Конкретное значение напряжения в состоянии высокого напряжения зависит от многих эксплуатационных факторов, но в некоторых примерах может составлять несколько вольт, например, примерно от 3 до 6 вольт. Поэтому, хотя в целом ‘высокое’ напряжение может быть относительно низким, оно является высоким по сравнению с состоянием ‘низкого’ напряжения шины, которое может быть, например, меньше 1 вольта.

[0046] Ведущее/главное устройство (например, в настоящем контексте, схема обработки или контроллер устройства печати в котором установлено сменное устройство печати) может генерировать тактовый сигнал, переводя напряжение линии SCL в низкое состояние, например, с использованием конфигурации свободного стока чтобы, фактически, обеспечивать заземление. Например, переключатель (например, полевой транзистор) может активироваться (закрываться) для предписания состояния низкого напряжения, затем повторно открываться, чтобы нагрузочный повышающий резистор на линии мог переводить напряжение в высокое состояние. В других примерах можно использовать конфигурацию свободного коллектора, в которой биполярный транзистор (BJT) можно использовать для аналогичного результата. Хронирование нагружения и освобождения обеспечивает тактовый сигнал, который управляется схемой обработки ведущего устройства.

[0047] Для передачи данных либо ведущее устройство, либо подчиненное (в этом примере логическая схема, ассоциированная со сменным устройством печати) может выборочно управлять напряжением на SDA аналогичным образом, понижая его (например, обеспечивая соединение с землей) или позволяя ему ‘плавать высоко’ (например, прерывая соединение с землей). Это хронируется тактовым сигналом: согласно протоколу I2C, состояние линии SDA, когда линия SCL находится в высоком состоянии, обеспечивает по меньшей мере один бит данных. Обычно, если линия SDA находится в низком (и устойчивом) состоянии, когда SCL находится в высоком состоянии, это означает двоичный 0, и если линия SDA находится в высоком (и устойчивом) состоянии, когда SCL находится в высоком состоянии, это означает двоичную 1, хотя очевидно, в данной системе, это может изменяться.

[0048] В одном примере способа, показанного на фиг. 4, вместо обеспечения сигнала данных, который хронируется для совпадения с линией SCL, находящейся в высоком состоянии, состояние линии SCL не рассматривается. Вместо этого напряжение понижается в течение длительности, которая отслеживается таймером логической схемы (опять же, например, путем обеспечения соединения с землей), затем ‘освобождается’, или может предполагаться по умолчанию в высоком состоянии (например, путем прерывания этого соединения). Действительно, в некоторых вариантах осуществления, может не существовать тактового сигнала, обеспеченного ведущим устройством в течение по меньшей мере части, и В некоторых примерах всей длительности условия низкого напряжения.

[0049] Как упомянуто выше, этот способ может использоваться в контексте обнаружения физического положения сменных компонентов устройства печати, как описано со ссылкой на фиг. 5. Например, этот способ может использоваться при определении, установлен ли сменный компонент устройства печати, например, источник материала печати в назначенной позиции. В некоторых примерах это может устранять или снижать использование ‘механической кодировки’, при этом сменный компонент устройства печати имеет конкретную форму, согласующуюся с ‘прорезью’, имеющей ответную форму. Это в свою очередь снижает сложность изготовления, поскольку сменные компоненты устройства печати, например, с разными типами материала печати, например, разными цветами, могут иметь общую физическую конструкцию. В некоторых примерах можно использовать комбинацию механической кодировки и описанных здесь методов. Например, согласно некоторым вариантам применения, черный (K) краситель обычно раздается чаще, чем другие цвета (например, в контекстах, где часто печатается текста), картриджи для подачи черного материала печати могут быть физически крупнее, чем, например, картриджи для подачи голубого, малинового или желтого материала печати в наборе картриджей CMYK. Поэтому, в некоторых примерах для черного картриджа можно использовать механическую кодировку (например, за счет того, что размер черного картриджа намного больше, чем у картриджей других цветов), что может быть достаточно, чтобы гарантировать размещение черных картриджей в предназначенной ‘прорези’, и описанные здесь методы можно использовать, чтобы гарантировать, что картриджи других цветов располагаются в нужных местах.

[0050] В некоторых примерах функция отслеживания периода времени, например, с помощью таймера, можно использовать в других целей. Например, комплект логических схем может быть выполнен с возможностью иметь более одного адреса I2C, например для облегчения связи с разными логическими схемами или разными функциями, содержащимися в комплекте, по одному и тому же шинному интерфейсу I2C комплекта логических схем (например, через одну и ту же единую контактную площадку обмена данными, и одну и ту же единую контактную площадку питания, одну и ту же единую контактную площадку заземления и/или одну и ту же единую контактную площадку тактового сигнала). Например, передачи считывания/записи данных по умолчанию и генерация и/или регистрация низкого напряжения может быть связана с первичным адресом комплекта логических схем, который является вышеупомянутым адресом комплекта. Комплект логических схем может быть дополнительно выполнен с возможностью временно “переключаться” (т.е. отвечать на адресованные ему команды) на вторичный, например, новый и/или временный, адрес I2C после приема соответствующей команды. Такому переключателю адреса I2C может предшествовать команда, включающая в себя второй период времени. Этот второй период времени может отслеживаться комплектом логических схем, например, с использованием таймера, для определения времени, в течение которого комплект логических схем должен отвечать на команды, принятые по вторичному адресу. Например, логическая схема может быть связана с первичным (например, “первым” или “принятым по умолчанию”) адресом в течение первого периода времени и вторичным адресом в течение второго периода времени, причем первый и второй период времени могут отслеживаться с использованием таймера. В этом контексте, первый период времени может быть любым периодом времени за пределами второго периода времени. В некоторых практических примерах этот второй период времени может быть длиннее, чем период времени для генерирования условия низкого напряжения, для обеспечения достаточного времени для передачи данных по вторичному адресу, причем этот период времени может быть длиннее, чем, например, обнаружение положения установки сменного компонента устройства печати этого изобретения. Активация по меньшей мере еще одного другого адреса может содержать задание (например, запись, перезапись или изменение), или инициирование задания другого адреса (например, нового, временного второго адреса), например, путем записи другого адреса в участке памяти, который указывает адрес комплекта логических схем.

[0051] Логическая схема может быть выполнена с возможностью обеспечения первого набора ответов, или работы в первом режиме, в ответ на инструкции, отправленные на первый адрес и обеспечения второго набора ответов, или работы во втором режиме, в ответ на инструкции, отправленные на вторичный адрес. Другими словами, адрес может инициировать разные функции, обеспеченные схемой. В некоторых примерах первый набор ответов доступен в ответ на команды, отправленные на первый адрес и не в ответ на команды, отправленные на вторичный адрес, и второй набор ответов доступен в ответ на команды, отправленные на вторичный адрес и не в ответ на команды, отправленные на первый адрес. В некоторых примерах первый набор из первого набора ответов может криптографически аутентифицироваться (например, сопровождаться аутентификацией сообщений, или иным образом криптографически ‘подписываться’ и/или шифроваться) и второй набор ответов не подлежит криптографической аутентификации. В некоторых примерах, например, второй адрес может использоваться для осуществления доступа к другим ячейкам или датчикам и т.п., которые могут обеспечиваться на логической схеме или иначе связываться с ней.

[0052] Благодаря многоцелевому характеру функции отслеживания периода времени, времена выполнения этих множественных заданий (например, обнаружения положения и передачи на вторичный адрес) может указываться в зависимости от характеристик каждой платформы устройства печати, например, включающий в себя скорость, возможности, спецификации комплекта логических схем, количество сменных компонентов, которые можно подключать к единой шине, скорость шины и т.д.

[0053] На фиг. 4A показан другой пример способа работы логической схемы, ассоциированной со сменным компонентом печатающего устройства. В одном примере этот способ может осуществляться без отслеживания длительности и/или таймера.

[0054] Блок 402A на фиг. 4A содержит прием первой команды аналогично фиг. 4. Блок 404A на фиг. 4A содержит идентификацию периода времени из первой команды и выбор или настройку длительности условия низкого напряжения на основании периода времени. Как будет представлено более подробно ниже, может выбираться или устанавливаться схема задержки, соответствующая принятому периоду времени, так что схема задержки может использоваться для генерации условия низкого напряжения до окончания длительности.

[0055] Блок 406A содержит генерирование условия низкого напряжения на протяжении выбранной или заданной длительности. Например, схема задержки логической схемы включает в себя переключатель линии задержки, подключенный к линии SDA. При приеме первой команды, логика может задействовать переключатель линии задержки, который будет генерировать условие низкого напряжения на линии SDA, пока его внутренняя логика не остановит работу, и в это время переключатель линии задержки больше не будет генерировать условие низкого напряжения на линии SDA. Длительность между задействованием и истечением может быть приблизительно равной, или немного короче или длиннее, чем идентифицированный период времени, например, достаточной для облегчения дискретизации печатающим устройством, что будет объяснено ниже. В другом примере, условие низкого напряжения может генерироваться аналогично тому, как показано на фиг. 4, например, с использованием аналогичного таймера внутри логики, который истекает и переключается в конце своей установленной длительности, или могут использоваться другие схемы переключения.

[0056] Блок 408A содержит возвращение к условию напряжения по умолчанию, по истечении длительности, связанной с периодом времени. Например, условие низкого напряжения можно удалить, так что последовательная шина данных снова переходит в состояние или условие высокого напряжения и/или напряжения по умолчанию. В одном примере условие низкого напряжения можно удалить предварительно не отслеживая таймер. Напротив, условие низкого напряжения можно удалить путем завершения работы схемы задержки и/или путем переключения на условие напряжения по умолчанию.

[0057] Способ, проиллюстрированный на фиг. 4, и способ, проиллюстрированный на фиг. 4A, могут повторяться в случае, когда, например, (i) печатающее устройство повторно инициируется, (ii) сменный компонент печатающего устройства устанавливается или переустанавливается в печатающем устройстве, (iii) другие сменные компоненты печатающего устройства устанавливаются в одном и том же печатающем устройстве, в котором установлен текущий компонент печатающего устройства, или, (iv) между заданиями на печать или мероприятиями по обслуживанию и т.д. По разным причинам логическая схема может принимать первую команду, указывающую первый период времени в первом мероприятии, и первую команду, указывающую другой, второй период времени в последующем мероприятии (которое может быть тем же мероприятием в другие моменты времени или другим мероприятием). Поэтому в ответ на другую первую команду (например, блок 402A), отправленную на один и тот же (по умолчанию) адрес одной и той же логической схемы через последовательную шину данных в разные моменты времени, где первая команда указывает второй период времени, отличный от первого периода времени, логическая схема может снова генерировать условие низкого напряжения на последовательной шине данных (например, блок 406A), на этот раз на протяжении второй длительности на основании второго периода времени, причем вторая длительность отличается от первой длительности на основании первого периода времени. Для разных первых команд в разные моменты времени (например, трех, четырех, пяти или гораздо больше первых команд), где каждый раз указывается разный период времени, условие низкого напряжения может генерироваться в течение, каждый раз, разной соответствующей длительности. В некоторых примерах условие низкого напряжения может генерироваться на протяжении разных длительностей без отслеживания таймера.

[0058] На фиг. 5 показан пример последовательной шины 500, содержащей всего четыре линии: две активные линии, SDA и SCL, как описано выше, соединение Vdd источника напряжения и соединение GND заземления. Активные линии являются двусторонними. Соединение Vdd источника напряжения подключено к первому источнику 502 напряжения, и линия SDA подключена ко второму источнику 504 напряжения через нагрузочный повышающий резистор 506.

[0059] Ведущее устройство 508, например, содержащее контроллер устройства печати, ассоциированный с аналого-цифровым преобразователем 510, присоединено к шине 500. Шина 500, ведущее устройство 508 и аналого-цифровой преобразователь 510 могут обеспечиваться устройством печати. Ведущее устройство 508 содержит схему обработки, ассоциированную с устройством печати (в некоторых примерах входящую в его состав). Четыре ‘подчиненных устройства’ 512a-d, которые содержат логическую схему, ассоциированную со сменными компонентами 514a-d устройства печати, в этом примере присоединенную к ним, также присоединены к шине 500. В этом примере, каждый из сменных компонентов 514a-d устройства печати содержит чернильный картридж того или иного цвета.

[0060] В этом примере каждое подчиненное устройство 512a-d, присоединенное к шине 500, имеет свой собственный уникальный адрес и может быть приемником и/или передатчиком. В типичной операции, последовательные тактовые сигналы и последовательные сигналы данных обеспечиваются из ведущего устройства 508 по линии SCL тактового сигнала и линии SDA данных, тогда как рабочее напряжение для подчиненных устройств обеспечивается между линией Vdd источника напряжения и линией GND заземления. Сигналы данных также могут отправляться от подчиненного устройства 512 на ведущее устройство 508.

[0061] В примере передача, которая начинается с условия начала и заканчивается условием остановки, может именоваться “пакетом” I2C. В примере пакета I2C, отправленного ведущим устройством 508, это может содержать адрес подчиненного устройства, указание, является ли команда командой считывания или записи (В некоторых примерах они могут совместно составлять байт), код команды (который может быть вторым байтом данных), и, в некоторых примерах любые дополнительные данные команды (например, дополнительные параметры команды, коды аутентификации сообщений (MAC), циклические проверки избыточности (CRC) и пр., которые могут быть одним или более последующими байтами данных).

[0062] В примере операции при осуществлении способа, представленного на фиг. 4, ведущее устройство 508 может сначала выдавать условие начала, которое действует как сигнал ‘внимание’ всем подключенным подчиненным устройствам 512. Это может, например, характеризоваться падением напряжения на линии SDA при высоком напряжении SCL. Затем ведущее устройство 508 может отправлять байт, включающий в себя адрес подчиненного устройства 512, доступ к которому желает осуществлять ведущее устройство 508, и бит, который обеспечивает указание, является ли доступ операцией считывания или записи.

[0063] После приема адресного байта все подчиненные устройства 512a-d будут сравнивать его со своим собственным адресом. В отсутствие совпадения подчиненное устройство 512 в общем случае будет ждать следующее условие начала, которое инициируется ведущим устройством 508.

[0064] Если же адрес совпадает, схема этого подчиненного устройства 512a-d будет принимать последующую информацию команды и затем создавать ответный сигнал квитирования (сигнал “ACK”) (который может содержать перевод линии SDA вниз в течение конкретного периода тактового сигнала).

[0065] В некоторых приведенных здесь примерах команда может быть командой, предписывающей подчиненному устройству 512 генерировать условие низкого напряжения в течение периода времени. Условие низкого напряжения может предписываться после генерации ответного сигнала ACK. Затем ведущее устройство 508 может генерировать условие остановки.

[0066] После того как ведущее устройство 508 принимает сигнал квитирования, (и в некоторых примерах после генерации условия остановки), ведущее устройство 508 может попытаться подтвердить, что подчиненное устройство 512 сгенерировало условие низкого напряжения на SDA (и, В некоторых примерах может прекратить отправку тактового сигнала на SCL, пока это условие низкого напряжения ожидается).

[0067] В этом примере на SDA последовательной шины 500 предусмотрена цепь резистивного делителя напряжения для обеспечения электронного определения соответствующих физических положений подчиненных устройств 512. В частности, несколько резисторов 516a-d делителя предусмотрены на линии SDA данных, и существует соединение 518 от линии SDA данных к аналого-цифровому преобразователю (ADC) 510. Эта конфигурация создает цепь делителя лестничного типа (резисторную цепь лестничного типа), которая обуславливает изменение напряжения сигнала от каждого устройства 512 в зависимости от физической позиции устройства 512, поскольку устройства 512 соединяются с цепью делителя в разных точках. Например, сигнал от подчиненного устройства 512d будет проходить через четыре из резисторов 516 делителя, тогда как сигнал от подчиненного устройства 512a будет проходить через только один из резисторов 516a делителя. Регистрируя значение напряжения, можно определять позицию подчиненного устройства 512, создающего условие низкого напряжения. Другими словами, каждое подчиненное устройство 512 создает особое условие низкого напряжения. Напряжение можно регистрировать с использованием ADC 510. ADC 510 включает в себя схему, которая преобразует аналоговое напряжение в цифровой сигнал, указывающий уровень напряжения. Этот цифровой сигнал используется ведущим устройством 508 для электронного различия физического положения подчиненных устройств 512 на шине на основании уровня напряжение сигналов от подчиненных устройств 512. Напряжение можно сравнивать с ожидаемым напряжением для устройства 512, имеющего адрес, используемый в команде.

[0068] ADC 510 может принимать сигналы управления от ведущего устройства 508 и подавать данные на него по линии связи (которая может быть другой шиной связи). Хотя ADC 510 показан отдельно от ведущего устройства 508, ADC 510 может физически составлять часть ведущего устройства 508, или может располагаться отдельно от него.

[0069] ADC 510 и цепь делителя лестничного типа могут быть выполнены с возможностью различать положение путем обнаружения порядка напряжений устройств на шине 500, не создавая помехи идентификации высокого и низкого состояний, используемых при переносе данных. Другими словами, все характеристически низкие напряжения, создаваемые на шине каждым подчиненным устройством 512 может быть относительно удалено от порога для характеризации каждого бита данных как высокого или низкого.

[0070] В порядке одного примера ведущее устройство 508 может быть выполнено с возможностью обнаружения любого сигнала ниже порогового значения в качестве условия низкого напряжения при приеме данных. Например, любое напряжение ниже 2 В, или ниже 1 В, при высоком напряжении SCL может идентифицироваться как низкий бит данных (в некоторых примерах 0), тогда как значения выше этого порога может идентифицироваться как высокий бит данных (В некоторых примерах 1). В некоторых примерах порог для обнаружения низкого бита данных является напряжением ниже 1,3 В.

[0071] Однако ведущее устройство 508 использующее преобразованное напряжение от ADC 510, может быть выполнено с возможностью различения между конкретными сигналами, которые ниже этого порога и немного выше нуля (или номинально 0 В) (например, до порядка нескольких сотен милливольт (мВ)) для обеспечения позиционной идентификации. Каждый резистор делителя 516 может иметь достаточное сопротивление, чтобы напряжение, созданное между суммой резисторов 516 делителя и нагрузочным повышающим резистором 504 является напряжением ниже нижнего порога напряжения. Однако сопротивление резисторов 516 делителя может выбираться достаточно малым, чтобы идентификация сигналов высокого напряжения от ведущего устройства 508 в ходе нормальной работы не была чрезмерно скомпрометирована, т.е. чтобы высокое напряжение оставалось относительно близким к максимальному напряжению, обеспеченному вторым источником 504 напряжения.

[0072] В одном варианте осуществления каждый из резисторов 516 делителя имеет сопротивление около 51 Ом, хотя это только один из многих уровней сопротивления, которые можно использовать, и уровни сопротивления могут изменяться между разными резисторами 516. В таком примере, первый и второй источники 502, 504 напряжения могут обеспечивать около 3,3 вольт, и нагрузочный повышающий резистор 506 может быть резистором около 1000 Ом (1 кОм), т.е. значительно большее значение сопротивления, чем резисторы 516 делителя.

[0073] Другими словами, резисторы 516 делителя могут действуют как отдельные ‘дополнительные’ нагрузочные повышающие резисторы на линии SDA, предотвращая падение до номинальных 0 В. Это может обеспечивать, например, разброс напряжения около 100-200 мВ вокруг указанных выше значений. ADC 510 может измерять их ‘отсчетами’. Например, в системе 3,3 В, где обеспечен 9-битовый ADC, это в свою очередь означает, что каждый отсчет представляет около 6 мВ (что получается делением 3,3 В на 512). Поэтому можно ожидать, что ADC 510 будет регистрировать от около 20 отсчетов для картриджа с самым низким напряжением до около 80 отсчетов для самого высокого напряжения.

[0074] Как упомянуто выше, позиции по меньшей мере некоторых сменных компонентов устройства печати могут проверяться с использованием механической кодировки, а не описанными здесь способами. Поэтому количество регистрируемых уровней напряжения может быть меньше количества, например, используемых картриджей печати.

[0075] Можно отметить, что, поскольку со сменными компонентами 514a-d устройства печати ассоциированы конкретные адреса, конкретная команда может отправляться, например, на 514a, напряжение дискретизироваться, и затем процесс может повторяться для каждого из сменных компонентов 514b, c и d устройства печати по очереди. Если сменные компоненты 514a-d устройства печати находятся в ожидаемых положениях, можно ожидать изменение значения напряжения в сторону увеличения в случае измеренная в этом порядке. Если же сменные компоненты 514a-d устройства печати не находятся в ожидаемых положениях, этот рисунок (или, в более общем случае, ожидаемые относительные напряжения) не будет наблюдаться, и может генерироваться предупреждение.

[0076] На практике период времени в течение которого линия SDA поддерживается на низком уровне, может превышать период времени дискретизации. Например, подчиненное устройство 512 может получить команду от ведущего устройства 508 поддерживать линию SDA на низком уровне в течение 50 мс. В течение этого времени, ADC 510 главного устройства может дискретизировать линию SDA данных на некоторое количество промежутков времени, например, от 3 до 10 промежутков времени. В некоторых примерах, если по меньшей мере одно из этих показаний выходит пределы некоторого порогового диапазона, команда может повторяться, давая новые выборки. В других примерах выборки можно брать, пока не будет превышен порог ‘хороших’ выборок. В некоторых таких примерах может существовать максимальное разрешенное количество выборок прежде чем будет объявлено состояние ошибки, например, дискретизация будет продолжаться, пока не будет получено 5 выборок, находящиеся в ожидаемом диапазоне или не будет взято максимум 10 выборок. Если ‘хорошего’ набора выборок не получается, могут указываться ошибка. Выборки можно усреднять для генерации репрезентативного значения для этого сменного компонента 514a-d устройства печати.

[0077] Период дискретизации может быть относительно коротким. Например, после того, как подчиненное устройство 512 получает команду поддерживать линию SDA на низком уровне, ведущее устройство 508 может ожидать дискретизации шины, чтобы шину можно было согласовать (например, около 10 мс). Получение выборок может происходить около 1 мс. Однако линия SDA может поддерживается на низком уровне в течение более длительного периода, например, 50 мс, для обеспечения перепроверки и т.п. Этот период может быть указан в первой команде или в некоторых примерах ассоциирован с ней (например, путем ссылки на поисковую таблицу или регистр, поддерживаемую/ый в подчиненном устройстве 512).

[0078] Поэтому не обязательно поддерживать линию SDA на низком уровне в течение всего периода времени, указанного в первой команде, где это применимо. Однако возможно, что, по меньшей мере статистически, подчиненное устройство 512 поддерживает линию SDA на низком уровне таким образом, что период дискретизации вероятно длится в течение времени, когда линия SDA поддерживается на низком уровне, в ходе по меньшей мере одного из допустимого набора испытаний.

[0079] Очевидно, что линия SDA может поддерживаться на низком уровне, фактически, путем отправки сигнала данных, образованного последовательностью битов данных, ассоциированных с состоянием низкого напряжения (например, последовательностью 0-битов). В результате линия SDA будет поддерживаться на низком уровне в течение периода времени. Однако при отправке сигнала данных, подчиненное устройство 512 может обращаться к сигналу на SCL, а не к своему собственному внутреннему таймеру, чтобы определить, когда освобождать линию SDA, чтобы она могла вернуться в высокое состояние (т.е. когда удалять условие низкого напряжения, таким образом, что последовательная шина данных предполагает другое, высокое и/или по умолчанию, состояние или условие напряжения). Однако в предусмотренных здесь способах условие низкого напряжения применялось после подачи первой команды независимо от любого тактового сигнала на шине SCL (и в ряде случаев в отсутствие любого подобного тактового сигнала на шине SCL).

[0080] На фиг. 6 и 7A показаны примеры способа эксплуатации логической схемы (например, комплекта логических схем, как описано выше), ассоциированной со сменным компонентом устройства печати. В обоих примерах со ссылкой на соответствующие блоки 602 и 702A, логическая схема принимает, через шину данных I2C, первую команду, которая указывает первый период времени. В этом примере первая команда также содержит указание условия начала, адрес комплекта логических схем, поле идентификации, указывающее команду записи и указание условия остановки (например, растущее напряжение на линии данных на протяжении высокого участка тактового импульса).

[0081] В некоторых примерах период времени может выбираться на основании атрибутов главного устройства или его схемы. В целом период времени может быть достаточно долгим для обеспечения захвата хороших выборок, но не настолько долгим, чтобы чрезмерно удлинять время, затрачиваемое для проверки позиции сменного компонента устройства печати.

[0082] Согласно фиг. 6, блок 604 содержит генерирование, логической схемой, условия низкого напряжения на последовательной линии данных шины I2C после приема указания условия остановки (который сам следует за передачей команды) и в течение, по существу, длительности первого периода времени. Как упомянуто выше, хотя в некоторых примерах условие низкого напряжения может генерироваться в течение всего периода времени, в некоторых примерах способ может содержать разрешение последовательной линии данных ‘плавать высоко’ в течение части первого периода времени, т.е. линия может поддерживается на низком уровне в прерывистом режиме. В некоторых примерах последовательная линия данных может поддерживается на низком уровне в течение по меньшей мере 60% первого периода времени или по меньшей мере 70% первого периода времени или по меньшей мере 80% первого периода времени или по меньшей мере 90% первого периода времени или по меньшей мере 95% первого периода времени. В некоторых примерах напряжение поддерживается низким в течение достаточной пропорции для надежного совпадения с периодом дискретизации. Длительность условия низкого напряжения содержит по меньшей мере один период дискретизации, где дискретизация осуществляется схемой обработки устройства печати, как описано выше. Кроме того, если линия данных поддерживается на низком уровне в течение чрезмерно долгого периода времени, это приводит к блокировке передач и может, например, предписывать главному устройству генерировать ошибку превышения лимита времени и т.п.

[0083] Генерирование условия низкого напряжения после приема условия остановки указание означает, что шина не будет блокироваться в течение текущей передачи пакета данных.

[0084] В этом примере генерирование условия низкого напряжения совпадает с состоянием, в котором на последовательной шине данных не существует тактового сигнала, и блок (этап) 606 содержит отслеживание длительности условия низкого напряжения с использованием интегрального таймера логической схемы.

[0085] Способ дополнительно содержит, в блоке (этапе) 608, в ответ на запрос считывания, имеющий поле идентификации, указывающее режим считывания, осуществление, логической схемой операции считывания. Другими словами, помимо особых описанных здесь признаков, логическая схема может функционировать как подчиненное устройство I2C. Логическая схема может демонстрировать другие признаки подчиненного устройства I2C, например, участвуя в обменах аутентификации и/или удостоверения, принимая или исполняя команды считывания и/или записи, выполняя задания обработки и пр.

[0086] В примере, где логическая схема выполнен с возможностью использования дополнительной, отличной, вторичной функции и/или вторичного адреса, вторичная функция может содержать задействование или запитывание пятой контактной площадки или линии, например для подключения к подсхеме. Вторичный адрес может быть любой адрес, отличный от принятого по умолчанию (или первого или “первичного”) адреса логической схемы. Соответственно, способ может дополнительно содержать, в блоке 610, задействование вторичной функции и/или адреса на протяжении другого (например, более длительного) периода времени, указанного в третьей команде, направленной на адрес по умолчанию логической схемы. Логическая схема может быть выполнена с возможностью, в ответ на третью команду, затем отвечать на команды, направленные на вторичный адрес, и в течение этого другого периода времени, сбрасывать ее вторичный адрес на новый вторичный адрес до истечения длительности.

[0087] В примере третья команда указывает другой (например, более длительный) период времени для использования вторичной функции, ассоциированной со вторичным адресом. Соответственно, логическая схема отвечает на команды, направленные на вторичный адрес на протяжении этого указанного периода времени. В примере, разные вторичные адреса могут использоваться на протяжении указанного периода времени, например, каждого сеанса начиная с вторичного адреса по умолчанию, и затем переключаться на новые (например, случайные или другие) вторичные адреса на основании такого нового вторичного адреса, указанного в последующей команде, следующей за третьей командой. Опять же, связь через вторичный адрес может задействоваться на протяжении длительности на основании указанного периода времени, но длительность которого не обязано точно соответствовать этому периоду времени, как объяснено со ссылкой на блок 604. Разные периоды времени могут быть указаны в разных третьих командах, так что логическая схема может быть выполнена с возможностью задействовать связь через вторичный адрес на протяжении разных соответствующих длительностей. В течение этих длительностей, логическая схема может не отвечать на команды посредством ее первого адреса по умолчанию.

[0088] В другом примере, соответствующем блоку 610, логическая схема может, на основании третьей команды, указывающей период времени, задействовать вторичному функцию на протяжении указанного периода времени без задействования вторичного адреса. Например, вторичная функция включает в себя запитывание или задействование подсхемы, например, включающей в себя пятую контактную площадку или линию, отдельную от линий питания, земли, тактового сигнала и данных интерфейса печатающего устройства. В дополнительном примере, вторичный адрес задействуется с использованием подключаемой или подключенной второй логической схемой, ассоциированной с вторичной функцией, которое может, в промежуточном состоянии логической схемы, отключаться от остальной логической схемы, и, в рабочем состоянии логической схемы, подключаться к остальной логической схеме как части комплекта.

[0089] В одном примере логическая схема выполнена с возможностью отслеживания длительности периода времени, указанного в третьей команде, например, с использованием таймера. Логическая схема может быть выполнена с возможностью, по истечении длительности, переключаться обратно к адресу и/или функции по умолчанию. В другом примере, логическая схема не обязана отслеживать длительность. Напротив, она выполнена с возможностью настраивать или выбирать схему задержки, чтобы длительность соответствовала (“другому”) периоду времени третьей команды, так что, логическая схема переключается обратно к адресу по умолчанию по окончании заданной или выбранной длительности, соответствующей периоду времени третьей команды.

[0090] На фиг. 7 приведен пример комплекта 700 логических схем для ассоциирования со сменным компонентом устройства печати, содержащего логику 702, интерфейс 704 последовательной шины данных, таймер 706 и, в этом примере, память 708. В ходе эксплуатации комплекта 700 логических схем логика 702, в ответ на первую команду, отправленную на комплект 700 логических схем через последовательную шину данных, подключенную к интерфейсу 704 последовательной шины данных, комплект 700 логических схем в этом примере выполнен с возможностью генерации условия низкого напряжения на последовательной шине данных и отслеживает длительность периода времени с использованием таймера 706. В некоторых примерах таймер 706 может находиться на связи с логикой 702, например, по проводной или беспроводной линии связи. В некоторых примерах таймер 706 может обеспечиваться на общей подложке с логикой 702.

[0091] В некоторых примерах логика 702 может быть выполнена с возможностью отслеживания длительности периода времени без ссылки на тактовый сигнал последовательной шины данных. Интерфейс 704 последовательной шины данных может содержать интерфейс шины данных I2C.

[0092] Первая команда может указывать период времени, и логика 702 может быть выполнена с возможностью генерации условия низкого напряжения на последовательной шине данных в течение, по существу, длительности первого периода времени. Логика 702 может осуществлять любые аспекты способов, описанных выше в отношении фиг. 4-6.

[0093] В ответ на вторую команду логика 702 может быть выполнена с возможностью записи данных, принятых через интерфейс 704 последовательной шины данных, в память 708. В ответ на запрос считывания, логика 702 может быть выполнена с возможностью считывания данных из памяти 708 и передачи сигнала данных через интерфейс 704 последовательной шины данных.

[0094] На фиг. 7A показан пример способа работы логической схемы, отличающегося в некоторых аспектах от способа, проиллюстрированного на фиг. 6. В одном примере способ, представленный на фиг. 7A, может выполняться без отслеживания таймера. Блок (этап) 702A, представленный на фиг. 7A, соответствует блоку 602 на фиг. 6.

[0095] Блок (этап) 704A, изображенный на фиг. 7A, содержит настройку или выбор схемы задержки (см., например, фиг. 7B) на основании указанного периода времени, причем период времени, как объяснено выше, может варьироваться для разных первых команд. Схема задержки используется для генерации условия низкого напряжения блока 706A. Настройка схемы задержки может включать в себя настройку времени задержки (или “истечения”), или длительность, схемы задержки, длительность которой, в ряде случаев, еще не является заранее заданной, для облегчения возвращения или переключения к условию напряжения по умолчанию (например, высокого) по истечении этой длительности. Выбор схемы задержки включает в себя выбор одной из множества схем задержки, включенных в логическую схему, где каждая схема задержки имеет ту или иную заранее заданную характерную длительность для генерирования условия низкого напряжения, для облегчения, с использованием выбранной схемы задержки, возвращения или переключения к условию напряжения по умолчанию (например, высокого) по истечении выбранной длительности. Иллюстративная(ые) схема(ы) задержки может(ут) настраиваться или выбираться, соответственно, так что, длительность условия низкого напряжения соответствует периоду времени первой команды. Соответственно, длительность может изменяться в соответствии с разными периодами времени, указанными в разных первых командах. В некотором примере схема задержки может включать в себя таймер или переключатель линии задержки или другие схемы, которые заранее задаются или настраиваются на некоторую задержку по времени для облегчения возврата к условию напряжения по умолчанию по истечении длительности, например, без необходимости отслеживать таймер.

[0096] Блок 706A соответствует блоку 604 на фиг. 6. В некоторых примерах в ходе выполнения особенности блоков (этапов) 604 и 706A, представленных на фиг. 6 и 7A, соответственно, логическая схема не отвечает на другие команды. Другими словами, логическая схема может не реагировать на команды, генерируя при этом условие низкого напряжения.

[0097] Блок 708A содержит возвращение к условию напряжения по умолчанию (например, высокого) на линии SDA. Логическая схема может возвращаться к условию напряжения по умолчанию без отслеживания таймера, например, на основании завершения работы и/или переключения схемы задержки в конце длительности.

[0098] Блок 710A на фиг. 7A соответствует блоку 608 на фиг. 6. Блок 712A на фиг. 7A соответствует блоку 610 на фиг. 6. Согласно блоку 712A, в одном примере длительность, ассоциированная с периодом времени третьей команды, не отслеживается. Например, одна схема задержки может настраиваться, или одна схема задержки из множества схем задержки может выбираться, чтобы прекращать работу в конце соответствующей длительности (которая может изменяться между разными третьими командами) для переключения обратно к адресу по умолчанию или функции по умолчанию по истечении (например, переменной) длительности.

[0099] На фиг. 7B показан другой пример логической схемы 700B или комплект логических схем для ассоциирования со сменным компонентом устройства печати, содержащий логику 702B и схему 706B задержки, интерфейс 704B последовательной шины данных (например, линию), и, в этом примере, память 708B. В одном примере комплект 700B логических схем, изображенный на фиг. 7B, является альтернативой или отличается от комплекта 700 логических схем на фиг. 7. В другом примере комплект 700B логических схем не использует функцию слежения.

[00100] В ходе эксплуатации комплект 700B логических схем может быть выполнен с возможностью, в ответ на первую команду, отправленную на комплект 700B логических схем через последовательную шину данных, подключенную к интерфейсу 704B последовательной шины данных, генерировать условие низкого напряжения на последовательной шине данных. Интерфейс 704B последовательной шины данных может содержать интерфейс шины данных I2C. Как объяснено, первая команда может указывать период времени, и логика 702B может быть выполнена с возможностью генерации условия низкого напряжения на последовательной шине данных в течение, по существу, длительности первого периода времени. Логика 702B и логическая схема 700B могут осуществлять любые аспекты способов, описанных выше со ссылкой на фиг. 4A - 7A.

[00101] В ответ на вторую команду логика 702B может быть выполнена с возможностью записывать данные, принятые через интерфейс 704B последовательной шины данных, в память 708B. В ответ на запрос считывания логика 702B может быть выполнена с возможностью считывать данные из памяти 708B и передавать сигнал данных через интерфейс 704B последовательной шины данных.

[00102] Логика 702B может дополнительно включать в себя схему 706B задержки. В одном примере схема 706B задержки представляет множество схем задержки. В одном примере схема 706B задержки может включать в себя множество переключателей линии задержки, каждый из которых настроен отключаться по истечение характерной длительности. Пример переключателя линии задержки включает в себя транзистор, имеющий плавающий затвор с утечкой, или схему R-C и компаратор, например, аналогично аспектам вышеописанного таймера. В некоторых примерах схема задержки может включать в себя оборудование, аналогичное или идентичное таймеру, например, описанному выше со ссылкой на блок 406 на фиг. 4. В примере схема 706B задержки подключается к интерфейсу 704B последовательной шины данных, например, соединяющему между собой интерфейс последовательной шины данных и логику микроконтроллера, хотя для достижения тех же результатов схему задержки можно реализовать в других аппаратных конфигурациях. В одном примере логика 702B выполнена с возможностью, по получении первой команды, выбирать переключатель линии задержки, который соответствует указанному периоду времени и задействовать его. Выбранный и задействованный переключатель линии задержки выполнен с возможностью генерации условия низкого напряжения на линии 704B SDA, до истечения времени его работы, и в это время переключатель будет останавливать генерирование условия низкого напряжения на интерфейсе 704B шины данных SDA. Выбранный и задействованный переключатель линии задержки может быть выполнен с возможностью отключать логику 702B (оставшуюся) от последовательной шины SDA в ходе генерации условия низкого напряжения, до истечения времени своей работы, так что связь по шине SDA оказывается невозможной при таком условии низкого напряжения. Поэтому условие низкого напряжения может генерироваться посредством разных схем задержки, отличающихся характерной длительностью, так что условие низкого напряжения может генерироваться на протяжении разных длительностей, соответствующих разным схемам задержки и разным принятым периодам времени. В некоторых примерах в течение времени генерации условия низкого напряжения, связь по шине SDA 704B может быть невозможной.

[00103] В памяти 708B может храниться поисковая таблица (LUT) и/или алгоритм, который связывает каждую схему задержки (например, переключатель линии задержки) с периодом времени или диапазоном периодов времени. Логика 702B может быть выполнена с возможностью, по получении первой команды, выбирать схему задержки, которая соответствует принятому периоду времени, с использованием LUT и/или алгоритма.

[00104] В другом примере схема задержки может быть выполнена с возможностью настройки на разные длительности, без функции отслеживания, с использованием внутренней логики. Например, схема задержки включает в себя несколько переключателей линии задержки и/или других выключателей, например, соединенных последовательно, так что в зависимости от необходимой длительности может настраиваться или выбираться соответствующий выключатель. Количество переключателей линии задержки, который используется для генерации условия низкого напряжения, зависит от выбранного переключателя, так что длительность задержки определяется накопленными длительностями разных используемых переключателей линии задержки, так что накопленная длительность может устанавливаться в соответствии с принятым периодом времени. Другие примеры схем переключения можно использовать для задания длительности генерации низкого напряжения в соответствии с принятым периодом времени. Специалисту в данной области техники понятно, что как часть логики 702B можно использовать единственную, настраиваемую, схему задержки для нескольких разных промежутков времени, или множество, например, фиксированных и/или параллельных схем задержки, каждая из которых ассоциирована с отдельным характерным временем задержки.

[00105] На фиг. 8 показан пример сменного компонента устройства печати, содержащего комплект логических схем как показано на фиг. 7. В этом примере, сменным компонентом устройства печати является картридж 800 печати, ширина корпуса 802 которого меньше его высоты. Выход 804 жидкости печати (в этом примере, выпуск, обеспеченный на нижней стороне картриджа 800), вход 806 воздуха и выемка 808 обеспечиваются на передней поверхности картриджа 800. Выемка 808 проходит по верхней части картриджа 800, и контакты 810 шины I2C комплекта 812 логических схем (например, комплекта 700 логических схем, как описано выше) обеспечиваются на стороне выемки 808 против внутренней стенки боковой стенки корпуса 802 рядом с верхней частью и передней частью корпуса 802. В этом примере, комплект 812 логических схем обеспечивается против внутренней стороны боковой стенки.

[00106] Примеры в настоящем изобретении могут обеспечиваться как способы, системы или машиночитаемые инструкции, например, любая комбинация программного обеспечения, аппаратного обеспечения, программно-аппаратного обеспечения и т.п. Такие машиночитаемые инструкции могут быть включены в машиночитаемый носитель данных (включающий в себя, но без ограничения дисковое запоминающее устройство, CD-ROM, оптическое запоминающее устройство и т.д.), на котором хранятся машиночитаемые программные коды.

[00107] Настоящее изобретение описано со ссылкой на блок-схемы операций и блок-схемы способа, устройств и систем согласно примерам настоящего изобретения. Хотя вышеописанные блок-схемы операций, демонстрируют конкретный порядок исполнения, порядок исполнения может отличаться от изображенной. Блоки, описанные в отношении одной блок-схемы операций, могут объединяться с блоками другой блок-схемы операций. Следует понимать, что по меньшей мере некоторые блоки в блок-схемах операций и блок-схемах, а также их комбинации можно реализовать посредством машиночитаемых инструкций.

[00108] Машиночитаемые инструкции могут, например, исполняться компьютером общего назначения, компьютером специального назначения, встроенным процессором или процессорами других программируемых устройств обработки данных для реализации функций, описанных в описании и схемах. В частности, процессор или схема обработки может исполнять машиночитаемые инструкции. Таким образом, функциональные модули устройства и устройств (например, логической схемы и/или контроллеров) могут быть реализованы процессором, выполняющим машиночитаемые инструкции, хранящиеся в памяти, или процессором, действующим в соответствии с инструкциями, встроенными в логическую схему. Термин ‘процессор’ следует интерпретировать в широком смысле, включая в него CPU, блок обработки, ASIC, логический блок или программируемую вентильную матрицу и т.д. Все способы и функциональные модули могут осуществляться единым процессором или делиться между несколькими процессорами.

[00109] Такие машиночитаемые инструкции также могут храниться в машиночитаемом хранилище (например, материальном машиночитаемом носителе), и могут предписывать компьютеру или другим программируемым устройствам обработки данных работать в конкретном режиме.

[00110] Такие машиночитаемые инструкции также могут загружаться на компьютер или другие программируемые устройства обработки данных, так что компьютер или другие программируемые устройства обработки данных осуществляют несколько операций для создания компьютерно-реализуемой обработки, таким образом, инструкции, исполняемые на компьютере или других программируемых устройствах, реализуют функции, указанные блоком(ами) в блок-схемах операций и/или в блок-схемах.

[00111] Дополнительно, изложенные здесь принципы могут быть реализованы в форме компьютерного программного продукта, причем компьютерный программный продукт хранится на носителе данных и содержит множество инструкций, чтобы заставить компьютерное устройство реализовать способы, упомянутые в примерах настоящего изобретения.

[00112] Хотя способ, устройство и родственные аспекты были описаны со ссылкой на некоторые примеры, можно предложить различные модификации, изменения, изъятия и замены, не выходя за рамки сущности настоящего изобретения. Поэтому предполагается, что способ, устройство и родственные аспекты ограничиваются только объемом нижеследующей формулы изобретения и ее эквивалентами. Следует отметить, что вышеупомянутые примеры иллюстрируют не только то, что описано здесь, и что специалисты в данной области техники смогут предложить многие альтернативные реализации, не выходя за рамки объема нижеследующей формулы изобретения. Признаки, описанные в отношении одного примера, можно объединять с признаками другого примера.

[00113] Слово “содержащий” не исключает наличия элементов, отличных от перечисленных в формуле изобретения, их упоминание в единственном числе не исключает множества, и единый процессор или другой блок может реализовать функции нескольких блоков, упомянутых в формуле изобретения.

[00114] Признаки любого зависимого пункта формулы изобретения можно объединять с признаками любого из независимых пунктов или других зависимых пунктов.

[00115] В некоторых примерах способ можно описать в любом из следующих аспектов.

[00116] Аспект 1: Способ, содержащий, в ответ на первую команду, отправленную на адрес логической схемы, ассоциированной со сменным компонентом устройства печати, через последовательную шину данных, причем первая команда указывает первый период времени, генерирование, логической схемой, условия низкого напряжения на последовательной шине данных в течение первой длительности на основании первого периода времени; и в ответ на другую первую команду, отправленную на один и тот же адрес одной и той же логической схемы через последовательную шину данных в разные моменты времени, в котором другая первая команда указывает второй период времени, отличный от первого периода времени, генерирование, логической схемой, условия низкого напряжения на последовательной шине данных в течение, соответственно, другой длительности на основании второго периода времени.

[00117] Аспект 2: способ согласно предыдущему аспекту, дополнительно содержащий удаление условия низкого напряжения, таким образом, что последовательная шина данных предполагает другое, высокое и/или по умолчанию, состояние или условие напряжения, по истечении периода времени.

[00118] Аспект 3: способ согласно предыдущему аспекту, дополнительно содержащий задействование схемы задержки, выполненной с возможностью поддержания условия низкого напряжения в течение разных периодов времени на основании принятого периода времени.

[00119] Аспект 4: способ согласно аспекту 2 или 3, содержащий генерирование и удаление условию низкого напряжения без отслеживания длительности периода времени.

[00120] Аспект 5: способ согласно любому из аспектов 2-4, содержащий использование таймера для поддержания условия низкого напряжения.

[00121] Аспект 6: способ согласно любому из аспектов 2-5, содержащий генерирование условия низкого напряжения на последовательной шине данных в течение, по существу, длительности периода времени, указанной в соответствующей одной из упомянутых команд.

[00122] Аспект 7: способ согласно любому предыдущему аспекту кроме аспекта 4, содержащий отслеживание условия низкого напряжения.

[00123] Аспект 8: способ согласно любому предыдущему аспекту, содержащий генерирование условия низкого напряжения на последовательной линии данных последовательной шины данных.

[00124] Аспект 9: способ согласно любому предыдущему аспекту, в котором длительность условия низкого напряжения содержит по меньшей мере один период дискретизации, причем дискретизация осуществляется схемой обработки устройства печати в течение периода дискретизации.

[00125] Аспект 10: способ согласно любому предыдущему аспекту, в котором генерирование условия низкого напряжения совпадает с состоянием, в котором на последовательной шине данных не существует тактового сигнала.

[00126] Аспект 11: способ согласно любому предыдущему аспекту, в котором первая команда содержит поле идентификации, указывающее команду записи и указание условия остановки, причем способ дополнительно содержит генерирование, логической схемой, условия низкого напряжения на последовательной шине данных после приема указания условия остановки.

[00127] Аспект 12: способ согласно аспекту 11, дополнительно содержащий, по истечении длительности, в ответ на команду считывания/записи, осуществление, логической схемой, операции считывания/записи.

[00128] Аспект 13: способ согласно любому предыдущему аспекту, в котором значение напряжения условия низкого напряжения указывает позицию сменного компонента устройства печати в устройстве печати.

[00129] Аспект 14: комплект логических схем для ассоциирования со сменным компонентом устройства печати, содержащий: логику и интерфейс последовательной шины данных, причем интерфейс последовательной шины данных служит для сопряжения с последовательной шиной данных устройства печати и, причем логика служит, в ответ на первую команду, отправленную на комплект логических схем через последовательную шину данных, подключенную к интерфейсу последовательной шины данных, причем первая команда включает в себя период времени, для генерации условия низкого напряжения на последовательной шине данных на протяжении длительности на основании периода времени, и, по истечении длительности, для возвращения к условию напряжения по умолчанию на последовательной шине данных.

[00130] Аспект 15: комплект логических схем согласно аспекту 14, в котором логика выполнена с возможностью генерации условия низкого напряжения на протяжении разных длительностей на основании соответствующих разных принятых периодов времени.

[00131] Аспект 16: комплект логических схем согласно аспекту 14 или 15, в котором логика предназначена, в ответ на другую первую команду, отправленную на комплект логических схем через последовательную шину данных, подключенную к интерфейсу последовательной шины данных, причем другая первая команда включает в себя второй период времени, отличный от первого периода времени, для генерации условия низкого напряжения на последовательной шине данных на протяжении второй длительности на основании второго периода времени, причем вторая длительность отличается от первой длительности, и, по истечении второй длительности, для возвращения к напряжению по умолчанию на последовательной шине данных.

[00132] Аспект 17: комплект логических схем согласно любому из аспектов 14-16, содержащий переключатель для возврата к напряжению по умолчанию по истечении продолжительности времени на основании принятого периода времени.

[00133] Аспект 18: комплект логических схем согласно любому из аспектов 14-17, в котором логика выполнена с возможностью, при условии низкого напряжения, не отвечать на команды.

[00134] Аспект 19: комплект логических схем согласно любому из аспектов 14-18, в котором логика содержит множество схем задержки для генерации условия низкого напряжения на последовательной шине данных, причем каждая схема задержки ассоциирована с характерной длительностью, так что разные схемы задержки из множества схем задержки ассоциированы с разными длительностями, причем логика служит для выбора схемы задержки на основании принятого периода времени.

[00135] Аспект 20: комплект логических схем согласно любому из аспектов 14-19, в котором логика содержит настраиваемую схему задержки для генерации условия низкого напряжения на последовательной шине данных на протяжении переменной длительности, и настройки длительности на основании принятого периода времени.

[00136] Аспект 21: комплект логических схем согласно любому из аспектов 14-20, в котором схема задержки или каждая из них выполнена с возможностью заканчивать работу по истечении продолжительности времени, причем логика должна возвращаться к напряжению по умолчанию, когда схема задержки заканчивает работу.

[00137] Аспект 22: комплект логических схем согласно аспекту 18 или 19, содержащий память, где хранится поисковая таблица или алгоритм для выбора или настройки схемы задержки.

[00138] Аспект 23: комплект логических схем согласно любому из аспектов 14-22, выполненный с возможностью генерации условия низкого напряжения на последовательной шине данных на основании периода времени без отслеживания длительности периода времени.

[00139] Аспект 24: комплект логических схем согласно любому из аспектов 14-23, в котором логика выполнена с возможностью генерации условия низкого напряжения на протяжении разных длительностей на основании соответствующих разных принятых периодов времени, длительность каждого из которых соответствует разному диапазону периодов времени.