ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

[0001] Данная заявка заявляет приоритет предварительной заявки No.61/407, 770, поданной 28 октября 2010 и озаглавленной ″Компьютерное самоисправление с частичной ре-синхронизацией″, компоненты которой включены в настоящее описание в качестве ссылок.

ОБЛАСТЬ ТЕХНИКИ

[0002] Настоящее изобретение относится к коррекции ошибок устройства с несколькими модулями вычислений. В частности, это раскрытие относится к коррекции ошибок в устройстве, в том числе с двумя или более процессорами. Некоторые реализации также включают несколько связанных с ними структур памяти.

ОПИСАНИЕ РОДСТВЕННЫХ С ИЗОБРЕТЕНИЕМ ТЕХНОЛОГИЙ

[0003] Некоторые среды требуют, чтобы компьютерные системы были чрезвычайно надежны. В то же время, некоторые из этих сред могут быть очень жесткими, подвергая компоненты компьютера к потенциально катастрофическим обстоятельствам.

[0004] Одной из таких сред является космическая среда. Компьютерные системы, которые могут быть размещены в пространстве, например, на околоземной орбите, не доступны для регулярного технического обслуживания и, следовательно, должны обеспечивать свои функции в течение времени жизни космических аппаратов. Таким образом, компьютерная система, установленная на космическом корабле, должна иметь высокую надежность и стабильность в своей устойчивости с учетом возникающих ошибок, внутренних или внешних.

[0005] Кроме того, объекты, расположенные в пространстве, могут быть различных типов излучения, которое может быть очень вредно для некоторых компонентов компьютера. Например, солнце может производить излучение элементов, которые влияют на электронные системы. Один элемент излучения может вызвать расстройство, называемое единичным событием (ЕР), либо процессора, либо памяти компьютерной системы путем изменения состояния транзистора в этих компьютерных компонентах. Компьютер в космической среде желательно должен быть толерантными к таким единичным событиям, поскольку в космическом пространстве они случаются часто.

[0006] Разработка компьютерных компонентов, которые по отдельности толерантны к такого рода расстройствам, может быть очень дорогой и неэффективной. Прежде всего, в связи с длительным циклом развития, таким компонентам обычно не хватает производительности современных компонентов. Например, разработка процессора, предназначенного для обеспечения толерантности к излучению, может занять два года к моменту ее завершения. Кроме того, защита таких компонентов от повреждений может сделать компоненты гораздо дороже, чем аналогичные компоненты без защиты.

[0007] Одним из способов защиты от ЕР является использование систем с несколькими, резервными процессорами. Например, в патенте США No.5,903,717 представлена компьютерная система для обнаружения и исправления ошибок от ЕР. Система включает множество процессоров (КП), выходы которых связаны с каждым тактовым циклом. Любой сигнал КП, выход, которого не согласуется с большинством процессоров выходных сигналов, приводит к возникновению ошибки производимого сигнала. Система реагирует на сигналы ошибки, генерируя прерывание управления системой. В ответ на прерывание системы управления в результате обнаружения ошибки, программное обеспечение инициирует в системе повторную синхронизацию из множества процессоров, когда ошибка возникает из-за одного события.

[0008] Патент США No.7,467,326 раскрывает вычислительную систему очистки модуля для повторной синхронизации процессора по истечении заданного интервала времени или любое другое событие, которое может быть определено пользователем. Модуль очистки повышает надежность системы путем очистки компонентов на регулярной основе, а не в режиме ожидания и обнаружения ошибки. Таким образом, ошибки, которые могут остаться незамеченными в течение длительного периода, не могут распространяться на дальнейшее повреждение системы.

РЕЗЮМЕ

[0009] Системы, способы и устройства раскрытие каждого есть несколько инновационных аспектов, ни один из которых не несет полной ответственности за желательные атрибуты, представленные здесь.

[0010] методы, устройства и системы, представленные здесь, относятся к компьютерным системам, которые являются надежными в их толерантности к единичному событию, которое может возникнуть, например, в космическом пространстве или на высотных самолетах. Эти методы, устройства и системы относятся к компьютерной системе, обеспечиваемой различными наборами средств защиты от сбоев, которые могут быть вызваны космическим или солнечным излучением, например. Такая защита включают одно или более из следующих действий: установку нескольких процессоров, нескольких модулей памяти, обнаружение ошибок и коррекции логики, и механическое экранирование компонентов системы. Представленные методы, устройства и системы обеспечивают улучшенные характеристики по сравнению известными системами в ряде отношений.

[0011] Одним из новых аспектов, представленных в заявке, является способ синхронизации состояния нескольких вычислительных модулей в электронной системе, при этом каждый вычислительный модуль имеет процессор. Способ может включать перемешивание обработки данных состояния для каждого из множества вычислительных модулей, сравнение хешей процессоров для обработки данных состояния и повторной синхронизации нескольких вычислительных модулей на основе, по крайней мере, сравнения хешей процессора.

[0012] Другим инновационным аспектом предмета, представленного в данном описании, может быть реализация отказоустойчивых вычислительных аппаратов. Отказоустойчивые вычислительные аппараты могут включать множество вычислительных модулей, причем каждый вычислительный модуль содержит процессор данных состояния и хеширования, при этом модуль выполнен с возможностью формирования хеш-значений данных состояния процессора, и отказоустойчивой блок проверки, выполненный с возможностью приема множества значений хеш-функции и определения, синхронизирован ли каждый вычислительный модуль с другими модулями вычислений.

[0013] Предметом изобретения также может быть реализация отказоустойчивых вычислительных аппаратов, включающих в себя множество вычислительных модулей, каждый вычислительный модуль включает в себя процессор, средство для хэширования выполненное с возможностью формирования хеш-значений данных состояния процессора, средство для сравнения множества хэш-значений, и средство для определения, если процессор в каждом вычислительном модуле синхронизирован с процессорами других модулей вычислений.

[0014] В некоторых реализациях предмет настоящего изобретения может быть реализован в виде не временного, считываемого компьютером носителя, содержащего сохраненные в нем команды, которые вызывают схему обработки для осуществления способа. Способ может включать хэширование обработки данных состояния для каждого из множества вычислительных модулях, сравнение хешей процессором для обработки данных состояния и повторной синхронизации нескольких вычислительных модулей на основе, по крайней мере, сравнения хешей процессора.

[0015] Детали одного или более реализаций предмета в этом описании изложены в прилагаемых чертежах и в описании ниже. Другие признаки, аспекты и преимущества станут очевидными из описания, чертежей и формулы изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

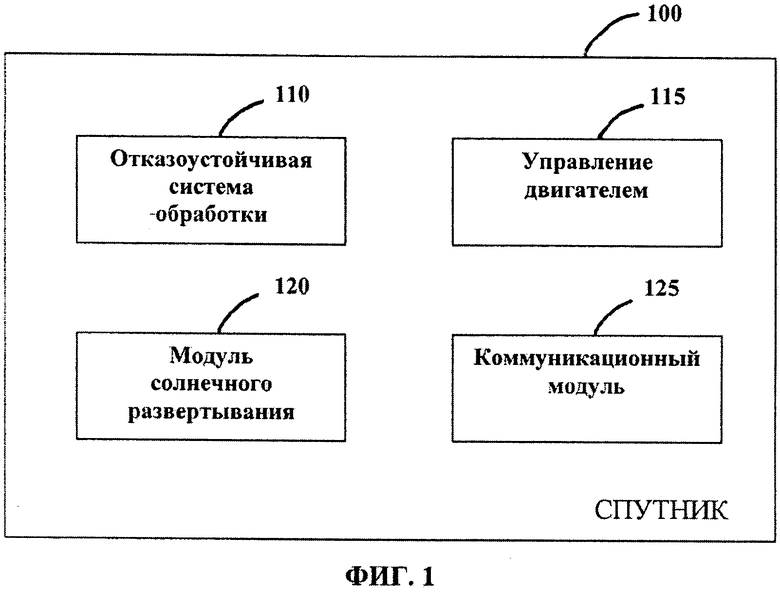

[0016] На фиг.1 показана блок-схема одного из вариантов осуществления изобретения - спутник, содержащий отказоустойчивый вычислительный аппарат.

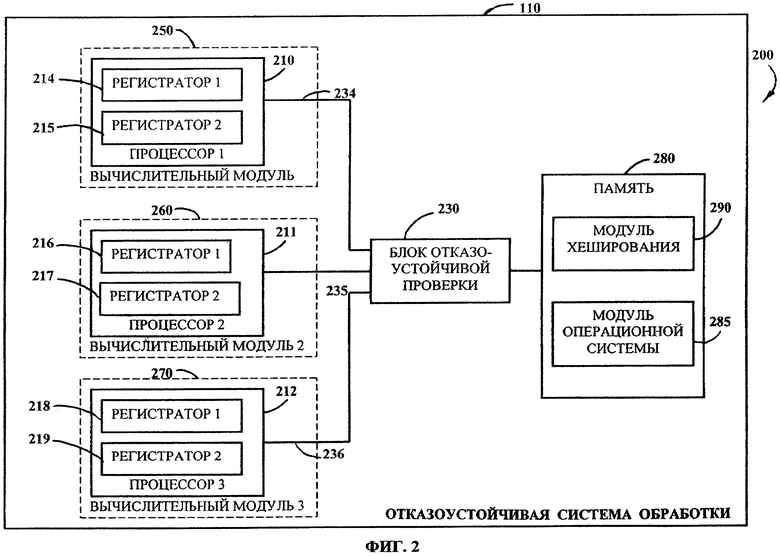

[0017] На фиг.2 показана блок-схема одного из вариантов осуществления изобретения - отказоустойчивой системы обработки, имеющей несколько процессоров.

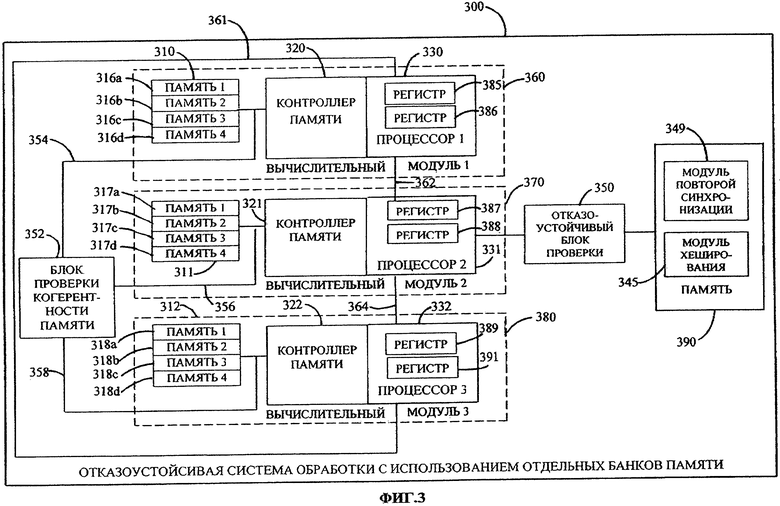

[0018] На фиг.3 показана блок-схема второго варианта примера отказоустойчивой системы обработки.

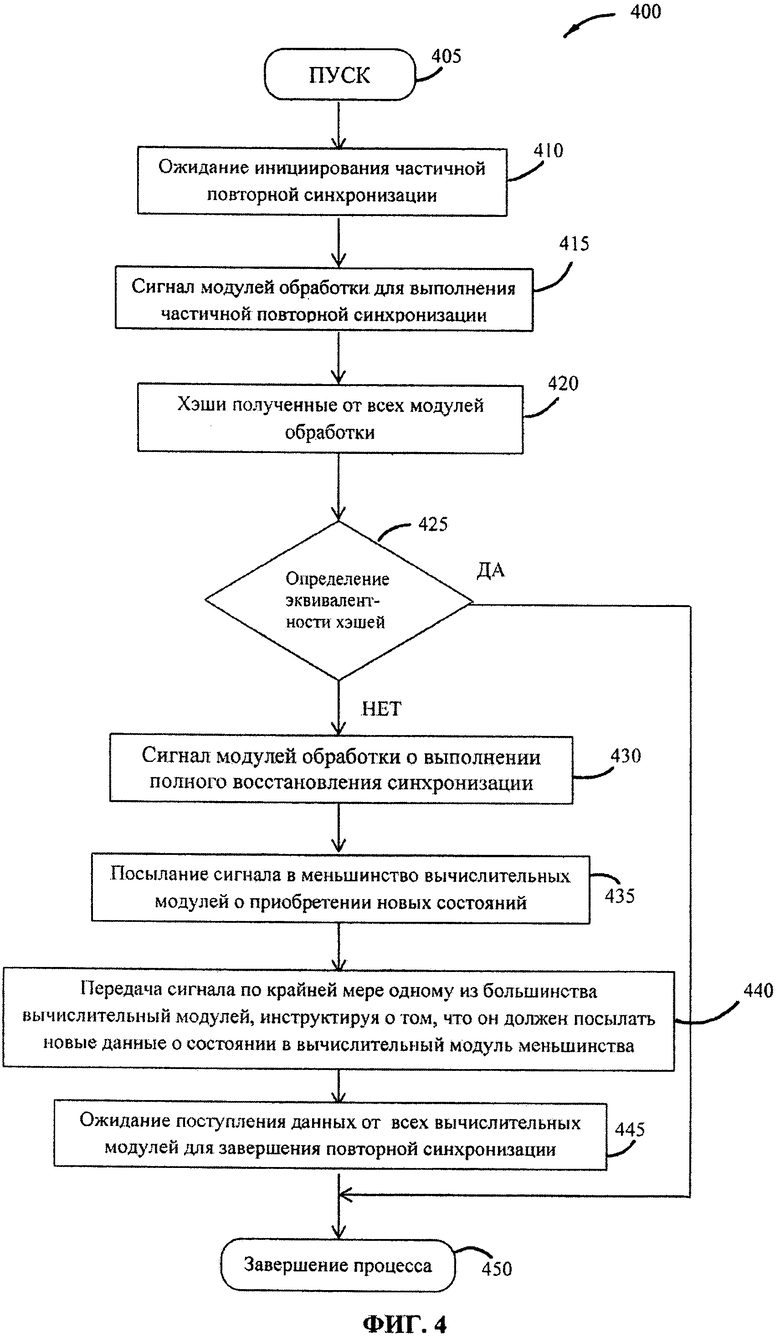

[0019] На фиг.4 представлена блок-схема, иллюстрирующая примерный процесс для верификации хэш на нескольких вычислительных модулях.

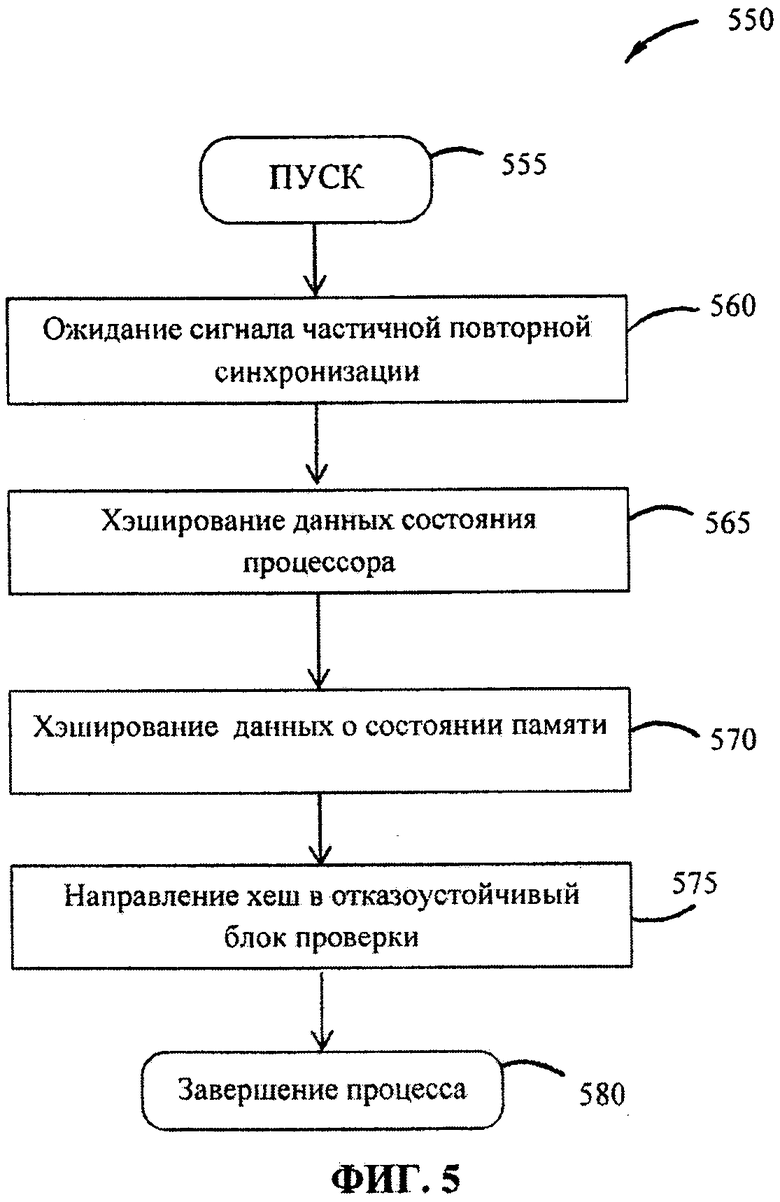

[0020] На фиг.5 показана блок-схема последовательности операций примерного процесса хэширования.

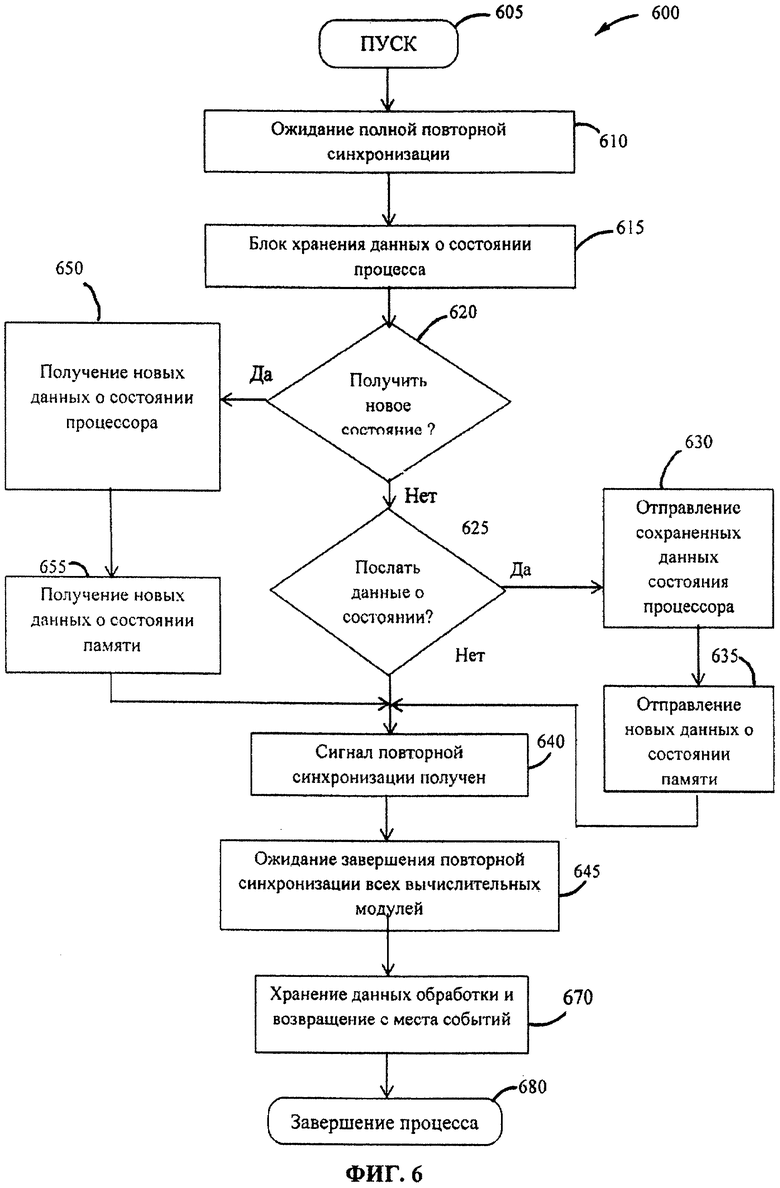

[0021] На фиг.6 показан пример блок-схемы последовательности операций процесса ресинхронизации вычислительного модуля.

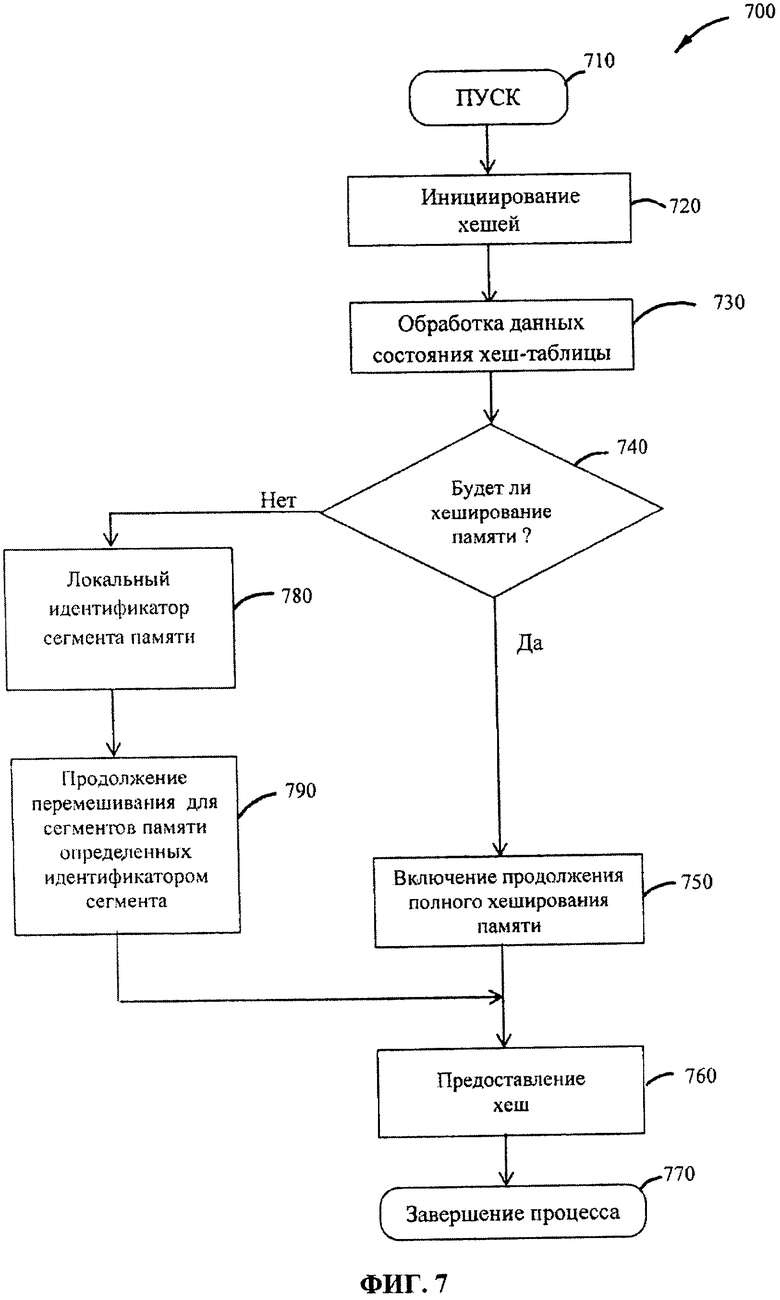

[0022] На фиг.7 показана блок-схема, иллюстрирующая пример реализации хеш-метода.

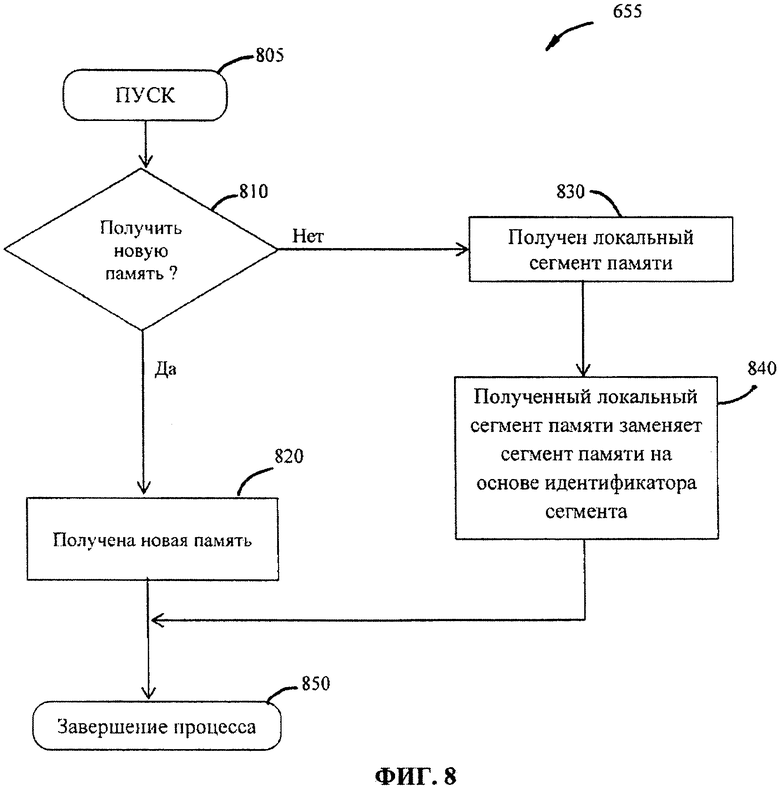

[0023] На фиг.8 показана блок-схема, иллюстрирующая пример получения памяти процесса.

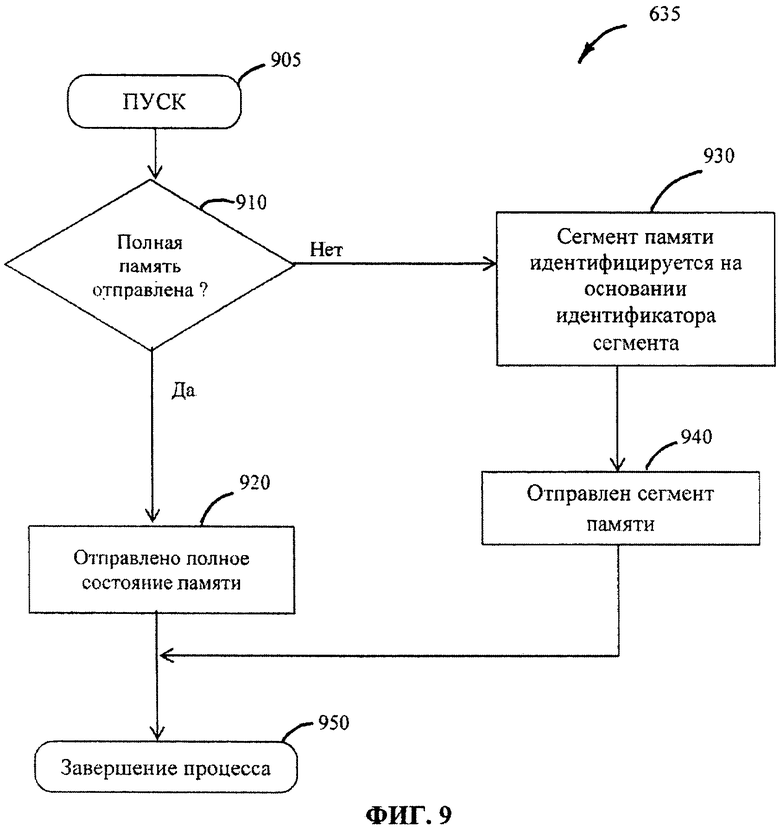

[0024] На фиг.9 показана блок-схема, иллюстрирующая пример процесса передачи памяти.

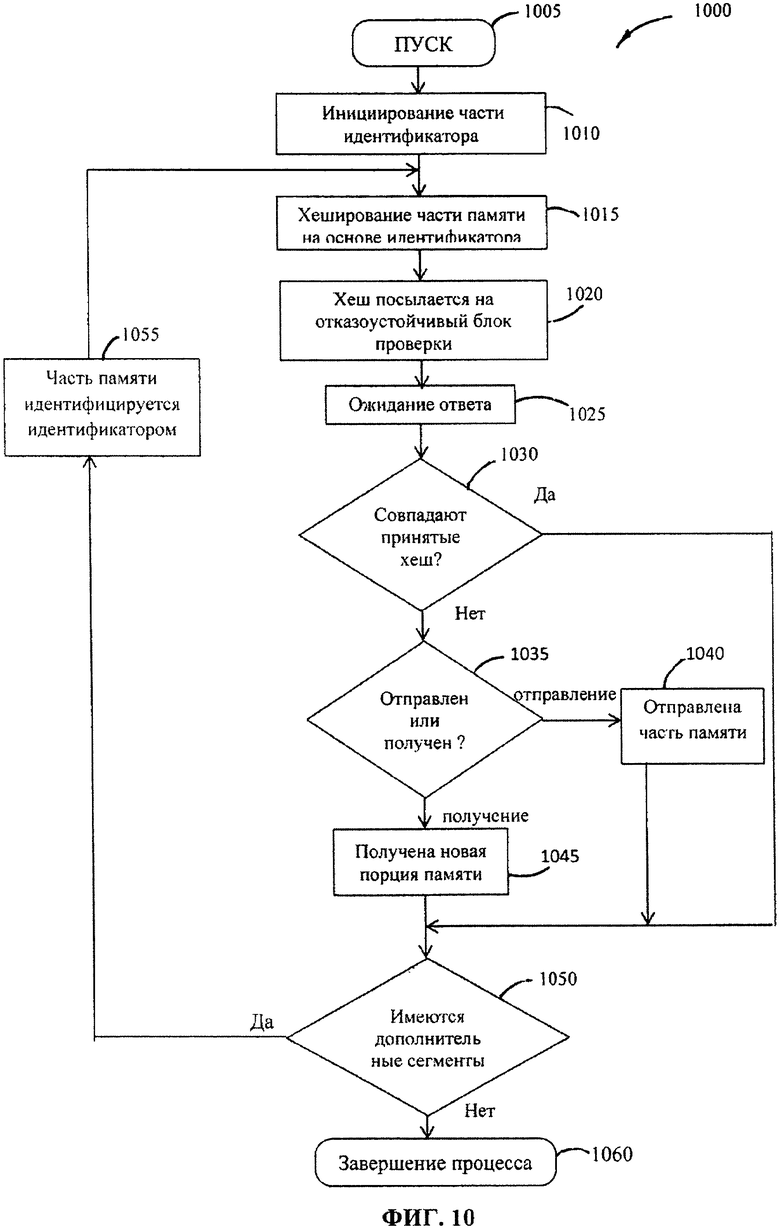

[0025] На фиг.10 показана блок-схема, иллюстрирующая пример процесса синхронизации памяти.

[0026] Как и условные обозначения, так и обозначения на различных чертежах обозначают одинаковые элементы.

ПОДРОБНОЕ ОПИСАНИЕ

[0027] Приведенное ниже описание относится к определенной реализации для целей представления инновационных аспектов настоящего изобретения. Однако человек, ориентирующийся в данной области техники, легко поймет, что идеи изобретения могут быть реализованы множеством различных способов. Таким образом, представление не предназначено для ограничения реализаций изобретения изображениями на чертежах, а может иметь широкое применение, как может быть понятно специалистам в данной области техники.

[0028] Одним из вариантов изобретения является отказоустойчивая системы обработки, имеющая улучшенные емкости и производительности. Система поддерживает высокую устойчивость к ошибкам, например, одним событием расстройства (ЕР), которые могут возникнуть, например, в космическом пространстве или в высотных самолетах. В этом варианте отказоустойчивая система обработки включает, по меньшей мере, один модуль обработки, который действует для управления и обработки данных для системы в целом. Каждый обрабатывающий модуль отказоустойчивой системы обеспечивает, путем включения, по меньшей мере, три вычислительных модуля, которые сконфигурированы таким образом, чтобы работать параллельно друг с другом, чтобы предотвратить ЕР, но могут включать в себя большее количество вычислительных модулей для дальнейшего улучшения надежности системы. В нескольких вариантах осуществления каждый вычислительный модуль работает независимо и параллельно другим модулям вычислений.

[0029] В то время как известные системы использовали системы с избыточными компонентами, которые могут быть повторно синхронизированы, производительность этих систем предшествующего уровня техники, может быть ограничена из-за характера их синхронизации. Например, в системах предшествующего уровня техники возможно соединение множества процессоров, контролеров когерентности, что сравнимо с синхронных выходами нескольких процессоров для обеспечения отказоустойчивой работы. Поскольку каждый из множества процессоров в этих системах в целом не гарантирован от воздействия ЕР, когерентность контролера не гарантирует, что операции процессора являются отказоустойчивыми. Это сравнение выходов может быть выполнена с каждым циклом, и, возможно, сравнению сигналов на адрес или линий передачи данных связан с процессором должны быть включены в вычислительные модули. Этот процесс может замедлить работу процессора, так как скорость когерентности контроллера возможно медленнее, чем максимальная скорость процессоров.

[0030] Доступ к памяти для этих известных систем, возможно, также ограничен. В этих системах памяти для процессоров могут быть предоставлены радиационно стойкие чипы памяти, доступные для процессоров через когерентность контролера. В некоторых случаях доступ к памяти через когерентный контроллер может замедлить работу процессора. В некоторых системах, взаимодействие между процессорами и контроллерами когерентности может быть медленнее, чем максимальная скорость поддерживаемых процессоров. Защищенные модули памяти, используемые в этих системах, могут также реализовывать на медленных скоростях доступ к данным, учитывая, что обычно радиационно стойкие конструкции, возможно, основаны на старых конструкций памяти.

[0031] Соответственно, некоторые представленные варианты могут улучшить производительность устройства за счет снижения зависимости каждого вычислительного модуля от взаимодействия с контролером когерентности. Например, современные процессоры могут быть сконструированы с несколькими адресами для данных. Используя эти современные процессоры, первый набор процессоров может быть оперативно соединен с контроллером когерентности, в то время как второй набор может быть соединен с другими компонентами аппарата и способен работать на более высокой скорости передачи данных. Процессор может затем выполнить определенные операции, не требующие строгого контроля когерентности использованием второго набора передающих соединений.

[0032] Для обеспечения дополнительного обнаружения и исправления ошибок из множества вычислительных модулей в этой конфигурации хэш состояние процессора могут быть выполнены в вариантах осуществления настоящего изобретения. Хэш состояние процессора можно сравнить, и вычислительное модули синхронизированы на основе результатов сравнения.

[0033] Некоторые реализации представленного здесь улучшения памяти производительность системы, обеспечивая каждый процессор непосредственной связью с локальной памятью для хранения состояния памяти или данных программы. В некоторых вариантах осуществления это локальное запоминающее устройство может быть подсоединено к процессору с помощью второго набора соединений, как описано ранее. Эта архитектура повышает скорость доступа и уменьшает потребность взаимодействовать с когерентностью контролера для каждого доступа к памяти процессора. По меньшей мере, часть адресного пространства процессора может быть непосредственно связана с блоком памяти. Поскольку напрямую связь памяти может быть незащищенной, память коммерческого класса может извлечь выгоду из более высокой плотности и более высоких скоростей доступны в коммерческом сегменте. В некоторых вариантах реализации, непосредственно связанных локальной памятью, отсутствует специальная защита от радиационного воздействия космического пространства, и, следовательно, может также быть восприимчивы к ЕР. В этом варианте осуществления, система будет также проверяться на когерентность памяти вместе с проверкой когерентности процессоров.

[0034] В одном из вариантов осуществления изобретения каждый процессор в вычислительном модуле включает в себя модуль хэширования, который имеет команды настройки процессора для получения данных о хэш состоянии, локальное запоминающее устройство, или комбинацию этих двух. Поскольку пространство памяти в каждом вычислительном модуле может быть относительно большим, объем памяти может быть разделен на предварительно заданных участках, и модуль выполнен с возможностью создавать только значение хеш-функции из конкретного сегмента или часть памяти. Таким же образом часть памяти из местных воспоминания в каждом вычислительном модуле затем хэшируется хеш-модулем для создания хэш-значений, которые могут быть сравнимы по нескольким вычислительных модулей.

[0035] В некоторых вариантах осуществления изобретения, система создает хэш-значения с регулярными временными интервалами во время работы системы. Например, система использует таймер, так что каждый 1, 2, 5, 10, 20, 30 или более миллисекунд система начинает проверку, чтобы убедиться, что хэш-значения из памяти или процессора данных соответствовали друг другу. Поскольку данных локальной памяти может быть относительно большой объем для передачи в хеш, система использует последовательный опрос всего пространства локальной памяти от вычислительного модуля, путем создания хеш-значения для различных частей памяти на каждом последовательном временном интервале. В этом варианте осуществления система делит память на части или сегменты, и в то время, t=1, создает и сравнивает значение хеш-функции первой части памяти от каждого вычислительного модуля. Затем в момент времени t=2 система создает и сравнивает значение хеш-функции второго участка памяти от каждого вычислительного модуля, и так далее, пока весь объем местный памяти каждого процессора не опрашивается. Это позволяет системе производить проверки памяти последовательно каждые несколько миллисекунд, так как процесс создания хеш относительно небольших порций памяти не столь компьютерно интенсивнее, чем в случае, если вся память хэшируется одновременно.

[0036] В некоторых реализациях изобретения, после того, как хэши создаются каждым процессором, хэши доводят до отказоустойчивых блоков проверки. Отказоустойчивой блок проверки может быть реализован в виде специализированной интегральной схемы (ASIC) или программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического устройства. Если отказоустойчивый блок проверки определяет, что хэши не совпадают, отказоустойчивой блок проверки может идентифицировать хэш, производимый большинством или меньшинством модулей.

[0037] В реализациях изобретения показано, что при хэшировании только части памяти с каждым временным интервалом, как описано выше, может привести к тому, что другие части памяти для каждого вычислительного модуля могут стать хэш-функцией в ответ на обнаружение несоответствия памяти хэшей между вычислительными модулями. Хэш каждой части памяти для каждого вычислительного модуля может затем сравниваться для определения любых дополнительных частей памяти, возможно содержащих ошибки. Такая конструкция признает, что повреждение памяти в одной части памяти может указывать на повышенную вероятность повреждения памяти в других частях памяти.

[0038] В некоторых других вариантах осуществления изобретения процессор, генерирующий инструкции, включающие хэширование, может генерировать хэш, который сочетает в себе данные состояния процессора с частью данных о локальном состоянии памяти. В некоторых вариантах осуществления часть памяти, которая включена в хэш, может изменяться с каждым хэш-поколением.

[0039] В некоторых реализациях изобретения адресное пространство каждого процессора также может быть сопоставлено с адресом, и линии данных контролируются отказоустойчивым блоком проверки. Другие реализации могут соединять отказоустойчивые блоки проверки. Отказоустойчивой блок проверки может определить, если один или более процессоров производит выходные данные, которые отличаются от большинства данных процессоров для обнаружения ошибки. После обнаружения ошибки работа процессора, вызвавшего ошибку, может быть приостановлена. В некоторых вариантах осуществления изобретения, процессору может быть разрешено продолжать работу при обнаружении ошибки. Это зависит от характера ошибки.

[0040] В некоторых реализациях изобретения, модуль обработки может не реагировать. Например, он может прекратить сигнализации адреса и линии данных, контролирующих отказоустойчивый блок проверки, или он может прекратить производство хэширование состояния данных процессора или данных о состоянии памяти. При таких обстоятельствах может быть предусмотрено средство для перезагрузки процессора. Например, отказоустойчивые модули проверки могут быть функционально соединены с линией сброса сигнализации процессора. Когда процессор сбрасывается, его состояние перезагружается, его данные и данные о состоянии памяти могут быть перезагружены в процессор данных о его состоянии и данных о состоянии памяти из другого модуля обработки.

[0041] В некоторых реализациях изобретения возможны одно или более следующих потенциальных преимуществ. Поскольку описанные способы, устройства и системы могут использовать коммерчески доступные модули памяти, большие объемы памяти могут быть предусмотрены для каждого вычислительного модуля при сохранении стоимостных параметров. Этот увеличенный объем памяти может обеспечить более быстрые и более мощные возможности. Например, более мощное программное обеспечение с расширенными возможностями может храниться в большей свободной памяти. Кроме того, увеличенный объем памяти может быть использован для увеличения размера кэша, обеспечивая быстрый доступ к данным и/или коду. Во-вторых, система может быть спроектирована таким образом, что сам доступ к данным может осуществляться с более высокой скоростью.

[0042] На фиг.1 показана блок-схема спутника 100, который включает в себя отказоустойчивую систему ПО обработки для управления различными функциями спутника 100. Например, отказоустойчивая система обработки 110 соединена с модулем управления двигателем 115, который контролирует работы двигателей спутника. Кроме того, отказоустойчивая система обработки 110 соединена с модулем солнечного развертывания 120, который включает в себя программированное управление развертыванием и позиционированием солнечных батарей на спутнике. Коммуникационный модуль 125 также может быть подключен к отказоустойчивой системе обработки 110, чтобы обеспечить каналы связи между спутником 100 и наземной станцией. При использовании отказоустойчивой компьютерной системы 110, спутник 100 снабжен системой, которая является надежной и устойчивой к ЕР. Спутник 100 может также включать в себя другие модули обработки для поддержания надежной вычислительной среды для спутника 100, не показанные на фиг.1.

[0043] Фиг.2 иллюстрирует блок-схему отказоустойчивой системы обработки 1 10, показанный на рисунке 1. Система включает в себя три отдельных вычислительных модуля 250, 260 и 270. Каждый вычислительный модуль включает в себя процессор. Например, вычислительный модуль 250 включает в себя процессор 210, вычислительный модуль 260 включает в себя процессор 211, вычислительный модуль 270 включает в себя процессор 212. Как показано, каждый процессор включает два внутренних регистратора. Например, процессор 220 включает регистраторы 214 и 215. Кроме того, процессор 211 включает в себя регистраторы 216 и 217, а процессор 212 включает регистраторы 218 и 219.

[0044] Доступной для каждого процессора является память 280. Память 280 доступна через отказоустойчивой блок проверки 230 (описано ниже). Каждый процессор может выполнять инструкции, сохраненные в запоминающем устройстве 280. В одной из реализаций изобретения, эти инструкции могут быть организованы в модуль операционной системы 285 и 290 модулях хэширования. Каждый процессор может читать инструкции, которые включены в операционную систему модулей 285 или 290 модулей хэширования. Эти инструкции могут настроить процессоры для выполнения функций. Например, модуль хэширования 290 может конфигурировать процессоры 210, 211, и 212 для выполнения хэширования по крайней мере части данных состояния соответствующего процессора. Например, команды в модуле хеширования 290 может настроить процессор 210 для считывания состояния данных, хранящихся в регистрах 214 или 215 для процессоров 210 и создать хэш. Таким образом, инструкции в модуль 290 хэширования выполняются на каждом из процессоров 215, 217 и 219 и представляют собой единое средство для хэширования с возможностью формирования хеш-значения для множества процессоров данных состояния. Как будет описано более подробно ниже, каждый процессор обеспечивает хэшированного данных состояния для сравнения, а отказоустойчивой системы обработки ПО может быстро и эффективно сравнивать состояния каждого процессора в системе, чтобы предотвратить любые ошибки.

[0045] Как показано на фиг.2, три процессора 210, 211, и 212 функционально соединены с блоком отказоустойчивой проверки 230, через линии 234, 235 и 236. Блок 230 настроен на сравнение хэшей, порожденных процессорами 210, 211, и 212, когда они выполняют инструкции включения в модуль хэширования 290. Например, отказоустойчивой блок проверки 230 может определить, являются ли три хэш, созданных процессорами 210, 211, и 212, равными при периодическом интервале. Если хэши не равны, блок отказоустойчивой проверки 230 может определить, равны ли, по крайней мере, большинство из хэшей. Таким образом, отказоустойчивой блок проверки 230 представляет собой одно из средств для сравнения множества хэш-значений. Этот процесс сравнения хэш-значения будет описан более подробно ниже.

[0046] Как известно, что создание хэшей относится к детерминированной процедуре, при которой могут быть получены данные переменного объема на вводе и выводе других данных фиксированного объема. Когда фиксированные данные процессора используются для выявления хэш-функции, любые небольшие изменения в данных состояния процессора приведет к большим и заметным изменениям в полученных хэш значениях. В одном из вариантов выполнения изобретения хэш возвращается процессоры при завершении выполнения команд, хранящихся в хэширования модуле 290, которые используется, для определения состояния каждого процессора того же типа и для синхронизации с другими процессорами.

[0047] Одна из хорошо известных хэш-функций, называется Secure Hash Algorithm или ″SHA″, была разработана Агентством национальной безопасности. Одним из вариантов SHA-1 является криптографической хэш-функция, информация о которой опубликована NIST в качестве Федерального стандарта США. SHA-1 использует 160-битный хэш-объем. Поскольку данные в пределах каждого хеш-значения значительно меньше, чем данные обо всех состояниях каждого процессора, рассматриваемый вариант, который сравнивает хэш-значения для каждого набора данных состояния процессора, является более эффективным.

[0048] Отказоустойчивой блок проверки 230 может быть сконфигурирован для повторной синхронизации вычислительных модулей 250, 260, и 270, когда он определяет, что три хэши генерирующих процессора 210, 211, и 212 не одинаковы. Таким образом, отказоустойчивой блок проверки 230 представляет собой средство для определения, является ли процессор в каждом вычислительном модуле синхронизированным с процессорами других модулей вычислений. Например, отказоустойчивое устройство контроля может повторно синхронизировать вычислительные модули 250, 260 и 270, когда один, два или все три из хэш не совпадают друг с другом. В одном варианте выполнения изобретения повторной синхронизации вычислительный модуль включает возможность восстановления состояния обработки вычислительного модуля, который произвел меньшинство хэш.

[0049] В некоторых вариантах осуществления изобретения состояние обработки вычислительного модуля, который произвел меньшинство хэш, может быть восстановлено на основе состояния обработки вычислительного модуля, который произвел большинство хэш. Например, если вычислительные модули 250 и 260 производят одинаковый объем хэшей, и вычислительный модуль 270 производит различные хэш-объемы, то вычислительный модуль 270 производит меньшинство хэш и вычислительные модули 250 и 260 производят большинство хэш. При таких обстоятельствах, постоянный объем процессора 210 в большинстве вычислительных модулей 250 может быть использован для восстановления значения процессора 212 в меньшинстве вычислительных модулей 270. Кроме того, значение переменного состояния процессора 211 в большинстве вычислительных модулей 260 также может быть использовано для восстановления состояния значения процессора 212 в меньшинстве вычислительных модулей 270.

[0050] Отказоустойчивый блок проверки 230 также может быть сконфигурирован для сравнения результатов вычислительных модулей 250, 260, и 270. Например, линии 234, 235 и 236 могут включать в себя адресные линии и линии данных процессоров 210, 211, и 212. Отказоустойчивый блок проверки 230 может сравнивать адреса и данные строк из вычислительных модулей 250, 260, и 270, и определять, если соответствующие линии между тремя вычислительных модулей соответствуют эквивалентным сигналам. Это сравнение может происходить на каждый цикле соединений для адресных линий и линий данных 234, 235 и 236.

[0051] Отказоустойчивых блок проверки 230 может определять выход большинства и дополнительный выход меньшинства на основе сигналов на линиях 234, 235, и 236. Отказоустойчивых блок проверки 230 может быть сконфигурирован для прохождения только большинства сигналов на другие аппаратные компоненты, например, в памяти 280. В то время как отказоустойчивой блок проверки 230 производит сравнение выходных сигналов от трех вычислительных модулях 250, 260 и 270, которые включают в себя три процессора 210, 211, 212, следует понимать, что отказоустойчивой блок проверки 230 может быть настроен на прием большего количества входов. Например, отказоустойчивой блок проверки 230 может сравнить выходы 5, 7, 9 или 11 процессоров для определения большинства и дополнительный выходной сигнал для определения меньшинства.

[0052] Как показано на фиг.2, отказоустойчивой блок проверки 230 соединен с основной памятью 280, которая используется отказоустойчивой системы обработки 110 для хранения данных, инструкций и программ, используемых системой 110. Кроме того, память 280 может включать в себя инструкции, которые конфигурируют процессоры 210, 211 и 212, например, путем считывания данных из модуля операционной системы 285 хранится в памяти 280 и загружается этой операционной системой на один или более процессоров в процессе восстановления.

[0053] Конечно, следует понимать, что каждый процессор, как показано на фиг.2, может быть как единичным устройством, так и одной из составляющих многопроцессорного устройства. Например, отказоустойчивая система обработки может включать в себя множество отдельных процессоров, таких, как сделанные INTEL или AMD. Наоборот, каждый процессор может быть одним из составляющих многопроцессорного устройства.

В некоторых случаях реализации изобретения возможно использование, как единичных процессоров, так и многопроцессорных устройств в системе 110.

[0054] На фиг.3 показан другой вариант отказоустойчивой системы обработки 300, но этот вариант осуществления отличается от варианта осуществления, показанного на фиг.2, с использованием отдельных банков памяти, связанных с каждым из процессоров. Как показано, система 300 включает в себя три вычислительных модуля 360, 370, и 380. Каждый вычислительный модуль содержит, по меньшей мере, один процессор. Например, вычислительный модуль 360 включает в себя процессор 330, в то время как вычислительный модуль 370 включает в себя процессор 331 и вычислительный модуль 380 включает в себя процессор 332.

[0055] Каждый процессор включает в себя внутренние регистры для хранения информации о состоянии процессора. Например, процессор 330 включает внутренние регистры 385 и 386. Процессор 331 включает в себя внутренние регистры 387 и 388, а процессор 332 включает в себя внутренние регистры 389 и 391. Каждый процессор также включает в себя контроллер памяти, связанный с процессором и служащий для контроля доступа к локальной памяти. В одном варианте осуществления изобретения локальным запоминающим устройством памяти является кэш-память. Например, процессор 330 включает в себя контроллер памяти 320 для управления доступом к локальной памяти 310. Кроме того, контроллер памяти процессоров 321, 331 управляет доступом к локальной памяти 311, и контроллер памяти процессора 332 управляет доступом к локальной памяти 312.

[0056] Следует понимать, что каждая локальная память может быть разделена на множество сегментов памяти. Например, локальная память 312 вычислительного модуля 380 разделена на четыре сегмента памяти в показанном примере. Эти сегменты памяти, которые определены как элементы 318A-D.

[0057] Следует также понимать, что локальная память может храниться вне процессора, или в качестве встроенной памяти на кристалле процессора. В некоторых вариантах осуществления изобретения локальная память является быстрым доступом к кэш-памяти и памяти сегментов кэш-памяти. В других вариантах осуществления локальная память является стандартной памятью с произвольным доступом, выполненной с возможностью хранения данных программы в дополнение к специфическим данным для конкретного процессора.

[0058] Как и в варианте осуществления, представленном на фиг.2, каждый вычислительный модуль может выполнять инструкции, включенные в модуль 345 хэширования. Инструкции в модуле хэширования 345 могут конфигурировать процессор вычисления значения хеш-функции из состояния данных, хранящихся в регистрах процессора. В то время как модуль хэширования 345 иллюстрируется как хранящийся в памяти 390, которая является доступной для вычислительных модулей 360, 370 и 380 через отказоустойчивой проверки блока 350, модуль хэширования 345 может вместо этого, быть сохранен в локальной памяти 310, 311,312. Эти локальные памяти могут обеспечить более быстрый доступ к коду сегментов, таких, как те, которые предусмотрены модулем хэширования 345. В других вариантах осуществления модуль хэширования 345 может храниться в памяти 390 и локальной памяти 310, 311, 312.

[0059] В некоторых вариантах осуществления модуль хэширования 345 конфигурирует процессоры для создания хеш и включает в себя данные из локальной памяти, связанные с каждым процессором. Например, когда инструкции, включенные в модуль хэширования 345, выполняются процессором 330, процессор 330 может создавать хэш для представления состояния процессора 330 и локальной памяти 310. Аналогичным образом, инструкции в модуле хэширования 345, которые выполняются процессором 331, приводят к тому, что процессор 331 может создать хэш для представления состояния процессора 331 и локальной памяти 311. Когда инструкции в модуле хеширования 345 выполняются процессором 332, процессор 332 может создать хэш, чтобы представить состояние процессора 332 и 312 локальной памяти. Таким образом, инструкции, включенные в модуль 345 хэширования, работающие на каждом из процессоров 330, 331 и 332, могут представлять собой одно средство для хэширования, выполненное с возможностью формирования хеш-значений состояния данных процессора из нескольких вычислительных модулях.

[0060] Как описано выше, хэш-операции могут включать в себя любые операции, которые однозначно отображают перевод большего набора данных в меньший набор данных. Например, хэш может отобразить несколько байтов, которые включают обработку состояния данных, хранящихся в регистрах 385 и 386, в четыре байта. Хэш может также позиционироваться как состояние обработки данных и памяти в меньший набор данных, например, объемом в четыре байта. Например, хэш может отображать содержимое обработки состояние данных в регистрах 385 и 386, а также с содержанием по меньшей мере части локальной памяти 310, в четыре байта. В некоторых реализациях хэш может быть контрольной суммы производимой SHA-1 хэш-алгоритма.

[0061] Инструкции в модуле хэширования 345 могут также конфигурировать процессоры 330, 331 и 332 для изменения состояния памяти данных, используемых для создания хеш. Например, когда инструкции в модуле хэширования 345 проявляются в вычислительном модуле 1 процессора 330, первый хеш может отображать состояние обработки данных регистров 385 и 386, вместе с памятью о данных сегмента 316а памяти в хэш. В одном примере хэш представляет четыре байта. Когда второй хеш производится процессором 330, модуль хэширования 345 может определять состояние обработки данных регистров 385 и 386, вместе с памятью сегмента 316b в хеш, например, еще четыре байта. После перемешивания модуль 345 работает на процессор 330, включает все сегменты памяти 310 в хеш, инструкции в модуле хэширования 345 может конфигурировать процессор 330, чтобы вернуться к сегменту памяти 316а и повторить цикл. Таким образом, в пределах инструкций модуль хэширования 345, работающий на процессорах 330, 331 или 332, представляет собой средство для хэширования комбинированного состояния данных процессора и состояния данных для каждого вычислительного модуля.

[0062] В некоторых реализациях модуль хэширования может не включать в себя инструкции, которые настраивают процессоры 330, 331 и 332 для создания хеш для локальной памяти 310, 311 и 312, как описано выше. В этих вариантах осуществления отдельная когерентность памяти может быть обеспечена блоком проверки 352. Блок проверки когерентности памяти 352 может быть сконфигурирован для мониторинга адреса, данные и управляющих линий между процессорами и соответствующими им для локальной памяти. Как показано, блок проверки когерентности памяти 352 выполнен с возможностью отслеживать линии между процессором 330 и локальной памяти 310 через линии 354. Блок проверки когерентности памяти 352 также может контролировать адрес, данные и управляющие линии между процессором 331 и памятью 311 через линии 356 и процессор 332 и память 312 через линии 358. Контролируя эти адреса, данные и линии управления, блок проверки когерентности памяти 352 может быть сконфигурирован для обнаружения ошибок в памяти 310, 311 и 312 путем выявления несоответствий между данными памяти. Блок проверки когерентности памяти 352 может быть дополнительно сконфигурирован для сигнализации отказоустойчивый блоком проверки 350 через отдельные линии сигнализации (не показан) при обнаружении такой ошибки.

[0063] В некоторых других вариантах осуществления изобретения, могут быть использованы как блок проверки когерентности памяти 352, так и модуль хэширования 345. Например, в некоторых из этих вариантов осуществления может начаться повторная синхронизация процесса на основании ошибки, обнаруженной модулем 352. Процессы ресинхронизации могут сами быть синхронизированы между модулями обработки, так как меньшинство и большинство модулей обработки, возможно, операционно разделены. Эта синхронизация может быть основана на периоде события или определенном времени, прошедшем после начала повторной синхронизации. Для координации процесса ресинхронизации между модулями обработки, модуль хэширования 345 может конфигурировать процессоры для хеширования части данных состояния процессора или данных о состоянии памяти. Эти хэши могут использовать отказоустойчивый блок 350 проверки для выявления различий в этих состояниях между модулями обработки. Эта информация может помочь модулям обработки 360, 370 и 380 для возвращения в операционный процесс.

[0064] В еще одних вариантах осуществления система 300 может включать прямой доступа к памяти (DMA) возможностей. Эти возможности DMA могут обеспечить способность читать и писать на участках локальной памяти 310, 311 и 312, не загружая каждое слово памяти для переработка в процессорах 330, 331 и 332. Это может позволить сбор данных из памяти для хэш вычислений осуществлять параллельно с работой процессоров 330, 331 и 332. В некоторых вариантах осуществления процессоры 330, 331 и 332 могут включать в себя интегрированные DMA возможности.

[0065] Некоторые варианты осуществления могут предусматривать дополнительные аппаратные компоненты для контроля процесса хеширования. В некоторых из этих вариантов осуществления, специализированные процессоры или аппаратные компоненты могут контролировать процесс DMA, который считывает данные из памяти. Эти данные могут быть использованы для создания хеш. Некоторые из этих вариантов осуществления могут также получить данные состояния процессоров 330, 331 и 332 с использованием специализированных аппаратных компонентов. Эти аппаратные компоненты могут затем вычислить хэши по мере необходимости на основе собранных данных и отправлять хэш информации в отказоустойчивый модуль проверки 350. Эти варианты могут обеспечивать повышенную производительность по сравнению с вариантами, которые используют существующие мощности процессора для периодических расчетов хэшей, варианты могут быть предусматривать также увеличение стоимости.

[0066] Каждый из процессоров 330, 331 и 332 при работе модуля хэширования 345 может создать хеш, как описано выше для соответствующего модуля вычислений. Хэш из каждого процессора может быть передан в отказоустойчивый блок проверки 350. В одном из вариантов осуществления отказоустойчивой блок проверки 350 сконфигурировано для сравнения хэшей, генерированных процессорами 330, 331 и 332, чтобы определить хэш большинства и необязательные хэш меньшинства. Отказоустойчивость модуль проверки 350 может инициировать повторную синхронизации вычислительных модулей 360, 370, и 380, когда хэши, предоставляемые процессорами 330, 331 и 332, отличаются. Отказоустойчивой модуль проверки 350 может представлять одно средство для определения, является ли процессор в каждом вычислительном модуль синхронизированным с процессором других модулей вычислений.

[0067] Отказоустойчивой блок проверки 350 может инициировать повторную синхронизацию путем посылки сигнала повторной синхронизации в модуль 349, который работает на каждом процессоре 330, 331 и 332. Модуль ресинхронизации 349 включает в себя инструкции, которые настраивают каждый процессор на выполнение повторной синхронизации. Модуль повторной синхронизации 349 может храниться как часть памяти 390.

[0068] Повторной синхронизация вычислительных модулей 360, 370, и 380 может контролироваться модулем повторной синхронизации 349, представленным на фиг.3. Отказоустойчивой блок проверки 350 вместе с инструкциями повторной синхронизации работает на каждый из процессоров 330, 331 и 332 и представляет собой одно средство для повторной синхронизации вычислительных модулей на основе хэш генерированных процессорами 330, 331, и 332.

[0069] Модуль ресинхронизации 349 может включать в себя инструкции настройки каждого из процессоров 330, 331 и 332 на обновление состояния обработки данных или данных о состоянии памяти вычислительного модуля, который произвел меньшинства хэш. В некоторых вариантах осуществления состояние обработки вычислительного модуля, который произвел меньшинство хэш, может быть обновлено на основе состояния обработки вычислительного модуля, который произвел большинство хэш. Например, если вычислительные модули 360 и 370 производят равный объем хэшей, а вычислительный модуль 380 производит отличный объем хэшей, то вычислительный модуль 380 производит меньшинство хэшей, а процессоры 360 и 370 производят большинство хэшей. В этом примере состояние обработки данных и данных о состоянии или в вычислительном модуле 380 может обновляться на основе состояния обработки данных и памяти о состоянии данных вычислительным модулем 360 или вычислительным модулем 370.

[0070] При производстве меньшинства хэш, вычислительный модуль 380 может получить новое состояние из любого вычислительного модуля 360 или вычислительного модуля 370. Например, вычислительный модуль 380 может получить новое состояние регистров 389 и 391 от вычислительного модуля 360. Данные о новом состоянии могут быть получены из регистров 385 и 386 процессора 330. Данные о новом состоянии могут быть переданы непосредственно от вычислительного модуля 360 к вычислительным модулям 380 через линию 361, которая соединяет процессоры 330, 331 и 332. В некоторых реализациях, соединением 361 может быть PCI Express соединение или другое высокоскоростное соединение с прямым подключением к каждому процессору системы 300.

[0071] Новые данные, полученные от состояния либо вычислительного модуля 360, либо вычислительного модуля 370 могут также включать данные о состоянии памяти. Например, вычислительный модуль 380 может получить новые данные о состоянии памяти для части или всей памяти 312 от вычислительного модуля 360. Новые данные о состоянии памяти может быть получено из памяти 310. Например, один или несколько сегментов памяти 316а-д могут быть переданы по каналу 361 к вычислительным модулям 380. Вычислительный модуль 380 может затем заменить содержимое памяти 312 с состоянием памяти данных, полученных от вычислительного модуля 360. Например, вычислительный модуль 380 может заменить данные о состоянии памяти для одного или более сегментов памяти 318а-д при получении соответствующие одному или более сегментам памяти 316а-д данные из вычислительного модуля 360.

[0072] До завершения ресинхронизации существует вероятность того, что в большинстве вычислительных модулей могут возникнуть ЕР. Это может привести к неправильной передаче процессором данных о его состоянии или о состоянии памяти данных в вычислительном модуле меньшинства. Эта ошибка сценария может привести к тому, что несколько вычислительных модулей будут генерировать эквивалентные результаты после повторной синхронизации. Однако, если ЕР произошло в данных о состоянии, прежде чем оно был передан от модуля вычислений для большинства вычислительному модулю меньшинства, модуль большинства модули меньшинства могут генерировать эквивалентные, но неверные результаты после повторной синхронизации. Поскольку эти два устройства могут образовывать большинство, например, в вариантах осуществления, использующих только три модуля вычислений, эти неправильные выходы могут быть приняты как большинство, если не предусмотрена дополнительная защита.

[0073] Чтобы избежать этого случая, некоторые варианты осуществления могут выполнять дополнительную проверку после повторной синхронизации прежде, чем процесс будет завершен. Например, эти варианты осуществления могут выполнять дополнительные частичные повторные синхронизации для проверки совпадения хэш, генерированных модулями обработки. Если вычислительные модули, которые составляли большинство в течение предыдущего процесса повторной синхронизации, не генерируют соответствующие хэши, процедуры восстановления могут быть целесообразны. Кроме того, если хэш вычислительного модуля меньшинства не соответствует хэш вычислительных модулей большинства, процедуры восстановления также могут быть целесообразны. Например, ошибка может быть помечена как результат сравнения этих хэшей. Перезагрузка отказоустойчивой системы обработки может быть выполнена в результате ошибки. Хотя это может нарушить работу, в то же время она может вернуть систему к правильной работе.

[0074] Когда данные состояния переданы между процессором 330 и процессором 331, соединение 362 может быть использовано, непосредственно для объединения этих процессоров. Аналогичным образом, когда новые данные о состоянии передаются между процессором 331 и процессором 332, соединение 364 может быть использовано для непосредственного объединения эти двух процессоров.

[0075] Каждый процессор может также иметь доступ к банку памяти 390 через отказоустойчивой блок проверки 350. Например, каждый процессор может обращаться к памяти 390 после проверки согласованности выходов из процессоров, как описано выше по отношению к фиг.2 и осуществляется блоком отказоустойчивой проверки 350. Локальная память 310, 311 и 312, или память, доступная через отказоустойчивый блок 350 проверки, такая как память 390, может хранить инструкции настройки процессоров 330, 331 и 332 для выполнения функций. Например, процессоры 330, 331 и 332 могут читать локальные ячейки памяти в памяти 390 через отказоустойчивой блок проверки 350. Память 390 может включать в себя инструкции, предназначенные для настройки процессоров 330, 331 и 332. Память 390 может также включать в себя инструкции для операционной системы (не показано), или повторной синхронизация модуля 349. Кроме того, каждый процессор 330, 331 и 332 может читать инструкции из локальной памяти в пределах своего вычислительного модуля. Например, процессор 330 может читать инструкции от локальной памяти 310. Процессор 331 может читать инструкции из памяти 311, и процессор 332 может читать инструкции от локальной памяти 312.

[0076] На фиг.4 представлена блок-схема, иллюстрирующая пример процесса 400, который может работать в отказоустойчивом блоке проверки для сравнения хэш, принятых от множества вычислительных модулей. В некоторых вариантах осуществления процесс 400 может быть реализован посредством указания блоку отказоустойчивой проверки блока 350 на фиг.3, или блоку отказоустойчивой проверки 230 на фиг.2. Процесс 400 начинается с пуска блока 405 и затем переходит к обработке в блоке 410, где процесс 400 ожидает инициирования частичной повторной синхронизации. В некоторых реализациях процессы частичной повторной синхронизации из процессоров могут выполняться периодически, чтобы каждый процессор находится в синхронизации с другими процессорами в системе. Некоторые варианты осуществления могут выполнять частичную синхронизацию каждые 1, 2, 5, 10, 20 или более миллисекунд.

[0077] Как только процесс 400 определяет время для выполнения частичной повторной синхронизации, процесс 400 переходит к блоку 415 обработки, где процессоры выдают сигнал для выполнения частичной повторной синхронизации. После получения сигнала о частичной повторной синхронизации, процессоры могут хэш данные об их состоянии или данные их памяти. Частичная повторная синхронизация представлена ниже на рисунке 5. Процесс 400 затем перемещается в блок обработки 420, где находятся хэши, полученные от всех модулей обработки. Процесс 400 затем переходит к блоку 425 для определения эквивалентности хэшей. В некоторых реализациях хэш может включать в себя отдельный хеш состояния данных процессора и данных памяти о состоянии каждого вычислительного модуля. Некоторые реализации могут сочетать хэши состояния обработки данных и состояния памяти в одном хэш-значении. В некоторых вариантах осуществления часть хеш, который представляет данные о состоянии памяти, может представлять только часть данных состояния вычислительных модулей памяти. Другие реализации могут включать хэш представление данных о состоянии памяти всех вычислительных модулей.

[0078] Если хэши эквивалентны, процесс 400 переходит в блок 450, а 400 процесс прекращается. Если не все хэши совпадают, могут быть хэш меньшинства и, по крайней мере, два хэш большинства. Процесс 400 затем перемещается от блока 425 к блоку обработки 430, где модули обработки сигнализируют о выполнении полного восстановления синхронизации.

[0079] Полная повторная синхронизация будет синхронизировать состояние данных процессора или данных о состоянии памяти для вычислительных модулей, которые генерируют хэш меньшинства, с данными состояния вычислительного модуля, который породил большинство хэш. Процесс ресинхронизации представлен на рисунке 6. Процесс 400 затем переходит к блоку 435, где процесс 400 посылает сигнал в меньшинство вычислительных модулей, указывая, что они будут приобретать новые состояния. Процесс 400 затем переходит к блоку обработки 440, где процесс 400 передает сигнал, по крайней мере, одному из большинства вычислительный модулей, инструктируя модуль большинства о том, что он должен посылать новые данные о состоянии в вычислительный модуль меньшинства. Процесс 400 затем переходит к блоку 445, где он ожидает поступления данных от всех вычислительных модулей для завершения повторной синхронизации. Процесс 400 затем перемещается в конечное состояние 450.

[0080] На фиг.5 показана блок-схема последовательности операций примерного процесса перемешивания. В некоторых вариантах осуществления процесс 500 может быть реализован посредством инструкций, включенных в модуль хэширования 290 на фиг.2. Кроме того, процесс 500 может быть реализован посредством инструкций, включенных в модуль хэширования 345 на фиг.3. Процесс 550 начинается в начальном состоянии 555, а затем переходит к блоку 560, где он ожидает сигнал частичной повторной синхронизации. Сигнал частичная повторная синхронизация может быть послан процессом 400, как представлено выше. При получении сигнала частичной повторной синхронизации процесс 550 переходит к блоку 565 обработки, в которым данные состояния процессора хэшируется. Для реализации блока 565, процессор 330 вычислительного модуля 360 может быть сконфигурирован по инструкции, включенной в модуль хэширования 345 для хеширования данных процессора о состоянии блоков 385 и 386. Процесс 550 затем переходит к блоку 570 обработки, где данные о состоянии памяти хэшируется. Для реализации блока 570, процессор 330 вычислительного модуля 360 может быть сконфигурирован по инструкции, включенной в модуль хэширования 345, показанный на фиг.3, для хэширования одного или более фрагментов памяти 316а-г. Процесс 550 затем переходит к блоку 575, где хэш или хэш от совместного перемешивания данных состояние процессора в блоке 565 памяти, и данных о состоянии в блоке 570 направляются в отказоустойчивый блок проверки. Например, процессор 330 может послать хэш отказоустойчивому блоку проверки 350 для осуществления обработки данных состояния блока 570. Процесс 550 затем перемещается в конец блока 580.

[0081] На фиг.6 показана блок-схема последовательности операций примерного процесса 600, который выполняет полную повторную синхронизацию вычислительного модуля. Процесс 600 может быть реализован посредством инструкций, включенных в модуль 349 повторной синхронизации, показанной на фиг.3. Кроме того, процесс 600 может быть реализован с помощью повторной синхронизации модуля локальной памяти, такой, как память 310, показанной на фиг.3. Эти инструкции могут работать на базе процессора в вычислительном модуле. Например, команды могут работать на процессоре 330 вычислительных модулей 360.

[0082] Процесс 600 начинается с запуска блока 605 и затем переходит к блок обработки 610, где процесс 600 ожидает в запрос о полной повторной синхронизации. При получении запроса о повторной синхронизации, процесс 600 переходит к блоку 615, где хранятся данные о состоянии процессора. Например, если процессор 330 вычислительного модуля 360 получает запрос о повторной синхронизации, он может сохранить регистры 385 и 386 при выполнении обработки блока 615 процесса 600. Процесс 600 затем переходит к блоку 620, где определяет получение им нового состояния. Если новое состояние получено, процесс 600 переходит к блоку 650, где новые данные о состоянии процессора получены. Процесс 600 затем переходит к блоку 655, где новые данные о состоянии памяти получены. В некоторых реализациях этого состояния памяти могут включать состояние всей локальной памяти, например, локальной памяти 310, 311, или 312, как показано на рисунке 3. В других реализациях это состояние памяти может включать только сегменты локальной памяти. Например, она может включать в себя только один сегмент памяти, например, сегмент памяти 316а, 317а или 318а, также показанные на фиг.3. После того, как данные о состоянии памяти получены, процесс 600 переходит к блоку обработки 640, откуда посылается сигнал, что восстановление синхронизации завершено.

[0083] Возвращаясь к решению блока 620, если новое состояние не будет получено вычислительным модулем, процесс 600 переходит к блоку принятия решения 625, где определяется необходимость передачи данных об изменении состояния.. Если данные об изменении состояния не должны быть направлены, процесс 600 переходит к блоку 640, где он сигнализирует, что процесс его повторной синхронизации завершен. Если в решающем блоке 625 определено, что модуль обработки выполняемого процесса 600 должен послать данные о состоянии, процесс 600 переходит к блоку 630 обработки, откуда передаются сохраненные данные состояния процессора. Процесс 600 затем перемещается в блок обработки 635, где новые данные о состоянии памяти будет отправлено. Состояние памяти данных, передаваемых в блоке 635, может включать в себя часть или всю локальную память. Например, она может включать в себя часть памяти 310, например, 316а сегмент памяти. Альтернативно, она может включать в себя два сегмента памяти, к примеру, сегменты памяти 316 а-б. Тем не менее, другие реализации могут отправить весь памяти 310, включая сегменты памяти 316 а-д. Процесс 600 затем переходит к обработке этапа 640, где она сигнализирует, что его часть повторной синхронизации. После обработки блока 640, процесс 600 переходит к блоку 645, где процесс 600ожидпет завершения повторной синхронизации всех вычислительных модулей. Когда все модули обработки дали понять (через блок обработки 640), что их повторная синхронизация событий завершена, процесс 600 переходит к блоку 670, где сохраненные данные обработки из блока обработки 615 восстанавливаются, и процесс 600 возвращается с места событий. Процесс 600 затем перемещается в конец блока 680.

[0084] На фиг.7 показана блок-схема, иллюстрирующая примерную реализацию хэш-метода. Процесс 700 может быть реализован посредством инструкций, включенных в модуль хэширования 345, как показано на рисунке 3. Процесс 700 начинается с пуска блока 710 и затем переходит к блоку обработки 720, где хэш инициируется. Процесс 700 затем переходит к блоку обработки 730, где происходит обработка данных состояния хэш-таблицы. Например, процессор 330 может быть сконфигурирован по инструкции в модуль хэширования 345 для хэширования состояния процессоров 385 и 386 для с целью введения блока обработки 723. Процесс 700 затем переходит к блоку 740, где он определяет, будет ли выполнено полное или частичное хэширование памяти.. Процесс 700 переходит к блоку обработки 750, если будет выполняться полное хэширование памяти, Блок 750 обработки может включать в себя все содержимое памяти при определении значения хэш-функции. Если блок 740 определяет, что только часть памяти будет включена в хэш, процесс 700 переходит к блоку 780 обработки, где используется локальный идентификатор сегмента памяти. Процесс 700 затем переходит к блоку 790, где перемешивание продолжается для сегментов памяти, определенных идентификатором сегмента.

[0085] Локальный идентификатор сегмента памяти может отслеживать сегменты памяти, которые должны быть включены в хэш. Например, некоторые реализации могут отличаться сегментами памяти, которые включаются в хэш для каждой частичной повторной синхронизации. Каждая последующая частичная повторная синхронизация может включать в себя различные сегменты памяти как часть значения хэш-функции. Когда все сегменты памяти из памяти включены как часть частичной повторной синхронизации, процесс 700 может снова использовать содержимое первого сегмента памяти в хэш. Эти дополнительные включения различных сегментов памяти может повторить.

[0086] После того, как определили сегмент памяти для включения в хэш, процесс 700 переходит к блоку 760, где хэш предоставляется. Например, хэш может быть предоставлен в отказоустойчивом блоке проверки 350, как показано на рисунке 3. Процесс 700 затем перемещается в конец блока 770.

[0087] На фиг.8 показана блок-схема, иллюстрирующая примерный процесс 655 получения памяти. Процесс 655 может быть реализован посредством инструкций, включенных в модуль 349 повторной, как показано на рисунке 3. Кроме того, процесс 655 может быть реализован посредством команд, хранящихся в локальной памяти 310, 311 или 312, также представлен на фиг.3. Процесс 655 начинается с пуска блока 805 и затем переходит к этапу 810, где определяет, будет ли вычислительный модуль выполняемого процесса 655 получать полную память или частичное изображение памяти. При приеме полной памяти, процесс 655 переходит на блок обработки 820, где полная память получена. Например, вычислительный модуль 360 может получать памяти изображений для локальной памяти 310. Это изображение может дать новые данные о состоянии памяти для каждого сегмента памяти локальной памяти 310, включая сегменты памяти 316а-д. Процесс 655 затем перемещается в конец блока 850. Возвращаясь к этапу 810, он процесс 655 определяет, что только частичное изображение памяти может быть получено, затем процесс 655 переходит к блоку 830, где сегмент памяти будет получен. Например, вычислительный модуль 360 может получать изображение для сегмента памяти локальной памяти 310. Например, изображение от 316а сегмента памяти могут быть получено в блоке обработки 830. Процесс 655 затем переходит к блоку 840, где полученный локальный сегмент памяти заменяет сегмент памяти на основе идентификатора сегмента. Сегмент ID ссылки в блоке 840 может быть одинаковым с ID сегментом, как ссылка в блоке 780 процесса 700, как показано на рисунке 7. Процесс 655 затем перемещается в конец блока 850.

[0088] На фиг.9 показана блок-схема, иллюстрирующая примерный процесс передачи из памяти 635. Процесс 635 может быть реализован посредством инструкций, включенных в модуль 349 повторной синхронизации, как показано на рисунке 3. Процесс 635 начинается с пуска блока 905 и затем переходит к этапу 910, где определяется, будет ли полная память отправлена или частичное состояние памяти будет отправлено. Если полное состояние памяти будет отправлено, процесс 635 переходит к блоку 920, куда полое состояние памяти будет отправлено. Процесс 635 затем перемещается в конец блока 950. Если частичное изображение памяти будет отправлено, процесс 635 переходит к блоку 933, где сегмент памяти идентифицируется на основании идентификатора сегмента. Сегмент, идентифицированный в блоке 930, может быть таким же, как идентифицированный в блоке 780, как показано на рисунке 7. Процесс 635 затем переходит к блоку 940, куда посылают сегмент памяти, определенный идентификатором. Процесс 635 затем перемещается в конец блока 950.

[0089] На фиг.10 показана блок-схема, иллюстрирующая примерный процесс отправки и приема памяти. Процесс 1000 может быть альтернативной реализацией процессов 635 или 655, которые обсуждались ранее. Процесс 1000 может быть реализован посредством инструкций, включенных в модуль 345 хэширования или в модуль 349 повторной синхронизации, модуль 349, или сочетанием двух модулей, как показано на фиг.3. Несколько модулей обработки, например, модули обработки 360, 370 и 380, как показано на рисунке 3, могут выполнять процесс 1000 по существу одновременно с ресинхронизацией локального содержания памяти между модулями обработки.

[0090] Процесс 1000 начинается с начального блока 1005, а затем переходит к блоку 1010, где часть идентификации инициируется. Эта часть идентификатора может быть использована для идентификации часть памяти, такой как часть локальной памяти 310. 311. или 312. В некоторых вариантах осуществления частью памяти может быть сегмент памяти. Процесс 1000 затем переходит к блоку 1015, где часть памяти хэшируется на основе идентификации. Процесс 1000 затем переходит к блоку 1020, где хеш посылается отказоустойчивой блок проверки, например отказоустойчивый блок проверки 350 на фиг.3.

[0091] Процесс 1000 затем переходит к блоку 1025 в ожидании ответа от отказоустойчивого блока проверки. Например, отказоустойчивые блок проверки может сравнивать хэши, отправленные вычислительными модулями 360, 370, 380 и 1000. После того, как будет получен ответ, процесс 1000 переходит к блоку принятия решений 1030, где определяется, совпадают ли принятые хэши. Например, отказоустойчивый модуль проверки 350 может отправить ответ на модули обработки запущенного процесса 1000, указывающее соответствует ли хэщ в блоке обработки 1015 хэшам, созданным другими модулями обработки. Если хэши соответствуют, процесс 1000 переходит к блоку принятия решения 1050.

[0092] Если хэши не совпадают, процесс 1000 переходит к блоку принятия решения 1035, где он определяет, является ли конкретный экземпляр процесса 1000 отправке или получению данных. Если хэши не совпадают, один модуль обработки, возможно, создали хэш меньшинство. Модуль обработки создает хэш меньшинства, и запущенный процесс 1000 может получить новую часть памяти, чтобы выполнить повторную синхронизацию с обработкой модулей, которые создают большинство хэшей. Модуль меньшинства может переходить от блока 1035, блокировать к блоку 1045. В блоке 1045, процесс 1000 может получить новую порцию памяти от другого модуля обработки, например, модуля обработки, который создал большинство хэш.

[0093] Другой вычислительный модуль выполнения процесса 1000, возможно, создал большинство хэш. Этот модуль обработки может определить в блоке принятия решения 1035, пошлет ли он часть памяти на модуль обработки, который создал меньшинство хэш. В этом случае этот модуль обработки могут перемещаться из блока принятия решения 1035 к блоку 1040.

[0094] После того, как часть памяти был отправлена через блок 1040 или получена с помощью блока 1045, процесс 1000 переходит к блоку принятия решений 1050, где определяется, имеются ли дополнительные порции памяти, которые должны быть синхронизированы. Если нет остальных частей, процесс 1000 переходит в конечное состояние 1060. Если есть остальные части, процесс 1000 переходит к блоку 1055, где осуществляется идентификация памяти. Процесс 1000 затем возвращается к блоку 1015 и часть памяти идентифицируется идентификатором для хэширования в блоке 1055. Процесс 1000 затем повторяется, как описано выше.

[0095] Различные иллюстративные логические схемы, логические блоки, модули, схемы и этапы алгоритма, представленные в связи с раскрытыми здесь реализаций, могут быть реализованы в виде электронных аппаратных средств, компьютерного программного обеспечения или их комбинации. Взаимозаменяемость аппаратных средств и программного обеспечения была описана как правило, с точки зрения функциональности, и различные иллюстративные компоненты, блоки, модули, схемы и этапы представлены выше. Реализованы ли такие функциональные возможности в аппаратном или программном обеспечении, зависит от конкретного применения и конструктивных ограничений, наложенных на всю систему.

[0096] Аппаратных средства и устройства обработки, используемые для реализации различные иллюстративные логики, логические блоки, модули и схемы, описаны в связи с раскрытыми аспектами возможной реализации или выполнены с помощью универсального одно- или мульти-чип процессора, цифровой сигнальный процессора (DSP), специализированной интегральной схемы (ASIC), программируемой пользователем вентильной матрицы (FPGA) или другого программируемого логического устройства, дискретного логического элемента или транзисторной, дискретных компонентов аппаратных средств или любой их комбинации, предназначенных для выполнения функций, описанных здесь. Процессор общего назначения может быть микропроцессором, или любым обычным процессором, контроллером, микроконтроллером или конечным автоматом. Процессор также может быть реализован как комбинация вычислительных модулей, например комбинация ЦСП и микропроцессора, множества микропроцессоров, одного или более микропроцессоров в соединении с ЦСП-ядром или любой другой такой конфигурацией. В некоторых реализациях конкретные шаги и способы могут быть выполнены в виде схемы, которая является специфической для конкретной функции.

[0097] В одном или более аспектах, описанные выше функции, могут быть реализованы в аппаратном обеспечении цифровых электронных схем, программного обеспечения, микропрограммного обеспечения, включая структуры, раскрытые в данном описании, и их структурные эквиваленты, или в любой их комбинации. Реализации предмета представлены в данном описании, также могут быть реализованы в виде одной или более компьютерных программ, то есть один или несколько модулей инструкций компьютерной программы, закодированные на компьютерные носители для исполнения, или для управления работой, аппаратом обработки.

[0098] Различные модификации в реализации, представленные в данном описании, могут быть очевидны специалистам в данной области техники, а общие принципы, определенные здесь, могут применяться в других вариантах осуществления без отхода от сущности или объема этого раскрытия. Таким образом, формула изобретения не должна ограничиваться реализациями, показанными здесь, но должно соответствовать самому широкому объему, совместимому с этим изобретением, принципами и новыми признаками, раскрытыми в данном документе. Слово ″примерный″ используется здесь исключительно в значении ″служащий в качестве примера, отдельного случая или иллюстрации″. Любые реализации, представленные здесь как ″примерный″, не обязательно должен быть истолкован как предпочтительный или преимущественный над другими реализациями. Кроме того, специалист с обычной квалификацией в данной области легко поймет, термины ″верхний″ и ″нижний″, иногда используется для простоты описания цифры и указывают относительные положения соответствующие ориентации на рисунке, но могут и не отражать правильную ориентацию устройства в его реализации.

[0099] Некоторые функции, представленные в данном описании в контексте отдельных реализаций, также может быть реализованы в комбинации в одном осуществлении. И наоборот, различные признаки, которые представлены в контексте одной реализации, также может быть реализовано в нескольких реализациях отдельно или в любой подходящей комбинации.

[0100] Кроме того, в то время операции представлены на рисунках в определенном порядке, это не следует понимать как требование, чтобы такие операции быть выполнены в определенном порядке, как показано, или в последовательном порядке, или что все проиллюстрированные операции выполняются для достижения желательных результатов. Кроме того, на чертежах может схематически изображен еще один процесс, например, в виде блок-схемы. Тем не менее, другие операции, которые не изображены, могут быть включены в примере процессов, которые схематически показаны. Например, одна или несколько дополнительных операций могут быть выполнены до, после, одновременно, или между любыми из представленных операций. При определенных обстоятельствах многозадачность и параллельная обработка могут быть преимущественными. Более того, разделение различных компонентов системы, в реализации, представленной выше, не следует понимать как требование такого разделения во всех реализациях, и следует понимать, что описанные программные компоненты и системы в общем случае могут быть интегрированы в единый программный продукт или упакованы в несколько программных продуктов. Кроме того, другие варианты осуществления находятся в пределах объема прилагаемой формулы изобретения. В некоторых случаях, действия в формуле изобретения могут быть выполнены в другом порядке, и достигать желаемых результатов.

Изобретение относится к вычислительной технике. Технический результат заключается в повышении безопасности компьютерной системы. Способ содержит: сохранение части данных состояния процессора для каждого из множества вычислительных модулей; хэширование части сохраненных данных состояния процессора для каждого из множества вычислительных модулей; сравнение хэшей процессора для данных состояния процессора; определение большинства вычислительных модулей, имеющих одни и те же данные состояния процессора и одного из меньшинства вычислительных модулей, имеющих другие данные состояния процессора; повторную синхронизацию множества вычислительных модулей, отправку сохраненных данных состояния процессора от первого вычислительного модуля большинства первому вычислительному модулю меньшинства, подтверждение того, что данные состояния второго вычислительного модуля большинства те же самые, что и сохраненные данные состояния из первого вычислительного модуля большинства или сохраненные данные состояния первого вычислительного модуля меньшинства после передачи сохраненных данных состояния процессора от первого вычислительного модуля большинства к вычислительному модулю меньшинства, обозначение ошибки, если данные состояния не одни и те же. 4 н. и 26 з.п. ф-лы, 10 ил.

1. Способ синхронизации состояния множества вычислительных модулей в электронной системе, каждый вычислительный модуль которого имеет процессор, включающий:

сохранение, по крайней мере, части данных состояния процессора для каждого из множества вычислительных модулей;

хэширование, по крайней мере, части сохраненных данных состояния процессора для каждого из множества вычислительных модулей;

сравнение хэшей процессора для данных состояния процессора;

определение большинства вычислительных модулей, имеющих одни и те же данные состояния процессора и, по крайней мере, одного из меньшинства вычислительных модулей, имеющих другие данные состояния процессора;

повторную синхронизацию множества вычислительных модулей, если определено, что большинство вычислительных модулей имеют одинаковые данные состояния процессора, а меньшинство вычислительных модулей имеют другие данные состояния процессора, где повторная синхронизация включает:

отправку сохраненных данных состояния процессора от первого вычислительного модуля большинства первому вычислительному модулю меньшинства,

подтверждение того, что данные состояния второго вычислительного модуля большинства те же самые, что и сохраненные данные состояния из первого вычислительного модуля большинства или сохраненные данные состояния первого вычислительного модуля меньшинства после передачи сохраненных данных состояния процессора от первого вычислительного модуля большинства к вычислительному модулю меньшинства,

обозначение ошибки, если данные состояния не одни и те же, причем данные состояния процессора вычислительного модуля большинства восстанавливаются на основе сохраненных данных состояния процессора вычислительного модуля в связи с завершением повторной синхронизации.

2. Способ по п. 1, далее включающий:

хэширование данных состояния памяти для каждого из множества вычислительных модулей;

сравнение хэшей памяти для данных состояния памяти и

повторную синхронизацию множества вычислительных модулей на основе, по крайней мере, сравнения хэшей памяти.

3. Способ по п. 1, отличающийся тем, что хэширование данных состояния процессора включает вычисление контрольной суммы данных состояния процессора.

4. Способ по п. 2, отличающийся тем, что хэширование данных о состоянии памяти включает вычисление контрольной суммы данных о состоянии памяти.

5. Способ по п. 1, в котором повторная синхронизация включает отправку данных состояния процессора от первого вычислительного модуля ко второму вычислительному модулю.

6. Способ по п. 5, отличающийся тем, что отправка данных состояния процессора включает отправку данных состояния процессора по шине данных, непосредственно соединяющей первый вычислительный модуль со вторым вычислительным модулем.

7. Способ по п. 2, в котором хэширование данных состояния памяти для каждого из множества вычислительных модулей включает хэширование части данных состояния памяти для каждого из множества вычислительных модулей.

8. Способ по п. 2, в котором способ выполняется через равные промежутки времени в процессе работы электронной системы.

9. Способ по п. 8, в котором во время каждого регулярного интервала способ создает значения хэшей только предварительно определенной части данных состояния памяти в каждом вычислительном модуле.

10. Способ по п. 9, в котором данные состояния памяти разделены, по крайней мере, на первую часть памяти и вторую часть памяти, и во время последовательных регулярных интервалов способ хэширует первую часть памяти для каждого вычислительного модуля, а затем хэширует вторую часть памяти для каждого вычислительного модуля.

11. Способ по п. 10, в котором последовательно сравниваются значения хэшей всех данных состояния памяти в течение множества последовательных регулярных интервалов.

12. Способ по п. 9, включающий во время каждого регулярного интервала:

Определение, эквивалентны ли значения хэшей предварительно определенных частей каждого вычислительного модуля, и

создание дополнительных значений хэшей для второй части данных состояния памяти в каждом вычислительном модуле, если значения хэшей предварительно определенных частей не эквивалентны.

13. Способ по п. 1, далее включающий выявление вычислительного модуля, который перестал отвечать на запросы, и его перезагрузку.

14. Способ по п. 1, в котором каждый из вычислительных модулей содержит процессорное ядро многоядерного процессора.

15. Отказоустойчивый вычислительный аппарат, содержащий

множество вычислительных модулей, где каждый вычислительный модуль включает аппаратное оборудование, процессор которого имеет данные состояния процессора;

модуль повторной синхронизации, выполненный, чтобы сохранять, по крайней мере, часть данных состояния процессора для каждого из множества вычислительных модулей;

модуль хэширования, выполненный с возможностью генерирования значений хэшей, по крайней мере, сохраненных данных состояния процессора;

отказоустойчивый блок проверки, выполненный с возможностью приема множества значений хэшей и повторной синхронизации множества вычислительных модулей, если большинство вычислительных модулей по определению имеют одни и те же данные состояния процессора, а меньшинство вычислительных модулей имеют другие данные состояния процессора и где модуль повторной синхронизации выполнен, чтобы:

посылать сохраненные данные с первого вычислительного модуля большинства к первому вычислительному модулю меньшинства,

подтверждать, что данные состояния второго вычислительного модуля большинства такие же, как сохраненные данные состояния с первого вычислительного модуля большинства или сохраненные данные состояния с первого вычислительного модуля меньшинства после передачи сохраненных данных состояния процессора с первого вычислительного модуля большинства к вычислительному модулю меньшинства; и

осуществлять обозначение ошибки, если данные состояния не одинаковы; и

восстанавливать данные состояния процессора вычислительного модуля большинства на основе сохраненных данных состояния процессора вычислительного модуля большинства при завершении повторной синхронизации.

16. Отказоустойчивый вычислительный аппарат по п. 15,

дополнительно содержащий блок проверки когерентности памяти, выполненный для проверки согласованности множества порций памяти, включенных в несколько вычислительных модулей.

17. Отказоустойчивый вычислительный аппарат по п. 15, в котором каждый из процессоров множества вычислительных модулей содержит данные о состоянии памяти, а модуль хэширования дополнительно выполнен с возможностью генерировать объемы хэширования данных о состоянии памяти, а множество объемов хэш, считываемых отказоустойчивым аппаратом, включают проверку хэш объемов для данных о состоянии памяти.

18. Отказоустойчивый вычислительный аппарат по п. 17, в котором модуль хэширования дополнительно выполнен с возможностью выбирать только заданную часть памяти для хэширования для каждого вычислительного модуля.

19. Отказоустойчивый вычислительный аппарат по п. 17, содержащий таймер, настроенный на начало генерирования значений хэшей данных состояния памяти через регулярные интервалы.

20. Отказоустойчивый вычислительный аппарат по п. 19, в котором регулярные интервалы составляют 2, 5, 10, 20 или 30 миллисекунд.

21. Отказоустойчивый вычислительный аппарат по п. 19, в котором модуль хэширования выполнен с возможностью выбирать только часть памяти от каждого вычислительного модуля для хэширования в каждом из регулярных интервалов.

22. Отказоустойчивый вычислительный аппарат по п. 21, в котором память каждого вычислительного модуля имеет, по меньшей мере, первую часть памяти и вторую часть памяти, а модуль хэширования сконфигурирован для последовательного хэширования первой части памяти, а затем второй части памяти от каждого вычислительного модуля при последовательно регулярных промежутках времени.

23. Отказоустойчивый вычислительный аппарат по п. 15, в котором каждый из множества вычислительных модулей функционально соединен, по меньшей мере, с одним другим модулем вычисления в нескольких вычислительных модулях одного или более соединений.

24. Отказоустойчивый вычислительный аппарат по п. 15, в котором отказоустойчивый блок проверки дополнительно выполнен с возможностью идентификации вычислительного модуля, который перестал отвечать на запросы, и его перезагрузки.

25. Отказоустойчивый вычислительный аппарат, содержащий:

множество вычислительных модулей, где каждый вычислительный модуль включает процессор с данными состояния процессора;

средства для сохранения, по крайней мере, части данных состояния процессора для каждого из множества вычислительных модулей;

средства для хэширования, выполненного с возможностью формирования значений хэшей, по крайней мере, сохраненных данных состояния процессора;

средства для сравнения множества значений хэшей;

средства для определения большинства вычислительных модулей, имеющих одни и те же данные состояния процессора и, по крайней мере, одного из меньшинства вычислительных модулей, имеющих другие данные состояния процессора; и

средства для повторной синхронизации множества вычислительных модулей на основе определения, где средства для повторной синхронизации выполнены в соответствии 1:25;

передают сохраненные данные состояния процессора с первого вычислительного модуля большинства к первому вычислительному модулю меньшинства,