Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении отказо- и сбоеустойчивых, радиационно стойких самосинхронных схем.

Известно мажоритарное устройство, содержащее первый элемент И, выход которого соединен с первым входом элемента ИЛИ, первый вход - с выходом мажоритального элемента, второй вход через элемент НЕ - с выходом элемента "равнозначность" и с первым входом второго элемента ИЛИ, второй вход второго элемента И соединен с одним из входов элемента "равнозначность" (авторское свидетельство СССР №711576, кл. G06F 11/00, Н03К 19/42).

Недостатком такого устройства является низкая отказо- и сбоеустойчивость в условиях радиации.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является мажоритарный элемент для трех парафазных сигналов, с парафазным выходом, содержащий два блока транзисторов р-проводимости, два блока транзисторов n-проводимости, три не инверсных информационных входа, три инверсных информационных входа, инверсный выход, не инверсный выход, вход подключения шины «+» питания, вход подключения шины «Ноль вольт», причем не инверсные информационные входы подключены к соответствующим входам первого блока транзисторов p-проводимости и первого блока транзисторов n-проводимости, инверсные информационные входы подключены к соответствующим входам второго блока транзисторов p-проводимости и второго блока транзисторов n-проводимости, токовые входы первого блока транзисторов p-проводимости и первого блока транзисторов n-проводимости объединены и подключены ко входу подключения шины «+» питания, токовые выходы второго блока транзисторов p-проводимости и второго блока транзисторов n-проводимости объединены и подключены ко входу подключения шины «Ноль вольт», токовый выход первого блока транзисторов p-проводимости подключен к токовому входу первого блока транзисторов n-проводимости и является инверсным выходом устройства, токовый выход второго блока транзисторов p-проводимости подключен к токовому входу второго блока транзисторов n-проводимости и является не инверсным выходом устройства.

Каждый блок транзисторов p-проводимости содержит пять транзисторов p-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора p-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов p-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов p-проводимости, стоки первого и четвертого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора группы транзисторов p-проводимости, сток пятого транзистора группы транзисторов p-проводимости подключен к истоку четвертого транзистора группы транзисторов p-проводимости.

Каждый блок транзисторов n-проводимости содержит пять транзисторов n-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора n-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов n-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов n-проводимости, стоки первого и четвертого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора группы транзисторов p-проводимости, сток пятого транзистора группы транзисторов p-проводимости подключен к истоку четвертого транзистора группы транзисторов p-проводимости (Ю.А. Степченков, А.Н. Денисов, Ю.Г. Дьяченко, Ф.И. Гринфельд, О.П. Филимоненко, Н.В. Морозов, Д.Ю. Степченков. Библиотека элементов для проектирования самосинхронных полузаказных микросхем серий 5503/5507 и 5508/5509 - М: ИЛИ РАН, 2014. - 296 с. - С. 150, 151). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения - два блока транзисторов p-проводимости; два блока транзисторов n-проводимости; три не инверсных информационных входа; три инверсных информационных входа; инверсный выход; не инверсный выход; вход подключения шины «+» питания; вход подключения шины «Ноль вольт»; не инверсные информационные входы подключены к соответствующим входам первого блока транзисторов p-проводимости и первого блока транзисторов n-проводимости; инверсные информационные входы подключены к соответствующим входам второго блока транзисторов p-проводимости и второго блока транзисторов n-проводимости; токовые входы первого блока транзисторов p-проводимости и первого блока транзисторов n-проводимости объединены и подключены к входу подключения шины «+» питания; токовый вход первого блока транзисторов n-проводимости является инверсным выходом устройства; токовый вход второго блока транзисторов n-проводимости является не инверсным выходом устройства; каждый блок транзисторов р-проводимости содержит пять транзисторов p-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора p-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов p-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов p-проводимости; стоки первого и четвертого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому выходу блока; истоки второго, третьего и пятого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому входу блока; стоки второго и третьего транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора группы транзисторов p-проводимости; сток пятого транзистора группы транзисторов p-проводимости подключен к истоку четвертого транзистора группы транзисторов p-проводимости; каждый блок транзисторов n-проводимости содержит пять транзисторов n-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора n-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов n-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов n-проводимости; стоки первого и четвертого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу блока; истоки второго, третьего и пятого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу блока; стоки второго и третьего транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора группы транзисторов p-проводимости; сток пятого транзистора группы транзисторов p-проводимости подключен к истоку четвертого транзистора группы транзисторов p-проводимости.

Недостатком известного устройства, принятого за прототип, является низкая отказоустойчивость относительно отказов транзисторов и источника питания.

Это обусловлено следующими обстоятельствами.

Технические средства прототипа позволяют обнаружить сбои и отказы транзисторов путем внешнего по отношению к устройству контроля состояний инверсного и не инверсного информационных выходов (они должны быть противоположны в рабочей фазе и одинаковы в фазе гашения), но теряют работоспособность при необратимых отказах хотя бы одного любого транзистора. Технические средства прототипа также теряют работоспособность при отказе блока питания.

Задачей изобретения является повышение отказоустойчивости относительно отказов транзисторов и блока питания.

Поставленная задача была решена за счет того, что в заявляемое устройство, содержащее два блока транзисторов p-проводимости, два блока транзисторов n-проводимости, три не инверсных информационных входа, три инверсных информационных входа, инверсный выход, не инверсный выход, вход подключения шины «+» питания, вход подключения шины «Ноль вольт», причем не инверсные информационные входы подключены к соответствующим входам первого блока транзисторов p-проводимости и первого блока транзисторов n-проводимости, инверсные информационные входы подключены к соответствующим входам второго блока транзисторов p-проводимости и второго блока транзисторов n-проводимости, токовые входы первого блока транзисторов p-проводимости и первого блока транзисторов n-проводимости объединены и подключены ко входу подключения шины «+» питания, токовый вход первого блока транзисторов n-проводимости является инверсным выходом устройства, токовый вход второго блока транзисторов n-проводимости является не инверсным выходом устройства; каждый блок транзисторов p-проводимости содержит пять транзисторов p-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора p-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов p-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов p-проводимости, стоки первого и четвертого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора группы транзисторов p-проводимости, сток пятого транзистора группы транзисторов p-проводимости подключен к истоку четвертого транзистора группы транзисторов p-проводимости;

каждый блок транзисторов n-проводимости содержит пять транзисторов n-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора n-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов n-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов n-проводимости, стоки первого и четвертого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора группы транзисторов p-проводимости, сток пятого транзистора группы транзисторов p-проводимости подключен к истоку четвертого транзистора группы транзисторов p-проводимости, согласно изобретению дополнительно введены шесть блоков транзисторов p-проводимости - третий, четвертый, пятый, шестой, седьмой и восьмой, шесть блоков транзисторов n-проводимости - третий, четвертый, пятый, шестой, седьмой и восьмой, второй вход подключения шины «+» питания и второй вход подключения шины «Ноль вольт», причем информационные входы третьего, четвертого и пятого блоков транзисторов p-проводимости и информационные входы третьего, четвертого и пятого блоков транзисторов n-проводимости подключены к соответствующим не инверсным информационным входам устройства, информационные входы шестого, седьмого и восьмого блоков транзисторов p-проводимости и информационные входы шестого, седьмого и восьмого блоков транзисторов n-проводимости подключены к соответствующим инверсным информационным входам устройства, токовые входы третьего и шестого блоков транзисторов p-проводимости объединены и подключены ко второму входу подключения шины «+», токовый выход первого блока транзисторов p-проводимости подключен к токовому входу четвертого блока транзисторов p-проводимости, выход которого подключен к токовому выходу пятого блока транзисторов p-проводимости и инверсному выходу устройства, токовый выход третьего блока транзисторов p-проводимости подключен к токовому входу пятого блока транзисторов p-проводимости, токовый выход второго блока транзисторов p-проводимости подключен к токовому входу седьмого блока транзисторов p-проводимости, токовый выход которого подключен к токовому выходу восьмого блока транзисторов p-проводимости и не инверсному выходу устройства, токовый выход шестого блока транзисторов p-проводимости подключен к токовому входу восьмого блока транзисторов p-проводимости, токовые выходы четвертого и седьмого блоков транзисторов n-проводимости объединены и подключены ко входу подключения шины «Ноль вольт», токовые выходы пятого и восьмого блоков транзисторов n-проводимости объединены и подключены ко второму входу подключения шины «Ноль вольт», токовый выход первого блока транзисторов n-проводимости подключен к токовому входу четвертого блока транзисторов n-проводимости, токовый выход второго блока транзисторов n-проводимости подключен к токовому входу седьмого блока транзисторов n-проводимости, токовый вход третьего блока транзисторов n-проводимости подключен к инверсному выходу устройства, токовый выход третьего блока транзисторов n-проводимости подключен к токовому входу пятого блока транзисторов n-проводимости, токовый выход второго блока транзисторов n-проводимости подключен к токовому входу седьмого блока транзисторов n-проводимости, токовый вход шестого блока транзисторов n-проводимости подключен к не инверсному выходу устройства, токовый выход шестого блока транзисторов n-проводимости подключен к токовому входу восьмого блока транзисторов n-проводимости.

Признаки заявляемого технического решения, отличительные от прототипа - введены шесть блоков транзисторов p-проводимости - третий, четвертый, пятый, шестой, седьмой и восьмой; шесть блоков транзисторов n-проводимости - третий, четвертый, пятый, шестой, седьмой и восьмой; второй вход подключения шины «+» питания; второй вход подключения шины «Ноль вольт»;

информационные входы третьего, четвертого и пятого блоков транзисторов p-проводимости и информационные входы третьего, четвертого и пятого блоков транзисторов n-проводимости подключены к соответствующим не инверсным информационным входам устройства; информационные входы шестого, седьмого и восьмого блоков транзисторов p-проводимости и информационные входы шестого, седьмого и восьмого блоков транзисторов n-проводимости подключены к соответствующим инверсным информационным входам устройства; токовые входы третьего и шестого блоков транзисторов p-проводимости объединены и подключены ко второму входу подключения шины «+»; токовый выход первого блока транзисторов p-проводимости подключен к токовому входу четвертого блока транзисторов p-проводимости, выход которого подключен к токовому выходу пятого блока транзисторов p-проводимости и инверсному выходу устройства; токовый выход третьего блока транзисторов p-проводимости подключен к токовому входу пятого блока транзисторов p-проводимости; токовый выход второго блока транзисторов p-проводимости подключен к токовому входу седьмого блока транзисторов p-проводимости; токовый выход которого подключен к токовому выходу восьмого блока транзисторов p-проводимости и не инверсному выходу устройства; токовый выход шестого блока транзисторов p-проводимости подключен к токовому входу восьмого блока транзисторов p-проводимости; токовые выходы четвертого и седьмого блоков транзисторов n-проводимости объединены и подключены ко входу подключения шины «Ноль вольт»; токовые выходы пятого и восьмого блоков транзисторов n-проводимости объединены и подключены ко второму входу подключения шины «Ноль вольт»; токовый выход первого блока транзисторов n-проводимости подключен к токовому входу четвертого блока транзисторов n-проводимости; токовый выход второго блока транзисторов n-проводимости подключен к токовому входу седьмого блока транзисторов n-проводимости; токовый вход третьего блока транзисторов n-проводимости подключен к инверсному выходу устройства; токовый выход третьего блока транзисторов n-проводимости подключен к токовому входу пятого блока транзисторов n-проводимости; токовый выход второго блока транзисторов n-проводимости подключен к токовому входу седьмого блока транзисторов n-проводимости; токовый вход шестого блока транзисторов n-проводимости подключен к не инверсному выходу устройства; токовый выход шестого блока транзисторов n-проводимости подключен к токовому входу восьмого блока транзисторов n-проводимости.

Отличительные признаки в сочетании с известными позволяют повысить отказоустойчивость устройства относительно необратимых отказов транзисторов, путем реализации логических функций, толерантных к константным или инверсным отказам одного любого блока транзисторов p-проводимости или n-проводимости в каждой группе из четырех блоков.

Кроме того, обеспечивается работоспособность при отключении одного из двух входов подключения шины «+» питания, одного из двух входов подключения шины «Ноль вольт».

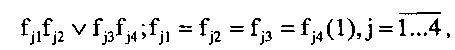

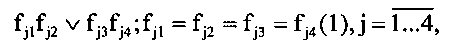

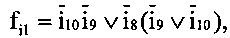

Введение новых связей для блоков транзисторов p-проводимости позволяет обеспечить реализацию логических функций

где fil=i10i9∨i8(i9∨i10) - мажоритарная функция i-го блока транзисторов p-проводимости. Такая функция сохраняет свое значение при изменении любого только одного из четырех членов fj1, fj2, fj3, fj4.

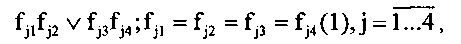

Введение новых связей для блоков транзисторов n-проводимости позволяет обеспечить реализацию логических функций

где fil=i10i9∨i8(i9∨i10) - мажоритарная функция i-го блока транзисторов n-проводимости. Такая функция сохраняет свое значение при изменении любого одного из четырех членов fj1, fj2, fj3, fj4.

Таким образом, введение новых элементов и связей позволяет обеспечить отказоустойчивость - устройство работоспособно при отказе одного из четырех блоков транзисторов p-проводимости и/или одного из четырех блоков транзисторов n-проводимости в каждой из двух «четверок» блоков транзисторов p-проводимости, блоков транзисторов n-проводимости.

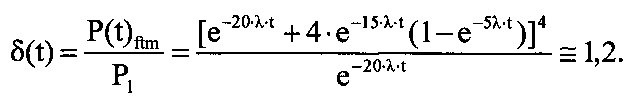

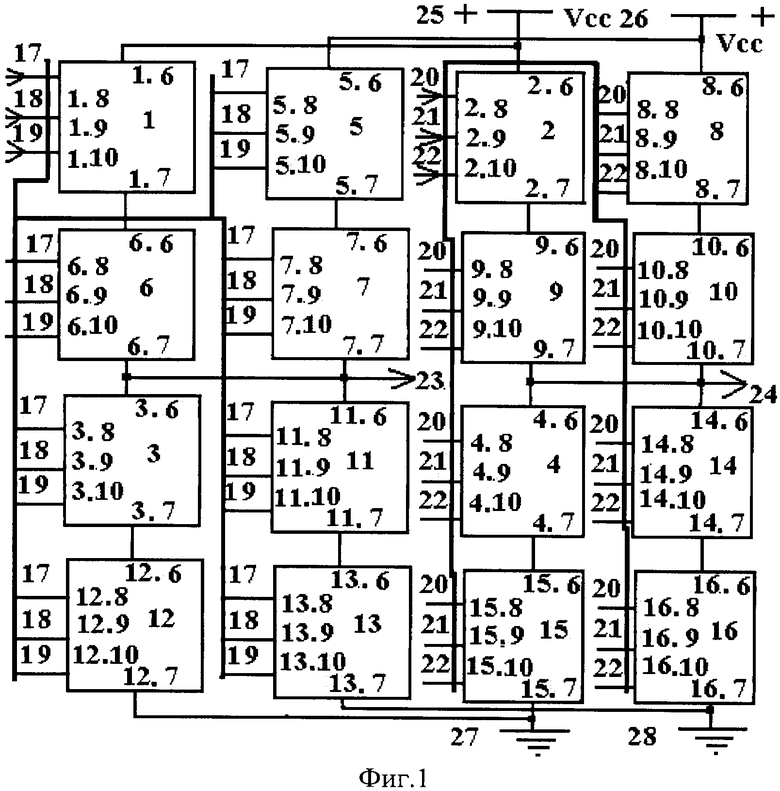

На фиг. 1 изображена схема электрическая структурная предлагаемого отказоустойчивого мажоритарного устройства для самосинхронных схем.

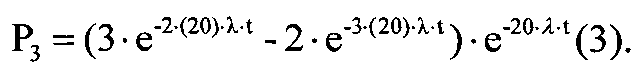

На фиг. 2 изображена схема электрическая функциональная i-го блока транзисторов p-проводимости.

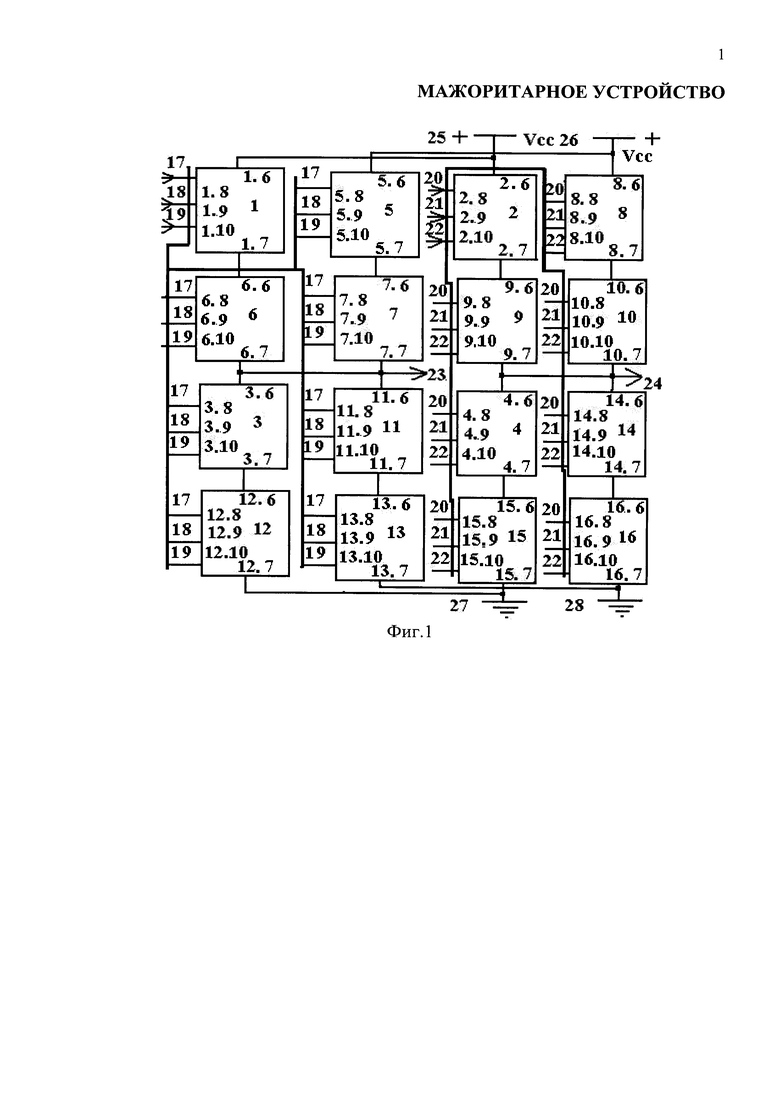

На фиг. 3 изображена схема электрическая функциональная i-го блока транзисторов n-проводимости.

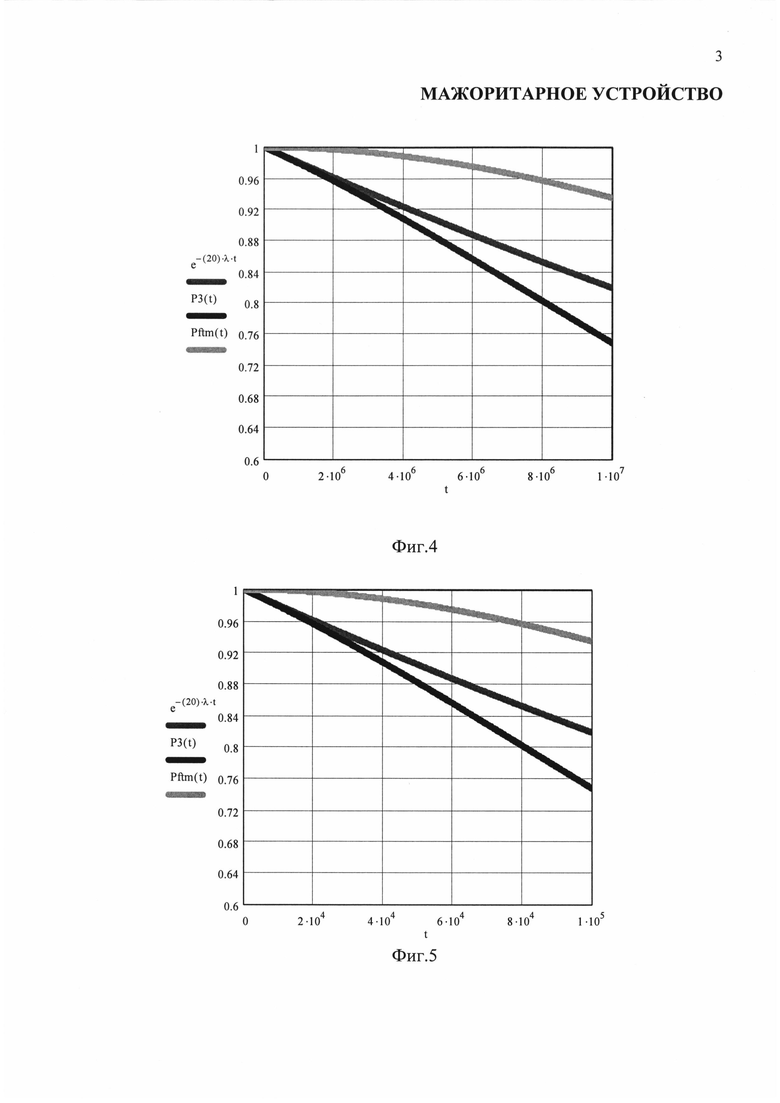

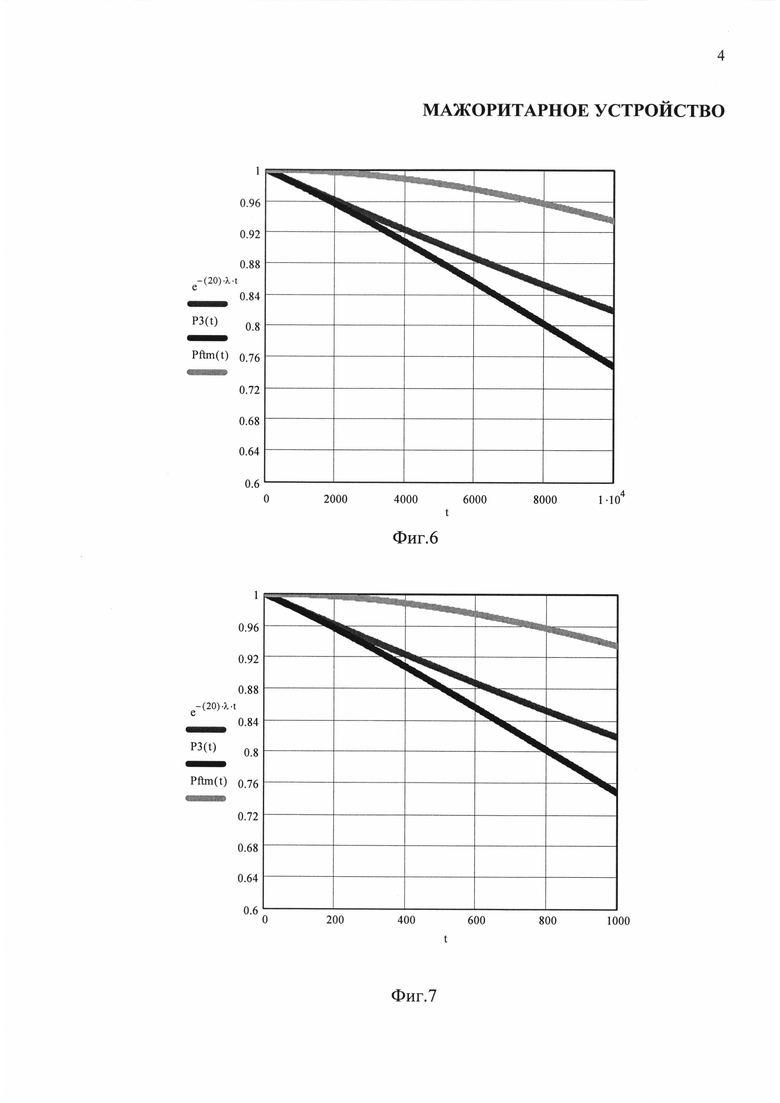

На фиг. 4 изображены графики изменения вероятности безотказной работы прототипа е-(20)λ·t, вероятности безотказной работы предлагаемого устройства Р(t)ftm и троированного прототипа Р3 при интенсивности отказов (сбоев) λ=10-9 1/час.

На фиг. 5 изображены графики изменения вероятности безотказной работы прототипа е-(20)λ·t, вероятности безотказной работы предлагаемого устройства P(t)ftm и троированного прототипа Р3 при интенсивности отказов (сбоев) λ=10-7 1/час.

На фиг. 6 изображены графики изменения вероятности безотказной работы прототипа е-(20)λ·t, вероятности безотказной работы предлагаемого устройства P(t)ftm и троированного прототипа Р3 при интенсивности отказов (сбоев) λ=10-6 1/час.

На фиг. 7 изображены графики изменения вероятности безотказной работы прототипа е-(20)λ·t, вероятности безотказной работы предлагаемого устройства P(t)ftm и троированного прототипа Р3 при интенсивности отказов (сбоев) λ=10-5 1/час.

Мажоритарное устройство (фиг. 1) содержит первый 1 и второй 2 блоки транзисторов p-проводимости, первый 3 и второй 4 блоки транзисторов n-проводимости, шесть дополнительных (третий 5, четвертый 6, пятый 7, шестой 8, седьмой 9, восьмой 10) блоков транзисторов p-проводимости, шесть дополнительных (третий 11, четвертый 12, пятый 13, шестой 14, седьмой 15, восьмой 16) блоков транзисторов n-проводимости, три не инверсных информационных входа 17, 18, 19, три инверсных информационных входа 20, 21, 22, инверсный выход 23, не инверсный выход 24, первый вход подключения шины «+» питания 25, второй вход подключения шины «+» питания 26, первый вход подключения шины «Ноль вольт» 27, второй вход подключения шины «Ноль вольт» 28.

Не инверсные информационные входы 17, 18, 19 подключены к соответствующим входам 1.8, 1.9, 1.10 первого блока транзисторов p-проводимости 1 и соответствующим входам 3.8, 3.9, 3.10 первого блока транзисторов n-проводимости 3.

Инверсные информационные входы 20, 21, 22 подключены к соответствующим входам 2.8, 2.9, 2.10 второго блока транзисторов p-проводимости 2 и соответствующим входам 4.8, 4.9, 4.10 второго блока транзисторов n-проводимости 4.

Токовый вход 1.6 первого блока транзисторов p-проводимости 1 и токовый вход 3.6 первого блока транзисторов n-проводимости 2 объединены и подключены к первому входу подключения шины «+» питания 25.

Токовый вход 3.6 первого блока транзисторов n-проводимости 3 является инверсным выходом устройства 23.

Токовый вход 4.6 второго блока транзисторов n-проводимости 4 является не инверсным выходом устройства 24.

Информационные входы 5.8, 5.9, 5.10 третьего 5, 6.8, 6.9, 6.10 четвертого 6 и 7.8, 7.9, 7.10 пятого 7 блоков транзисторов p-проводимости и информационные входы 11.8, 11.9, 11.10 третьего 11, 12.8, 12.9, 12.10 четвертого 12 и 13.8, 13.9, 13.10 пятого 13 блоков транзисторов n -проводимости подключены к соответствующим не инверсным информационным входам устройства 17, 18, 19.

Информационные входы 8.8, 8.9, 8.10 шестого 8, 9.8, 9.9, 9.10 седьмого 9 и 10.8, 10.9, 10.10 восьмого 10 блоков транзисторов p-проводимости и информационные входы 14.8, 14.9, 14.10 шестого 14, 15.8, 15.9, 15.10 седьмого 15 и 16.8, 16.9, 16.10 восьмого 16 блоков транзисторов n-проводимости подключены к соответствующим инверсным информационным входам устройства 20, 21, 22.

Токовые входы 5.6 третьего 5 и 8.6 шестого 8 блоков транзисторов p-проводимости объединены и подключены ко второму входу подключения шины «+» 26.

Токовый выход 1.7 первого блока транзисторов p-проводимости 1 подключен к токовому входу 6.6 четвертого блока транзисторов p-проводимости 6, выход которого подключен к токовому выходу 7.7 пятого блока транзисторов p-проводимости 7 и инверсному выходу устройства 23.

Токовый выход 5.7 третьего блока транзисторов p-проводимости 5 подключен к токовому входу 7.6 пятого блока транзисторов p-проводимости 7.

Токовый выход 2.7 второго блока транзисторов p-проводимости 2 подключен к токовому входу 9.6 седьмого блока транзисторов p-проводимости 9, токовый выход 9.7 которого подключен к токовому выходу 10.7 восьмого блока транзисторов p-проводимости 10 и не инверсному выходу устройства 24.

Токовый выход 8.7 шестого блока транзисторов p-проводимости 8 подключен к токовому входу 10.6 восьмого блока транзисторов p-проводимости 10.

Токовые выходы 12.7 четвертого 12 и 15.7 седьмого 15 блоков транзисторов n-проводимости объединены и подключены к первому входу подключения шины «Ноль вольт» 27.

Токовые выходы 13.7 пятого 13 и 16.7 восьмого 16 блоков транзисторов n-проводимости объединены и подключены ко второму входу подключения шины «Ноль вольт» 28.

Токовый выход 3.7 первого блока транзисторов n-проводимости 3 подключен к токовому входу 12.6 четвертого 12 блока транзисторов n -проводимости.

Токовый выход 4.7 второго блока транзисторов n-проводимости 4 подключен к токовому входу 15.6 седьмого 15 блока транзисторов n-проводимости.

Токовый вход 11.6 третьего блока транзисторов n-проводимости 11 подключен к инверсному выходу устройства 23, а токовый выход 11.7 третьего блока транзисторов n-проводимости 11 подключен к токовому входу 13.6 пятого блока транзисторов n-проводимости 13.

Токовый вход 14.6 шестого блока транзисторов n-проводимости 14 подключен к не инверсному выходу устройства 24, а токовый выход 14.7 шестого блока транзисторов n-проводимости 14 подключен к токовому входу 16.6 восьмого блока транзисторов n-проводимости 16.

Каждый i-й (i=1…8) блок транзисторов p-проводимости (фиг. 2) содержит пять транзисторов p-проводимости i.1, i.2, i.3, i.4, i.5, три информационных входа i.8, i.9, i.10, токовый вход i.6, токовый выход i.7.

Первый информационный вход i.8 блока i подключен к затворам первого транзистора p-проводимости i.1, второй информационный вход i.9 блока i подключен к затворам второго i.2 и четвертого i.4 транзисторов p-проводимости.

Третий информационный вход i.10 блока подключен к затворам третьего i.3 и пятого i.5 транзисторов p-проводимости.

Стоки первого i.1 и четвертого i.4 транзисторов группы транзисторов p-проводимости объединены и подключены к токовому выходу i.7 блока.

Истоки второго i.2, третьего i.3 и пятого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому входу i.6 блока.

Стоки второго i.2 и третьего i.3 транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора i.1 группы транзисторов p-проводимости.

Сток пятого транзистора i.5 группы транзисторов p-проводимости подключен к истоку четвертого i.4 транзистора группы транзисторов p-проводимости.

Каждый i-й (i=1…8) блок транзисторов n-проводимости (фиг. 3) содержит пять транзисторов n-проводимости i.1, i.2, i.3, i.4, i.5, три информационных входа i.8, i.9, i.10, токовый вход i.6, токовый выход i.7.

Первый информационный вход i.8 блока i подключен к затворам первого транзистора n-проводимости i.1, второй информационный вход i.9 блока i подключен к затворам второго i.2 и четвертого i.4 транзисторов n-проводимости.

Третий информационный вход i.10 блока подключен к затворам третьего i.3 и пятого i.5 транзисторов n-проводимости.

Стоки первого i.1 и четвертого i.4 транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу i.7 блока.

Истоки второго i.2, третьего i.3 и пятого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу i.6 блока.

Стоки второго i.2 и третьего i.3 транзисторов группы транзисторов n-проводимости объединены и подключены к истоку первого транзистора i.1 группы транзисторов п - проводимости.

Сток пятого транзистора i.5 группы транзисторов n-проводимости подключен к истоку четвертого i.4 транзистора группы транзисторов n-проводимости.

Устройство работает следующим образом.

1. Работа устройства при отсутствии отказов.

В этом случае работоспособны все блоки 1-16 транзисторов p-проводимости и транзисторов n-проводимости (фиг. 1) и устройство работает аналогично прототипу.

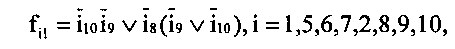

В рабочей фазе при поступлении на три инверсных входа 17, 18, 19 информации инверсной информации, поступающей на не инверсные входы 20, 21, 22, блоки транзисторов p-проводимости 1, 5, 6, 7, 2, 8, 9, 10 (фиг. 1, 2) вычисляют инверсную мажоритарную функцию вида:

блоки транзисторов n-проводимости 3, 11, 13, 12, 4, 14, 15, 16 (фиг. 1, 3) вычисляют не инверсную мажоритарную функцию вида:

fil=i10i9∨i1(i9∨i10), i=3, 11, 13, 15, 4, 14, 15, 16.

То есть, например, при наличии логических нулей на входах 10 и 9, или 8 и 9 или 8 и 10 i-го блока (наборы 000, 001, 010, 100 на входах 17, 18, 19) активируются соответствующие затворы транзисторов p-проводимости и образуется цепочка (цепочки) открытых транзисторов, что обеспечивает протекание тока с токового входа i.6 на токовый выход i.7 i-го блока транзисторов p-проводимости. В то же время такая ситуация не позволяет активировать ни один путь с токового входа i.6 на токовый выход i.7 i-го блока транзисторов n-проводимости 3, 11, 12, 13 (фиг. 1, 3).

Все это обеспечивает появление на инверсном выходе 23 логической единицы за счет протекания тока с первого 25 или второго 26 входа подключения шины «+» питания (фиг. 1).

Тогда, поскольку в описанном выше примере на инверсных входах 20, 21, 22 имеется большинство единиц (наборы 111, 110, 101, 011 на входах 20, 21, 22) блоки транзисторов p-проводимости 2, 8, 9, 10 (фиг. 1, 2) не образуют ни одной цепочки с токового входа i.6 на токовый выход i.7 i-го блока, но зато такие цепочки образуют блоки транзисторов n-проводимости 4, 14, 15, 16 (фиг. 1, 3):

fi1=i10i9∨i8(i9∨i10), i=4, 14, 15, 16.

Все это обеспечивает появление на не инверсном выходе 24 логического нуля к первому 27 или второму 28 входу подключения шины «Ноль вольт».

В случае поступления на входы 17, 18, 19 наборов 111, 110, 101, 011, а на входы 20, 21, 22 наборов 000, 001, 010, 100 образуются цепочки с токовых входов i.6 на токовые выходы i.7 i-x блоков транзисторов n-проводимости 3, 11, 12, 13 (Фиг. 1, 3) и i-x блоков транзисторов p-проводимости 2, 8, 9, 10 (Фиг. 1, 2).

Это обеспечивает появление на не инверсном выходе 24 логической единицы - за счет протекания тока с первого 25 или второго 26 входа подключения шины «+» питания через блоки 2, 8, 9, 10, причем на инверсном выходе 23 формируется логический ноль за счет протекания тока к первому 27 или второму 28 входу подключения шины «Ноль вольт» через блоки 3, 11, 12, 13.

В фазе гашения на входы 17, 18, 19; 20, 21, 22 поступает одинаковая информация, например все нули, поэтому на выходах 23 и 24 устанавливаются одинаковые логические уровни, например единицы (если на входах 17, 18, 19; 20, 21, 22 все нули).

2. Работа устройства при наличии отказов.

В этом случае и в рабочей фазе, и в фазе гашения допускаются отказы одного из четырех блоков среди блоков 1, 5, 6, 7; одного из четырех блоков среди блоков 2, 6, 9, 10; одного из четырех блоков среди блоков 3, 11, 12, 13; одного из четырех блоков среди блоков 4, 14, 15, 16.

Соединения каждой такой j-й «четверки» (j=1 для 1, 5, 6, 7; j=2 для 12, 6, 9, 10; j=3 для 3, 11, 12, 13; j=4 для 4, 14, 15, 16) реализуют логические функции вида

где  i=1, 5, 6, 7, 2, 8, 9, 10 - мажоритарная функция i-го блока транзисторов p-проводимости или n-проводимости fi1=i10i9∨i8(i9∨i10), i=3, 11, 13, 15, 4, 14, 15, 16.

i=1, 5, 6, 7, 2, 8, 9, 10 - мажоритарная функция i-го блока транзисторов p-проводимости или n-проводимости fi1=i10i9∨i8(i9∨i10), i=3, 11, 13, 15, 4, 14, 15, 16.

Такая функция  сохраняет свое значение при изменении любого одного из четырех членов - одной любой функции fj1, fj2, fj3, fj4.

сохраняет свое значение при изменении любого одного из четырех членов - одной любой функции fj1, fj2, fj3, fj4.

То есть одна любая функция может вследствие отказов (или воздействия заряженных частиц) стать произвольной функцией либо константой. Например, первая функция fj1 становится некоторой другой функцией g:

gj1fj2∨fj3fj4.

Но поскольку fj2=fj3=fj4=f, то в соответствие с законами булевой алгебры логики требуемая функция «четверки» сохраняется:

gj1f∨ff=f(gj1∨f)=f.

Если вследствие отказа, например, функция fj2 становится константой нуля:

fj1·0∨fj3fj4=fj3fj4=ff=f.

Если вследствие отказа, например, функция fj1 становится константой единицы:

fj1fj2∨1·fj4=fj1fj2∨fj4=ff∨f=f.

То есть при отказах одного блока в каждой «четверке» за счет оставшихся трех блоков, в которых нет отказа, в соответствие с законами булевой алгебры логики требуемая функция «четверки» f сохраняется, что обеспечивает получение правильных логических уровней на выходах 23, 24.

При обрыве (пропадании) напряжения питания на одном из двух входов 25 или 26 подключения шины «+» за счет подачи питания на два оставшихся блока 1,6 или 5,7; 2.9 или 8, 10 транзисторов p-проводимости обеспечивается получение правильных логических уровней на выходах 23, 24 как в рабочей фазе, так и в фазе гашения при условии отсутствия отказов в этих блоках.

При обрыве одного из двух входов 27, 28 подключения шины «Ноль вольт» аналогично обеспечивается работа за счет блоков транзисторов n-проводимости 3, 12; 4, 14; или 11, 13; 14, 16 и получение правильных логических уровней на выходах 23, 24 как в рабочей фазе, так и в фазе гашения при условии отсутствия отказов в этих блоках.

Оценка технико-экономической эффективности относительно отказов (сбоев) транзисторов.

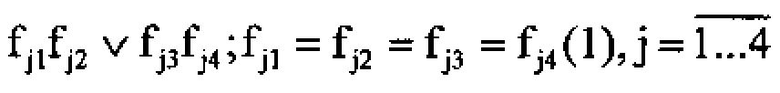

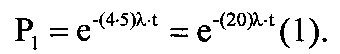

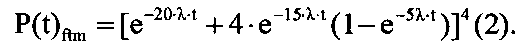

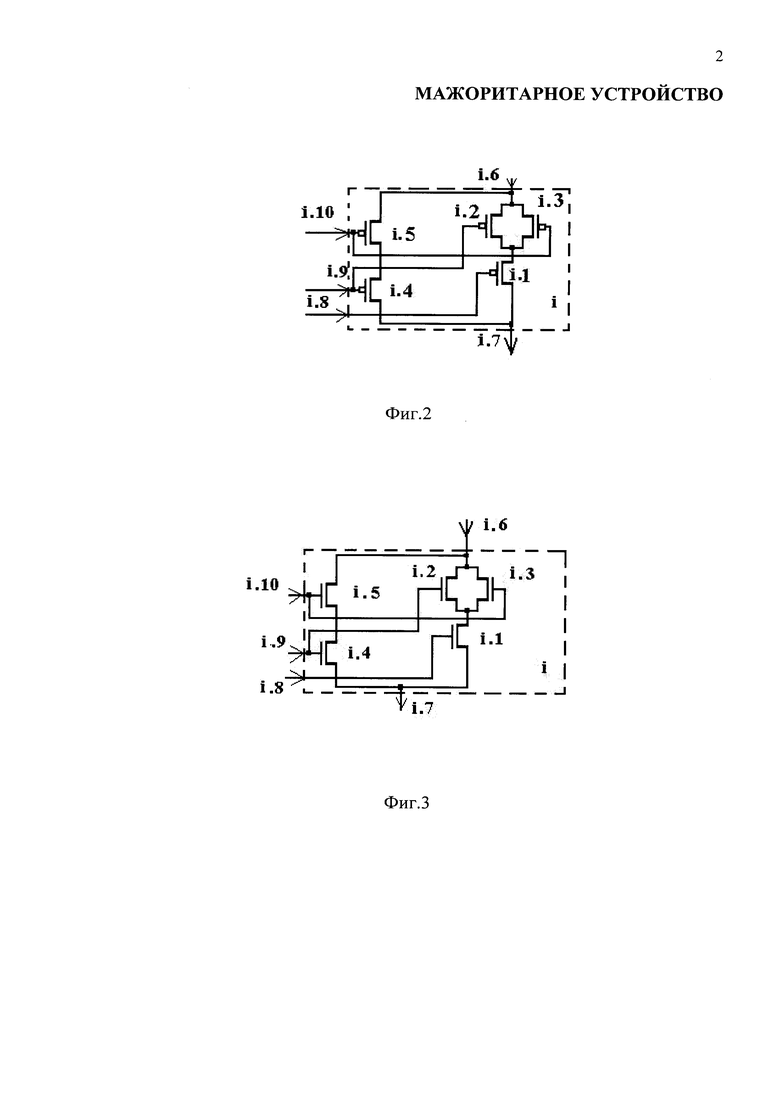

Оценим вероятность безотказной (бессбойной) работы прототипа, имеющего в своем составе 4 блока по 5 транзисторов для экспоненциальной модели отказов:

Для предлагаемого устройства с учетом того, что обеспечивается, как показано выше, работоспособность при отказе одного из четырех блоков среди блоков 1, 5, 6, 7; одного из четырех блоков среди блоков 2, 6, 9, 10; одного из четырех блоков среди блоков 3, 11, 12, 13; одного из четырех блоков среди блоков 4, 14, 15, 16:

Так, при интенсивности отказов (сбоев) λ=10-5 1/час на допустимом временном интервале при t=2000 часов выигрыш δ(t) составляет:

Сравним выражения (1) и (2) с выражением, описывающим троирование прототипа с одним мажоритаром (всего 20·3+20=80 транзисторов, столько же, сколько в предлагаемом устройстве):

Графики сравнения вероятностей (1), (2), (3) для различных интенсивностей отказов (сбоев) представлены на Фиг. 4-7.

Так, при интенсивности отказов (сбоев) λ=10-4 1/час при t=200 часов выигрыш в вероятности безотказной работы составляет почти 0,039, причем троирование прототипа с одним мажоритаром даже хуже нетроированной схемы.

Так, при интенсивности отказов (сбоев) λ=10-4 1/час при t=600 часов выигрыш составляет почти 70% от максимально возможного выигрыша до значения единицы.

Достижение технического результата изобретения подтверждается приведенными оценками.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 2016 |

|

RU2618192C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2011 |

|

RU2449469C1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2016 |

|

RU2628152C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ЛЕВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2021 |

|

RU2776031C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ПРАВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2020 |

|

RU2725149C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ТРОИЧНЫЙ D-ТРИГГЕР | 2022 |

|

RU2784374C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении отказоустройчивых и сбоеустойчивых, радиационно стойких самосинхронных схем. Технический результат изобретения заключается в повышении отказоустойчивости при отказах транзисторов и блока питания. Технический результат достигается за счет введения шести блоков транзисторов p-проводимости - третьего, четвертого, пятого, шестого, седьмого и восьмого, шести блоков транзисторов n-проводимости - третьего, четвертого, пятого, шестого, седьмого и восьмого, второго входа подключения шины «+» питания и второго входа подключения шины «Ноль вольт». 7 ил.

Мажоритарное устройство, содержащее два блока транзисторов p-проводимости, два блока транзисторов n-проводимости, три не инверсных информационных входа, три инверсных информационных входа, инверсный выход, не инверсный выход, вход подключения шины «+» питания, вход подключения шины «Ноль вольт», причем не инверсные информационные входы подключены к соответствующим входам первого блока транзисторов p-проводимости и первого блока транзисторов n-проводимости, инверсные информационные входы подключены к соответствующим входам второго блока транзисторов p-проводимости и второго блока транзисторов n-проводимости, токовые входы первого блока транзисторов p-проводимости и первого блока транзисторов n-проводимости объединены и подключены ко входу подключения шины «+» питания, токовый вход первого блока транзисторов n-проводимости является инверсным выходом устройства, токовый вход второго блока транзисторов n-проводимости является не инверсным выходом устройства, каждый блок транзисторов p-проводимости содержит пять транзисторов p-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора p-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов p-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов p-проводимости, стоки первого и четвертого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов p-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора группы транзисторов p-проводимости, сток пятого транзистора группы транзисторов p-проводимости подключен к истоку четвертого транзистора группы транзисторов p-проводимости, каждый блок транзисторов n-проводимости содержит пять транзисторов n-проводимости, три информационных входа, токовый вход, токовый выход, причем первый информационный вход блока подключен к затворам первого транзистора n-проводимости, второй информационный вход блока подключен к затворам второго и четвертого транзисторов n-проводимости, третий информационный вход блока подключен к затворам третьего и пятого транзисторов n-проводимости, стоки первого и четвертого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому выходу блока, истоки второго, третьего и пятого транзисторов группы транзисторов n-проводимости объединены и подключены к токовому входу блока, стоки второго и третьего транзисторов группы транзисторов p-проводимости объединены и подключены к истоку первого транзистора группы транзисторов p-проводимости, сток пятого транзистора группы транзисторов p-проводимости подключен к истоку четвертого транзистора группы транзисторов p-проводимости,

отличающееся тем, что в него дополнительно введены шесть блоков транзисторов p-проводимости - третий, четвертый, пятый, шестой, седьмой и восьмой, шесть блоков транзисторов n-проводимости - третий, четвертый, пятый, шестой, седьмой и восьмой, второй вход подключения шины «+» питания и второй вход подключения шины «Ноль вольт», причем информационные входы третьего, четвертого и пятого блоков транзисторов p-проводимости и информационные входы третьего, четвертого и пятого блоков транзисторов n-проводимости подключены к соответствующим не инверсным информационным входам устройства, информационные входы шестого, седьмого и восьмого блоков транзисторов p-проводимости и информационные входы шестого, седьмого и восьмого блоков транзисторов n-проводимости подключены к соответствующим инверсным информационным входам устройства, токовые входы третьего и шестого блоков транзисторов p-проводимости объединены и подключены ко второму входу подключения шины «+», токовый выход первого блока транзисторов p-проводимости подключен к токовому входу четвертого блока транзисторов p-проводимости, выход которого подключен к токовому выходу пятого блока транзисторов p-проводимости и инверсному выходу устройства, токовый выход третьего блока транзисторов p-проводимости подключен к токовому входу пятого блока транзисторов p-проводимости, токовый выход второго блока транзисторов p-проводимости подключен к токовому входу седьмого блока транзисторов p-проводимости, токовый выход которого подключен к токовому выходу восьмого блока транзисторов p-проводимости и не инверсному выходу устройства, токовый выход шестого блока транзисторов p-проводимости подключен к токовому входу восьмого блока транзисторов p-проводимости, токовые выходы четвертого и седьмого блоков транзисторов n-проводимости объединены и подключены ко входу подключения шины «Ноль вольт», токовые выходы пятого и восьмого блоков транзисторов n-проводимости объединены и подключены ко второму входу подключения шины «Ноль вольт», токовый выход первого блока транзисторов n-проводимости подключен к токовому входу четвертого блока транзисторов n-проводимости, токовый выход второго блока транзисторов n-проводимости подключен к токовому входу седьмого блока транзисторов n-проводимости, токовый вход третьего блока транзисторов n-проводимости подключен к инверсному выходу устройства, токовый выход третьего блока транзисторов n-проводимости подключен к токовому входу пятого блока транзисторов n-проводимости, токовый выход второго блока транзисторов n-проводимости подключен к токовому входу седьмого блока транзисторов n-проводимости, токовый вход шестого блока транзисторов n-проводимости подключен к не инверсному выходу устройства, токовый выход шестого блока транзисторов n-проводимости подключен к токовому входу восьмого блока транзисторов n-проводимости.

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 2000 |

|

RU2173876C1 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 1996 |

|

RU2110836C1 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 2008 |

|

RU2395161C2 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 1998 |

|

RU2141130C1 |

| US 8975916 B1, 10.03.2015. | |||

Авторы

Даты

2016-04-10—Публикация

2015-05-12—Подача