Изобретение относится к вычислительной технике и может использоваться для реализации цифровых схем, имеющих повышенные требования по надежности, в частности в авиационной и космической областях промышленности.

Известен логический элемент на КМДП транзисторах, содержащий первый, второй и третий информационные транзисторы n-типа, включенные последовательно, четвертый, пятый и шестой информационные транзисторы n-типа, включенные последовательно, четыре входные шины, шины прямого и инверсного сигнала управления. Первый, второй и третий информационные транзисторы включены между выходной и общей шинами четвертый, пятый и шестой информационные транзисторы включены между выходной и общей шинами, первый, второй и третий нагрузочные транзисторы p-типа включены последовательно между шиной источника питания и выходной шиной, четвертый, пятый и шестой нагрузочные транзисторы p-типа включены последовательно между шиной источника питания и выходной шиной, сток первого блокирующего транзистора p-типа соединен с шиной источника питания, а исток подключен к стоку третьего нагрузочного транзистора p-типа, сток первого коммутирующего транзистора p-типа подключен к стоку второго нагрузочного транзистора p-типа, а исток соединен со стоком шестого нагрузочного транзистора p-типа, сток второго коммутирующего транзистора p-типа подключен к стоку пятого нагрузочного транзистора p-типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора n-типа соединен с общей шиной, а исток подключен к стоку первого информационного транзистора n-типа, сток третьего коммутирующего транзистора n-типа подключен к стоку второго информационного транзистора n-типа, а исток - к стоку четвертого информационного транзистора n-типа, сток четвертого коммутирующего транзистора n-типа подключен к стоку пятого нагрузочного транзистора p-типа, а исток соединен с выходной шиной, сток второго блокирующего транзистора n-типа соединен с общей шиной, а исток подключен к стоку первого информационного транзистора n-типа, сток третьего коммутирующего транзистора n-типа подключен к стоку второго информационного транзистора n-типа, а исток - к стоку четвертого информационного транзистора n-типа, сток четвертого коммутирующего транзистора n-типа подключен к стоку пятого информационного транзистора n-типа, а исток соединен с выходной шиной, затворы первого нагрузочного транзистора p-типа и третьего информационного транзистора n-типа соединены с первой входной шиной, затворы второго нагрузочного транзистора p-типа и второго информационного транзистора n-типа соединены с второй входной шиной, затворы пятого нагрузочного транзистора p-типа и пятого информационного транзистора n-типа соединены с третьей входной шиной, затворы шестого нагрузочного транзистора p-типа и четвертого информационного транзистора n-типа соединены с четвертой входной шиной, затворы первого и шестого информационных транзисторов n-типа и третьего и четвертого нагрузочных транзисторов p-типа соединены с шиной прямого сигнала управления, затворы коммутирующих и блокирующих транзисторов соединены с шиной инверсного сигнала управления (авт. св. СССР №1064470, кл. H03K 19/094, опубл. 30.12.83).

Недостатком известного элемента является большое количество транзисторов и вследствие этого низкая структурная надежность. Кроме того, в случае отказов, элемент не сохраняет функциональной полноты с точки зрения теоремы Поста (см. Марченков С.С. Замкнутые классы булевых функций. - М.: Физматлит, 2000, с.18).

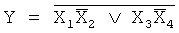

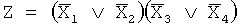

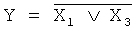

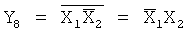

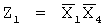

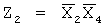

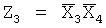

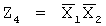

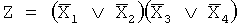

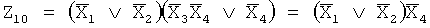

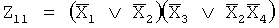

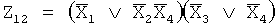

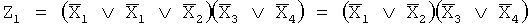

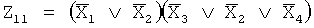

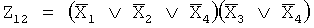

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является логический элемент на КМДП-транзисторах, содержащий четыре транзистора с проводимостью n-типа, четыре транзистора с проводимостью p-типа, четыре входные шины, одну выходную и шину питания и нулевую шину, сток первого транзистора подключен к первой входной шине, на затворы первого и второго транзисторов подключена вторая входная шина, сток третьего транзистора подключен к третьей входной шине, на затворы третьего и четвертого транзисторов подключена четвертая входная шина, сток пятого транзистора подключен к шине питания, исток первого транзистора, сток второго транзистора и затворы шестого и седьмого транзисторов соединены между собой, истоки второго, седьмого, восьмого и четвертого транзисторов подключены к нулевой шине, исток пятого транзистора соединен со стоком шестого транзистора, исток третьего транзистора, сток четвертого транзистора и затворы пятого и восьмого транзисторов соединены между собой, исток шестого транзистора подключен к стокам седьмого и восьмого транзисторов и выходной шине. Данная схема построена на основе двухвходового элемента ИЛИ-НЕ, за счет применения дополнительных вентильных и блокирующих КМДП транзисторов и реализует логическую функцию  (см. Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. - 4-е изд., перераб. и доп. М.: Техносфера, 2009. - 712 с, ил. 2.25). Данное устройство принято за прототип.

(см. Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. - 4-е изд., перераб. и доп. М.: Техносфера, 2009. - 712 с, ил. 2.25). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения - четыре транзистора с проводимостью n-типа; четыре транзистора с проводимостью p-типа; четыре входные шины; одна выходная шина; шина питания и нулевая шина.

Недостатком известного устройства, принятого за прототип, является низкая вероятность сохранения базиса при отказах транзисторов. Данный факт создает трудности при использовании элемента для реализации комбинационных устройств в неремонтируемой аппаратуре.

Задачей изобретения является повышение надежности элемента при отказах внешних входов и транзисторов за счет сохранения функциональной полноты реализуемой функции.

Поставленная задача была решена за счет того, что в известном устройстве, содержащем первый, второй, третий, четвертый транзисторы с проводимостью n-типа, пятый, шестой, седьмой, восьмой транзисторы с проводимостью p-типа, четыре входные шины, одну выходную, шину питания и нулевую шину, затворы первого и пятого транзисторов подключены к первой входной шине, затворы второго и седьмого транзистора подключены к третьей входной шине, затворы третьего и шестого транзисторов подключены ко второй входной шине, затворы четвертого и шестого транзистора подключены к четвертой входной шине, истоки первого и третьего транзисторов с проводимостью n-типа подключены к шине питания, истоки шестого и восьмого транзисторов с проводимостью p-типа подключены к нулевой шине, сток первого транзистора с проводимостью n-типа подключен к истоку второго транзистора, сток третьего транзистора с проводимостью n-типа подключен к истоку четвертого транзистора, при этом стоки первого и третьего транзисторов с проводимостью n-типа и истоки второго и четвертого транзисторов с проводимостью n-типа соединены между собой, стоки второго и четвертого транзисторов с проводимостью n-типа и стоки пятого и седьмого транзисторов подключены к выходной шине, исток пятого транзистора с проводимостью p-типа подключен к стоку шестого транзистора с проводимостью p-типа, исток седьмого транзистора с проводимостью p-типа подключен к стоку восьмого транзистора с проводимостью p-типа.

Признаки заявляемого технического решения, отличительные от прототипа, - затворы первого и пятого транзисторов подключены к первой входной шине; затворы второго и седьмого транзистора подключены к третьей входной шине; затворы третьего и шестого транзисторов подключены ко второй входной шине; затворы четвертого и шестого транзистора подключены к четвертой входной шине; истоки первого и третьего транзисторов с проводимостью n-типа подключены к шине питания; истоки шестого и восьмого транзисторов с проводимостью p-типа подключены к нулевой шине; сток первого транзистора с проводимостью n-типа подключен к истоку второго транзистора; сток третьего транзистора с проводимостью n-типа подключен к истоку четвертого транзистора; стоки первого и третьего транзисторов с проводимостью n-типа и истоки второго и четвертого транзисторов с проводимостью n-типа соединены между собой; стоки второго и четвертого транзисторов с проводимостью n-типа и стоки пятого и седьмого транзисторов подключены к выходной шине; исток пятого транзистора с проводимостью p-типа подключен к стоку шестого транзистора с проводимостью p-типа; исток седьмого транзистора с проводимостью p-типа подключен к стоку восьмого транзистора с проводимостью p-типа.

Отличительные признаки в сочетании с известными позволяют повысить надежность элемента при отказах внешних входов и транзисторов за счет сохранения функциональной полноты реализуемой функции.

Базисная функция в соответствие с теоремой Поста позволяет реализовать путем суперпозиции любую функцию любого числа переменных.

При дискретном исполнении, в качестве КМДП транзисторов с проводимостью n-типа могут использоваться КП301, IRF7304, а в качестве КМДП транзисторов с проводимостью p-типа КП302, IRF7311 или любые другие.

Элемент может быть реализован в интегральном исполнении и использоваться в качестве универсального базиса для программируемых логических интегральных схем (ПЛИС), так как существующие базисные элементы при отказах в матрице коммутаций и при отказах транзисторов не обладают способностью к сохранению базиса.

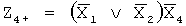

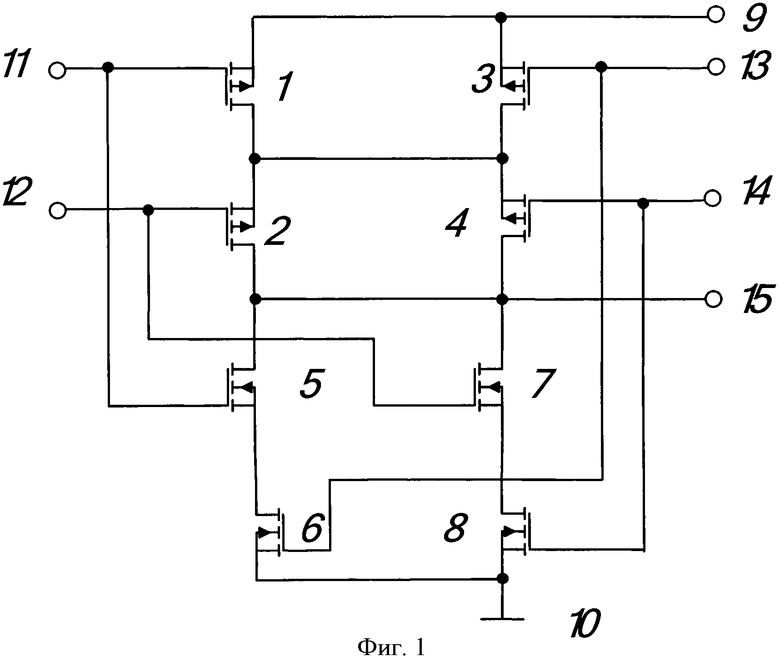

На фиг.1 приведена принципиальная электрическая схема заявляемого логического элемента.

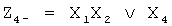

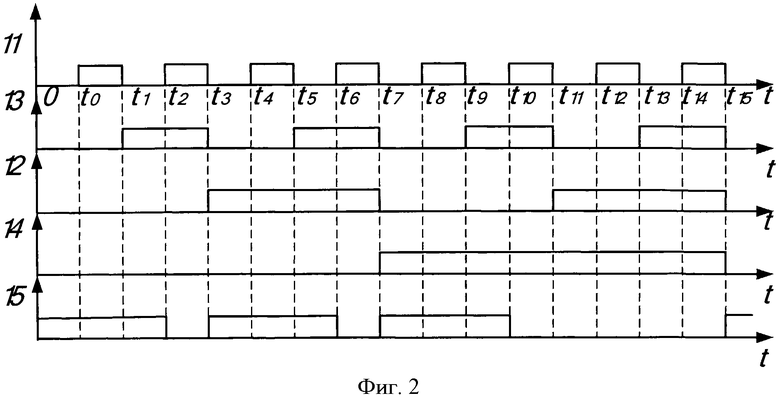

На фиг.2 приведена временная диаграмма работы заявляемого элемента.

Устройство включает четыре КМДП транзистора проводимости n-типа 1-4 и четыре КМДП транзистора проводимости p-типа 5-8 (фиг.1). Истоки транзисторов 1, 3 с проводимостью n-типа подключены к шине питания 9, истоки транзисторов 6, 8 с проводимостью p-типа подключены к нулевой шине 10. Затворы транзисторов 1, 5 подключены к первой входной шине 11, затворы транзисторов 2, 7 подключены к третьей входной шине 12, затворы транзисторов 3, 6 подключены ко второй входной шине 13, затворы транзисторов 4, 8 подключены к четвертой входной шине 14. Сток транзистора 1 с проводимостью n-типа подключен к истоку транзистора 2, сток транзистора 3 с проводимостью n-типа подключен к истоку транзистора 4. Стоки транзисторов 1, 3 с проводимостью n-типа подключены к истокам транзисторов 2, 4 с проводимостью n-типа и соединены между собой. Стоки транзисторов 2, 4 с проводимостью n-типа и стоки транзисторов 5, 7 с проводимостью p-типа подключены к выходной шине 15. Исток транзистора 5 с проводимостью p-типа подключен к стоку транзистора 6 с проводимостью p-типа, исток транзистора 7 с проводимостью p-типа подключен к стоку транзистора 8 с проводимостью p-типа.

Устройство работает следующим образом.

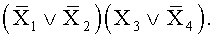

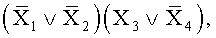

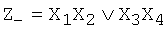

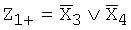

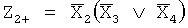

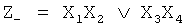

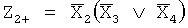

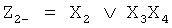

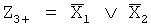

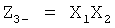

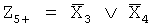

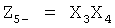

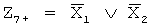

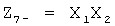

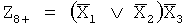

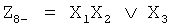

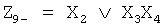

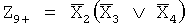

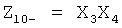

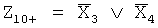

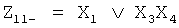

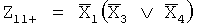

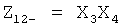

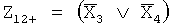

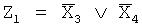

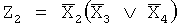

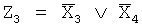

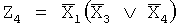

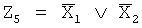

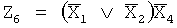

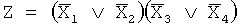

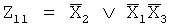

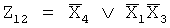

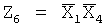

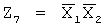

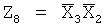

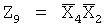

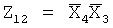

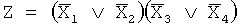

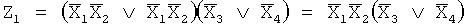

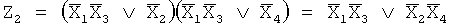

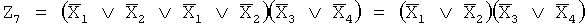

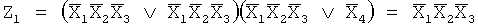

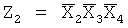

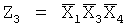

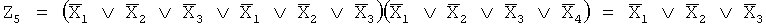

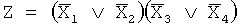

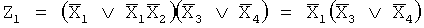

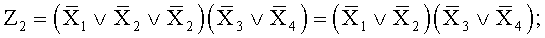

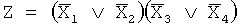

Две параллельные цепочки транзисторов 1, 3 и 2, 4 с проводимостью n-типа, включенные последовательно реализуют путем конъюнкции двух дизъюнкций выражение  Подключение источника питания на выход Z происходит при равенстве логической единице выражения

Подключение источника питания на выход Z происходит при равенстве логической единице выражения  в случае неравенства логической единице этих конъюнкций нижняя последовательно-параллельная цепь транзисторов 5-8 с проводимостью p-типа обеспечивает подключение нулевой шины 10 на выход Z в соответствии с выражением

в случае неравенства логической единице этих конъюнкций нижняя последовательно-параллельная цепь транзисторов 5-8 с проводимостью p-типа обеспечивает подключение нулевой шины 10 на выход Z в соответствии с выражением  .

.

На фиг.2 временная диаграмма отображает изменение состояния выходной шины 15 в зависимости от состояния входных сигналов 11, 12, 13, 14.

В интервале времени от 0 до t0 все входные шины 11, 12, 13, 14 находятся в низком логическом уровне, это приводит к закрытию транзисторов 5-8 с проводимостью p-типа и открытию транзисторов 1-4 с проводимостью n-типа. Через две последовательные цепочки открытых транзисторов происходит подключение выходной шины 15 к шине питания 9, поэтому на выходе элемента высокий логический уровень.

В интервале времени от t0 до t1 значение первой входной шины 11 изменяется на высокий логический уровень. В этом случае транзисторы 6-8 с проводимостью p-типа будут по-прежнему закрыты, а транзистор 5 с проводимостью p-типа будет открыт. Также изменение значения напряжения на первой входной шине 11 приведет к закрытию транзистора 1 с проводимостью n-типа, в то время как остальные транзисторы с проводимостью n-типа 2-4 будут в открытом состоянии. Через последовательную цепочку открытых транзисторов с проводимостью n-типа 3, 4 происходит подключение выходной шины 15 к шине питания 9. На выходе по-прежнему высокий логический уровень.

В интервале времени от t1 до t2 значение первой входной шины 11 переключается в ноль, а вторая входная линия 13 переключается в единицу. В данном временном промежутке транзисторы 1, 2, 4 с проводимостью n-типа и транзистор 6 с проводимостью p-типа открыты, а транзисторы 3, 5, 7, 8 находятся в закрытом состоянии. Через последовательную цепочку открытых транзисторов 1, 2 происходит подключение выходной шины 15 к шине питания 9. На выходе сохраняется высокий логический уровень.

В интервале времени от t3 до t4 на первой и второй входных линиях 11, 13 устанавливается высокий логический уровень, на другой паре входов низкий уровень. При данном наборе входных сигналов транзисторы 2, 4 с проводимостью n-типа и транзисторы 5, 6 с проводимостью p-типа открыты, а транзисторы 1, 3, 7, 8 находятся в закрытом состоянии. Через последовательную цепочку открытых транзисторов 5, 6 выходная шина 15 подключается к нулевой шине 10. Выход переключается на низкий логический уровень.

В интервале времени от t3 до t4 на третьей входной шине 12 высокий логический уровень, а на остальных входных линиях 11, 13, 14 низкий. В этом случае транзисторы 1, 3, 4, 5 находятся в открытом состоянии, а транзисторы 2, 6-8 находятся в закрытом состоянии. Через последовательную цепочку открытых транзисторов 3, 4 выходная шина 15 подключается к шине питания 9. На выходе высокий логический уровень.

В интервале времени от t4 до t5 на первой 11 и третьей 12 входных шинах высокий логический уровень, а на остальных входных линиях 13, 14 низкий логический уровень. Тогда транзисторы 3, 4, 5, 7 находятся в открытом состоянии, а транзисторы 1, 2, 6, 8 находятся в закрытом состоянии. В этом случае через открытые транзисторы 3, 4 происходит подключение выходной шины 15 к шине питания 9, поэтому значение выходного сигнала остается в высоком логическом уровне.

В интервале времени от t5 до t6 на второй 13 и третьей 12 входных шинах высокий логический уровень, в то время как на остальных входных линиях 11, 14 низкий логический уровень. Это приводит к открытию транзисторов 1, 4, 6, 7 и закрытию транзисторов 2, 3, 5, 8. Через последовательную цепочку открытых транзисторов 1, 4 происходит подключение выходной шины 15 к шине питания 9, поэтому значение выходного сигнала остается равным единице.

Во временном интервале от t6 до t7 на первых трех входных линиях 11, 13, 12 устанавливается высокий логический уровень, а на входе 14 низкий логический уровень. В этом случае транзисторы 4, 5, 6, 7 находятся в открытом состоянии, а транзисторы 1, 2, 3, 8 закрыты. Тогда через пару открытых транзисторов 5, 6 происходит подключение выхода 15 к нулевой шине 10. Отсюда следует, что выходная шина 15 переключится в низкий логический уровень.

Во временном интервале от t7 до t8 на первых трех входных линиях 11, 13, 12 устанавливается низкий логический уровень, а на входе 14 высокий логический уровень. В этом случае транзисторы 1, 2, 3, 8 находятся в открытом состоянии, а транзисторы 4, 5, 6, 7 закрыты. Поэтому через две пары последовательных цепочек открытых транзисторов 1, 2 и 2, 3 происходит подключение выхода 15 к шине питания 9 и на выходе установится высокий логический уровень.

Во временном интервале от t8 до t9 на первом 11 и четвертом 14 входе единицы, а на остальных 12, 13 нули. Тогда транзисторы 2, 3, 5, 8 находятся в открытом состоянии, а транзисторы 1, 4, 6, 7 закрыты. Через последовательную цепочку открытых транзисторов 2, 3 выходная шина 15 подключается к шине питания 9 и на выходе будет высокий логический уровень.

Во временном интервале от t9 до t10 на втором 13 и четвертом 14 входе единицы, а на остальных входных линиях 11, 12 нули. Поэтому транзисторы 1, 2, 6, 8 находятся в открытом состоянии, а транзисторы 3, 4, 5, 7 закрыты. Через открытые транзисторы 1, 2 выходная шина 15 подключается к шине питания 9 и на выходе остается высокий логический уровень.

Во временном интервале от t10 до t11 на первой 11, второй 13 и четвертой 14 входных шинах высокий логический уровень, а третьем входе 12 низкий логический уровень. Тогда транзисторы 2, 5, 6, 8 находятся в открытом состоянии, а транзисторы 1, 3, 4, 7 закрыты. Через открытую цепочку транзисторов 5, 6 выходная шина 15 подключается к нулевой шине 10 и на выходе устанавливается низкий логический уровень.

В интервале времени от t11 до t12 на первой паре входных линий 11, 13 находится низкий логический уровень, а на второй паре входных линий 12, 14 высокий логический уровень. Данный набор входных сигналов приведет к открытию транзисторов 1, 3, 7, 8 и закрытию транзисторов 2, 4, 5, 6. Через два открытых транзистора 7, 8 выходная шина 15 будет подключена к нулевой шине 10 и на выходе останется низкий логический уровень.

В интервале времени от t12 до t13 на первой 11, третьей 12 и четвертой 14 входных линиях высокий логический уровень, а на втором входе 13 низкий логический уровень. В этом случае транзисторы 3, 5, 7, 8 будут открыты, а транзисторы 1, 2, 4, 6 закрыты. Через открытую цепочку транзисторов 7, 8 выходная шина 15 подключается к нулевой шине 10 и на выходе останется ноль.

В интервале времени от t13 до t14 на первой входной шине 11 будет низкий логический уровень, а на второй 13, третьей 12 и четвертой 14 входных шинах будет высокий логический уровень. Тогда транзисторы 1, 6-8 будут открыты, а транзисторы 2-5 закрыты. Через открытую цепочку транзисторов 7, 8 выходная шина 15 остается подключенной к нулевой шине 10 и на выходе по-прежнему остается низкий логический уровень.

В интервале времени от t14 до t15 на всех входных шинах 11, 13, 12, 14 будет высокий логический уровень. Поэтому транзисторы 5-8 с проводимостью p-типа будут открыты, а транзисторы 1-4 с проводимостью n-типа закрыты. Через открытые транзисторы 5, 6 и 7, 8 выходная шина 15 подключена к нулевой шине 10 и на выходе низкий логический уровень.

Покажем, что заявляемое устройство обеспечивает сохранение базиса при однократных константных отказах. Для этого рассчитаем вероятность сохранения базиса у ФПТ при однократных константных отказах транзисторов. Для КМДП транзисторов возможны два случая константных отказа это константа единицы, которая эквивалентна пробою связи сток-исток или постоянно включенному затвору и константа нуля, которая эквивалентна обрыву связи сток-исток или обрыву затвора. Таким образом, возможны 16 случаев отказов. Полная группа событий включает следующие реализации:

1. Пробой цепи сток-исток (или постоянно включенный затвор) первого транзистора.

2. Обрыв цепи сток-исток (или обрыв затвора) первого транзистора.

3. Пробой цепи сток-исток (или постоянно включенный затвор) второго транзистора.

4. Обрыв цепи сток-исток (или обрыв затвора) второго транзистора.

5. Пробой цепи сток-исток (или постоянно включенный затвор) третьего транзистора.

6. Обрыв цепи сток-исток (или обрыв затвора) третьего транзистора.

7. Пробой цепи сток-исток (или постоянно включенный затвор) четвертого транзистора.

8. Обрыв цепи сток-исток (или обрыв затвора) четвертого транзистора.

9. Пробой цепи сток-исток (или постоянно включенный затвор) пятого транзистора.

10. Обрыв цепи сток-исток (или обрыв затвора) пятого транзистора.

11. Пробой цепи сток-исток (или постоянно включенный затвор) шестого транзистора.

12. Обрыв цепи сток-исток (или обрыв затвора) шестого транзистора.

13. Обрыв цепи сток-исток (или обрыв затвора) седьмого транзистора.

14. Пробой цепи сток-исток (или постоянно включенный затвор) седьмого транзистора.

15. Обрыв цепи сток-исток (или обрыв затвора) восьмого транзистора.

16. Пробой цепи сток-исток (или постоянно включенный затвор) восьмого транзистора.

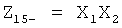

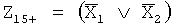

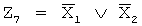

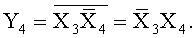

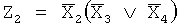

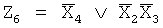

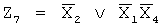

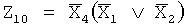

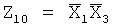

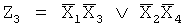

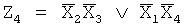

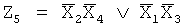

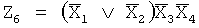

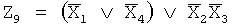

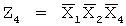

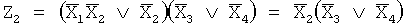

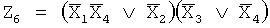

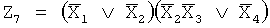

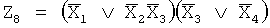

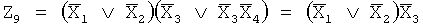

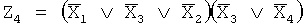

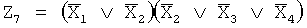

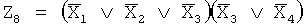

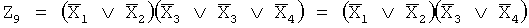

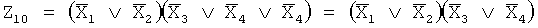

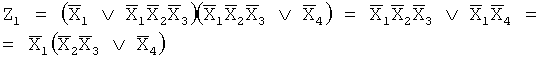

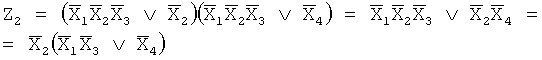

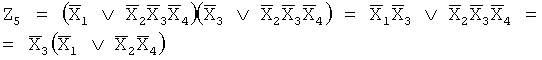

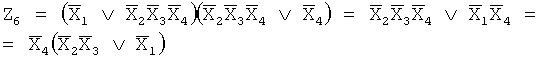

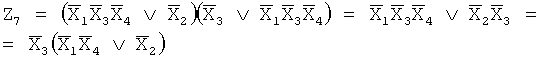

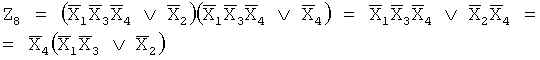

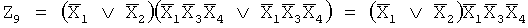

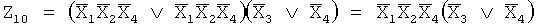

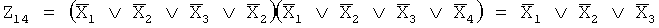

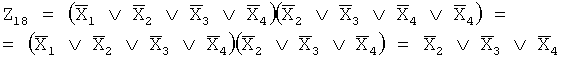

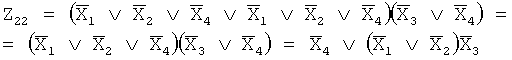

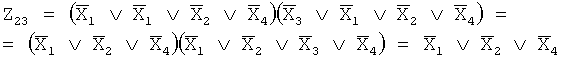

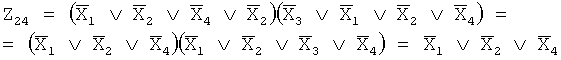

Произведем расчет сохранения базиса для ФПТ по фиг.1.

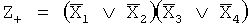

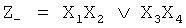

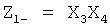

Причем в данном случае необходимо рассматривать как функцию подключения к шине питания  , так и функцию подключения к шине ноль вольт

, так и функцию подключения к шине ноль вольт  .

.

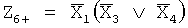

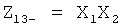

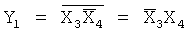

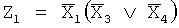

1. Пробой цепи сток-исток (или постоянно включенный затвор) первого транзистора. В данном случае исток второго транзистора оказывается подключенным к шине питания, и базис будет иметь вид  .

.

Это базисная функция в смысле теоремы Поста. Таким образом, поскольку  не изменяется, для обеспечения ортогональности необходима

не изменяется, для обеспечения ортогональности необходима  . Для этого в подаваемых наборах Х1=0 и Х2=0.

. Для этого в подаваемых наборах Х1=0 и Х2=0.

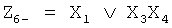

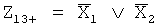

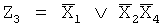

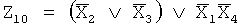

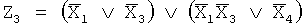

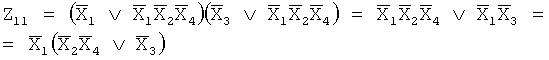

2. Обрыв цепи сток-исток (или обрыв затвора) первого транзистора.

Получаем базисную с точки зрения теоремы Поста функцию  . Однако, поскольку

. Однако, поскольку  не изменяется, для обеспечения ортогональности (взаимной инверсности) с

не изменяется, для обеспечения ортогональности (взаимной инверсности) с  , необходима

, необходима  . Для этого в подаваемых наборах X1=1.

. Для этого в подаваемых наборах X1=1.

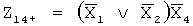

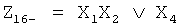

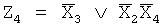

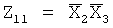

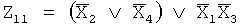

3. Пробой цепи сток-исток (или постоянно включенный затвор) второго транзистора. Аналогично получаем базисную с точки зрения теоремы Поста функцию  . Тогда

. Тогда  .

.

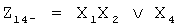

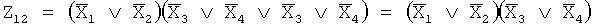

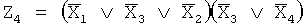

4. Обрыв цепи сток-исток (или обрыв затвора) второго транзистора. В данном случае получим  и

и  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

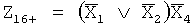

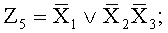

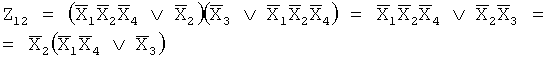

5. Пробой цепи сток-исток (или постоянно включенный затвор) третьего транзистора. Аналогично получаем  и

и  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

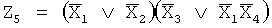

6. Обрыв цепи сток-исток (или обрыв затвора) третьего транзистора. Получаем базисную функцию  , а

, а  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

7. Пробой цепи сток-исток (или постоянно включенный затвор) четвертого транзистора. Аналогично получаем  и

и  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

8. Обрыв цепи сток-исток (или обрыв затвора) четвертого транзистора. Получаем базисную функцию  , в то время как

, в то время как  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

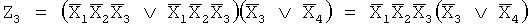

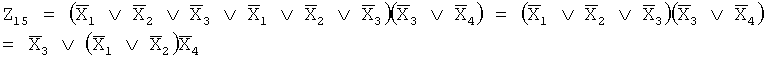

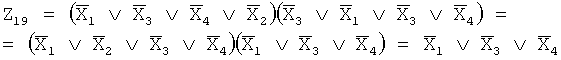

9. Пробой цепи сток-исток (или постоянно включенный затвор) пятого транзистора. Для пятого и последующих транзисторов отказы будут сказываться на функции подключения к шине ноль вольт. Поэтому получаем  , значит надо использовать базис

, значит надо использовать базис  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

10. Обрыв цепи сток-исток (или обрыв затвора) пятого транзистора. Получаем  . Значит надо использовать базис

. Значит надо использовать базис  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

11. Пробой цепи сток-исток (или постоянно включенный затвор) шестого транзистора. Получаем  , значит, базис

, значит, базис  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

12. Обрыв цепи сток-исток (или обрыв затвора) шестого транзистора. Получаем  . Базис

. Базис  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

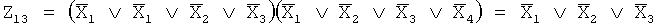

13. Обрыв цепи сток-исток (или обрыв затвора) седьмого транзистора. Получаем  . Базис

. Базис  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

14. Пробой цепи сток-исток (или постоянно включенный затвор) седьмого транзистора. Получаем  , значит, базис

, значит, базис  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

15. Обрыв цепи сток-исток (или обрыв затвора) восьмого транзистора. Получаем  . Базис

. Базис  . Это базисная функция в смысле теоремы Поста.

. Это базисная функция в смысле теоремы Поста.

16. Пробой цепи сток-исток (или постоянно включенный затвор) восьмого транзистора. Получаем  , значит, базис

, значит, базис  .

.

Это базисная функция в смысле теоремы Поста.

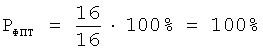

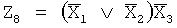

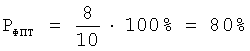

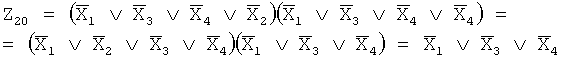

Получаем, что из шестнадцати случаев однократных константных отказов в транзисторах базис ни разу не был потерян, поэтому вероятность сохранения базиса равна

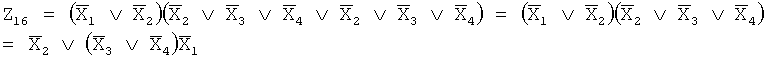

Теперь произведем расчет вероятности сохранения базиса у функционально-полного толерантного элемента в случае внешних однократных константных отказах входов и выхода. Для каждой входной шины 11, 13, 12, 14 и для выходной шины 15 возможны случаи замыкания на шину питания 9 и на шину ноль вольт 10. Таким образом, всего возможны 10 случаев отказов. Полная группа событий включает следующие реализации:

1. Замыкание первого входа 11 на шину ноль вольт 10.

2. Замыкание первого входа 11 на шину питания 9.

3. Замыкание второго входа 13 на шину ноль вольт 10.

4. Замыкание второго входа 13 на шину питания 9.

5. Замыкание третьего входа 12 на шину ноль вольт 10.

6. Замыкание третьего входа 12 на шину питания 9.

7. Замыкание четвертого входа 14 на шину ноль вольт 10.

8. Замыкание четвертого входа 14 на шину питания 9.

9. Замыкание выходной шины 15 на шину ноль вольт 10.

10. Замыкание выходной шины 15 на шину питания 9.

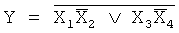

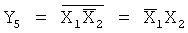

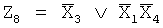

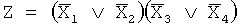

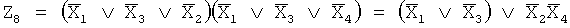

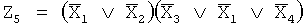

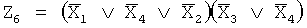

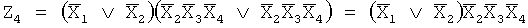

Как известно ФПТ реализует логическую функцию  . Рассмотрим подробней каждую реализацию:

. Рассмотрим подробней каждую реализацию:

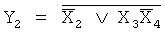

1. Замыкание первого входа 11 на шину ноль вольт 10. В данном случае, в выражение для логической функции нужно поставить ноль, тогда в качестве базиса будет выступать выражение  .

.

2. Замыкание первого входа 11 на шину питания 9. В данном случае, в выражение для логической функции нужно поставить единицу, тогда в качестве базиса будет выступать выражение  .

.

3. Замыкание второго входа 13 на шину ноль вольт 10. Базис  .

.

4. Замыкание второго входа 13 на шину питания 9. Базис  .

.

5. Замыкание третьего входа 12 на шину ноль вольт 10. Базис  .

.

6. Замыкание третьего входа 12 на шину питания 9. Базис  .

.

7. Замыкание четвертого входа 14 на шину ноль вольт 10. Базис  .

.

8. Замыкание четвертого входа 14 на шину питания 9. Базис  .

.

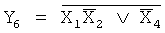

9. Замыкание выхода 15 на шину ноль вольт 10. В этом случае на выходе всегда будет низкий логический уровень. Элемент не сможет реализовать никакого базиса. Базис потерян  .

.

10. Замыкание выхода 15 на шину питания 9. В этом случае на выходе всегда будет высокий логический уровень. Базис потерян  .

.

Таким образом, из десяти случаев внешних однократных константных отказов базис был потерян в двух из них, поэтому вероятность сохранения базиса равна

В случае внешних однократных константных отказов выхода происходит потеря базиса, однако в случае однократных константных отказов входов базис сохраняется.

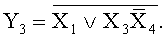

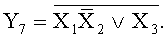

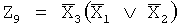

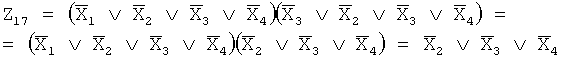

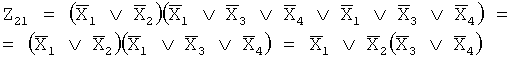

Теперь рассмотрим функционирование прототипа в случае внешних однократных константных отказах входов и выходов. Для него также возможны десять случаев отказов. Прототип реализует логическую функцию  . Это базисная функция при X4=0, X2=0 - НЕ-ИЛИ:

. Это базисная функция при X4=0, X2=0 - НЕ-ИЛИ:  .

.

Рассмотрим подробней каждую реализацию при отказах:

1. Замыкание первого входа на шину ноль вольт. В данном случае, в выражение для логической функции нужно поставить ноль, тогда  . Это не базисная функция.

. Это не базисная функция.

2. Замыкание первого входа на шину питания. В данном случае, в выражение для логической функции нужно поставить единицу, тогда прототип будет реализовывать функцию  . Это не базисная функция.

. Это не базисная функция.

3. Замыкание второго входа на шину ноль вольт. Функция  Это базисная функция при Х4=0.

Это базисная функция при Х4=0.

4. Замыкание второго входа на шину питания. Функция  Это не базисная функция.

Это не базисная функция.

5. Замыкание третьего входа на шину ноль вольт. Функция  . Это не базисная функция.

. Это не базисная функция.

6. Замыкание третьего входа на шину питания. Функция  . Это не базисная функция.

. Это не базисная функция.

7. Замыкание четвертого входа на шину ноль вольт. Функция  Это базисная функция при Х2=0.

Это базисная функция при Х2=0.

8. Замыкание четвертого входа на шину питания. Функция  . Это не базисная функция.

. Это не базисная функция.

9. Замыкание выхода на шину ноль вольт. В этом случае на выходе всегда будет низкий логический уровень. Прототип не сможет реализовать никакой логической функции  .

.

10. Замыкание выхода на шину питания. В этом случае на выходе всегда будет высокий логический уровень. На выходе будет  .

.

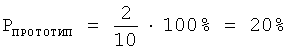

Таким образом, прототип сохраняет базис только в случае внешних однократных константных отказов входов. Из десяти случаев внешних однократных константных отказов прототип реализовывал базисную с точки зрения теоремы Поста функцию в двух случаях. Поэтому вероятность сохранения базиса равна

В случае же однократных константных отказах в транзисторах вероятность сохранения базиса у прототипа равна нулю.

Таким образом, заявляемый элемент сохраняет базис в смысле теоремы Поста при внешних однократных константных отказах входов и выхода с вероятностью 80% и с вероятностью 100% при внутренних однократных константных отказах транзисторов. В то время как у прототипа базис сохраняется при внешних однократных константных отказах в 20%, при отказах транзисторов не сохраняется ни в одном случае.

Кроме того, ФПТ элемент устойчив к отказам типа замыканий (bridging fault). Как известно данный тип отказов представляется тремя моделями отказов: модель замыканий типа проводного И/ИЛИ (Wired - AND/OR), доминантная модель замыканий (Dominant), доминантная модель замыкания типа И/ИЛИ (Dominant - AND/OR).

Рассмотрим доминантную модель при замыканиях двух входов. В этом случае получаем  вариантов. Каждый такой вариант характеризуется «превалированием» одной из двух переменных. Тогда полная группа событий включает 12 реализаций:

вариантов. Каждый такой вариант характеризуется «превалированием» одной из двух переменных. Тогда полная группа событий включает 12 реализаций:

1. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  ;

;

2. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  ;

;

3. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  ;

;

4. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  ;

;

5. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  ;

;

6. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  ;

;

7. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  ;

;

8. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  ;

;

9. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  ;

;

10. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  ;

;

11. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  ;

;

12. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  .

.

Рассмотрим подробней каждую реализацию при отказах в функции  :

:

1. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  ;

;

1. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

3. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  ;

;

4. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

5. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис

6. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  ;

;

7. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

8. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

9. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

10. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  ;

;

11. Замыкание  и

и  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

12. Замыкание  и

и  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  .

.

Рассмотрим доминантную модель отказов при замыкании трех входов. В этом случае получаем  вариантов. Каждый вариант характеризуется «превалированием» одной из трех переменных. Тогда полная группа событий включает 12 реализаций:

вариантов. Каждый вариант характеризуется «превалированием» одной из трех переменных. Тогда полная группа событий включает 12 реализаций:

1. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

2. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

3. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

4. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

5. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

6. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

7. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

8. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

9. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

10. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

11. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  ;

;

12. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  .

.

Рассмотрим подробней каждую реализацию при отказах в функции  :

:

1. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  ;

;

2. Замыкание  ,

,  ,

,  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

3. Замыкание  ,

,  ,

,  третья вариант - превалирует

третья вариант - превалирует  . Базис

. Базис  ;

;

4. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  ;

;

5. Замыкание  ,

,  ,

,  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

6. Замыкание  ,

,  ,

,  третий вариант - превалирует

третий вариант - превалирует  . Базис

. Базис  ;

;

7. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  ;

;

8. Замыкание  ,

,  ,

,  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

9. Замыкание  ,

,  ,

,  третий вариант - превалирует

третий вариант - превалирует  . Базис

. Базис  ;

;

10. Замыкание  ,

,  ,

,  первый вариант - превалирует

первый вариант - превалирует  . Базис

. Базис  ;

;

11. Замыкание  ,

,  ,

,  второй вариант - превалирует

второй вариант - превалирует  . Базис

. Базис  ;

;

12. Замыкание  ,

,  ,

,  третий вариант - превалирует

третий вариант - превалирует  . Базис

. Базис  .

.

Рассмотрим модель отказов типа проводного И/ИЛИ при замыкании двух входов. В этом случае получаем  вариантов. Для каждого варианта возможны отказы типа И и ИЛИ. Тогда полная группа событий включает 12 реализаций:

вариантов. Для каждого варианта возможны отказы типа И и ИЛИ. Тогда полная группа событий включает 12 реализаций:

1. Замыкание  и

и  проводное И;

проводное И;

2. Замыкание  и

и  проводное И;

проводное И;

3. Замыкание  и

и  проводное И;

проводное И;

4. Замыкание  и

и  проводное И;

проводное И;

5. Замыкание  и

и  проводное И;

проводное И;

6. Замыкание  и

и  проводное И;

проводное И;

7. Замыкание  и

и  проводное ИЛИ;

проводное ИЛИ;

8. Замыкание  и

и  проводное ИЛИ;

проводное ИЛИ;

9. Замыкание  и

и  проводное ИЛИ;

проводное ИЛИ;

10. Замыкание  и

и  проводное ИЛИ;

проводное ИЛИ;

11. Замыкание  и

и  проводное ИЛИ;

проводное ИЛИ;

12. Замыкание  и

и  проводное ИЛИ.

проводное ИЛИ.

Рассмотрим подробней каждую реализацию при отказах в функции  :

:

1. Замыкание  и

и  проводное И. Базис

проводное И. Базис  ;

;

2. Замыкание  и

и  проводное И. Базис

проводное И. Базис  ;

;

3. Замыкание  и

и  проводное И. Базис

проводное И. Базис  ;

;

4. Замыкание  и

и  проводное И. Базис

проводное И. Базис  ;

;

5. Замыкание  и

и  проводное И. Базис

проводное И. Базис  ;

;

6. Замыкание  и

и  проводное И. Базис

проводное И. Базис  ;

;

7. Замыкание  и

и  проводное ИЛИ. Базис

проводное ИЛИ. Базис  ;

;

8. Замыкание  и

и  проводное ИЛИ. Базис

проводное ИЛИ. Базис  ;

;

9. Замыкание  и

и  проводное ИЛИ. Базис

проводное ИЛИ. Базис  ;

;

10. Замыкание  и

и  проводное ИЛИ. Базис

проводное ИЛИ. Базис  ;

;

11. Замыкание  и

и  проводное ИЛИ. Базис

проводное ИЛИ. Базис  ;

;

12. Замыкание  и

и  проводное ИЛИ. Базис

проводное ИЛИ. Базис  .

.

Рассмотрим модель отказов типа проводного И/ИЛИ при замыкании трех входов. В этом случае получаем  вариантов. Для каждого варианта возможны отказы типа И и ИЛИ. Тогда полная группа событий включает 8 реализаций:

вариантов. Для каждого варианта возможны отказы типа И и ИЛИ. Тогда полная группа событий включает 8 реализаций:

1. Замыкание  ,

,  ,

,  проводное И;

проводное И;

2. Замыкание  ,

,  ,

,  проводное И;

проводное И;

3. Замыкание  ,

,  ,

,  проводное И;

проводное И;

4. Замыкание  ,

,  ,

,  проводное И;

проводное И;

5. Замыкание  ,

,  ,

,  проводное ИЛИ;

проводное ИЛИ;

6. Замыкание  ,

,  ,

,  проводное ИЛИ;

проводное ИЛИ;

7. Замыкание  ,

,  ,

,  проводное ИЛИ;

проводное ИЛИ;

8. Замыкание  ,

,  ,

,  проводное ИЛИ.

проводное ИЛИ.

Рассмотрим подробней каждую реализацию при отказах в функции  :

:

1. Замыкание  ,

,  ,

,  проводное И. Базис

проводное И. Базис  ;

;

2. Замыкание  ,

,  ,

,  проводное И. Базис

проводное И. Базис  ;

;

3. Замыкание  ,

,  ,

,  проводное И. Базис

проводное И. Базис  ;

;

4. Замыкание  ,

,  ,

,  проводное И. Базис

проводное И. Базис  ;

;

5. Замыкание  ,

,  ,

,  проводное ИЛИ. Базис

проводное ИЛИ. Базис  ;

;

6. Замыкание  ,

,  ,

,  проводное ИЛИ. Базис

проводное ИЛИ. Базис  ;

;

7. Замыкание  ,

,  ,

,  проводное ИЛИ. Базис

проводное ИЛИ. Базис  ;

;

8. Замыкание  ,

,  ,

,  проводное ИЛИ. Базис

проводное ИЛИ. Базис  .

.

Рассмотрим доминантную модель отказов типа И/ИЛИ при замыкании двух входов. В этом случае получаем  вариантов. Для каждого варианта возможны отказы типа И и ИЛИ и превалирование одного из двух входов. Тогда полная группа событий включает 24 реализации:

вариантов. Для каждого варианта возможны отказы типа И и ИЛИ и превалирование одного из двух входов. Тогда полная группа событий включает 24 реализации:

1. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

2. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

3. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

4. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

5. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

6. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

7. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

8. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

9. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

10. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

11. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

12. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  ;

;

13. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

14. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

15. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

16. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

17. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

18. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

19. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

20. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

21. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

22. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

23. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

24. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  .

.

Рассмотрим подробней каждую реализацию при отказах в функции  .

.

1. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

2. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

3. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

4. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

5. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

6. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

7. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

8. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

9. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

10. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

11. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

12. Замыкание  и

и  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

13. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

14. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис

15. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

16. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

17. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

18. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

19. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

20. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

21. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

22. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

23. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

24. Замыкание  и

и  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  .

.

Рассмотрим доминантную модель отказов типа И/ИЛИ при замыкании трех входов. В этом случае получаем  вариантов. Для каждого варианта возможны отказы типа И и ИЛИ и превалирование одного из трех входов. Тогда полная группа событий включает 24 реализации:

вариантов. Для каждого варианта возможны отказы типа И и ИЛИ и превалирование одного из трех входов. Тогда полная группа событий включает 24 реализации:

1. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

2. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

3. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

4. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

5. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

6. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

7. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

8. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

9. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

10. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

11. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

12. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  ;

;

13. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

14. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

15. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

16. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

17. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

18. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

19. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

20. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

21. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

22. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

23. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  ;

;

24. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  .

.

Рассмотрим подробней каждую реализацию при отказах в функции  :

:

1. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

2. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

3. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

4. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

5. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

6. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

7. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

8. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

9. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

10. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

11. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис  ;

;

12. Замыкание  ,

,  ,

,  доминантное И - превалирует

доминантное И - превалирует  . Базис

. Базис

;

;

13. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

14. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

15. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

16. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

17. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

18. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

19. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

20. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

21. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

22. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

23. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  ;

;

24. Замыкание  ,

,  ,

,  доминантное ИЛИ - превалирует

доминантное ИЛИ - превалирует  . Базис

. Базис  .

.

Таким образом, проведенный расчет показывает, что функционально-полный толерантный элемент сохраняет функциональную полноту не только для константных однократных отказов, но и для отказов типа замыканий, которые описывают большое число неисправностей, наблюдаемых в ПЛИС. В свою очередь прототип подобными свойствами не обладает. Следовательно, заявляемый элемент имеет более высокую надежность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2010 |

|

RU2438234C1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2012 |

|

RU2496227C1 |

| ФУНКЦИОНАЛЬНО-ПОЛНЫЙ ТОЛЕРАНТНЫЙ ЭЛЕМЕНТ | 2013 |

|

RU2541854C1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2015 |

|

RU2616874C2 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2016 |

|

RU2628152C1 |

| ЯЧЕЙКА СТАТИЧЕСКОЙ ОПЕРАТИВНОЙ ПАМЯТИ | 2014 |

|

RU2573226C2 |

| МАЖОРИТАРНОЕ УСТРОЙСТВО | 2015 |

|

RU2580080C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ на полевых транзисторах | 2023 |

|

RU2813863C1 |

| ИНТЕГРАЛЬНЫЙ ВЫХОДНОЙ МДП-ИНВЕРТОР | 1992 |

|

RU2012100C1 |

| ДИНАМИЧЕСКИЙ D-ТРИГГЕР | 2018 |

|

RU2679220C1 |

Изобретение относится к вычислительной технике, а именно к цифровым схемам, имеющим повышенные требования по надежности, в частности в авиационной и космической областях промышленности. Техническим результатом является повышение надежности элемента при отказах внешних входов и транзисторов за счет сохранения функциональной полноты реализуемой функции. Функционально-полный толерантный элемент содержит первый, второй, третий, четвертый транзисторы с проводимостью n-типа, пятый, шестой, седьмой, восьмой транзисторы с проводимостью p-типа, первую, вторую, третью, четвертую входную шину, шину питания, нулевую шину, выходную шину. 2 ил.

Функционально-полный толерантный элемент, содержащий первый, второй, третий, четвертый транзисторы с проводимостью n-типа, пятый, шестой, седьмой, восьмой транзисторы с проводимостью p-типа, четыре входные шины, одну выходную шину питания и нулевую шину, отличающийся тем, что затворы первого и пятого транзисторов подключены к первой входной шине, затворы второго и седьмого транзистора подключены к третьей входной шине, затворы третьего и шестого транзисторов подключены ко второй входной шине, затворы четвертого и шестого транзистора подключены к четвертой входной шине, истоки первого и третьего транзисторов с проводимостью n-типа подключены к шине питания, истоки шестого и восьмого транзисторов с проводимостью p-типа подключены к нулевой шине, сток первого транзистора с проводимостью n-типа подключен к истоку второго транзистора, сток третьего транзистора с проводимостью n-типа подключен к истоку четвертого транзистора, при этом стоки первого и третьего транзисторов с проводимостью n-типа и истоки второго и четвертого транзисторов с проводимостью n-типа соединены между собой, стоки второго и четвертого транзисторов с проводимостью n-типа и стоки пятого и седьмого транзисторов подключены к выходной шине, исток пятого транзистора с проводимостью p-типа подключен к стоку шестого транзистора с проводимостью p-типа, исток седьмого транзистора с проводимостью p-типа подключен к стоку восьмого транзистора с проводимостью p-типа.

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2004 |

|

RU2275737C1 |

| US 6188339 B1, 13.02.2001 | |||

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

Авторы

Даты

2012-04-27—Публикация

2011-05-23—Подача