Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении отказоустойчивых самосинхронных схем.

Известен С-элемент Маллера, функциональный аналог гистерезисного триггера, содержащий три элемента, два инвертера и цепи подключения шины «+» питания и шины «Ноль вольт». [Yancey S., Smith S. С.A differential design for C-elements and NCL gates // Circuits and Systems (MWSCAS), 2010 53rd IEEE International Midwest Symposium on, vol., no. - 2010. - T. 632. - C. 1-4.]

Недостатком известного устройства является низкая отказоустойчивость.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является гистерезисный триггер, содержащий группу из шести транзисторов p-проводимости, группу шести транзисторов n-проводимости, выход триггера, вход подключения шины питания «Vcc», вход подключения шины «Ноль вольт», первый и второй входы триггера, причем первый вход триггера подключен к затворам пятого и третьего транзисторов p-проводимости, пятого и третьего транзисторов n-проводимости, второй вход триггера подключен к затворам четвертого и шестого транзисторов p-проводимости, четвертого и шестого транзистора n-проводимости, истоки первого, третьего, четвертого и пятого транзисторов p-проводимости подключены ко входу подключения шины питания «Vcc», сток пятого транзистора p-проводимости подключен к истоку шестого транзистора p-проводимости, истоки первого третьего, четвертого и пятого транзистора n-проводимости подключены ко входу подключения шины «Ноль вольт», сток пятого транзистора n-проводимости подключен к истоку шестого транзистора p-проводимости, сток первого транзистора p-проводимости подключен к стоку первого транзистора n-проводимости и к выходу триггера, который подключен к объединенным затворам второго транзистора p-проводимости и второго транзистора n-проводимости, стоки которых объединены и подключены к затворам первого транзистора p-проводимости и первого транзистора n-проводимости, объединенным стокам шестого транзистора p-проводимости и шестого транзистора n-проводимости, стоки третьего и четвертого транзисторов p-проводимости подключены к истоку второго транзистора p-проводимости, стоки третьего и четвертого транзисторов n-проводимости, подключены к истоку второго транзистора n-проводимости (Ю.А. Степченков, А.Н. Денисов, Ю.Г. Дьяченко, Ф.И. Гринфельд, О.П. Филимоненко, Н.В. Морозов, Д.Ю. Степченков. Библиотека элементов для проектирования самосинхронных полузаказных микросхем серий 5503/5507 и 5508/5509 - М.: ИЛИ РАН, 2008. - 238 с., функциональная схема гистерезисного триггера представлена на стр. 91). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения: группа из шести транзисторов p-проводимости, группа шести транзисторов n-проводимости, выход триггера, вход подключения шины питания «Vcc», вход подключения шины «Ноль вольт», первый и второй входы триггера, причем первый вход триггера подключен к затворам пятого транзистора p-проводимости и пятого транзистора n-проводимости, второй вход триггера подключен к затворам шестого транзистора p-проводимости и шестого транзистора n-проводимости, исток первого транзистора p-проводимости и пятого транзистора p-проводимости подключены ко входу подключения шины питания «Vcc», сток пятого транзистора p-проводимости подключен к истоку шестого транзистора p-проводимости, исток первого транзистора n-проводимости и пятого транзистора n-проводимости подключены ко входу подключения шины «Ноль вольт», сток пятого транзистора n-проводимости подключен к истоку шестого транзистора n-проводимости, сток первого транзистора p-проводимости подключен к стоку первого транзистора n-проводимости и к выходу триггера, который подключен к объединенным затворам второго транзистора p-проводимости и второго транзистора n-проводимости, стоки которых объединены и подключены к затворам первого транзистора p-проводимости и первого транзистора n-проводимости, стоки третьего и четвертого транзисторов p-проводимости объединены и подключены к истоку второго транзистора p-проводимости, стоки третьего и четвертого транзисторов n-проводимости объединены и подключены к истоку второго транзистора n - проводимости, затворы третьего транзистора p-проводимости и третьего транзистора n - проводимости подключены ко второму входу триггера.

Недостатком известного устройства, принятого за прототип, является невозможность использования в резервированных самосинхронных схемах, учитывающих возможность отказа в одном из каналов.

Это обусловлено следующими обстоятельствами.

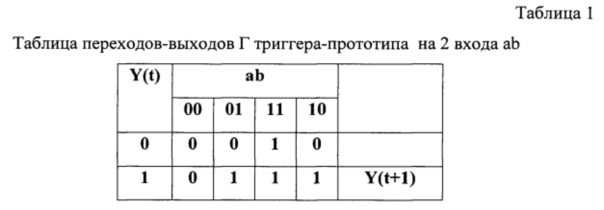

Г триггер-прототип ожидает завершения переходных процессов на всех его входах: а (первый вход) и b (второй вход), когда они оба станут единицами, после чего переходит в состояние Y(t)=1, из которого возвращается в состояние Y(t)=0 в том случае, когда оба входа станут нулями - табл. 1:

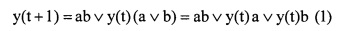

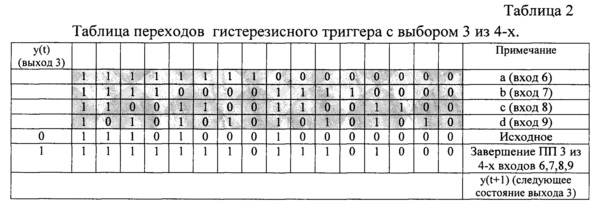

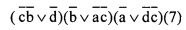

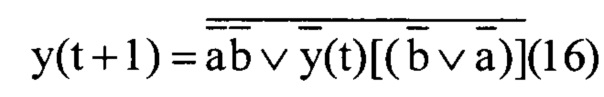

Из табл. 1 получается функция переходов Г триггера-прототипа, которая имеет вид:

.

.

Преобразуя (1) с помощью двойной инверсии, получим:

.

.

Выражению (2) и соответствует Комплементарная Металл-Окисел-Проводник схема - КМОП схема (Ю.А. Степченков, А.Н. Денисов, Ю.Г. Дьяченко, Ф.И. Гринфельд, О.П. Филимоненко, Н.В. Морозов, Д.Ю. Степченков. Библиотека элементов для проектирования самосинхронных полузаказных микросхем серий 5503/5507 и 5508/5509 - М.: ИЛИ РАН, 2008. - 238 с., функциональная схема гистерезисного триггера представлена на стр. 91). В случае не завершения переходного процесса по одному из входов, в случае использования прототипа в двухканальной резервированной схеме, работа такой самосинхронной схемы будет невозможна. При каскадировании Г триггеров-прототипов для реализации трех и более канальных самосинхронных схем в случае не завершения переходного процесса (вследствие отказа) в одном из каналов произойдет отказ всей резервированной самосинхронной схемы.

Таким образом, технические средства прототипа не обеспечивают возможность его использования в резервированных самосинхронных схемах, учитывающих возможность отказа в одном из каналов.

Задачей изобретения является обеспечение возможности использования гистерезисного триггера в резервированных самосинхронных схемах, учитывающих возможность отказа в одном из каналов.

Поставленная задача была решена за счет того, что в известное устройство, содержащее группу из шести транзисторов p-проводимости, группу шести транзисторов n-проводимости, выход триггера, вход подключения шины питания «Vcc», вход подключения шины «Ноль вольт», первый и второй входы триггера, причем первый вход триггера подключен к затворам пятого транзистора p-проводимости и пятого транзистора n-проводимости, второй вход триггера подключен к затворам шестого транзистора p-проводимости и шестого транзистора n-проводимости, исток первого транзистора p-проводимости и пятого транзистора p-проводимости подключены ко входу подключения шины питания «Vcc», сток пятого транзистора p-проводимости подключен к истоку шестого транзистора p-проводимости, исток первого транзистора n-проводимости и пятого транзистора n-проводимости подключены ко входу подключения шины «Ноль вольт», сток пятого транзистора n-проводимости подключен к истоку шестого транзистора n-проводимости, сток первого транзистора p-проводимости подключен к стоку первого транзистора n-проводимости и к выходу триггера, который подключен к объединенным затворам второго транзистора p-проводимости и второго транзистора n-проводимости, стоки которых объединены и подключены к затворам первого транзистора p-проводимости и первого транзистора n-проводимости, стоки третьего и четвертого транзисторов p-проводимости объединены и подключены к истоку второго транзистора p-проводимости, стоки третьего и четвертого транзисторов n-проводимости объединены и подключены к истоку второго транзистора n-проводимости, затворы третьего транзистора p-проводимости и третьего транзистора n-проводимости подключены ко второму входу триггера, согласно изобретению дополнительно введены 15 транзисторов p-проводимости и 15 транзисторов n-проводимости, третий и четвертый входы, причем истоки девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов n-проводимости подключены ко входу подключения шины «Ноль вольт», истоки девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов p-проводимости подключены ко входу подключения шины «Vcc», затворы десятого, двенадцатого и четырнадцатого транзисторов p-проводимости подключены к первому входу триггера, затворы десятого, двенадцатого и четырнадцатого транзисторов n-проводимости подключены к первому входу триггера, затворы девятого транзистора p-проводимости и девятого транзистора n-проводимости подключены ко второму входу триггера, затворы одиннадцатого и тринадцатого транзисторов p-проводимости и одиннадцатого и тринадцатого транзисторов n-проводимости подключены к третьему входу триггера, затворы восьмого транзистора p-проводимости и восьмого транзистора n-проводимости подключены к четвертому входу триггера, стоки девятого, десятого, одиннадцатого транзисторов p-проводимости подключены к истоку транзистора p-проводимости, сток которого подключен к стоку третьего транзистора p-проводимости, стоки двенадцатого и тринадцатого транзисторов p-проводимости подключены к истоку третьего транзистора p-проводимости, сток четырнадцатого транзистора p-проводимости подключен к истоку четвертого транзистора p-проводимости, стоки девятого, десятого, одиннадцатого транзисторов n-проводимости подключены к истоку транзистора n-проводимости, стоки двенадцатого и тринадцатого транзисторов n-проводимости подключены к истоку третьего транзистора n-проводимости, сток четырнадцатого транзистора n-проводимости подключен к истоку четвертого транзистора n-проводимости, сток седьмого транзистора p-проводимости и сток седьмого транзистора n-проводимости подключены к стоку второго транзистора p-проводимости и стоку пятнадцатого транзистора p-проводимости, который подключен к стоку пятнадцатого транзистора n-проводимости, исток седьмого транзистора p-проводимости подключен к стоку шестого транзистора p-проводимости, затвор седьмого транзистора p-проводимости подключен к третьему входу триггера, исток седьмого транзистора n-проводимости подключен к стоку шестого транзистора n-проводимости, затвор седьмого транзистора n-проводимости подключен к третьему входу триггера, затвор пятнадцатого транзистора p-проводимости и затвор пятнадцатого транзистора n-проводимости подключены к четвертому входу устройства, исток пятнадцатого транзистора p-проводимости подключен к стокам шестнадцатого, семнадцатого и восемнадцатого транзисторов p-проводимости, истоки которых подключены к стокам девятнадцатого, двадцатого и двадцать первого транзисторов p-проводимости соответственно, истоки девятнадцатого, двадцатого и двадцать первого транзисторов p-проводимости подключены ко входу подключения шины питания «Vcc», исток пятнадцатого транзистора n-проводимости подключен к стокам шестнадцатого, семнадцатого и восемнадцатого транзисторов n-проводимости, истоки которых подключены к стокам девятнадцатого, двадцатого и двадцать первого транзисторов n-проводимости соответственно, истоки девятнадцатого, двадцатого и двадцать первого транзисторов n-проводимости подключены ко входу подключения шины «Ноль вольт», затвор шестнадцатого транзистора p-проводимости и затвор шестнадцатого транзистора n-проводимости, семнадцатого транзистора p-проводимости и затвор семнадцатого транзистора n-проводимости подключены к третьему входу триггера, затвор восемнадцатого транзистора p-проводимости и затвор восемнадцатого транзистора n-проводимости, девятнадцатого транзистора p-проводимости и затвор девятнадцатого транзистора n-проводимости подключены ко второму входу триггера, затвор двадцатого транзистора p-проводимости и затвор двадцатого транзистора n-проводимости, двадцать первого транзистора p-проводимости и затвор двадцать первого транзистора n-проводимости подключены к первому входу триггера.

Признаки заявляемого технического решения, отличительные от прототипа - дополнительно введены 15 транзисторов p-проводимости и 15 транзисторов n-проводимости, третий и четвертый входы, причем истоки девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов n-проводимости подключены ко входу подключения шины «Ноль вольт», истоки девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов p-проводимости подключены ко входу подключения шины «Vcc», затворы десятого, двенадцатого и четырнадцатого транзисторов p-проводимости подключены к первому входу триггера, затворы десятого, двенадцатого и четырнадцатого транзисторов n-проводимости подключены к первому входу триггера, затворы девятого транзистора p-проводимости и девятого транзистора n-проводимости подключены ко второму входу триггера, затворы одиннадцатого и тринадцатого транзисторов p-проводимости и одиннадцатого и тринадцатого транзисторов n-проводимости подключены к третьему входу триггера, затворы восьмого транзистора p-проводимости и восьмого транзистора n-проводимости подключены к четвертому входу триггера, стоки девятого, десятого, одиннадцатого транзисторов p-проводимости подключены к истоку транзистора p-проводимости, сток которого подключен к стоку третьего транзистора p-проводимости, стоки двенадцатого и тринадцатого транзисторов p-проводимости подключены к истоку третьего транзистора p-проводимости, сток четырнадцатого транзистора p-проводимости подключен к истоку четвертого транзистора p-проводимости, стоки девятого, десятого, одиннадцатого транзисторов n-проводимости подключены к истоку транзистора n-проводимости, стоки двенадцатого и тринадцатого транзисторов n-проводимости подключены к истоку третьего транзистора n-проводимости, сток четырнадцатого транзистора n-проводимости подключен к истоку четвертого транзистора n-проводимости, сток седьмого транзистора p-проводимости и сток седьмого транзистора n-проводимости подключены к стоку второго транзистора p-проводимости и стоку пятнадцатого транзистора p-проводимости, который подключен к стоку пятнадцатого транзистора n-проводимости, исток седьмого транзистора p-проводимости подключен к стоку шестого транзистора p-проводимости, затвор седьмого транзистора p-проводимости подключен к третьему входу триггера, исток седьмого транзистора n-проводимости подключен к стоку шестого транзистора n-проводимости, затвор седьмого транзистора n-проводимости подключен к третьему входу триггера, затвор пятнадцатого транзистора p-проводимости и затвор пятнадцатого транзистора n-проводимости подключены к четвертому входу устройства, исток пятнадцатого транзистора p-проводимости подключен к стокам шестнадцатого, семнадцатого и восемнадцатого транзисторов p-проводимости, истоки которых подключены к стокам девятнадцатого, двадцатого и двадцать первого транзисторов p-проводимости соответственно, истоки девятнадцатого, двадцатого и двадцать первого транзисторов p-проводимости подключены ко входу подключения шины питания «Vcc», исток пятнадцатого транзистора n-проводимости подключен к стокам шестнадцатого, семнадцатого и восемнадцатого транзисторов n-проводимости, истоки которых подключены к стокам девятнадцатого, двадцатого и двадцать первого транзисторов n-проводимости соответственно, истоки девятнадцатого, двадцатого и двадцать первого транзисторов n-проводимости подключены ко входу подключения шины «Ноль вольт», затвор шестнадцатого транзистора p-проводимости и затвор шестнадцатого транзистора n-проводимости, семнадцатого транзистора p-проводимости и затвор семнадцатого транзистора n-проводимости подключены к третьему входу триггера, затвор восемнадцатого транзистора p-проводимости и затвор восемнадцатого транзистора n-проводимости, девятнадцатого транзистора p-проводимости и затвор девятнадцатого транзистора n-проводимости подключены ко второму входу триггера, затвор двадцатого транзистора p-проводимости и затвор двадцатого транзистора n-проводимости, двадцать первого транзистора p-проводимости и затвор двадцать первого транзистора n-проводимости подключены к первому входу триггера.

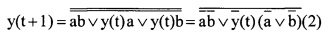

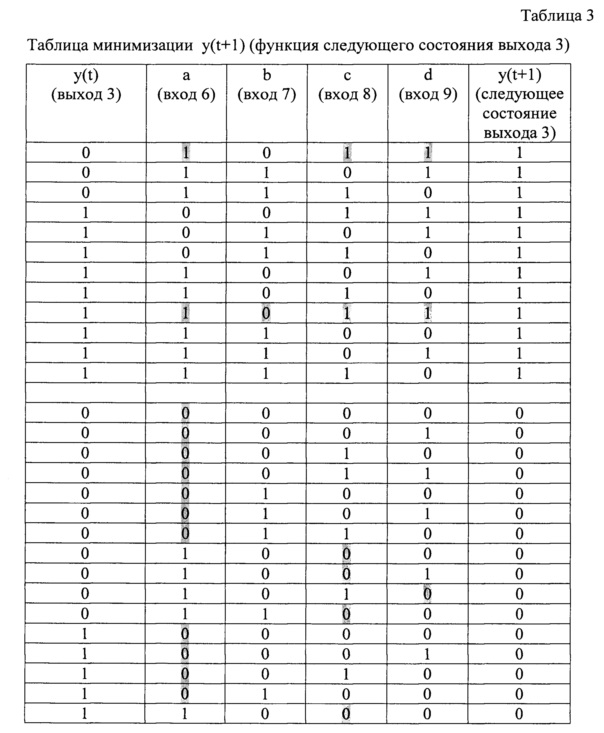

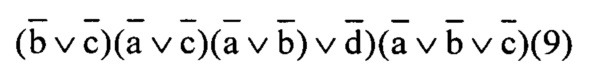

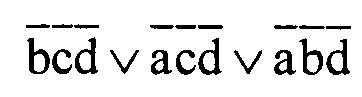

Отличительные признаки в сочетании с известными позволяют реализовать следующую таблицу переходов гистерезисного триггера, учитывающего возможность не завершения переходного процесса в одном из 4-х входных каналов - гистерезисного триггера с выбором 3 из 4-х переходных процессов по входам - табл. 2:

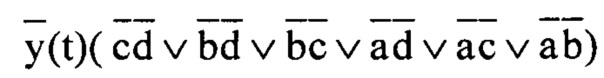

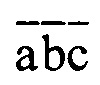

Гистерезисный триггер с выбором 3 из 4-х переходит в состояние 1 в случае не менее 3-х завершенных переходных процесса и остается в этом состоянии до тех пор, пока не менее чем три входа из входов 6,7,8,9 перейдут в состояние «0». Минимизация функции y(t+1) (функция следующего состояния выхода 3) по табл. 3:

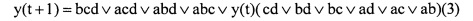

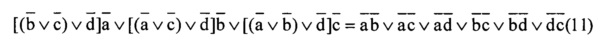

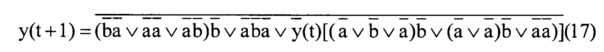

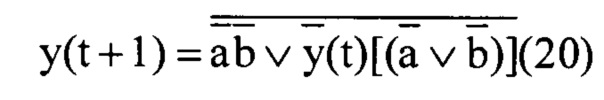

Соответствующая функция имеет вид:

,

,

где a - это вход 6, b это вход 7, с - это вход 8, d - это вход 9, y(t) - это выход 3, y(t+1) - это следующее состояние выхода 3.

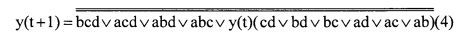

Выполняем двойную инверсию выражения (3):

.

.

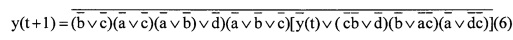

Раскроем нижнюю инверсию:

.

.

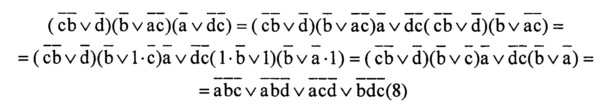

Преобразуем, используя дистрибутивный закон:

.

.

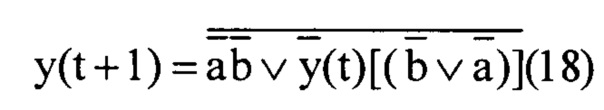

Преобразуем подвыражение

,

,

получим:

.

.

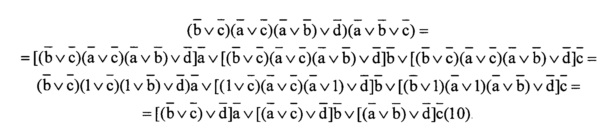

Преобразуем подвыражение

,

,

получим

Раскрывая скобки, получим:

.

.

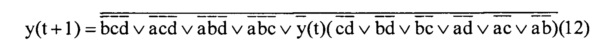

В итоге получаем:

.

.

Верхняя инверсия выражения (12) реализуется первым транзистором группы транзисторов p-проводимости и первым транзистором группы транзисторов n-проводимости. Подвыражение  выражения (12) реализуется вторым, третьим, четвертым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым транзисторами группы транзисторов p-проводимости и вторым, третьим, четвертым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым транзисторами группы транзисторов n-проводимости.

выражения (12) реализуется вторым, третьим, четвертым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым транзисторами группы транзисторов p-проводимости и вторым, третьим, четвертым, восьмым, девятым, десятым, одиннадцатым, двенадцатым, тринадцатым, четырнадцатым транзисторами группы транзисторов n-проводимости.

Подвыражение  выражения (12) реализуется пятым, шестым, седьмым транзисторами группы транзисторов p-проводимости; пятым, шестым, седьмым транзисторами группы транзисторов n-проводимости.

выражения (12) реализуется пятым, шестым, седьмым транзисторами группы транзисторов p-проводимости; пятым, шестым, седьмым транзисторами группы транзисторов n-проводимости.

Подвыражение  выражения (12) реализуется пятнадцатым, шестнадцатым, семнадцатым, восемнадцатым, девятнадцатым, двадцатым и двадцать первым транзисторами группы транзисторов p-проводимости; пятнадцатым, шестнадцатым, семнадцатым, восемнадцатым, девятнадцатым, двадцатым и двадцать первым транзисторами группы транзисторов n-проводимости.

выражения (12) реализуется пятнадцатым, шестнадцатым, семнадцатым, восемнадцатым, девятнадцатым, двадцатым и двадцать первым транзисторами группы транзисторов p-проводимости; пятнадцатым, шестнадцатым, семнадцатым, восемнадцатым, девятнадцатым, двадцатым и двадцать первым транзисторами группы транзисторов n-проводимости.

Таким образом, введение дополнительных транзисторов и связей позволяет обеспечить возможность использования гистерезисного триггера в резервированных самосинхронных схемах, учитывающих возможность отказа в одном из каналов, то есть переход в единичное состояние при единицах на трех и более входах и возврат в нулевое состояние при нулях на трех и более входах.

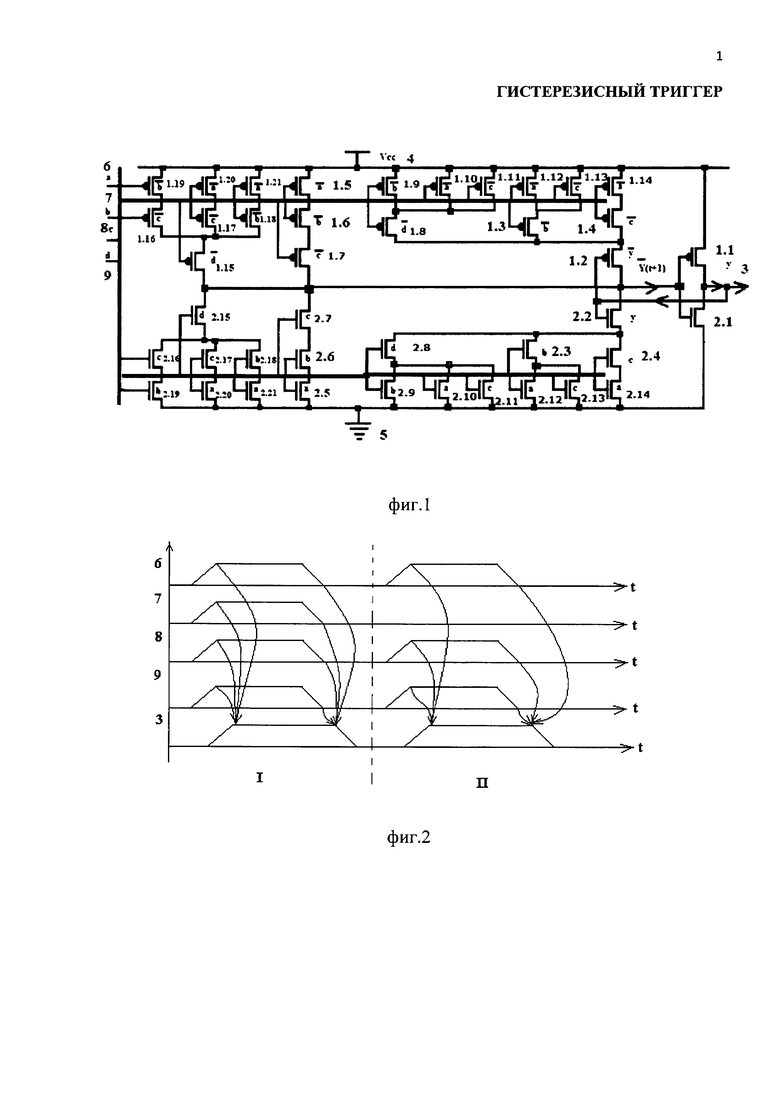

На фиг. 1 изображена схема электрическая принципиальная предлагаемого гистерезисного триггера.

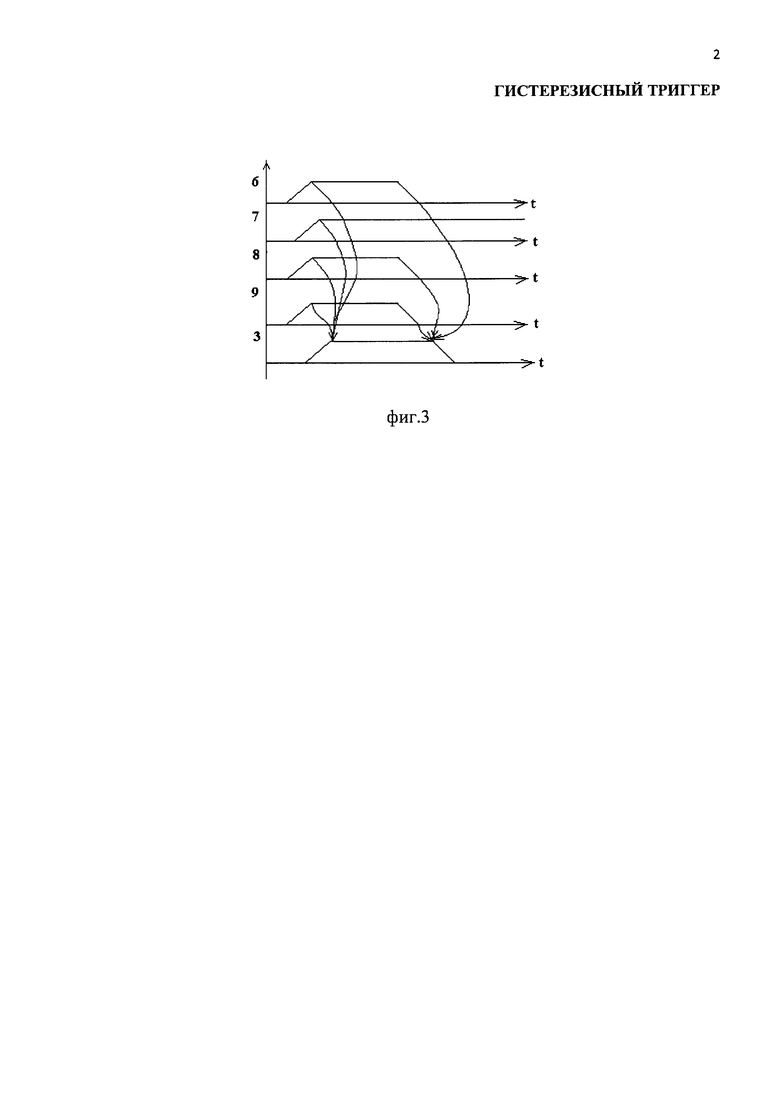

На фиг. 2 показана временная диаграмма работы устройства при резервировании самосинхронных схем в случае отсутствия отказов.

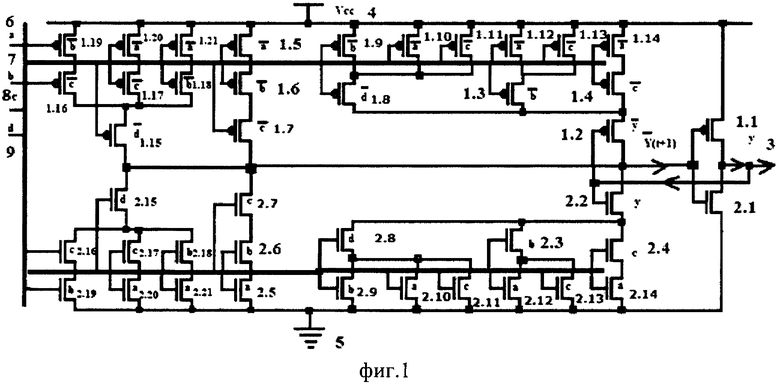

На фиг. 3 показана временная диаграмма работы устройства при резервировании самосинхронных схем в случае наличия отказа по одному их четырех входов.

Гистерезисный триггер (фиг. 1) содержит группу из шести транзисторов p-проводимости - первого 1.1, второго 1.2, третьего 1.3, четвертого 1.4, пятого 1.5, шестого 1.6, группу шести транзисторов n-проводимости - первого 2.1, второго 2.2, третьего 2.3, четвертого 2.4, пятого 2.5, шестого 2.6, выход триггера 3, вход подключения шины питания «Vcc» 4, вход подключения шины «Ноль вольт» 5, первый 6 и второй 7 входы триггера, третий 8 и четвертый 9 входы, 15 дополнительных транзисторов p-проводимости 1.7, 1.8, 1.9, 1.10, 1.11, 1.12, 1.13, 1.14, 1.15, 1.16, 1.17, 1.18, 1.19, 1.20, 1.21 и 15 дополнительных транзисторов n-проводимости 2.7, 2.8, 2.9, 2.10, 2.11, 2.12, 2.13, 2.14, 2.15, 2.16, 2.17, 2.18, 2.19, 2.20, 2.21.

Первый вход триггера 6 подключен к затворам пятого транзистора p-проводимости 1.5 и пятого транзистора n-проводимости 2.5. Второй вход триггера 7 подключен к затворам шестого транзистора p-проводимости 1.6 и шестого транзистора n-проводимости 2.6. Исток первого транзистора p-проводимости 1.1 и пятого транзистора p-проводимости 1.5 подключены ко входу подключения шины питания «Vcc» 4, сток пятого транзистора p-проводимости 1.5 подключен к истоку шестого транзистора p-проводимости 1.6. Исток первого транзистора n-проводимости 2.1 и пятого транзистора n-проводимости 2.5 подключены ко входу подключения шины «Ноль вольт» 5, сток пятого транзистора n-проводимости 2.5 подключен к истоку шестого транзистора n-проводимости 2.6. Сток первого транзистора p-проводимости 1.1 подключен к стоку первого транзистора n-проводимости 2.1 и к выходу триггера 3, выход 3 подключен к объединенным затворам второго транзистора p-проводимости 1.2 и второго транзистора n-проводимости 2.2, стоки которых объединены и подключены к затворам первого транзистора p-проводимости 1.1 и первого транзистора n-проводимости 2.1. Стоки третьего 1.3 и четвертого 1.4 транзисторов p-проводимости объединены и подключены к истоку второго 1.2 транзистора p-проводимости. Стоки третьего 2.3 и четвертого 2.4 транзисторов n-проводимости объединены и подключены к истоку второго транзистора n-проводимости 2.2.

Затворы третьего 1.3 транзистора p-проводимости и третьего транзистора n-проводимости 2.3 подключены ко второму входу триггера 7.

Истоки девятого 2.9, десятого 2.10, одиннадцатого 2.11, двенадцатого 2.12, тринадцатого 2.13 и четырнадцатого 2.14 транзисторов n-проводимости подключены ко входу подключения шины «Ноль вольт» 5.

Истоки девятого 1.9, десятого 1.10, одиннадцатого 1.11, двенадцатого 1.12, тринадцатого 1.13 и четырнадцатого 1.14 транзисторов p-проводимости подключены ко входу подключения шины «Vcc» 4.

Затворы десятого 1.10 двенадцатого 1.12 и четырнадцатого 1.14 транзисторов p-проводимости подключены к первому входу 6 триггера.

Затворы десятого 2.10, двенадцатого 2.12 и четырнадцатого 2.14 транзисторов n-проводимости подключены к первому входу 6 триггера.

Затворы девятого 1.9 транзистора p-проводимости и девятого 2.9 транзистора n-проводимости подключены ко второму входу 7 триггера.

Затворы одиннадцатого 1.11 и тринадцатого 1.13 транзисторов p-проводимости и одиннадцатого 2.11 и тринадцатого 2.13 транзисторов n-проводимости подключены к третьему входу 8 триггера.

Затворы восьмого 1.8 транзистора p-проводимости и восьмого 2.8 транзистора n-проводимости подключены к четвертому входу 9 триггера.

Стоки девятого 1.9, десятого 1.10, одиннадцатого 1.11 транзисторов p-проводимости подключены к истоку 1.8 транзистора p-проводимости, сток которого подключен к стоку третьего 1.3 транзистора p-проводимости.

Стоки двенадцатого 1.12 и тринадцатого 1.13 транзисторов p-проводимости подключены к истоку третьего 1.3 транзистора p-проводимости.

Сток четырнадцатого 1.14 транзистора p-проводимости подключен к истоку четвертого 1.4 транзистора p-проводимости.

Стоки девятого 2.9, десятого 2.10, одиннадцатого 2.11 транзисторов n-проводимости подключены к истоку 2.8 транзистора n-проводимости.

Стоки двенадцатого 2.12 и тринадцатого 2.13 транзисторов n-проводимости подключены к истоку третьего 2.3 транзистора n-проводимости.

Сток четырнадцатого 2.14 транзистора n-проводимости подключен к истоку четвертого 2.4 транзистора n-проводимости.

Сток седьмого 1.7 транзистора p-проводимости и сток седьмого 2.7 транзистора n-проводимости подключены к стоку второго 1.2 транзистора p-проводимости и стоку пятнадцатого 1.15 транзистора p-проводимости, который подключен к стоку пятнадцатого 2.15 транзистора n-проводимости.

Исток седьмого 1.7 транзистора p-проводимости подключен к стоку шестого 1.6 транзистора p-проводимости, затвор седьмого 1.7 транзистора p-проводимости подключен к третьему 8 входу триггера.

Исток седьмого 2.7 транзистора n-проводимости подключен к стоку шестого 2.6 транзистора n-проводимости, затвор седьмого 2.7 транзистора n-проводимости подключен к третьему 8 входу триггера.

Затвор пятнадцатого 1.15 транзистора p-проводимости и затвор пятнадцатого 2.15 транзистора n-проводимости подключены к четвертому входу устройства 9.

Исток пятнадцатого 1.15 транзистора p-проводимости подключен к стокам шестнадцатого 1.16, семнадцатого 1.17 и восемнадцатого 1.18 транзисторов p-проводимости, истоки которых подключены к стокам девятнадцатого 1.19, двадцатого 1.20 и двадцать первого 1.21 транзисторов p-проводимости соответственно, истоки девятнадцатого 1.19, двадцатого 1.20 и двадцать первого 1.21 транзисторов p-проводимости подключены ко входу подключения шины питания «Vcc» 4.

Исток пятнадцатого 2.15 транзистора n-проводимости подключен к стокам шестнадцатого 2.16, семнадцатого 2.17 и восемнадцатого 2.18 транзисторов n-проводимости, истоки которых подключены к стокам девятнадцатого 2.19, двадцатого 2.20 и двадцать первого 2.21 транзисторов n-проводимости соответственно, истоки девятнадцатого 2.19, двадцатого 2.20 и двадцать первого 2.21 транзисторов n-проводимости подключены ко входу подключения шины «Ноль вольт» 5.

Затвор шестнадцатого 1.16 транзистора p-проводимости и затвор шестнадцатого 2.16 транзистора n-проводимости, семнадцатого 1.17 транзистора p-проводимости и затвор семнадцатого 2.17 транзистора n-проводимости подключены к третьему входу триггера 8.

Затвор восемнадцатого 1.18 транзистора p-проводимости и затвор восемнадцатого 2.18 транзистора n-проводимости, девятнадцатого 1.19 транзистора p-проводимости и затвор девятнадцатого 2.19 транзистора n-проводимости подключены ко второму входу триггера 7.

Затвор двадцатого 1.20 транзистора p-проводимости и затвор двадцатого 2.20 транзистора n-проводимости, двадцать первого 1.21 транзистора p-проводимости и затвор двадцать первого 2.21 транзистора n-проводимости подключены к первому входу триггера 6.

Устройство работает следующим образом.

Работа устройства при резервировании самосинхронных схем.

В этом режиме устройство работает в соответствие с таблицей 2, где а - это вход 6, b это вход 7, с - это вход 8, d - это вход 9, y(t) - это выход 3, y(t+1) - это следующее состояние выхода 3. Гистерезисный триггер выполняет временную диаграмму - Фиг. 2. В исходном состоянии входы 6,7,8,9 обнулены, выход 3 гистерезисного триггера обнулен.

После завершения переходных процессов во внешней к предлагаемому устройству резервированной самосинхронной схеме, в случае отсутствия отказов, на все входы - 6,7,8,9 поступают логические единицы (Фиг. 2, участок I), поэтому выход 3 устанавливается в состояние логической единицы. Затем на входы 6,7,8,9 поступают логические нули и выход 3 устанавливается в состояние логического нуля.

В случае отказа, например, по входу 7 (Фиг. 2, участок II), когда он постоянно равен нулю, выход 3 все равно устанавливается в состояние логической единицы, то есть отказ одного канала не приведет к отказу всей внешней к предлагаемому устройству резервированной самосинхронной схемы, гистерезисный триггер работает по трем из четырех каналов, осуществляя выбор «3 из 4-х». Далее на входы 6,8,9 поступают логические нули, и выход 3 устанавливается в состояние логического нуля.

В случае отказа по входу 7, когда он после установления в состояние логической единицы так в ней и остается (Фиг.3), предлагаемый гистерезисный триггер в соответствие с табл.2 перейдет в состояние логического нуля (на выходе 3 устанавливается состояние логического нуля). В дальнейшем будет отрабатываться временная диаграмма Фиг. 3.

Таким образом, предлагаемый гистерезисный триггер обеспечивает работу внешней к предлагаемому устройству резервированной самосинхронной схемы в условиях отказа по одному их входов 6,7,8,9 (при отказе одного из четырех каналов внешней к предлагаемому устройству резервированной самосинхронной схемы).

Предлагаемое устройство не рассчитано на возникновение двух и более отказов.

Таким образом обеспечивается возможность использования предлагаемого гистерезисного триггера в резервированных самосинхронных схемах, учитывающих возможность отказа в одном из четырех каналов.

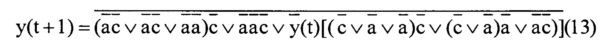

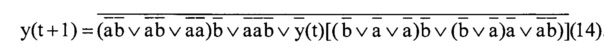

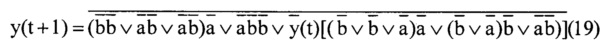

Работа устройства в нерезервированных самосинхронных схемах В этом режиме входы группируются попарно и тогда устройство работает аналогично прототипу. Докажем это. Пусть, например, a=b, c=d. Тогда функция (12) превращается в функцию:

.

.

Теперь обозначим с=b:

.

.

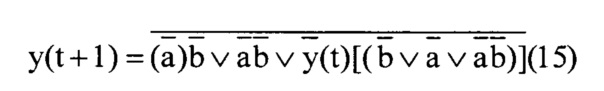

Преобразуя, получаем

.

.

Легко видеть, что в итоге (15) эквивалентна (2):

,

,

что и требовалось доказать. То есть, мы перешли к исходному гистерезисному триггеру, описываемому выражением (2).

Объединим попарно а=с, b=d:

,

,

получим

, что соответствует (16), (2).

, что соответствует (16), (2).

Объединим попарно a=d, b=с:

получим

, что соответствует (16), (18) (2).

, что соответствует (16), (18) (2).

Больше вариантов пар нет. Таким образом, предлагаемый гистерезисный триггер в этом режиме работает как прототип и ожидает завершения всех переходных процессов на входах. В этом режиме устройство работает в соответствие с таблицей 1, при этом входы а соответствуют объединенным парам входов (6,7), (6,8), (6,9), входы b соответствуют объединенным парам входов (8,9), (7,9), (7,8).

Временная диаграмма в этом случае соответствует Фиг. 2, (участок I).

То есть обеспечивается возможность использования в нерезервированных самосинхронных схемах, не учитывающих возможность отказа в одном из каналов (в данном случае - в двух).

Таким образом, достижение технического результата изобретения подтверждается.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

| СУММАТОР | 2008 |

|

RU2380739C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ КМОП СУММАТОР | 2011 |

|

RU2454703C1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| ТОКОВЫЙ ПОРОГОВЫЙ ЭЛЕМЕНТ ЛЕВОГО ЦИКЛИЧЕСКОГО СДВИГА | 2021 |

|

RU2776031C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ЧЕТЫРЁХВХОДОВОЙ КМОП ЛОГИЧЕСКИЙ ВЕНТИЛЬ ИСКЛЮЧАЮЩЕЕ-ИЛИ/ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ | 2022 |

|

RU2784457C1 |

| ТРОИЧНЫЙ ИНВЕРТОР НА КМОП ТРАНЗИСТОРАХ | 2008 |

|

RU2373639C1 |

| ПРЕОБРАЗОВАТЕЛЬ УРОВНЯ НАПРЯЖЕНИЯ | 2017 |

|

RU2667798C1 |

| СУММАТОР | 2011 |

|

RU2455680C1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано при построении отказоустойчивых самосинхронных схем. Технический результат изобретения заключается в обеспечении возможности использования гистерезисного триггера в резервированных самосинхронных схемах, учитывающих возможность отказа в одном из каналов. Гистерезисный триггер содержит группу из 6 транзисторов p-проводимости и группу из 6 транзисторов n-проводимости и дополнительно 15 транзисторов p-проводимости и 15 транзисторов n-проводимости, а также связи между ними. 3 ил., 3 табл.

Гистерезисный триггер, содержащий группу из шести транзисторов р-проводимости, группу из шести транзисторов n-проводимости, выход триггера, вход подключения шины питания «Vcc», вход подключения шины «Ноль вольт», первый и второй входы триггера, причем первый вход триггера подключен к затворам пятого транзистора р-проводимости и пятого транзистора n-проводимости, второй вход триггера подключен к затворам шестого транзистора р-проводимости и шестого транзистора n-проводимости, истоки первого транзистора р-проводимости и пятого транзистора р-проводимости подключены к входу подключения шины питания «Vcc», сток пятого транзистора р-проводимости подключен к истоку шестого транзистора р-проводимости, истоки первого транзистора n-проводимости и пятого транзистора n-проводимости подключены к входу подключения шины «Ноль вольт», сток пятого транзистора n-проводимости подключен к истоку шестого транзистора n-проводимости, сток первого транзистора р-проводимости подключен к стоку первого транзистора n-проводимости и к выходу триггера, который подключен к объединенным затворам второго транзистора р-проводимости и второго транзистора n-проводимости, стоки которых объединены и подключены к затворам первого транзистора р-проводимости и первого транзистора n-проводимости, стоки третьего и четвертого транзисторов р-проводимости объединены и подключены к истоку второго транзистора р-проводимости, стоки третьего и четвертого транзисторов n-проводимости объединены и подключены к истоку второго транзистора n-проводимости, затворы третьего транзистора р-проводимости и третьего транзистора n-проводимости подключены ко второму входу триггера, отличающийся тем, что в него дополнительно введены пятнадцать транзисторов р-проводимости и пятнадцать транзисторов n-проводимости, третий и четвертый входы, причем истоки девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого

транзисторов n-проводимости подключены к входу подключения шины «Ноль вольт», истоки девятого, десятого, одиннадцатого, двенадцатого, тринадцатого и четырнадцатого транзисторов р-проводимости подключены ко входу подключения шины «Vcc», затворы десятого, двенадцатого и четырнадцатого транзисторов р-проводимости подключены к первому входу триггера, затворы десятого, двенадцатого и четырнадцатого транзисторов n-проводимости подключены к первому входу триггера, затворы девятого транзистора р-проводимости и девятого транзистора n-проводимости подключены ко второму входу триггера, затворы одиннадцатого и тринадцатого транзисторов р-проводимости и одиннадцатого и тринадцатого транзисторов n-проводимости подключены к третьему входу триггера, затворы восьмого транзистора р-проводимости и восьмого транзистора n-проводимости подключены к четвертому входу триггера, стоки девятого, десятого, одиннадцатого транзисторов р-проводимости подключены к истоку транзистора р-проводимости, сток которого подключен к стоку третьего транзистора р-проводимости, стоки двенадцатого и тринадцатого транзисторов р-проводимости подключены к истоку третьего транзистора р-проводимости, сток четырнадцатого транзистора р-проводимости подключен к истоку четвертого транзистора р-проводимости, стоки девятого, десятого, одиннадцатого транзисторов n-проводимости подключены к истоку транзистора n-проводимости, стоки двенадцатого и тринадцатого транзисторов n-проводимости подключены к истоку третьего транзистора n-проводимости, сток четырнадцатого транзистора n-проводимости подключен к истоку четвертого транзистора n-проводимости, сток седьмого транзистора р-проводимости и сток седьмого транзистора n-проводимости подключены к стоку второго транзистора р-проводимости и стоку пятнадцатого транзистора р-проводимости, который подключен к стоку пятнадцатого транзистора n-проводимости, исток седьмого транзистора р-проводимости подключен к стоку шестого транзистора р-проводимости,

затвор седьмого транзистора р-проводимости подключен к третьему входу триггера, исток седьмого транзистора n-проводимости подключен к стоку шестого транзистора n-проводимости, затвор седьмого транзистора n-проводимости подключен к третьему входу триггера, затвор пятнадцатого транзистора р-проводимости и затвор пятнадцатого транзистора n-проводимости подключены к четвертому входу устройства, исток пятнадцатого транзистора р-проводимости подключен к стокам шестнадцатого, семнадцатого и восемнадцатого транзисторов р-проводимости, истоки которых подключены к стокам девятнадцатого, двадцатого и двадцать первого транзисторов р-проводимости соответственно, истоки девятнадцатого, двадцатого и двадцать первого транзисторов р-проводимости подключены к входу подключения шины питания «Vcc», исток пятнадцатого транзистора n-проводимости подключен к стокам шестнадцатого, семнадцатого и восемнадцатого транзисторов n-проводимости, истоки которых подключены к стокам девятнадцатого, двадцатого и двадцать первого транзисторов n-проводимости соответственно, истоки девятнадцатого, двадцатого и двадцать первого транзисторов n-проводимости подключены к входу подключения шины «Ноль вольт», затвор шестнадцатого транзистора р-проводимости и затвор шестнадцатого транзистора n-проводимости, семнадцатого транзистора р-проводимости и затвор семнадцатого транзистора n-проводимости подключены к третьему входу триггера, затвор восемнадцатого транзистора р-проводимости и затвор восемнадцатого транзистора n-проводимости, девятнадцатого транзистора р-проводимости и затвор девятнадцатого транзистора n-проводимости подключены ко второму входу триггера, затвор двадцатого транзистора р-проводимости и затвор двадцатого транзистора n-проводимости, двадцать первого транзистора р-проводимости и затвор двадцать первого транзистора n-проводимости подключены к первому входу триггера.

| Ю.А | |||

| СТЕПЧЕНКОВ и др., Библиотека элементов для проектирования самосинхронных полузаказных микросхем серий 5503/5507 и 5508/5509, Москва, ИПИ РАН, 2008 | |||

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| МИКРОСХЕМА С МИКРОЭЛЕКТРОМЕХАНИЧЕСКОЙ ЗАЩИТОЙ ОТ ЭЛЕКТРИЧЕСКИХ И/ИЛИ ТЕПЛОВЫХ ПЕРЕГРУЗОК | 2011 |

|

RU2466496C1 |

| УСТРОЙСТВО ВОССТАНОВЛЕНИЯ РАБОТОСПОСОБНОСТИ РЕЗЕРВИРОВАННОЙ СИСТЕМЫ С ПОМОЩЬЮ МАЖОРИТАРНЫХ ЭЛЕМЕНТОВ | 2014 |

|

RU2563798C1 |

Авторы

Даты

2017-08-15—Публикация

2016-06-08—Подача