ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к устройствам обработки данных, и может быть использовано для построения функциональных узлов для анализа свойств генераторов псевдослучайных последовательностей двоичных чисел, фильтрации событий, обработки сигналов, изображений и результатов физических экспериментов.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известно устройство последовательного типа для детектирования групп нулевых и единичных бит и определение их количества (RU №2680759 С1, МПК G06F 7/74, заявлено 16.02.2018, опубликовано 26.02.2019, Бюл. №6) в котором для входных последовательностей данных размерностью N, поступающих на внешний вход данных DI, на соответствующих внешних выходах групп устройства формируются двоичные коды, соответствующие количеству групп QG, количеству нулевых бит QZ, количеству единичных бит QU, разности между количеством единичных и нулевых бит QZU, количество бит по группам QO с выходного буфера ОВ 11, при этом в четных адресах, начиная с нулевого адреса, указывается количество нулевых бит в группах, а в нечетных адресах, начиная с первого адреса, указывается количество единичных бит в группах, а также формируются флаг готовности FE, флаг «нулей больше единиц» F01, флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

Недостатками данного устройства является определение групп нулевых и единичных бит произвольной размерности, а не заданной размерности, и отсутствие средств для выявления максимальных групп.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, устройство для детектирования групп бит (RU №2780985, МПК G06F 7/74, G06F 7/02, заявлено 01.12.2021, опубликовано 04.10.2022, Бюл. №28), содержащее внешний m разрядный вход данных ID, внешний m разрядный вход заданного шаблона IG, группу внешних выходов данных QB, первый RS-триггер пуска-останова TSS 1, второй D-триггер TR2 задержки 2, счетчик CTG групп 3, выходной буфер ОВ 4, первый R1 регистр данных 5, второй R2 регистр данных 6, группу из m компараторов 71, 72, …, 7m, группу из (m-1) элементов И 82, 83, …, 8m, элемент ИЛИ 9 и элемент И 10, а также введены внешние входы асинхронной установки в нулевое состояние CLR, пуска устройства START, остановки устройства STOP и тактовый С, внутренняя 2m-разрядная шина данных BD, внутренняя m-разрядная шина данных буфера IOB, внутренний флаг совпадения FE, внешняя шина управления обменом ЕО, внешние флаг «Буфер заполнен» FF и флаг «Буфер пуст» FZ.

Недостатком данного устройства является выявление на каждом такте групп бит соответствующих только одному заданному шаблону.

ЗАДАЧА ИЗОБРЕТЕНИЯ

Задачей изобретения является разработка аппаратных средств групповой структуры для исследования свойств генераторов псевдослучайных последовательностей двоичных чисел, а также для обработки сигналов и результатов физических экспериментов.

При анализе генераторов псевдослучайных последовательностей двоичных чисел устройство предназначено для выявления групп (рядов) подряд идущих единичных бит и самой длинной последовательности из единиц в блоках входных данных заданной размерности.

При обработке результатов физических экспериментов устройство предназначено для выявления событий заданной размерности, определение их количества и максимальных событий.

Техническим результатом изобретения является расширение арсенала средств того же назначения, в части возможности детектирования групп единичных бит, определение количества заданных групп и выявления максимальных групп в двоичных блоках, а также подсчет единичных групп во входной последовательности.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

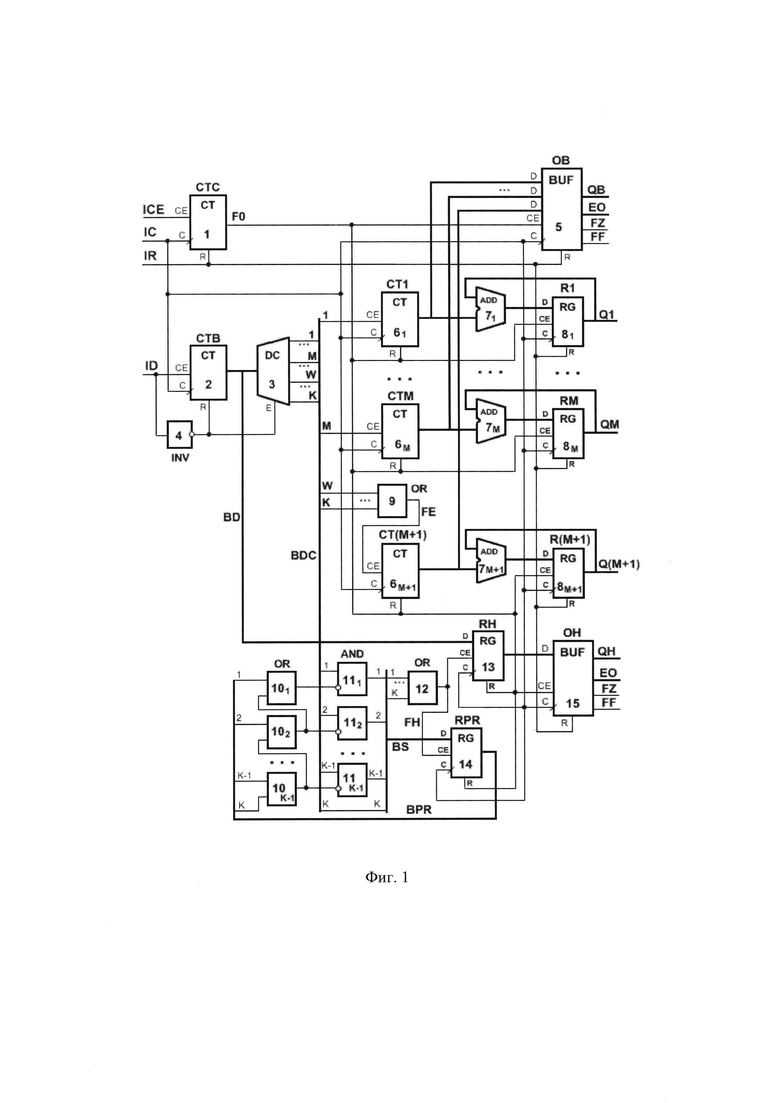

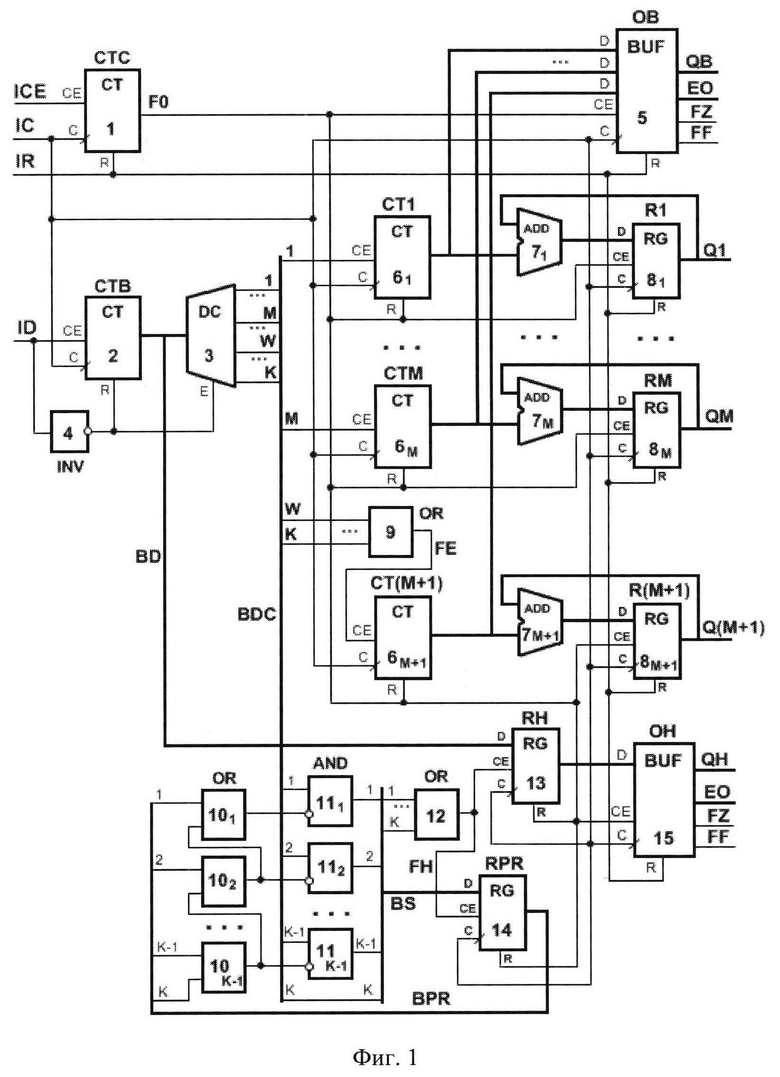

Указанный технический результат при осуществлении изобретения достигается тем, что устройство для детектирования групп единичных бит в блоках двоичной последовательности содержит внешний вход данных ID последовательного ввода К-разрядных блоков данных ВВ из входной N-разрядной бинарной последовательности данных, группу внешних выходов групп ОВ, группу внешних выходов максимальных групп QH, группу внешних шин количества единичных групп Q1, Q2, …, Q(M+1) (где М - разрядности детектируемых единичных групп, 1≤М≤К), счетчик тактов СТС 1, счетчик единичных бит СТВ 2, дешифратор 3, инвертор 4, выходной буфер групп ОВ 5, группу из (М+1) счетчиков единичных групп 61, 62, …, 6(M+1), группу из (М+1) сумматоров 71, 72, …, 7(M+1), группу из (М+1) регистров 81, 82, …, 8(M+1), первый элемент ИЛИ 9, группу из (К-1) элементов ИЛИ 101, 102, …, 10(К-1), группу из (К-1) элементов И с инверсным входом 111, 112, …, 11(К-1), второй элемент ИЛИ 12, регистр максимальной группы RH 13, регистр приоритета RPR 14 и выходной буфер максимальных групп ОН 15,

а также введены внешние входы тактовый IC, синхронной установки в нулевое состояние IR и разрешения работы ICE, внутренние шины количества единичных бит в группе BD, унитарного кода BDC, старшей группы BS и приоритета BPR, внутренние флаги начала блока F0, разрешения счета FE и максимума FH, внешние шины управления обменом ЕО, внешние флаги «Буфер заполнен» FF и «Буфер пуст» FZ,

причем внешний вход синхронной установки в нулевое состояние IR соединен с соответствующими входами синхронной установки в нулевое состояние R счетчика тактов СТС 1, выходного буфера групп ОВ 5, регистров 81, 82, …, 8(M+1) и выходного буфера максимальных групп ОН 15, а внешний вход разрешения работы ICE соединен с входом разрешения работы СЕ счетчика тактов СТС 1,

внешний тактовый вход устройства IC соединен с входами синхронизации С счетчика тактов СТС 1, счетчика единичных бит СТВ 2, выходного буфера групп ОВ 5, счетчиков единичных групп 61, 62, …, 6(M+1), регистров 81, 82, …, 8(M+1), регистра максимальной группы RH 13, регистра приоритета RPR 14 и выходного буфера максимальных групп ОН 15,

причем выход счетчика тактов СТС 1 является внутренним флагом начала блока F0, который соединен с входами синхронной установки в нулевое состояние R счетчиков единичных групп 61, 62, …, 6(M+1), регистра максимальной группы RH 13 и регистра приоритета RPR 14, а также соединен с входами разрешения работы СЕ выходного буфера групп ОВ 5, регистров 81, 82, …, 8(M+1) и выходного буфера максимальных групп ОН 15,

внешний вход данных ID соединен с входом инвертора 4 и с входом разрешения работы СЕ счетчика единичных бит СТВ 2, выходы которого являются разрядами внутренней шины количества единичных бит в группе BD, которая подключена к адресным входам дешифратора 3 и к информационным D-входам регистра максимальной группы RH 13, а выход инвертора 3 соединен с входом синхронной установки в нулевое состояние R счетчика единичных бит СТВ 2 и входом разрешения работы Е дешифратора 3, выходы которого являются К разрядами внутренней шина унитарного кода BDC,

причем первые М разрядов внутренней шины унитарного кода BDC, начиная с первого до М-го разряда, соединены с входами разрешения работы СЕ соответствующих одноименных М счетчиков единичных групп 61, 62, …, 6M, а также первые (К-1) разрядов внутренней шины унитарного кода BDC, начиная с первого до (К-1)-го разряда, соединены с первыми прямыми входами соответствующих одноименных элементов И с инверсным входом группы 111, 112, …, 11(К-1), кроме того разряды внутренней шины унитарного кода BDC, начиная с W-го разряда до К-го разряда (где W разрядность детектируемых единичных групп, 1≤W≤К), соединены с входами первого элемента ИЛИ 9, выход которого является внутренним флагом разрешения счета FE и соединен с входом разрешения работы СЕ (М+1)-го счетчика единичных групп 6(М+1),

причем выходы элементов И с инверсным входом группы 111, 112, …, 11(К-1) являются первыми (К-1) разрядами внутренней шины старшей группы BS, у которой К-й разряд соединен с К-м разрядом внутренней шины унитарного кода BDC, а все К разряды внутренней шины старшей группы BS соединены с группой информационных D-входов регистра приоритета RPR 14 и соединены с соответствующими входами второго элемента ИЛИ 12, выход которого является внутренним флагом максимума FH и соединен с входами разрешения работы СЕ регистра максимальной группы RH 13 и регистра приоритета RPR 14, выходы которого являются разрядами внутренней шины приоритета BPR, у которой первые (К-1) разряды соединены с первыми входами одноименных (К-1) элементов ИЛИ из группы 101, 102, …, 10(К-1), выходы которых соединены с инверсными входами одноименных элементов И с инверсным входом из группы 111, 112, …, 11(К-1),

причем вторые входы первых (К-2) элементов ИЛИ группы 101, 102, …, 10(К-2), начиная с первого до (К-2)-го элементов, соединены с выходами соответствующих последующих (К-2) элементов ИЛИ группы 102, 103, …, 10(К-1), начиная со второго до (К-1)-го элементов, а К-й разряд внутренней шины приоритета BPR соединен со вторым входом (К-1)-го элемента 10(К-1),

кроме того, выходы счетчиков единичных групп 61, 62, …, 6(М+1) соединены с соответствующими группами информационных D-входов выходного буфера групп ОВ 5, а также соединены со вторыми группами входов соответствующих (М+1) сумматоров 71, 72, …, 7(М+1), у которых первые группы входов соединены с выходами одноименных (М+1) регистров 81, 82, …, 8(М+1), выходы которых также являются соответствующими одноименными внешними шинами Q1, Q2, Q(M+1) количества единичных групп,

кроме того, выходной буфер групп ОВ 5 также подключен к внешней соответствующей шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 5 являются группой внешних выходов групп QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

причем группа выходов выходной регистра максимальной группы RH 13 соединена с группой информационных D-входов буфера максимальных групп ОН 15, выход которого подключен к внешней соответствующей шине ЕО управления обменом, а соответствующие выходы выходного буфера максимальных групп ОН 15 являются группой внешних выходов максимальных групп QH и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

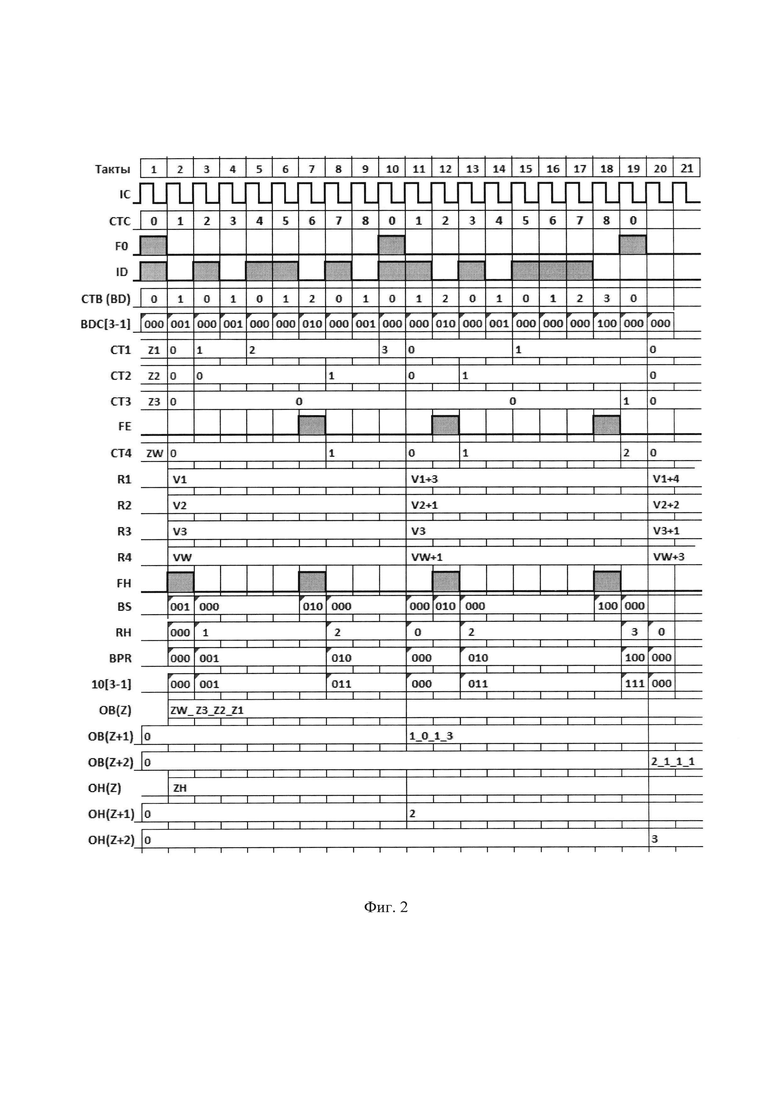

На фиг. 1 представлена схема предлагаемого устройства. На фиг. 2 приведена временная диаграмма работы предлагаемого устройства для детектирования групп, содержащих от 1 до М=3 единичных бит и W≥2 единичных бит, в двух последовательных блоках входных данных BB(Z+1) и BB(Z+2), содержащих по К=8 разрядов.

На фиг. 1-2 и в тексте приняты следующие обозначения:

ADD - сумматор,

AND - элемент И,

ВВ1, ВВ2, …, BBL - блоки входных данных, содержащие по К разрядов,

BD - внутренняя шина количества единичных бит в группе,

BDC - внутренняя K-разрядная шина унитарного кода,

BS - внутренняя K-разрядная шина старшей группы,

BPR - внутренняя K-разрядная шина приоритета,

BUF - буфер с дисциплиной обслуживания FIFO,

С - тактовый вход,

СЕ - вход разрешения работы,

СТ - счетчик,

СТВ - счетчик единичных бит,

СТС - счетчик тактов,

СТ1, СТ2, …, СТ(М+1) - группа из (М+1) счетчиков единичных групп,

D - информационные входы,

DC - дешифратор,

Е - вход разрешения работы дешифратора,

ЕО - внешняя шина управления обменом,

F0 - внутренний флаг начала блока,

FE - внутренний флаг разрешения счета,

FH - внутренний флаг максимума,

FF - внешний флаг «Буфер заполнен»,

FZ - внешний флаг «Буфер пуст»,

IC - внешний тактовый вход,

ICE - внешний вход разрешения работы,

ID - внешний вход данных,

IR - внешний вход синхронной установки в нулевое состояние,

INV - инвертор,

К - разрядность входных блоков данных,

L - количество входных блоков ВВ, где L=N/K,

N - размерность (длина) входной последовательности данных,

М - разрядность детектируемых единичных групп, где 1≤М≤К,

OR - элемент ИЛИ,

OB - выходной буфер групп,

ОН - выходной буфер максимальных групп,

QB - группа внешних выходов групп,

QH - группа внешних выходов максимальных групп,

Q1, Q2, …, Q(M+1) - группа внешних шин количества единичных групп,

R - вход синхронной установки в нулевое состояние,

R1, R2, …, R(M+1) - группа из (М+1) регистров единичных групп,

RG - регистр,

RH - регистр максимальной группы,

RPR - регистр приоритета,

W - разрядность детектируемых единичных групп, где 1≤W≤К,

1 - счетчик тактов СТС,

2 - счетчик единичных бит СТВ

3 - дешифратор,

4 - инвертор (INV),

5 - выходной буфер групп ОВ,

61, 62, …, 6(M+1) - группа из (М+1) счетчиков единичных групп,

71, 72, …, 7(М+1) - группа из (М+1) сумматоров (ADD),

81, 82, …, 8(M+1) - группа из (М+1) регистров,

9 - первый элемент ИЛИ (OR),

101, 102, …, 10(К-1) - группа из (К-1) элементов ИЛИ (OR),

111, 112, …, 11(К-1) - группа из (К-1) элементов И с инверсным входом (AND),

12 - второй элемент ИЛИ (OR),

13 - регистр максимальной группы RH,

14 - регистр приоритета RPR,

15 - выходной буфер максимальных групп ОН.

Предлагаемое устройство содержит вход данных ID последовательного ввода К-разрядных блоков данных ВВ из входной N-разрядной бинарной последовательности данных, группу внешних выходов групп QB, группу внешних выходов максимальных групп QH, группу внешних шин количества единичных групп Q1, Q2, …, Q(M+1) (где М - разрядности детектируемых единичных групп, 1≤М≤К), счетчик тактов СТС 1, счетчик единичных бит СТВ 2, дешифратор 3, инвертор 4, выходной буфер групп ОВ 5, группу из (М+1) счетчиков единичных групп 61, 62, …, 6(M+1), группу из (М+1) сумматоров 71, 72, …, 7(M+1), группу из (М+1) регистров 81, 82, …, 8(M+1), первый элемент ИЛИ 9, группу из (К-1) элементов ИЛИ 101, 102, …, 10(К-1), группу из (К-1) элементов И с инверсным входом 111, 112, …, 11(К-1), второй элемент ИЛИ 12, регистр максимальной группы RH 13, регистр приоритета RPR 14 и выходной буфер максимальных групп ОН 15.

В предлагаемое устройство также введены внешние входы тактовый IC, синхронной установки в нулевое состояние IR и разрешения работы ICE, внутренние шины количества единичных бит в группе BD, унитарного кода BDC, старшей группы BS и приоритета BPR, внутренние флаги начала блока F0, разрешения счета FE и максимума FH, внешние шины управления обменом ЕО, внешние флаги «Буфер заполнен» FF и «Буфер пуст» FZ.

Внешний вход синхронной установки в нулевое состояние IR соединен с соответствующими входами синхронной установки в нулевое состояние R счетчика тактов СТС 1, выходного буфера групп ОВ 5, регистров 81, 82, …, 8(M+1) и выходного буфера максимальных групп ОН 15, а внешний вход разрешения работы ICE соединен с входом разрешения работы СЕ счетчика тактов СТС 1.

Внешний тактовый вход устройства IC соединен с входами синхронизации С счетчика тактов СТС 1, счетчика единичных бит СТВ 2, выходного буфера групп ОВ 5, счетчиков единичных групп 61, 62, …, 6(M+1), регистров 81, 82, …, 8(M+1), регистра максимальной группы RH 13, регистра приоритета RPR 14 и выходного буфера максимальных групп ОН 15.

Выход счетчика тактов СТС 1 является внутренним флагом начала блока F0, который соединен с входами синхронной установки в нулевое состояние R счетчиков единичных групп 61, 62, 6(M+1), регистра максимальной группы RH 13 и регистра приоритета RPR 14, а также соединен с входами разрешения работы СЕ выходного буфера групп ОВ 5, регистров 81, 82, …, 8(M+1) и выходного буфера максимальных групп ОН 15.

Внешний вход данных ID соединен с входом инвертора 4 и с входом разрешения работы СЕ счетчика единичных бит СТВ 2, выходы которого являются разрядами внутренней шины количества единичных бит в группе BD, которая подключена к адресным входам дешифратора 3 и к информационным D-входам регистра максимальной группы RH 13. Выход инвертора 3 соединен с входом синхронной установки в нулевое состояние R счетчика единичных бит СТВ 2 и входом разрешения работы Е дешифратора 3, выходы которого являются К разрядами внутренней шина унитарного кода BDC.

Причем первые М разрядов внутренней шины унитарного кода BDC, начиная с первого до М-го разряда, соединены с входами разрешения работы СЕ соответствующих одноименных М счетчиков единичных групп 61, 62, …, 6M, а также первые (К-1) разрядов внутренней шины унитарного кода BDC, начиная с первого до (К-1)-го разряда, соединены с первыми прямыми входами соответствующих одноименных элементов И с инверсным входом группы 111, 112, …, 11(К-1), Кроме того, разряды внутренней шины унитарного кода BDC, начиная с W-го разряда до К-го разряда (где W разрядность детектируемых единичных групп, 1≤W≤К), соединены с входами первого элемента ИЛИ 9, выход которого является внутренним флагом разрешения счета FE и соединен с входом разрешения работы СЕ (М+1)-го счетчика единичных групп 6(М+1).

Выходы элементов И с инверсным входом группы 111, 112, …, 11(К-1) являются первыми (К-1) разрядами внутренней шины старшей группы BS, у которой К-й разряд соединен с К-м разрядом внутренней шины унитарного кода BDC, а все К разряды внутренней шины старшей группы BS соединены с группой информационных D-входов регистра приоритета RPR 14 и соединены с соответствующими входами второго элемента ИЛИ 12, выход которого является внутренним флагом максимума FH и соединен с входами разрешения работы СЕ регистра максимальной группы RH 13 и регистра приоритета RPR 14, выходы которого являются разрядами внутренней шины приоритета BPR, у которой первые (К-1) разряды соединены с первыми входами одноименных (К-1) элементов ИЛИ из группы 101, 102, …, 10(К-1), выходы которых соединены с инверсными входами одноименных элементов И с инверсным входом из группы 111, 112, …, 11(К-1).

Вторые входы первых (К-2) элементов ИЛИ группы 101, 102, …, 10(К-2), начиная с первого до (К-2)-го элементов, соединены с выходами соответствующих последующих (К-2) элементов ИЛИ группы 102, 103, …, 10(К-1), начиная со второго до (K-1)-го элементов, а К-й разряд внутренней шины приоритета BPR соединен со вторым входом (K-1)-го элемента 10(К-1).

Выходы счетчиков единичных групп 61, 62, …, 6(М+1) соединены с соответствующими группами информационных D-входов выходного буфера групп ОВ 5, а также соединены со вторыми группами входов соответствующих (М+1) сумматоров 71, 72, …, 7(М+1), у которых первые группы входов соединены с выходами одноименных (М+1) регистров 81, 82, …, 8(М+1), выходы которых также являются соответствующими одноименными внешними шинами Q1, Q2, …, Q(M+1) количества единичных групп.

Выходной буфер групп ОВ 5 также подключен к внешней соответствующей шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 5 являются группой внешних выходов групп QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

Группа выходов выходной регистра максимальной группы RH 13 соединена с группой информационных D-входов буфера максимальных групп ОН 15, выход которого подключен к внешней соответствующей шине ЕО управления обменом, а соответствующие выходы выходного буфера максимальных групп ОН 15 являются группой внешних выходов максимальных групп QH и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Принцип работы предлагаемого устройства состоит в следующем.

Предлагаемое устройство позволяет детектировать группы, содержащие от 1 до М единичных бит (где М задается из диапазона 1≤М≤К) и содержащие W и более W единичных бит (где W задается из диапазона 1≤W≤К), в К-разрядных блоках ВВ во входной N-разрядной бинарной последовательности. При этом W разрядность единичных групп, для которых осуществляется общий подсчет всех групп ≥W разрядности, может быть меньше М разрядности отдельных единичных групп, т.е. единичные группы могут учитываться дважды - в отдельной и общей группах.

Входное N разрядное двоичное число без знака разбивается на L=N/К блоков ВВ по К разрядов в каждом блоке. Разряды каждого блока ВВ1, ВВ2, …, BBL входных данных последовательно в каждом такте IC поступают на внешний вход данных ID, а между блоками передается один разделительный нулевой бит.

На каждом такте осуществляется поиск (выявление, детектирование, анализ) с входа данных ID единичных групп (рядов подряд идущих единичных значений). При этом на счетчике СТВ 2 осуществляется подсчет единичных бит в текущей группе с входа данных ID, выходы которого являются разрядами внутренней шины количества единичных бит в группе BD. При вводе нулевого значения разряда на вход данных ID определяется завершение текущей единичной группы, поэтому далее код со счетчика единичных бит СТС 2 на дешифраторе DC 3 преобразуется в унитарный код «1 из К» и передается на внутреннюю шину унитарного кода BDC, так как при нулевом значении на входе данных ID=0 на входе разрешения Е через инвертор INV 3 установлено единичное значение. Также по следующему такту IC в нулевое состояние устанавливается счетчик единичных бит СТС 2, так как на входе синхронной установки R установлено единичное значение.

Единичное значение в одном из разрядов внутренней шины унитарного кода BDC, которое соответствует количеству (сумме) единиц в текущей группе, поступает на вход разрешения работы СЕ соответствующего счетчика единичных групп СТ1, СТ2, …, СТ(М+1) из группы 61, 62, …, 6(M+1), в котором значение увеличивается на единицу (+1). При этом при выявлении ≥W единичных бит в текущей группе подсчет групп осуществляется на счетчике СТ(М+1) 6(M+1), так как соответствующие разряды с W по К внутренней шины унитарного кода BDC поступают на входы первого элемента ИЛИ 9, выход которого является внутренним флагом флаг разрешения счета FE, который далее передается на вход разрешения работы СЕ счетчика СТ(М+1) 6(M+1).

Одновременно унитарный код «1 из К» с внутренней шины BDC передается на прямые входы элементов И с инверсным входом из группы 111, 112, …, 11(К-1). При этом на основании единичных значений с регистра приоритета RPR 14, которые через внутреннюю шину приоритета BPR поступают на группу из элементов ИЛИ 101, 102, …, 10(К-1) и далее по цепочке элементов ИЛИ единичное значение от старшего разряда передается последовательно в сторону младших разрядов и на выходах элементов ИЛИ 101, 102, …, 10(К-1) устанавливается многоразрядный унитарный код (количество единиц, начиная с младшего первого разряда, соответствующее значению, установленному в регистре приоритета RPR 14), по которому запрещаются единичные значения соответствующих разрядов совпадающего или младшего приоритета унитарного код «1 из К» с внутренней шины BDC. Поэтому далее на выходах элементов И с инверсным входом из группы 111, 112, …, 11(К-1) формируется унитарный код «1 из К», который передается на внутреннюю шину старшей группы BS, если текущая выявленная группа единичных бит содержит количество единиц превышающее предыдущее значение, и далее с шины BS передается на входы регистра приоритета RPR 14.

Одновременно унитарный код «1 из К» с внутренней шины старшей группы BS передается на входы второго элемента ИЛИ 12, на выходе которого формируется единичное значение, при наличии на одном из входов единичного значения, которое является внутренним флагом максимума FH=1. При единичном значении флага максимума FH=T разрешается запись в регистр максимальной группы RH 13, кода с внутренней шины количества единичных бит в группе BD, и запись в регистр приоритета RPR 14, значения кода с внутренней шины старшей группы BS.

Счетчик тактов СТС 1 осуществляет счет тактовых импульсов IC по модулю (К+1). При этом когда счетчик СТС установлен в нулевое состояние СТС=0, на выходе формируется единичное значение флага начала блока F0=1, по которому разрешается запись в выходной буфер групп ОВ 5 значений количества выявленных единичных групп со счетчиков 61, 62, …, 6(M+1) и запись в выходной буфер максимальных групп ОН 15 с выхода регистра максимальной группы RH 13 значений для предыдущего входного блока ВВ.

Считывание результатов на группу внешних выходов групп QB из выходного буфера ОВ 5 и на группу внешних выходов максимальных групп QH из выходного буфера ОН 15 выполняется под управлением по соответствующим внешним шинам управления ЕО. При реализации выходных буферов ОВ 5 и ОН 15 в виде двухпортовой памяти FIFO, обмен можно выполнять в процессе детектирования групп с учетом значений флагов «Буфер пуст» FZ и «Буфер заполнен» FF.

Кроме того, значения со счетчиков единичных групп 61, 62, …, 6(M+1) поступают на группы входов вторых слагаемых одноименных сумматоров из группы 71, 72, …, 7(M+1), на которых проводится суммирование со значениями соответствующих сумм (количества) с выходов регистров из группы 81, 82, …, 8(M+1), выявленных в предыдущих блоках входных данных. При этом на группе сумматоров 71, 72, …, 7(M+1) и группе регистров 81, 82, …, 8(M+1) реализованы накапливающие сумматоры. Кроме того, значения с выходов регистров 81, 82, …, 8(M+1) являются группой внешних шин количества единичных групп Q1, Q2, …, Q(M+1).

Предлагаемое устройство работает следующим образом.

Предлагаемое устройство работает при задании единичного значения на внешнем входе ICE разрешения работы ICE=1. При подаче сигнала на вход IR синхронной установки по тактовому сигналу IC в нулевое состояние устанавливаются счетчик тактов СТС 1, счетчик единичных бит СТВ 2, и регистры из группы 81, 82, …, 8(M+1), и устанавливаются нулевые адреса в выходном буфере групп ОВ 5 и в выходном буфере максимальных групп ОН 15.

На фиг. 2 приведена временная диаграмма работы предлагаемого устройства для детектирования групп, содержащих от 1 до М=3 единичных бит и W≥2 единичных бит, в двух последовательных блоках входных данных BB(Z+1) и BB(Z+2), содержащих по К=8 разрядов. На внешний вход данных ID для блока входных данных BB(Z+1) подана последовательность «10101101», а для блока входных данных BB(Z+2) подана последовательность «11010111». Между блоками BB(Z+1) и BB(Z+2) в такте 9 и после второго блока данных BB(Z+2) в такте 18 на вход данных ID поданы разделительные нулевые биты.

В такте 1 на счетчике тактов СТС 1 установлено нулевое значение СТС=0, по которому формируется единичное значение флага начала блока F0=1, по которому в такте 2 осуществляется запись по адресам Z в выходной буфер групп ОВ 5 значений OB(Z)=ZW_Z3_Z2_Z1 - количество выявленных единичных групп со счетчиков 61, 62, …, 6(M+1) и запись в выходной буфер максимальных групп ОН 15 значения OH(Z)=ZH с выхода регистра максимальной группы RH 13 - значений для предыдущего входного блока данных BB(Z). Также осуществляется подсчет общего количества выявленных единичных групп для первых Z блоков входных данных, начиная с первого ВВ1 до BB(Z) блока, в накапливающих сумматорах на группе сумматоров 71, 72, …, 7(M+1) и группе регистров 81, 82, …, 8(M+1) и запись вычисленных значений V1, V2, V3, VW в регистры 81, 82, …, 8(M+1). Кроме того, в такте 2 по единичному значению флага начала блока F0=1 в нулевое состояние устанавливаются счетчики единичных групп из группы 61, 62, …, 6(M+1), регистр максимальной группы RM 13 и регистр приоритета RPR 14.

Одновременно в такте 1 на вход данных ID поступает единичное значение первого бита блока данных BB(Z+1), подсчет которого осуществляется на такте 2 в счетчике единичных бит 2 СТС=1 и на шине количества единичных бит в группе устанавливается код BD=1. В такте 2 на вход данных ID поступает нулевое значение второго бита блока данных BB(Z+1), по которому на выходе инвертора 4 устанавливается единичное значение и разрешается работа дешифратора 3. Далее устанавливается значение на шине унитарного кода BDC=001, так как выявлена группа, содержащая один единичный бит.Поэтому в такте 3 осуществляется счет в первом счетчике 61 единичных групп СТ1=1. Кроме того в такте 2 формируется код BS=001 на внутренней шине старшей группы BS, так как в регистре приоритета RPR 14 установлен нулевой код «000». При этом в такте 2 на выходе элемента ИЛИ 12 формируется единичное значение флага максимума FH=1, по которому в такте 3 осуществляется запись в регистр 13 максимальной группы RH=1 и запись в регистр приоритета RPR 14 и установка на шине приоритета кода BPR=001, по которому на следующих тактах на группе элементов ИЛИ 101, 102, …, 10(К-1) и группе элементов И с инверсным входом 11i, 112, …, 11(К-1) исключаются единичные значения с шины унитарного кода BDC в первом разряде унитарного код «1 из К» на внутренней шине старшей группы BS.

Кроме того, на вход данных ID поступают в такте 3 единичное значение третьего бита и в такте 4 нулевое значение четвертого бита блока данных BB(Z+1), для которых выявлена вторая единичная группа, содержащая один единичный бит и формируется код на шине унитарного кода BDC=001. Поэтому в такте 5 осуществляется счет в первом счетчике 61 единичных групп СТ1=2, но не изменяется значение кода максимальной группы в регистре RH 13 и регистре приоритета RPR 14.

В тактах 5 и 6 на вход данных ID поступают единичные значения пятого и шестого бит и в такте 7 нулевое значение седьмого бита блока данных BB(Z+1), для которых выявлена первая единичная группа, содержащая два единичных бита и устанавливается значение на шине унитарного кода BDC=010. Поэтому в такте 8 осуществляется счет во втором счетчике 62 единичных групп СТ2=1. Одновременно единичное значение формируется на выходе первого элемента ИЛИ 9 и формируется внутренний флаг разрешения счета FE=1, по которому в такте 8 также осуществляется счет в четвертом счетчике 64 единичных групп СТ4=1 (выявлена группа, содержащая два и более единичных бит W≥2).

Кроме того, в такте 7 формируется код BS=010 на внутренней шине старшей группы BS, так как в регистре приоритета RPR 14 установлен код «001». При этом в такте 7 на выходе элемента ИЛИ 12 формируется единичное значение флага максимума FH=1, по которому в такте 8 осуществляется запись в регистр RH 13 максимальной группы RH=2 и запись в регистр приоритета RPR 14 и установка на шине приоритета кода BPR=010, по которому на выходах элементов ИЛИ группы 101, 102, …, 10(К-1) устанавливается код «011» и на следующих тактах в группе элементов И с инверсным входом 111, 112, …, 11(К-1) исключаются единичные значения с шины унитарного кода BDC в первом и втором разрядах унитарного код «1 из К» на внутренней шине старшей группы BS.

На вход данных ID в такте 8 поступает единичное значение восьмого (К-го, старшего) бита блока данных BB(Z+1) и далее в такте 9 значение нулевого разделительного бита между блоками данных BB(Z+1) и BB(Z+2), для которых выявлена третья единичная группа, содержащая один единичный бит и формируется код на шине унитарного кода BDC=001. Поэтому в такте 10 осуществляется счет в первом счетчике 61 единичных групп СТ1=3, но не изменяется значение кода максимальной группы в регистре RH 13 и регистре приоритета RPR 14, так как выявленная группа содержит меньше единичных бит, чем зарегистрированы в регистре 13 максимальной группы RH=2 и на выходе элемента ИЛИ 12 формируется нулевое значение флага максимума FH=0.

Одновременно в каждом такте проводится счет тактовых сигналов IC на счетчике тактов СТС 1, в котором задан период (модуль) счета равный девяти (для К+1=9). Поэтому в такте 10 в счетчике СТС 1 устанавливается начальное нулевое состояние СТС=0 и формируется единичное значение флага начала блока F0=1, по которому в такте 11 осуществляется запись по адресам (Z+1) в выходной буфер групп ОВ 5 значений OB(Z+1)=1_0_1_3 - количество выявленных единичных групп со счетчиков 61, 62, …, 6(M+1) и запись в выходной буфер максимальных групп ОН 15 значения OH(Z+1)=2 с выхода регистра максимальной группы RH 13 - значений для текущего входного блока BB(Z+1).

Также осуществляется подсчет общего количества выявленных единичных групп для всех блоков входных данных, начиная с первого ВВ1 до BB(Z+1) блока, в накапливающих сумматорах на группе сумматоров 71, 72, …, 7(M+1) и группе регистров 81, 82, …, 8(M+1) и в такте 11 запись вычисленных значений (V1+3), (V2+1), V3, (VW+1) в регистры 81, 82, …, 8(M+1). Кроме того, в такте 11 по единичному значению флага начала блока F0=1 в нулевое состояние устанавливаются счетчики единичных групп из группы 61, 62, …, 6(M+1), регистр максимальной группы RH 13 и регистр приоритета RPR 14.

Далее для следующей входной группы BB(Z+2) в тактах 10-17 на вход данных ID поступает следующая последовательность бит «11010111» и в такте 18 нулевое значение разделительного бита входных блоков. При этом в соответствии с приведенным выше алгоритмом на такте 12 выявляется группа, содержащая два единичных бита, и осуществляется счет во втором счетчике 62 единичных групп СТ2=1, а также формируется внутренний флаг разрешения счета FE=1, по которому также осуществляется счет в четвертом счетчике 64 единичных групп СТ4=1 (выявлена группа, содержащая два и более единичных бит W≥2). Кроме того, также формируется единичное значение флага максимума FH=1, по которому в такте 13 осуществляется запись в регистр 13 максимальной группы RH=2 и запись в регистр приоритета RPR 14 и установка на шине приоритета кода BPR=010, по которому на выходах элементов ИЛИ группы 101, 102, …, 10(К-1) устанавливается код «011».

В такте 14 выявляется группа, содержащая один единичный бит и осуществляется счет в первом счетчике 61 единичных групп СТ1=1, но не изменяется значение кода максимальной группы в регистре RH 13 и регистре приоритета RPR 14.

В такте 18 выявляется группа, содержащая три единичных бита и в такте 19 осуществляется счет в третьем счетчике 63 единичных групп СТ3=1 и четвертом счетчике 64 единичных групп СТ4=2. Кроме того, выявлена максимальная группа, содержащая три единичных бита, поэтому формируется единичное значение флага максимума FH=1, по которому в такте 19 осуществляется запись в регистр 13 максимальной группы RH=3 и запись в регистр приоритета RPR 14.

В такте 19 на выходе счетчика тактов СТС 1 формируется единичное значение флага начала блока F0=1, по которому в такте 20 осуществляется запись по адресам (Z+2) в выходной буфер групп ОВ 5 значений OB(Z+2)=2_1_1_1 - количество выявленных единичных групп со счетчиков 61, 62, …, 6(М+1) и запись в выходной буфер максимальных групп ОН 15 значения OH(Z+2)=3 с выхода регистра максимальной группы RH 13 - значений для текущего входного блока BB(Z+2). Также осуществляется подсчет общего количества выявленных единичных групп для всех блоков входных данных, начиная с первого ВВ1 до BB(Z+2) блока, в накапливающих сумматорах на группе сумматоров 71, 72, …, 7(M+1) и группе регистров 81, 82, …, 8(М+1) и запись вычисленных значений (V1+4), (V2+2), (V3+1), (VW+3) в регистры 81, 82, …, 8(M+1).

Таким образом, по адресам (Z+1) и (Z+2) в выходной буфер групп ОВ 5 и в выходной буфер максимальных групп ОН 15 записаны соответствующие значения выявленных единичных групп и максимальных групп в блоках BB(Z+1) и BB(Z+2). Кроме того, значения с выходов регистров 81, 82, …, 8(М+1) являются группой внешних выходов количества единичных групп Q1, Q2, …, Q(M+1), на которых установлены значения общего количества соответствующих единичных групп для всей N разрядной входной последовательности данных.

Считывание результатов на группу внешних выходов групп QB из выходного буфера ОВ 5 и на группу внешних выходов максимальных групп QH из выходного буфера ОН 15 выполняется под управлением по соответствующим внешним шинам управления ЕО. При реализации выходных буферов ОВ 5 и ОН 15 в виде двухпортовой памяти FIFO, обмен можно выполнять в процессе детектирования групп с учетом значений флагов «Буфер пуст» FZ и «Буфер заполнен» FF.

Предлагаемое устройство может быть применено для аппаратной реализации статистических тестов, разработанных лабораторией информационных технологий Национального института стандартов и технологий (NIST, США), целью которых является определение меры случайности двоичных последовательностей, порожденных генераторами случайных чисел. В частности, предлагаемое устройство реализует тест на самую длинную последовательность единиц в блоке, в котором определяется самый длинный ряд единиц внутри блока заданной длины, например, в блоках содержащих 8 бит или 128 бит. Например, в восьмиразрядных блоках осуществляется выявление самой длинной последовательности из единиц, содержащих 1, 2, 3, ≥4 разрядные единичные группы при задании разрядности входных блоков данных К=8, разрядности детектируемых единичных групп М=3 и W=4.

При обработке сигналов и результатов физических экспериментов предлагаемое устройство обеспечивает выявление событий заданной размерности, определение их количества и максимальных событий.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое устройство решает поставленную задачу, обладает регулярностью узлов и связей, и соответствует заявляемому техническому результату - расширение арсенала средств того же назначения в части возможности детектирования групп единичных бит, определение количества заданных групп и выявления максимальных групп в двоичных блоках, а также подсчет единичных групп во входной последовательности.

Изобретение относится к устройствам обработки данных. Технический результат заключается в расширении арсенала средств того же назначения, в части возможности детектирования групп единичных бит, определение количества заданных групп и выявление максимальных групп в двоичных блоках, а также подсчет единичных групп во входной последовательности. Устройство содержит внешний вход данных ID последовательного ввода К-разрядных блоков данных ВВ из входной N-разрядной бинарной последовательности данных, группу внешних выходов групп QB, группу внешних выходов максимальных групп ОН, группу внешних шин количества единичных групп Q1, Q2, …, Q(М+1) (где М - разрядности детектируемых единичных групп, 1≤М≤К), счетчик тактов СТС 1, счетчик единичных бит СТВ 2, дешифратор 3, инвертор 4, выходной буфер групп ОВ 5, группу из (М+1) счетчиков единичных групп 61, 62, …, 6(M+1), группу из (М+1) сумматоров 71, 72, …, 7(M+1), группу из (М+1) регистров 81, 82, …, 8(M+1), первый элемент ИЛИ 9, группу из (К-1) элементов ИЛИ 101, 102, …, 10(К-1), группу из (К-1) элементов И с инверсным входом 111, 112, …, 11(К-1), второй элемент ИЛИ 12, регистр максимальной группы RH 13, регистр приоритета RPR 14 и выходной буфер максимальных групп ОН 15, а также введены внешние входы тактовый IC, синхронной установки в нулевое состояние IR и разрешения работы ICE, внутренние шины количества единичных бит в группе BD, унитарного кода BDC, старшей группы BS и приоритета BPR, внутренние флаги начала блока F0, разрешения счета FE и максимума FH, внешние шины управления обменом ЕО, внешние флаги «Буфер заполнен» FF и «Буфер пуст» FZ. 2 ил.

Устройство для детектирования групп единичных бит в блоках двоичной последовательности содержит внешний вход данных ID последовательного ввода К-разрядных блоков данных ВВ из входной N-разрядной бинарной последовательности данных, группу внешних выходов групп QB, группу внешних выходов максимальных групп QH, группу внешних шин количества единичных групп Q1, Q2, …, Q(M+1) (где М - разрядности детектируемых единичных групп, 1≤М≤К), счетчик тактов СТС 1, счетчик единичных бит СТВ 2, дешифратор 3, инвертор 4, выходной буфер групп ОВ 5, группу из (М+1) счетчиков единичных групп 61, 62, …, 6(M+1), группу из (М+1) сумматоров 71, 72, …, 7(M+1), группу из (М+1) регистров 81, 82, …, 8(M+1), первый элемент ИЛИ 9, группу из (К-1) элементов ИЛИ 101, 102, …, 10(К-1), группу из (К-1) элементов И с инверсным входом 111, 112, …, 11(К-1), второй элемент ИЛИ 12, регистр максимальной группы RH 13, регистр приоритета RPR 14 и выходной буфер максимальных групп ОН 15,

а также введены внешние входы тактовый IC, синхронной установки в нулевое состояние IR и разрешения работы ICE, внутренние шины количества единичных бит в группе BD, унитарного кода BDC, старшей группы BS и приоритета BPR, внутренние флаги начала блока F0, разрешения счета FE и максимума FH, внешние шины управления обменом ЕО, внешние флаги «Буфер заполнен» FF и «Буфер пуст» FZ,

причем внешний вход синхронной установки в нулевое состояние IR соединен с соответствующими входами синхронной установки в нулевое состояние R счетчика тактов СТС 1, выходного буфера групп ОВ 5, регистров 81, 82, …, 8(М+1) и выходного буфера максимальных групп ОН 15, а внешний вход разрешения работы ICE соединен с входом разрешения работы СЕ счетчика тактов СТС 1,

внешний тактовый вход устройства IC соединен с входами синхронизации С счетчика тактов СТС 1, счетчика единичных бит СТВ 2, выходного буфера групп ОВ 5, счетчиков единичных групп 61, 62, …, 6(М+1), регистров 81, 82, …, 8(М+1), регистра максимальной группы RH 13, регистра приоритета RPR 14 и выходного буфера максимальных групп ОН 15,

причем выход счетчика тактов СТС 1 является внутренним флагом начала блока F0, который соединен с входами синхронной установки в нулевое состояние R счетчиков единичных групп 61, 62, …, 6(М+1), регистра максимальной группы RH 13 и регистра приоритета RPR 14, а также соединен с входами разрешения работы СЕ выходного буфера групп ОВ 5, регистров 81, 82, …, 8(М+1) и выходного буфера максимальных групп ОН 15,

внешний вход данных ID соединен с входом инвертора 4 и с входом разрешения работы СЕ счетчика единичных бит СТВ 2, выходы которого являются разрядами внутренней шины количества единичных бит в группе BD, которая подключена к адресным входам дешифратора 3 и к информационным D-входам регистра максимальной группы RH 13, а выход инвертора 3 соединен с входом синхронной установки в нулевое состояние R счетчика единичных бит СТВ 2 и входом разрешения работы Е дешифратора 3, выходы которого являются К разрядами внутренней шина унитарного кода BDC,

причем первые М разрядов внутренней шины унитарного кода BDC, начиная с первого до М-го разряда, соединены с входами разрешения работы СЕ соответствующих одноименных М счетчиков единичных групп 61, 62, …, 6М, а также первые (К-1) разрядов внутренней шины унитарного кода BDC, начиная с первого до (К-1)-го разряда, соединены с первыми прямыми входами соответствующих одноименных элементов И с инверсным входом группы 111, 112, …, 11(К-1), кроме того разряды внутренней шины унитарного кода BDC, начиная с W-го разряда до К-го разряда (где W разрядность детектируемых единичных групп, 1≤W≤К), соединены с входами первого элемента ИЛИ 9, выход которого является внутренним флагом разрешения счета FE и соединен с входом разрешения работы СЕ (М+1)-го счетчика единичных групп 6(М+1),

причем выходы элементов И с инверсным входом группы 11i, 112, …, 11(К-1) являются первыми (К-1) разрядами внутренней шины старшей группы BS, у которой К-й разряд соединен с К-м разрядом внутренней шины унитарного кода BDC, а все К разряды внутренней шины старшей группы BS соединены с группой информационных D-входов регистра приоритета RPR 14 и соединены с соответствующими входами второго элемента ИЛИ 12, выход которого является внутренним флагом максимума FH и соединен с входами разрешения работы СЕ регистра максимальной группы RH 13 и регистра приоритета RPR 14, выходы которого являются разрядами внутренней шины приоритета BPR, у которой первые (К-1) разряды соединены с первыми входами одноименных (К-1) элементов ИЛИ из группы 101, 102, …, 10(К-1), выходы которых соединены с инверсными входами одноименных элементов И с инверсным входом из группы 111, 112, …, 11(К-1),

причем вторые входы первых (К-2) элементов ИЛИ группы 101, 102, …, 10(К-2), начиная с первого до (К-2)-го элементов, соединены с выходами соответствующих последующих (К-2) элементов ИЛИ группы 102, 103, 10(К-1), начиная со второго до (К-1)-го элементов, а К-й разряд внутренней шины приоритета BPR соединен со вторым входом (К-1)-го элемента 10(К-1),

кроме того, выходы счетчиков единичных групп 61, 62, … 6(М+1) соединены с соответствующими группами информационных D-входов выходного буфера групп ОВ 5, а также соединены со вторыми группами входов соответствующих (М+1) сумматоров 71, 72, …, 7(М+1), у которых первые группы входов соединены с выходами одноименных (М+1) регистров 81, 82, …, 8(М+1), выходы которых также являются соответствующими одноименными внешними шинами Q1, Q2, …, Q(M+1) количества единичных групп,

кроме того, выходной буфер групп ОВ 5 также подключен к внешней соответствующей шине ЕО управления обменом, а соответствующие выходы выходного буфера ОВ 5 являются группой внешних выходов групп QB и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ,

причем группа выходов выходной регистра максимальной группы RH 13 соединена с группой информационных D-входов буфера максимальных групп ОН 15, выход которого подключен к внешней соответствующей шине ЕО управления обменом, а соответствующие выходы выходного буфера максимальных групп ОН 15 являются группой внешних выходов максимальных групп QH и соответствующими внешними флагами «Буфер заполнен» FF и «Буфер пуст» FZ.

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| УСТРОЙСТВО ПОСЛЕДОВАТЕЛЬНОГО ТИПА ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2018 |

|

RU2680759C1 |

| US 6904114 B2, 07.06.2005 | |||

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ ЧИСЕЛ | 2020 |

|

RU2740339C1 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНОЙ СТРУКТУРЫ ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП НУЛЕВЫХ И ЕДИНИЧНЫХ БИТ И ОПРЕДЕЛЕНИЕ ИХ КОЛИЧЕСТВА | 2019 |

|

RU2711054C1 |

Авторы

Даты

2023-12-15—Публикация

2023-08-07—Подача