Область техники, к которой относится изобретение

Изобретение относится к области информационно-вычислительных сетей и может быть использовано при построении мультисервисных сетей, а также при проектировании сетей следующего поколения (NGN).

Уровень техники

Известны устройства для преобразования случайных импульсных последовательностей, например «Частотное множительно-делительное устройство» (авторское свидетельство СССР №1312571 от 23.05.87 г.) Устройство содержит триггер, четыре элемента И, четыре формирователя импульсов, четыре счетчика, два элемента задержки, две группы элементов И, три элемента ИЛИ, три информационных входа и выход с соответствующими связями. За счет попеременного подключения двух входных частотных сигналов к входам двух параллельно подключенных счетчиков (делителей частоты) с частотой третьего входного сигнала на выходе устройства формируется равномерная импульсная последовательность, пропорциональная отношению второго входного сигнала к первому. Однако данное устройство не может формировать последовательности с заданным законом распределения интервалов времени между импульсами в выходной последовательности.

Наиболее близким по технической сущности к предлагаемому устройству является «Устройство для упорядочивания случайных импульсных последовательностей», см. авторское свидетельство СССР №1221636 от 30.03.1986 г. Устройство содержит два блока осреднения, каждый из которых имеет два идентичных канала, объединенных управляющим триггером по входу и элементом ИЛИ. Каждый канал содержит счетчики, логические элементы И, элемент задержки, формирователь импульса по переднему фронту, блок формирования импульса сброса. Поставленная цель - повышение точности осреднения за счет увеличения интервала времени осреднения - достигается функциональными связями блоков осреднения. Частота выходной последовательности в точности равна средней частоте входной последовательности импульсов. Недостатком является то, что устройство может перераспределять интервалы времени между пакетами, делая последовательность упорядоченной с постоянной длительностью интервала времени между пакетами (регулярный поток). Однако данное устройство не в состоянии распределить интервалы времени между пакетами по заданному закону.

Раскрытие изобретения

Задачей предлагаемого изобретения является преобразование трафика с произвольным законом распределения интервалов времени между пакетами в любой другой закон распределения, в том числе в пуассоновский.

Технический результат

Технический результат представляет собой преобразование трафика информационно-вычислительных сетей с произвольным законом распределения интервалов времени между пакетами в заданный закон распределения, что позволит повысить их производительность и увеличить скорость передачи в каналах связи.

Технический результат достигается тем, что в устройство для преобразования трафика, содержащее входную шину, первый и второй логические элементы И, счетный триггер, счетчик, логический элемент ИЛИ, введены первый и второй элементы буферной памяти, третий и четвертый логические элементы И, выходную шину, а также вычислительное устройство, причем входная шина соединена с первыми входами первого и третьего логических элементов И, вторые входы которых соединены с инверсным и прямым выходами счетного триггера, соответственно, при этом выход вычислительного устройства подсоединен к первым входам второго и четвертого логических элементов И, вторые входы которых соединены с прямым и инверсным выходами счетного триггера, соответственно, выходы первого и третьего логических элементов И подключены к входам записи первого и второго элементов буферной памяти, соответственно, а выходы второго и четвертого логических элементов подсоединены к входам считывания первого и второго элементов буферной памяти, соответственно, выходы элементов буферной памяти соединены с входами элемента ИЛИ, выход которого соединен с выходной шиной, при этом вход счетчика подсоединен к входной шине, а выход соединен с счетным входом счетного триггера.

Краткое описание чертежей

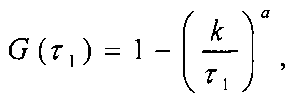

Структурная схема устройства для преобразования трафика показана на фигуре 1.

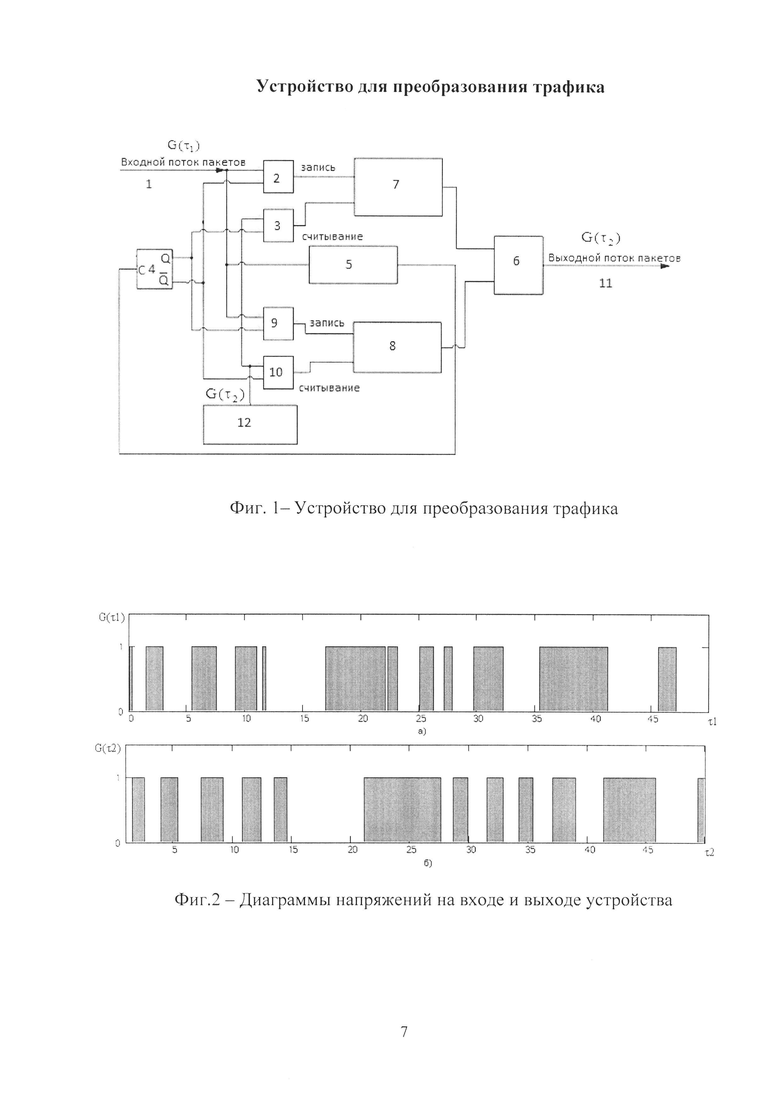

На фигуре 2 показаны диаграммы напряжений на входе и выходе устройства, поясняющие его работу.

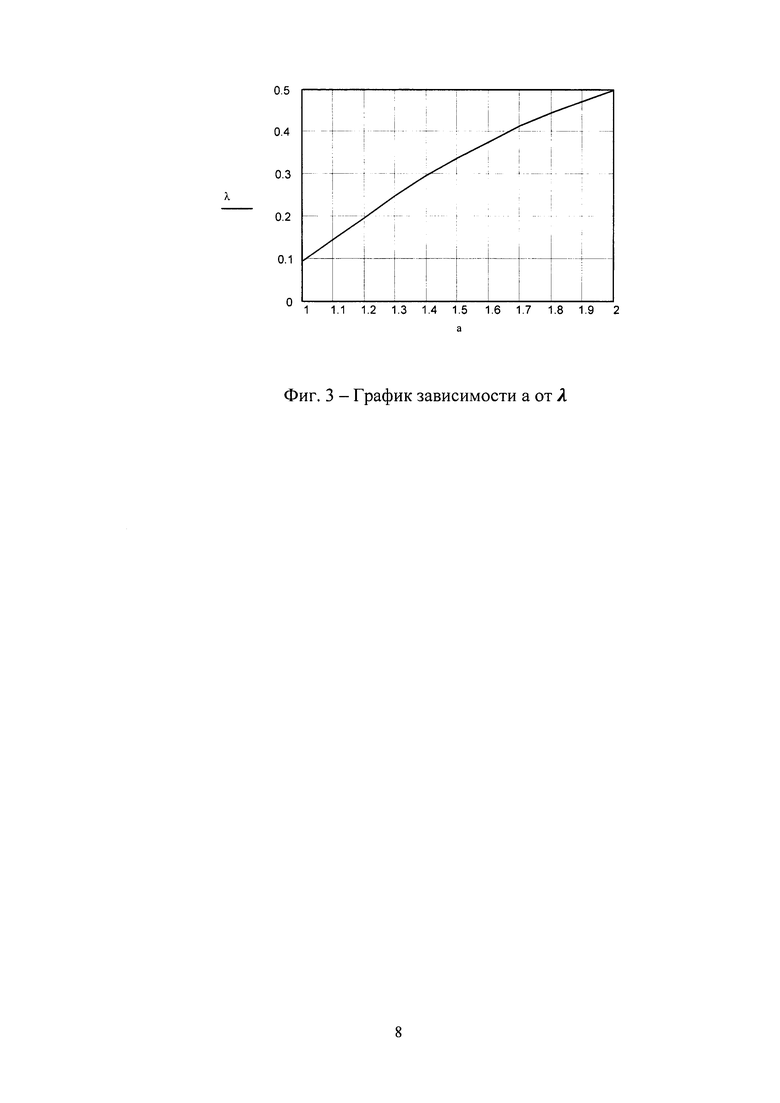

На фигуре 3 приведен график зависимости а от λ.

Осуществление изобретения

Устройство для преобразования трафика, содержащее входную шину 1, первый 2 и второй 3 логические элементы И, счетный триггер 4, счетчик 5, логический элемент ИЛИ 6, отличающееся тем, что в него введены первый 7 и второй 8 элементы буферной памяти, третий 9 и четвертый 10 логические элементы И, выходная шина 11, объединяющая элементы И по выходу, а также вычислительное устройство 12, причем входная шина 1 соединена с первыми входами первого 2 и третьего 9 логических элементов И, вторые входы которых соединены с инверсным и прямым выходами счетного триггера 4, соответственно, при этом выход вычислительного устройства 12 подсоединен к первым входам второго 3 и четвертого 10 логических элементов И, вторые входы которых соединены с прямым и инверсным выходами счетного триггера 4, соответственно, выходы первого 2 и третьего логических 9 элементов И подключены к входам записи первого 7 и второго 8 элементов буферной памяти, соответственно, а выходы второго 3 и четвертого 10 логических элементов И подсоединены к входам считывания первого 7 и второго 8 элементов буферной памяти, соответственно, выходы элементов буферной памяти 7 и 8 соединены с входами элемента ИЛИ 6, выход которого соединен с выходной шиной 11, при этом вход счетчика 5 подсоединен к входной шине 1, а выход соединен с счетным входом счетного триггера 4.

Работа устройства

Входной поток пакетов G(τ1), где τ1 - интервал времени между пакетами во входной последовательности (см. фигуру 2а), с входной шины 1 подается на первые входы первого 2 и третьего 9 логических элементов И, с выходов которых поступает на входы записи первого 7 и второго 8 элементов буферной памяти, соответственно. Поток G(τ2), где τ2 - интервал времени между пакетами в выходной последовательности (см. фигуру 2б), с выхода вычислительного устройства 12 подается на первые входы второго 3 и четвертого 10 логических элементов И, с выходов которых он поступает на входы считывания элементов буферной памяти первого 7 и второго 8, соответственно. Перед началом работы оба элемента буферной памяти, первый 7 и второй 8, емкость каждого элемента буферной памяти равна m, и счетчик 5 с коэффициентом пересчета, равным m1, причем m>m1, обнулены, а счетный триггер 4 находится в исходном состоянии, при котором вторые входы первого логического элемента И 2 и четвертого логического элемента 10 находятся под высоким потенциалом, снимаемым с инверсного выхода счетного триггера 4, в то время как потенциал вторых входов второго 3 и третьего 9 логических элементов И оказывается низким, поскольку он обусловлен потенциалом прямого выхода счетного триггера 4. Учитывая распределение потенциалов на вторых входах логических элементов И, после начала работы вначале заполняется первый элемент буферной памяти 7, в то время как со второго элемента буферной памяти 8 информация считывается, но поскольку там информация не была записана, то на выходе логического элемента ИЛИ 6 будет фиксироваться ноль. Одновременно с этим информация с входной шины 1 начнет заполнять счетчик 5 и при его переполнении на выходе счетчика 5 появится высокий потенциал, который переведет счетный триггер 4 по счетному входу во второе устойчивое состояние. При этом откроются второй 3, третий 9 логические элементы И, а первый 2 и четвертый 10 логические элементы И закроются. Первый элемент буферной памяти 7 начнет заполняться пакетами с входной шины 1, а записанные в предыдущем цикле пакеты начнут вытесняться из второго элемента буферной памяти 8. Длительность интервалов времени между пакетами τ2 будет определяться последовательностью G(τ2), формируемой вычислительным устройством 12. Входная последовательность на фигуре 2а приведена для распределения длительности интервалов между пакетами по закону Парето с заведомо самоподобными свойствами:

где а - параметр формы.

Выходная последовательность имеет распределение длительности интервалов времени между паллетами по закону Пуассона:

G(τ2)=1-exp(λτ2),

где λ - интенсивность потока пакетов.

Анализ показал, что наивысшая точность преобразования достигается при определенном соотношении между а и λ, которое задается в данном случае графиком (см. фигуру 3).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ СНИЖЕНИЯ ВЛИЯНИЯ САМОПОДОБНОСТИ В СЕТЕВЫХ СТРУКТУРАХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2413284C2 |

| Устройство для распределения заданий процессорам | 1989 |

|

SU1837287A1 |

| Устройство для сопряжения двух асинхронных магистралей | 1986 |

|

SU1403083A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| АВТОМАТИЧЕСКИЙ СЛЕДЯЩИЙ ДЕЛИТЕЛЬ ПЕРИОДОВ ИМПУЛЬСНЫХ СИГНАЛОВ | 1992 |

|

RU2105410C1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1728968A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для сопряжения ЭВМ с каналом связи | 1987 |

|

SU1439612A1 |

| СПОСОБ ДОСТУПА К ШИНЕ ПЕРЕДАЧИ ДАННЫХ В ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 1989 |

|

RU2010320C1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

Изобретение относится к области информационно-вычислительных сетей и может быть использовано при проектировании сетей связи следующего поколения (NGN). Технический результат заключается в повышении производительности информационно-вычислительных сетей и в увеличении скорости передачи в каналах связи путем преобразования входного потока информационно-вычислительных сетей с произвольным законом распределения интервалов времени между пакетами в заданный закон распределения, в частности в пуассоновский. Объектом преобразования является одномерная плотность распределения интервалов времени между пакетами входного потока. Устройство осуществлено на элементах вычислительной техники: логических элементах И и ИЛИ, буферной памяти, счетчика, счетного триггера, вычислительного устройства. Устройство отличается от известных тем, что можно произвольный входной поток пакетов преобразовать в закон с заданной функцией распределения интервалов времени между пакетами. 3 ил.

Устройство для преобразования трафика, содержащее входную шину, первый и второй логические элементы И, счетный триггер, счетчик, логический элемент ИЛИ, отличающееся тем, что в него введены первый и второй элементы буферной памяти, третий и четвертый логические элементы И, выходная шина, а также вычислительное устройство, причем входная шина соединена с первыми входами первого и третьего логических элементов И, вторые входы которых соединены с инверсным и прямым выходами счетного триггера, соответственно, при этом выход вычислительного устройства подсоединен к первым входам второго и четвертого логических элементов И, вторые входы которых соединены с прямым и инверсным выходами счетного триггера, соответственно, выходы первого и третьего логических элементов И подключены к входам записи первого и второго элементов буферной памяти, соответственно, а выходы второго и четвертого логических элементов подсоединены к входам считывания первого и второго элементов буферной памяти, соответственно, выходы элементов буферной памяти соединены с входами элемента ИЛИ, выход которого соединен с выходной шиной, при этом вход счетчика подсоединен к входной шине, а выход соединен с счетным входом счетного триггера.

| ГЕНЕРАТОР ИСКУССТВЕННОГО ТРАФИКА | 2006 |

|

RU2339155C2 |

| Устройство для упорядочивания случайных импульсных последовательностей | 1983 |

|

SU1221636A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

Авторы

Даты

2016-07-20—Публикация

2015-04-01—Подача