С

со о

Изобретение относитск к выч.1сли- тельной технике и может- бьп ь использовано для построения многомашп.ньгьгх вычислите. систег-.

Целью изобретения является повышение достоверности обмена ннформа lyieft за счет обеспечения зозможно- сти аппаратного контроля работы устройства при передаче пакета в ядре- устройство и ириема пакета в свою память (режим шлейфа)р а также упрощение устройства за счет сокращения гисла липий канала с:хчзи и за счет возможности передачи управляющих сигналов захвата и подтверждения по каналу связи.

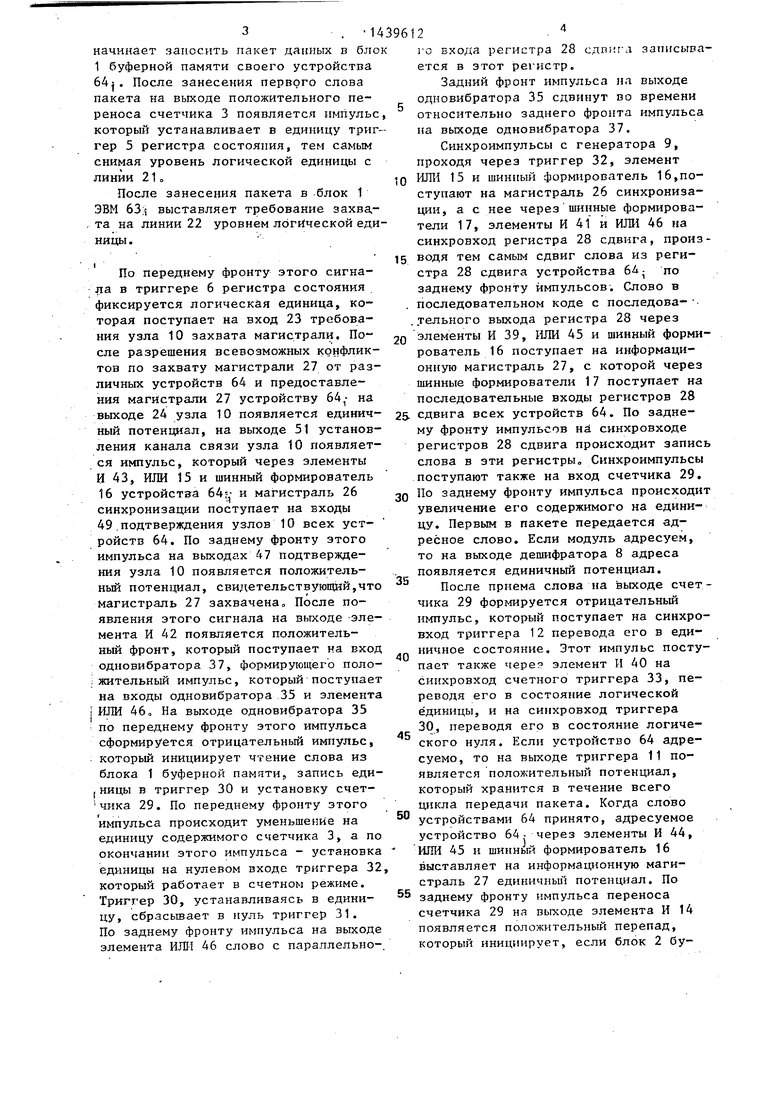

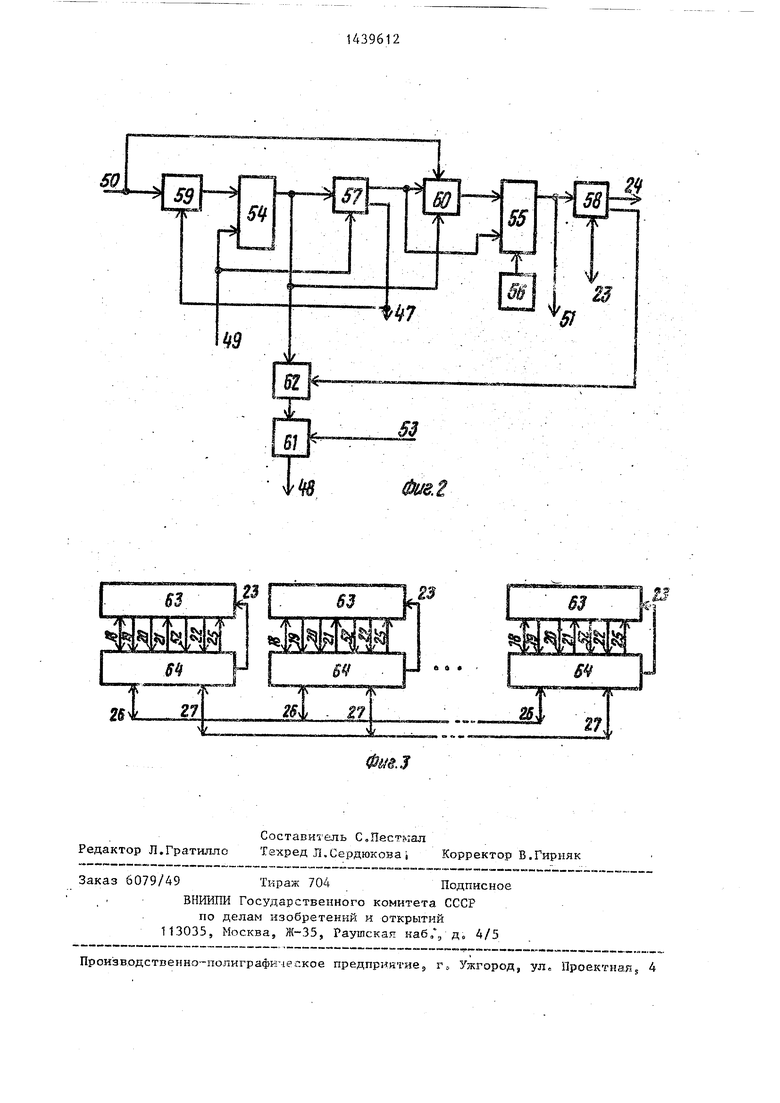

На фиг,1 прс.цетавлена структурная

с хема устройства; на фиг. 2 - схема узла захвата магистрали; на фиг.З - объединение ЭВМ с помощью предл;ага- емого устройства в многомашинную систему „

Устройство (фиг,1) содержит блоки 1 и 2 буферной памяти5 счетчики 3 и 4, триггеры 5-7 регистра состояния, дешифратор 8 адреса генератор 9 импульсов., узел 10 захвата ма.гистрали, триггере, 11 и 12. элементы И 13 и 14, элемент ИЛИ 15, шинные фор.нировате- ли 16 и 17, линию 18 данных, .пипию 19 записи, линию 20 чтения, .пинию 21 требования записи, линию 22 требования захвата, вход 23 требова.ния уз.па 10, выход 2А узла 10, линию 25 требования чтения. вход- вьгход (магистраль) 26 синхронизации, информационный вход-выход (магистраль) 27, регистр 28 сдвига, счетчик 29s триггеры 30-34, одчовибраторы ЗЗ-ЗУ, элементы И 38-44,элементы ИЛИ 45 J 46, выход 47 подтверждения узла 10, выход 48 освобождения узла. 10, вход 49 под--, тверждения узла 10, вход 50 си гхронп- зации узла 10, выход 51 установлепия канала связи узла 10, линию 52 началь ной установки, вход 53 установки„

Узел 10 захвата магистр.я.ли содержит (фиг,2) счетчики 54-55, регистр 56, триггеры 57 и 58, элементы И 59 - 61 -I элемент И.ПИ 52 .

На фиг.З обозначепы ЭВМ 63 . предлагаемое устройство 64,

Работа устройства заключается в .следуюш,ем.

Обмен между паро.й Э.ВМ 6.3 .; и 63 j через устройства 64.; и 64;,, через ипфор;-(ациоппую магистрат-.. включ.а- ет этапы:

5

0

0

5

0

5

0

проверка инициатором 63; обмена занятост-и своего устройства и при пeoбxoд. ожидания его освобож-- дения;

занесение пакета данных по линии 18 из ЭВМ 63, в блок 1 буферной памяти устройства 64 ,-;

захват устройством 64 информационной магистрали 27;

проверка занятости блока 2 буферной памяти устройства -64 , i- в случае гЕеобходимости ожидание его освобождения;

передача пакета данных из блока 1 буферной памяти устройства fi в блок 2 буферной памяти устройства 64;;

передача ггакета из блока 2 буферной памяти устройства 64 ,. по линии 18 в ЭВМ 63,

Ни первых этапах уиря Ление осуществляется от ЭВМ 63;. ь-1 ггослед нем - 63:.

Работа ;- строьс.тВ,. натинается с- начальной установки устройств б-, которая осуществляется подачей отрицательного импульса на линии 52,, По этому сиг.гмлу счетчики 3 и 4 уста- навливаштся в максимально возг. состояние, триггеры 5 и 6 регистра СОСТОЯН31Я, триггеры 30 и 34 устанавливаются в состояние логического нуля, а триггер 31 - в состоян 1е логической единицы,

В устройствах 64 блок 1 буферной памяти доступен с линии 18 дап11ык то.пько по записи, а блок /. буферной памяти - только по чтению.

Запись данных с .линии 1S в блок , 1 буферной пам-лти сог-рово;кдается отрицательным имп льсом на ЛГЕПИИ 19 а чтение .гдЯ41п-и.х из бло. са 2 буфер- . ной памяти сопровождается отрицательным .имп шьсом на линии 20 По им- пу.пьсу ка линиях 19 и 20 происходит соответственно запись .или чтеы1-ге ин формации блоков 1 и 2, По заднему фрон.ту импульса на ляпии 19 содержи мое счетчика 3 уве.личивается на сди- ЕП .-|.1,У5 а по переднему импуль- -са па линии 20 происходит уменьшение со.аершамого счетчика 4 на единицу, Лг-рес записываемого или читаемого слова п блоках 1 и 2 буферной пяь-я-си -;гпт еделяется состоянием на -выходах -::оотве -ствинио счетчиков 3 я 4

После нача 7ьной установкг: на ли- ппк 21 находится уровень .г.о. гческ.ой ..li.i-nrniaiij анализируя -:оторую;, Э.БМ 633 . -14396 начинает заносить пакет данных в блок 1 буферной памяти своего устройства 64. После занесения первого слова пакета на выходе положительного переноса счетчика 3 появляется импульс, который устанавливает в единицу триг-- гер 5 регистра состояния, тем самым снимая уровень логической единицы с линии 21 о

После занесения пакета в блок 1 ЭВМ 63; выставляет требование захва- та на линии 22 уровнем логической единицы.

10

По переднему фронту этого сигна- ла в триггере 6 регистра состояния фиксируется логическая единица, которая поступает на вход 23 требования узла 10 захвата магистрали. После разрешения всевозможных конфликтов по захвату магистрали 27 от различных устройств 64 и предоставления магистрали 27 устройству на выходе 24 узла 10 появляется единичный потенциал, на выходе 51 установления канала связи узла 10 появляется импульс, который через элементы И 43, ИЛИ 15 и шинный формирователь 16 устройства 64- и магистраль 26 синхронизации поступает на входы 49.подтверждения узлов 10 всех устройств 64. По заднему фронту зтого импульса на выходах 47 подтверждения узла 10 появляется положительный потенщал, свидетельствующий,что магистраль 27 захвачена. После появления этого сигнала на выходе элемента И 42 появляется положительный фронт, который поступает на вход одновибратора 37, формирующего поло- жительньш импульс, который поступает на .входы одновибратора 35 и элемента ИЛИ 46 о На выходе одновибратора 35 по переднему фронту этого импульса сформируется отрицательный импульс, который инициирует чтение слова из блока 1 буферной памяти, запись еди- ницы в триггер 30 и установку счет- чика 29. По переднему фронту этого импульса происходит уменьшение на единицу содержимого счетчика 3 а по окончании этого импульса - установка единицы на нулевом входе триггера 32, который работает в счетном режиме. Триггер 30, устанавливаясь в единицу, сбрасьшает в нуль триггер 31. По заднему фронту импульса на выходе элемента ИШ 46 слово с параллельно-.

0

5

0

&

0

5

0

5

0

5

12.

с входа регистра 28 сдпигм записывается в этот регистр.

Задний фронт импульса на выходе одновибратора 35 сдвинут во времени относительно заднего фронта импульса на выходе одновибратора 37.

Синхроимпульсы с генератора 9, проходя через триггер 32, элемент ИЛ11 15 и шинный формирователь 16,поступают на магистраль 26 синхронизации, а с нее через шинные формирователи 17, элементы И 41 и ИЛИ 46 на синхровход регистра 28 сдвига, производя тем самьм сдвиг слова из регистра 28 сдвига устройства по заднему фронту импульсов; Слово в последовательном коде с последова- .тельного выхода регистра 28 через элементы И 39, ИПИ 45 и шинный формирователь 16 поступает на информационную магистраль 27, с которой через шинные формирователи 17 поступает на последовательные входы регистров 28 сдвига всех устройств 64. По заднему фронту импульсов на синхровходе регистров 28 сдвига происходит запись слова в эти регистры. Синхроимпульсы поступают также на вход счетчика 29. По заднему фронту импульса происходит увеличение его содержимого на единицу. Первым в пакете передается адресное слово. Если модуль адресуем, то на выходе дешифратора 8 адреса появляется единичный потенциал.

После приема слова на выходе счетчика 29 формируется отрицательньй импульс, который поступает на сикхро- вход триггера 12 перевода его в единичное состояние. Этот импульс поступает также чере элемент И 40 на синхровход счетного триггера 33, переводя его в состояние логической единицы, и на синхровход триггера 30, переводя его в состояние логического нуля. Если устройство 64 адресуемо, то на выходе триггера 11 появляется положительный потенциал, который хранится в течение всего цикла передачи пакета. Когда слово устройствами 64 принято, адресуемое устройство 64: через элементы И 44, ИЛИ 45 и шинный формирователь 16 выставляет на информационную магистраль 27 единнчньш потенциал. По заднему фронту импульса переноса счетчика 29 на выходе элемента И 14 появляется положительный перепад, который инициирует, если блок 2 буферной памяти устройства 64, свободен, появление на выходе одновибра- тора 36 отрицательного импульсаз который инициирует чтение слова из регистра 28 сдвига в устройств.е 64- з блок 2 буферной памяти. По заднему фронту этого импульса происходит увеличение на единицу счетчика 4 и переключение в нуль триггера 33, тем самьм снимается положительный потенциал с информационной магистрали 27. Перепад с единицы в нуль на магистрали 27 фиксируется в триггере 31 / устройства 64 как признак подтв1грж- дения приема слова устройством 64j и разрешение выдачи в магистраль 27 очередного слова пакета, которое осу й1ествляется фронтом на входе одиовИб ратора 37. Если блок 2 буферной памяти адресуемого устройства 64 i за нят, то на выходе 23.требования по- является нулевой уровень,

После передачи всего пакета на выходе отрицательного переноса счетчика 3 устройства . формируется импульс, по заднему фронту которого триггер 5 регистра состояния переводится в состояние логического нуля выставляя требование записи на линии 21 уровнем логической . В устройстве 64; после приема первого слова в блок 2 буферной памяти на выходе положительного переноса счетчика 4 формируется импул-ьс, ко торый переводит триггер 34 в состояние логической единицы. Как только пакет передан, то на выходе 48 освобождения узла 10 устройства 64-j,- формируется отрицательньй импульс, которьш снимает уровень логической единицы с выхода 47 подтверждения у зла 10 всех устройств 64 и обнуля-, ет триггер 6 регистра состояния устройства 64-. Нуль на выходе тригге-- ра 6 регистра состоя|яия инициирует снятие уровня логической единицы с выхода 24 узла 10 устройства 64.. Время реакции ЭВМ 63j на логическую единицу на линии 21 значительно больше времени освобождения магистрали 27 По заднему фронту на выходе 47 подтверждения узла 10 з ст- ройства 64 . значение триггера 34 пе- реписывается в триггер 7 регистра состбяния, тем самым выставляя требование чтения на линию 25.

ЭВМ 63 : начинает читать данные из блока 2 буферной памяти своего

, ;

10

ис20

25

439612 6

устройства о При чтении слова значение счетчика 4 уменьшается на едини-. цу, После чтения пакета на выходе отрицательного переноса счетчика 4 устройства 64; формируется импульс, обпул яюпщй триггер 34 и триггер 7 регистра состояния, тем самым снимая единичный потенциал с линии 25 устройства 64,

Узел 10 захвата магистрали (фиг.2) фу1гкционирует следующим образом . В исходном состоянии синхроимпульсы с входа 50 синхронизации через элемент 15 И 60 поступают на вход счетчика 55, на входе которого находится двоичное значение, задаваемое регистром 56. При поступлении единичного потенциала с входа 23 требования на нулевой вход триггера 58 этот триггер в устройстве 64 импульсом переноса с выхода счетчика 55 переключается в состояние логической единицы. Имп гльсы переноса на выходах счетчиков 55 узлов -10 захвата магистрали сдвинуты во времени друг относительно друга за счет различия кодов, задаваемых на регистрах 56 устройств 64. Чем вьше приори-- тет устройства 64, тем большее двоичное значение находится на выхо де ре- регистра 56. Импульс с выхода счетчика 55 через выход 51 установления канала связи и через магистраль 26 синхронизации поступает на входы 49 . подтверждения узЛов 10 захвата маги- страли всех устройств 64, тем ёаным устанавливая счетчики 54 в йуль и переводя в. нуль триггеры 57 перёкл;о- чая Ичвправления прохождения синхроимпульсов с входов 50 синхронизации на вход счетчиков 54, устанавливая счетчики 55 и выставляя единицу на выходы 47 подтверждения всех устройств 64, Счетчик 54 осуществляет контроль за передачей слов по маги- , страли 27, сопровождаемых синхросигналами на выходе 26. Если в течение времени, определяемого интервалами от установки счетчиков в нуль до появления отрицательного импуль - са переноса на выходе счетчиков нет передачи данных по информационной магистрали 27s. то счетчики выраба- тывая этот импульс, производят переключение в нуль триггеров 57, снимая уровень логической единицы с выходов 47 подтверждения. Этот им- пульс через элементы ИЛИ 62 и И 61 в устройстве, захватившем магистраль.

30

35

40

45

SO

55

7. 4

передается на выход 48 освобождения, тем самым обнуляя триггер 6 регист- ра состояния и снимая уроаень логической единицы с входа 23 требования, обнуляя этим самым триггер 58, Узел 10 захвата магистрали, построенный по такому принципу, исключает; одновременный захват магистрали двумя и более устройствами. Режим шлейфа предназначен для обеспечения контроля достоверности работы уст- .ройства и осуществляется путем пере- 1дачи по информационной магистрали 27 данных, передаваемых из блока 1 бу- ферной памяти устройства 64- в блок 2 буферной памяти этого же устройства через шинный ;формирователь 17.Введение этого режима позволяет проанализировать качество работы приемо- передающих цепей устройств . При

этом адрес приемного устройства 64

J

J

задается позиционным кодом в адресном слове каждого пакета, что в силу одинакового подключения к магист - рали 27 устройств системы позволяет одновременно обращаться к блоку 2 буферной памяти приемного 64; и пе

редающего 64 устройств.

Формула изобретения

1. Устройство для сопряжения ЭВМ с каналом связи, содержащее два блока буферной памяти, два счетчика, три триггера регистра состояния, де- пшфратор адреса, генератор импульсов узел захвата магистрали, два триг- . гера, два элемента И, первый элемент ИЛИ, два шинных формирователя, причем группа информационных входов первого блока буферной памяти и группа информационных выходов второго блока буферной памяти образуют группу входов-выходов устройства для подключя.ния к группе информационных входов- выходов ЭВМ, первый счетный вход первого счетчика соединен с входами за - писи первого блока буферной памяти

.и является входом устройства для подключения к вьпсоду записи ЭВМ,первый счетный вход второго счетчика соединен с входом чтения второго блока

буферной памяти и является входом устройства для подключения к выходу чтения ЭВМ, нулевой выход первого триггера регистра состояния и синхро вход второго триггера регистра состояния являются выходом и входом

4396

Q д 20

25

30

35

45

,

50

55

128.

устройства для подключения соответ- ственно к входу требования записи и к выходу требования захвата ЭВМ,единичный выход третьего триггера регистра состояния является выходом устройства для подключения к входу требования чтения ЭВМ, первый информационный выход первого шинного формирователя и первый информационный вход второго шинного формирователя образуют вход-выход устройства для подключения к синхровходу-вькоду канала связи, второй информационный выход первого шинного формирователя и второй информационный вход втЬро- го шинного формирователя образуют вход-выход устройства для подключе- .ния к информационному входу-выходу канала связи, при этом группы разрядных выходов первого и второго счетчикой соединены соответственно с группами адресных входов первого и второго блоков буферной памяти, выход первого элемента ИЖ соединен с первым информационным входом первого шинного формирователя, выход первого триггера соединен с первым входом первого элемента И, отличающееся V тем, что,с целью повьшения достовер- ности обмена информацией за счет обеспечения возможности аппаратного контроля работы устройства, в него введены регистр сдвига, третий счетчик, четыре триггера, три одновибратора, семь элементов И, два элейента ИЛИ, причем установочный вход первого счетчика соединен с установочным входом второго счетчика, с нулевым входом первого триггера регистра состояния, с нулевыми входами второго, третьего триггеров, с единичным входом четвертого триггера , с установочными входами узла захвата маги-i страли и является входом устройства для подключения к выходу начальной установки ЭВМ, выход второго триггера регистра состояния соединен с входом требования узла захвата магистрали, с первым входом второго элемента И и является выходом устройства для подключения к входу прерывания ЭВМ, при этом выход генератора импульсов соединен с синхровходом узла захвата магистрали и с сиихровхо- дом пчтого триггера, выход которого соеди tн с первым входом первого элемента ilH, второй вход которого соединен I выходом второго элемента И,

второй вход которого соединен с выходом установления канала связи узла захвата магистрали, выход которого соединен с первым входом третьего элемента И и с первым входом четвертого элемента И, второй вход которого соединен с выходом четвертого J триггера, нулевой вход которого соединен с выходом третьего триггера и с вторыи входом третьего элемента И, выход которого соединен с нулевым входом пятого триггера и с первым входом пятого элемента И, второй вход которого соединен с информационным выходом регистра сдви га, информационный вход которого соединен с синхррвходом четвертого . триггера и с первым информационным выходом второго шинного формирователя, второй информационный выход которого соединен с первым, входом шестого элемента И и с входом подтверждения узла захвата магистрали,выход

10

которого соединен с первым входом восьмого элемента И, второй вход которого соединен с выходом седьмого триггера, синхровход которого соеди- ней с выходом девятого элемента И, первый вход которого соединен с син- хровходом третьего триггера, с выходом переноса третьего счетчика, с вторым входом первого .элемента И и с синхровходом шестого триггера, вьгход которого соединен с синхровходом первого триггера, информационный вход которого соединен с выхо- 4g дом дешифратора адреса, группа ни- формационньпс входов которбго соединена с группой информацион 5ых выходов регистра сдвига и с группой информационных входов второго блока буферной памяти, вход записи которого соединен с вторьйч счетным входом второго счетчика, с информационным входом девятого триггера, с выходом третьего одкозибратора я с

20

освобождения которого соединен с ну™ 25 третьим входом седьмого элемента И,

аыход которого соединен с установочным входом третьего счетчика, счетный вход которого со едннен с дом шестого элемента И и с вторым

выходом первого триггера регистра со- .Q входом второго элемента ИЛИ, выход синхровход и единичный вход пятого элемента И соединен с первым

левьм входом второго триггера регистра состояния, информационный вход которого соединен с третьим входом четвертого элемента И и с-единичным

стояния.

которого соединены соответственно с выходами отрицательного и положительного переноса первого счетчика, второй счетный вход которого соединен с третьим входом третьего элемента И, с первым входом седьмого элемента И, с единичным вхоДом третьего триггера, с выходом первого одиовибратора, с входом режима работы регистра сдвига НС входом чтения первого блока буферной „памяти, группа информацион нь1х йьгйодов которого соединена с группой информационных входов регистра сдвига, синхровход которого соединен с выходом второго элемента . ИЛИ, первый вход которого соединен с входом первого одновибратора и с выходом второго одновибратора,вход которого соеди ен с выходом четвер того элемента И, четвертый вход которого соединен с вторым входом седьмого элемента И, . синхровходo i третьего триггера регистра состояния, с выходом подтверждения узла захвата магистрали, с вторым входом шестого элемента И, с нулевыми входами шестого, седьмого триггеров, с нулевым входом первого триггер- ,, выход

40

входом третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом восьмого элемента И и с вторым информацион ным входом первого шинного формиро- вателя, вход третьего одновибратора соединен с выходом певвого элемента И третий вход которого соединен с кулавым выходом третьего триггера регистра состояния, нулевой и информационный входы которого соединены с выходок второго триггера, единичный вход и синхровход которого соединены соответственно с выходами положи:тельного и отрицательного переноса второго / счетчика.

2. Устройство по п,1, отлича ющееся тем, что узел захвата мапг.страли содержит два счетчика, два триггера, регистр, три элемента И., элемент ИШ1, причем первый вход первого элемента И соединен с первым входом второго элемента И и является синхровходом-узла5 первый вход и ход третьего элемента И являются со- ртветственно установочным входом и вы выходом освобождения узла, установоч ный вход первого счетчика соединен

45

50

которого соединен с первым входом восьмого элемента И, второй вход которого соединен с выходом седьмого триггера, синхровход которого соеди- ней с выходом девятого элемента И, первый вход которого соединен с син- хровходом третьего триггера, с выходом переноса третьего счетчика, с вторым входом первого .элемента И и с синхровходом шестого триггера, вьгход которого соединен с синхро; входом первого триггера, информационный вход которого соединен с выхо- g дом дешифратора адреса, группа ни- формационньпс входов которбго соединена с группой информацион 5ых выходов регистра сдвига и с группой информационных входов второго блока буферной памяти, вход записи которого соединен с вторьйч счетным входом второго счетчика, с информационным входом девятого триггера, с выходом третьего одкозибратора я с

0

входом третьего элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом восьмого элемента И и с вторым информационным входом первого шинного формиро- ; вателя, вход третьего одновибратора соединен с выходом певвого элемента И, третий вход которого соединен с кула: вым выходом третьего триггера регистра состояния, нулевой и информационный входы которого соединены с выходок второго триггера, единичный вход и синхровход которого соединены соответственно с выходами положи:тельного и отрицательного переноса второго / счетчика.

2. Устройство по п,1, отличающееся тем, что узел захвата мапг.страли содержит два счетчика, два триггера, регистр, три элемента И., элемент ИШ1, причем первый вход первого элемента И соединен с первым входом второго элемента И и является синхровходом-узла5 первый вход и выход третьего элемента И являются со- ртветственно установочным входом и вы выходом освобождения узла, установоч. ный вход первого счетчика соединен

с синхровходом первого триггера и является входом подтверждения узла, нулевой выход первого триггера соединен с вторым входом первого эле- мента И и является выходом подтверждения узла, выход переноса второго счетчика соединен с синхровходом второго триггера и является выходом установления канала связи узла, нулевой вход и единичный выход второго триггера являются соответственно входом требования и выходом узла, при этом в узле захвата магистрали нулевой выход второго триггера соединен с первым, входом элемента ИЛИ,

выход и второй вход которого соединены с вторым входом третьего элемента И и с выходом переноса первого счетчика, соединенного также с вторым входом второго элемента И и с единичным входом первого триггера, единичный выход которого соединен с установочным входом второго счетчика и

с третьим входом второго элемента И, выход которого соединен со счетным входом второго счетчика, информационный вход которого соединен с выходом регистра, выход первого элемента

И соединен со счетным входом первого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения электронных вычислительных машин | 1987 |

|

SU1443001A1 |

| Устройство для подключения источников информации к общей магистрали | 1989 |

|

SU1679498A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1986 |

|

SU1354199A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

| Устройство для сопряжения электронной вычислительной машины с общей магистралью | 1987 |

|

SU1411765A1 |

| Устройство для сопряжения ЭВМ | 1987 |

|

SU1460724A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

Изобретение относится к вычис- лительной технике и может быть использовано для построения многома- пинных вычислительных систем. Целью изобретения является повышение достоверности обмена информацией за счет обеспечения возможности ahna- ратного контроля работы устройства. Устройство содержит два блока буферной памяти, узел захвата магистрали, регистр сдвига, дешифратор адреса, три триггера регистра состояния, три счетчика, семь триггеров, три элемента ШШ, девять элементов И, три одновибратора, два шинных формирователя и генератор импульсов. 1 з.п, ф-лы, 3 ил.

Фиг.1

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1987-04-01—Подача