Изобретение относится к радиотехнике и может использоваться для приёма широкополосных сигналов в системе сбора телеметрической информации от бортовой аппаратуры космических аппаратов.

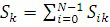

Известен способ формирования диаграммы направленности антенной решётки введением фазового сдвига в числовые последовательности отсчётов сигналов с антенн решётки [см. Проблемы антенной техники/Под ред. Л.Д. Бахраха, Д.И. Воскресенского. – М.: Радио и связь, 1989. – 368 с.: ил. – ISBN5-256-00335-6]. Для сравнительно небольшого количества антенн этот способ реализуется последовательной схемой, представленной на фиг. 1, где: 1 – приёмная антенна; 2 – входной малошумящий усилитель (МШУ) и фидер до смесителя; 3 – смеситель; 4 – первый гетеродин; 5 – усилитель промежуточной частоты с полосовым фильтром (УПЧ-ПФ); 6 – делитель; 7 – синхронные фазовые детекторы (СФД); 8 – второй гетеродин; 9 – постоянный фазовращатель на 90°; 10 – аналого-цифровые преобразователи (АЦП); 11 – генератор тактовых импульсов (ГТИ); 12 – дешифратор адресного сигнала; 13 – шина данных; 14 – процессор формирования диаграммы направленности (ПФДН); 15 – запоминающее устройство (ЗУ); 16 – устройство управления (УУ); 17 – приёмник; 18 – управляющая ЭВМ, 21 – ключ.

Выход каждой приёмной антенны 1 соединён с входом соответствующего МШУ 2, выход каждого МШУ 2 соединён с сигнальным входом соответствующего смесителя 3, гетеродинный вход которого соединён с выходом первого гетеродина 4, выход каждого смесителя 3 соединён с входом соответствующего УПЧ-ПФ 5, выход которого соединён с входом соответствующего делителя 6, первый выход каждого делителя 6 соединён с сигнальным входом первого, а второй выход делителя соединён с сигнальным входом второго из соответствующей пары синхронных фазовых детекторов 7, причём гетеродинный вход каждого первого в соответствующей паре СФД 7 соединён с выходом второго гетеродина 8, а гетеродинный вход каждого второго в соответствующей паре СФД 7 соединён с выходом постоянного фазовращателя на 90° 9, вход которого соединён с выходом второго гетеродина 8, выход каждого СФД 7 соединён с сигнальным входом соответствующего АЦП 10, вход импульсов запуска которого соединён с выходом ГТИ 11, выход данных каждого АЦП 10 соединён с входом соответствующего ключа 21, управляющий вход которого соединён с соответствующим выходом дешифратора адресного сигнала 12, вход которого соединён с первой адресной шиной УУ 16, вход синхронизации УУ 16 соединён с выходом ГТИ 11, выход ключа 21 соединён с соответствующим входом шины данных 13, выход которой соединён с первым входом данных ПФДН 14, причём второй вход данных ПФДН 14 соединён с выходом данных ЗУ 15, а вход управления ПФДН 14 соединён с выходом управления УУ 16, адресная шина ЗУ 15 соединена со второй адресной шиной УУ 16, выход данных ПФДН 14 соединён с входом данных приёмника 17, шина данных и адреса ЗУ 15 соединена с шиной данных и адреса управляющей ЭВМ 18.

На антенны 1 решётки падает фронт волны радиосигнала со сдвигом для антенны №i на время разности хода лучей Дtio относительно опорной антенны №0. Принятый антенной сигнал усиливают в соответствующем малошумящем усилителе 2, понижают по частоте с использованием первого гетеродина 4 и смесителя 3, усиливают и ограничивают по полосе частот с использованием усилителя промежуточной частоты и полосового фильтра 5, разветвляют на два сигнала делителем 6, формируют квадратурные сигналы с помощью соответствующего синхронного фазового детектора 7, второго гетеродина 8 и постоянного фазовращателя на 90° 9, после чего на аналого-цифровом преобразователе 10 под воздействием импульсов с частотой дискретизации fд от генератора тактовых импульсов 11 формируют цифровые отсчёты значений квадратурных сигналов Siс=Ai·cos(2рfst) и Sis = Ai·sin(2рfst) со средней частотой спектра fs, причём под воздействием адресных сигналов с дешифратора 12, поступающих от устройства управления 16 по приходу импульса синхронизации с ГТИ, отсчёты сигналов разных антенн решётки через соответствующие ключи 21 последовательно вводят в шину данных 13 и далее вводят в процессор формирования диаграммы направленности 14, на котором формируют индивидуальные фазовые сдвиги сигнала каждой антенны на основе данных об относительных задержках сигнала одного фазового фронта на разных антеннах Дtio, которые хранят в запоминающем устройстве 15 и рассчитывают заранее по целеуказаниям в управляющей ЭВМ 18. Процессор формирования диаграммы направленности 14 на основе относительных задержек Дtio фронта волны вычисляет разности фаз сигналов на средней частоте fs спектра сигнала после АЦП по формуле Дцio = 2рfsДtio, определяет результирующие сфазированные сигналы по формуле SiД = Ai·cos(2рfst + Дцio) = Ai·[cos(2рfst)·cos(Дцio) – sin(2рfst)·sin(Дцio)] = Siс·cos(Дцio) – Sis·sin(Дцio) и вычисляет суммарный сигнал со всех антенн решётки, после чего выдаёт его в приёмник 17.

Основные недостатки известного решения для формирования диаграммы направленности антенной решётки введением фазового сдвига в числовые последовательности отсчётов сигналов с антенн решётки состоят в его относительной трудоёмкости и непригодности для передачи широкополосных сигналов. Действительно, при фазировании сигналов от N антенн требуется 2N сравнительно трудоёмких операций умножения и N-1 операция сложения. Кроме того, при достаточно широком спектре набеги фаз в достаточно далеко отстоящих по частоте симметричных гармониках разных антенн приводят к недопустимому искажению передаваемого сигнала. Например, гармоники по краям спектра при передаче телеметрической информации (ТМИ) со скоростью 3 Мбит/с, отстоящие примерно на Дf = 6 МГц, при разности хода лучей между антеннами в ДL = 30 м дадут набег фаз Дц =2р·Дf·Дt = 2р·Дf·(ДL/c) = 2р·6·106·30/(3·108)= 1,2р. Гармоники из средней части спектра сигнала ТМИ, отстоящие примерно на Дf = 3 МГц, дадут набег фаз 0,6р. Поскольку при детектировании симметричные частоты спектра радиосигнала складываются, то указанные набеги фаз приведут к сильным искажениям передаваемых широкополосных сигналов. Помимо этого, в известном техническом решении относительные задержки сигнала одного фазового фронта на разных антеннах Дtio на протяжении всей зоны радиовидимости необходимо рассчитывать по целеуказаниям заранее, что требовало хранения значительных объёмов информации в запоминающем устройстве 15.

В свою очередь, перечисленные выше недостатки устранены в предлагаемом способе и устройстве фазирования и автосопровождения неэквидистантной цифровой антенной решётки приёма широкополосных сигналов. Использование предложенных способа и устройства обеспечит приём и обработку широкополосных сигналов без искажений при одновременном обеспечении автосопровождения космического аппарата (КА) и обеспечении быстродействия устройства фазирования антенн антенного поля при приёме от антенного поля широкополосных сигналов, несущих, например, телеметрическую информацию о состоянии бортовых систем космических аппаратов, например низкоорбитальных.

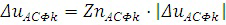

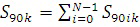

Предложен способ обработки широкополосных сигналов и автосопровождения космического аппарата, предусматривающий приём сигнала антеннами, являющимися частью антенной решётки, и формирование цифровых (дискретных) отсчётов принятого сигнала каждой антенны в соответствующих двух квадратурных информационных каналах с последующим суммированием цифровых (дискретных) отсчётов каждого квадратурного канала от нескольких антенн при контроле времени хода сигнала от опорной и ведомых антенн антенной решётки до своего устройства аналого-цифрового преобразования, а также предусматривающий формирование цифровых (дискретных) отсчётов принятого сигнала каждой антенны в четырёх каналах автосопровождения с некоторым опережением и таким же отставанием от отсчётов соответствующего квадратурного информационного канала с последующим формированием на их основе сигналов автосопровождения антенн по азимуту и углу места, а также расчётом по их значениям новых величин относительных задержек сигнала одного фазового фронта на разных антеннах с последующим вводом соответствующих сигналов задержки в соответствующие регистры предложенного устройства для формирования последующих отсчётов принимаемых сигналов одного фронта. В отличие от аналога широкополосные сигналы, принятые указанными антеннами и пришедшие в предлагаемое устройство фазирования и автосопровождения (УФА), не смещают по фазе, а дискретизируют с периодом дискретизации Дtд с задержками относительно времени прихода по соответствующим фидерам на соответствующие УФА на время подставки Дtп, как показано на диаграмме фиг. 2 для информационных каналов. То есть задерживают не принятые сигналы, а соответствующие последовательности импульсов дискретизации так, чтобы момент времени дискретизации сигнала каждой антенны соответствовал одному и тому же фронту приходящего сигнала. Для этого очередной k-й импульс дискретизации генератора для информационного сигнала антенны №i, сформированный в момент времени tГk, задерживают на время

Дtzik = Дtсi0k+ Дtфi – Дtф0 + Дtп . (1)

Здесь Дtсi0k – время сдвига момента прихода фронта волны принимаемого сигнала на антенне №i относительно опорной антенны №0, может быть отрицательным, если сигнал приходит на антенну №i раньше, чем на антенну №0, и положительным, если сигнал приходит на антенну №i позже, чем на антенну №0 и изменяется в течение времени зоны радиовидимости КА. Остальные слагаемые времени задержки являются константами. Так, Дtфi – время распространения фронта волны сигнала в фидере от фазового центра антенны №i до устройства фазирования и автосопровождения УФА. Далее, Дtп – время подставки, которое выбирается так, чтобы момент времени k-го импульса дискретизации на всех антеннах наступил позже k-го импульса дискретизации генератора, то есть из условия Дtzik>0. Это условие выполняется всегда, если время подставки Дtп выбирается из условия

Дtп>Дtфmax – Дtфmin + Дtрmax+ Дtоткл + ДtАЦП, (2)

где Дtфmax и Дtфmin – максимальное и минимальное время распространения фронта волны сигнала в фидерах антенной решётки, соответственно, Дtрmax – максимально возможное время распространения фронта волны сигнала в свободном пространстве по поперечнику антенной решётки, Дtоткл – время отклонения момента времени взятия отсчёта в отрицательную и в положительную сторону для формирования сигналов автосопровождения относительно времени взятия отсчёта в информационном канале, ДtАЦП – время формирования отсчёта на АЦП.

В одном канале автосопровождения каждой квадратуры i-й антенны последовательности импульсов дискретизации задерживают на время Дtоткл меньшее, чем задержка импульсов дискретизации в соответствующем информационном канале Дtzik, то есть задерживают на время

ДtzikАС1 =Дtzik – Дtоткл = Дtсi0k+ Дtфi – Дtф0 + Дtп – Дtоткл , (3)

а во втором канале автосопровождения этой же квадратуры этой же i-й антенны последовательности импульсов дискретизации задерживают на время Дtоткл большее, чем задержка импульсов дискретизации в соответствующем информационном канале Дtzi, то есть задерживают на время

ДtzikАС2 =Дtzik + Дtоткл = Дtсi0k+ Дtфi – Дtф0 + Дtп + Дtоткл . (4)

Поскольку в соответствии с фиг. 2 отсчёт в информационном канале каждой антенны берут спустя одно и то же для всех антенн время подставки Дtп после прихода на устройство фазирования и автосопровождения (УФА) одного и того же фронта волны принимаемого сигнала в разные моменты времени для разных антенн tУФАi, то отсчёты, взятые для разных антенн в моменты времени tk + Дtzi, также относятся к одному и тому же фронту волны принимаемого сигнала, приходящему на фазовые центры антенн и на УФА позже на время Дtп . То есть, если значение сигнала, приходящего в моменты времени tвik на фазовые центры антенн, равно S(t), тогда значение этого сигнала (назовём его синусным квадратурным сигналом), приходящего в моменты времени tУФАik на УФА, равно

Si(t) = Ki·S(t), (5)

где Ki – коэффициент передачи тракта i-й антенны от фазового центра до УФА.

Если значение сигнала S(t), пропущенного через фазовращатель на 90° в моменты времени tвik, равно S90(t), то значение этого косинусного квадратурного сигнала, приходящего в моменты времени tУФАik на УФА, будет равно

S90i(t) = Ki· S90(t). (6)

Таким образом, из сигнала i-й антенны Si(t), i = 0, … , N, в дискретные моменты времени tik = tГk + Дtzik= tУФАik+ Дtп формируют отсчёты двух квадратур информационного канала:

Sik = Si(t + Дtп) = Ki·S(t + Дtп) (7)

S90ik = S90i(t + Дtп) = Ki· S90(t + Дtп) (8)

Из (7) и (8) видим, что в идеале при одинаковых коэффициентах передачи Ki в приёмных трактах разных антенн и при отсутствии шумов соответствующие квадратурные отсчёты сигналов в информационных каналах разных антенн для одного фронта волны будут одинаковыми.

В дискретные моменты времени tikАС1 = tГk + ДtzikАС1 = tГk + Дtzik – Дtоткл= tУФАik + Дtп – Дtоткл для каждой квадратуры формируют отсчёты канала автосопровождения с опережением соответствующего информационного канала:

Sik– = Si(t + Дtп – Дtоткл) = Ki·S(t + Дtп – Дtоткл) (9)

S90ik– = S90i(t + Дtп – Дtоткл) = Ki·S90(t + Дtп – Дtоткл) (10)

Наконец, в дискретные моменты времени tikАС2 = tГk + ДtzikАС2 = tГk + Дtzik + Дtоткл= tУФАik + Дtп + Дtоткл для каждой квадратуры формируют отсчёты канала автосопровождения с отставанием от соответствующего информационного канала:

Sik+ = Si(t + Дtп + Дtоткл) = Ki·S(t + Дtп + Дtоткл) (11)

S90ik+ = S90i(t + Дtп + Дtоткл) = Ki·S90(t + Дtп + Дtоткл) (12)

Из (9) ÷ (12) видим, что в идеале при одинаковых коэффициентах передачи Ki в приёмных трактах разных антенн и при отсутствии шумов отсчёты сигналов в соответствующих каналах автосопровождения (с отставанием или с опережением) разных антенн для одного фронта волны также будут одинаковыми.

Сформированные цифровые (дискретные) отсчёты принятых сигналов от каждой антенны по каждому из шести каналов (двум информационным (синусному и косинусному) и четырём каналам автосопровождения (двум синусным с опережением и отставанием и двум косинусным с опережением и отставанием) записывают каждый в свой соответствующий индексированный массив памяти в ячейку с соответствующим текущим индексом k, относящимся к текущему фронту волны сигнала.

С задержкой от k-го импульса дискретизации на задающем генераторе, достаточной для прихода сигнала от антенны с наибольшим запаздыванием, в синусном и косинусном информационном канале выбирают из соответствующих массивов и суммируют цифровые (дискретные), соответственно, синусные и косинусные отсчёты по одному от каждой антенны с одним и тем же индексом k, относящимся к одному фронту волны сигнала. Затем определяют амплитуду и фазу отсчёта принятого информационного сигнала. Для синусного и косинусного информационного канала процесс суммирования информационных отсчётов антенн осуществляется в каждом интервале дискретизации Дtд.

В соответствии с (1) время задержки, гарантирующее момент начала времени суммирования отсчётов антенн одного фронта после прихода этого фронта от антенны с наибольшим запаздыванием, выбирается из условия:

Дtz∑ > Дtрmax+ Дtфmax – Дtфmin + Дtп (13)

В соответствии с (2) это условие эквивалентно следующему условию:

Дtz∑> 2·Дtп – Дtоткл – ДtАЦП (14)

По аналогии с условием (13) для начала обработки отсчётов в четырёх каналах автосопровождения в соответствии с (4) должна быть обеспечена задержка формирования отсчёта относительно k-го импульса дискретизации на задающем генераторе исходя из условия:

ДtzАС> Дtрmax+ Дtфmax – Дtфmin + Дtп + Дtоткл, (15)

что с учётом (2) эквивалентно условию:

ДtzАС> 2·Дtп – ДtАЦП . (16)

Поскольку время отклонения Дtоткл и время ДtАЦП формирования сигнала в АЦП малы по сравнению с максимально возможным временем распространения фронта волны сигнала в свободном пространстве по поперечнику антенной решётки Дtрmax, то в соответствии с (13) и (15) значение задержки времени начала обработки отсчётов одного фронта волны в информационных каналах ДtzобрИ и в каналах автосопровождения ДtzобрАС может быть установлено исходя из одного и того же условия:

ДtzобрИ> 2·Дtп (17)

ДtzобрАС> 2·Дtп

Вместе с тем, следует отметить, что обработка в информационном контуре сводится к простому сложению дискретных отсчётов, относящихся к одному фронту волны принимаемого сигнала, что требует времени ДtобрИ существенно меньше периода дискретизации сигнала Дtд, тогда как на каждом шаге автосопровождения необходимо выполнить достаточно сложные вычисления, которые могут потребовать времени обработки ДtобрАС существенно большего, чем период дискретизации Дtд, однако и динамика углового перемещения КА на несколько порядков медленнее динамики изменения передаваемых информационных сигналов.

Обработку значений отсчётов в каналах автосопровождения осуществляют с периодом времени TАС, который выбирают из условия:

TАС > ДtобрАС (18)

и составляет

MдАС = (TАС/Дtд) (19)

периодов дискретизации. Поскольку процесс углового движения КА намного медленнее процесса изменения радиосигнала, то всегда выполняются условия TАС>>Дtд и MдАС>>1, чтобы успеть рассчитать скорректированные цифровые сигналы автосопровождения антенн.

На j-м шаге автосопровождения обрабатывают отсчёты каналов автосопровождения с номером k = (ДtzобрИ /Дtд) + j·(TАС/Дtд).

Обработка состоит в следующем:

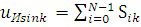

1) Определяют сумму значений информационных сигналов, соответственно, синусной и косинусной квадратур всех антенн решётки:

(20)

(20)

(21)

(21)

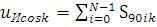

2) Определяют фазу информационного сигнала решётки:

(22)

(22)

3) Для каждой i-й антенны находят разность значений отсчётов для синусной и косинусной квадратур в каналах автосопровождения, взятых с отклонением в отрицательную и в положительную сторону относительно k-го отсчёта информационного канала, и получают значения разностного сигнала для синусной и косинусной квадратуры i-й антенны:

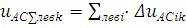

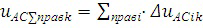

ДuАСik = Sik– – Sik+ (23)

ДuАС90ik = S90ik– – S90ik+ (24)

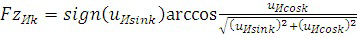

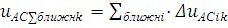

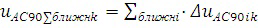

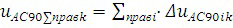

4) Определяют сумму значений разностных сигналов синусной и косинусной квадратур антенн ближней к КА части антенного поля относительно фазового центра решётки:

(25)

(25)

(26)

(26)

5) Определяют сумму значений разностных сигналов синусной и косинусной квадратур антенн дальней к КА части антенного поля относительно фазового центра решётки:

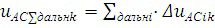

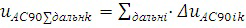

(27)

(27)

(28)

(28)

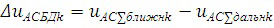

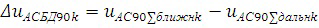

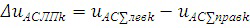

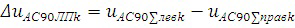

6) Определяют значение разности суммарных значений разностных сигналов синусной и косинусной квадратур антенн ближней и дальней к КА частей антенного поля относительно фазового центра решётки:

(29)

(29)

(30)

(30)

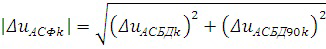

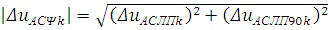

5) Определяют модуль управляющего сигнала наведения антенн решётки по углу места Φ:

(31)

(31)

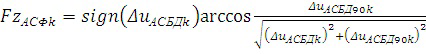

6) Определяют фазу управляющего сигнала наведения антенн решётки по углу места Φ:

(32)

(32)

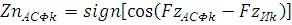

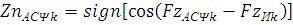

7) Определяют знак управляющего сигнала наведения антенн решётки по углу места Φ:

(33)

(33)

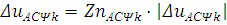

8) Управляющий сигнал наведения антенн решётки по углу места Φ со значением

(34)

(34)

преобразуют в аналоговую форму, фильтруют на фильтре нижних частот, усиливают на электромашинных усилителях и подают на приводы наведения антенн решётки по углу места.

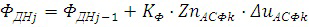

9) Определяют значение угла места диаграммы направленности антенн решётки на j-м шаге автосопровождения:

(35)

(35)

Здесь KΦ – коэффициент передачи цифрового контура управления по углу места.

Значение угла места в начале зоны радиовидимости определяют по принятой технологии проведения сеансов связи с КА. Как правило, по КА работают с горизонта по нулевой зоне радиовидимости, когда ΦДН0 = 0, однако за исходное может быть принято любое направление на КА в пределах зоны радиовидимости и, следовательно, любое значение исходного угла места от нулевого до наибольшего значения угла места на параметре по целеуказаниям на КА.

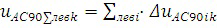

10) Определяют сумму значений разностных сигналов синусной и косинусной квадратур антенн левой части антенного поля относительно направления на КА от фазового центра решётки:

(36)

(36)

(37)

(37)

11) Определяют сумму значений разностных сигналов синусной и косинусной квадратур антенн правой части антенного поля относительно направления КА от фазового центра решётки:

(38)

(38)

(39)

(39)

12) Определяют значение разности суммарных значений разностных сигналов синусной и косинусной квадратур антенн левой и правой относительно КА и фазового цента решётки частей антенного поля:

(40)

(40)

(41)

(41)

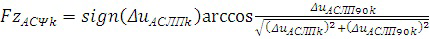

13) Определяют модуль управляющего сигнала наведения антенн решётки по азимуту Ш:

(42)

(42)

14) Определяют фазу управляющего сигнала наведения антенн решётки по азимуту Ш:

(43)

(43)

15) Определяют знак управляющего сигнала наведения антенн решётки по азимуту Ш:

(44)

(44)

16) Управляющий сигнал наведения антенн решётки по азимуту Ш со значением

(45)

(45)

преобразуют в аналоговую форму, фильтруют на фильтре нижних частот, усиливают на электромашинных усилителях и подают на приводы наведения антенн решётки по азимуту.

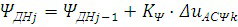

17) Определяют значение азимута диаграммы направленности антенн решётки на j-м шаге автосопровождения:

(46)

(46)

Здесь KΨ – коэффициент передачи цифрового контура управления по азимуту. Исходное значение азимута определяют по целеуказаниям на КА.

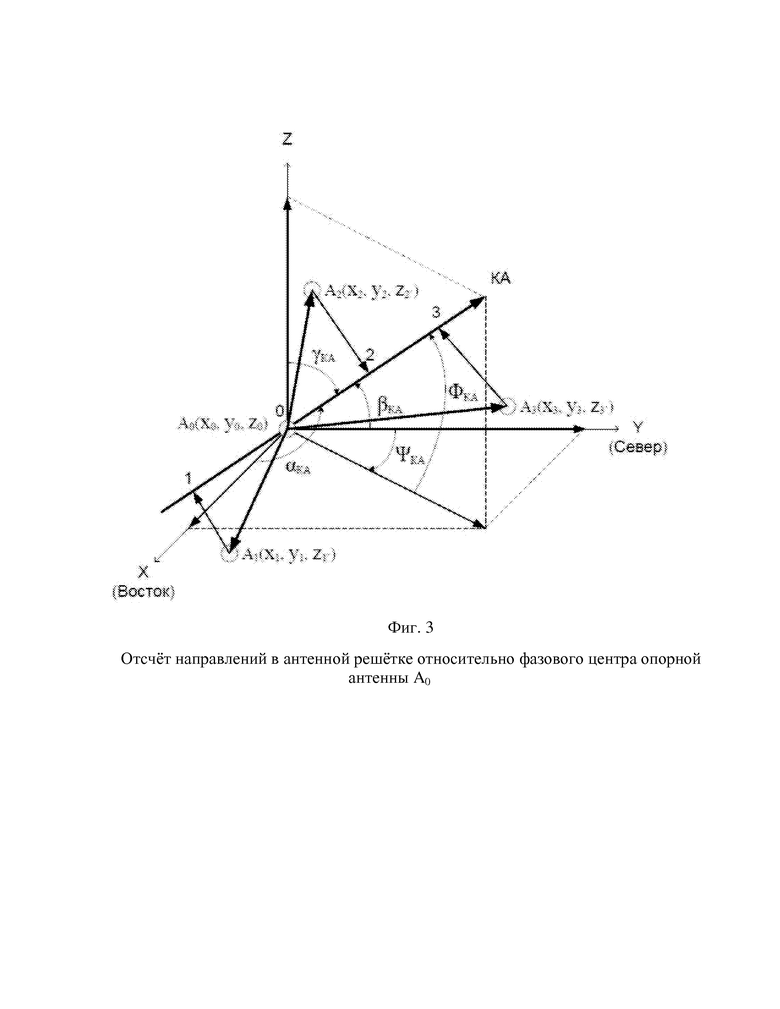

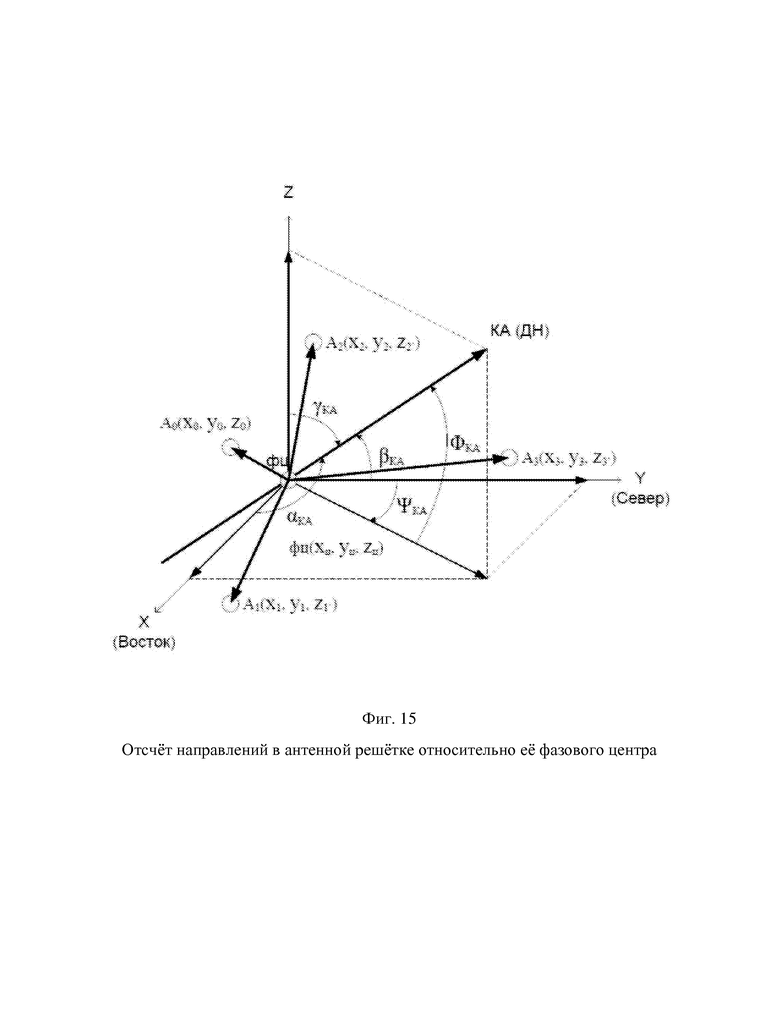

18) Определяют направляющие косинусы диаграмм направленности антенн антенной решётки на j-м шаге автосопровождения в местной системе координат, представленной на фиг. 3, по формулам

cos(αДНj) = cos(ЦДНj)·sin(ШДНj); (47)

cos(βДНj) = cos(ЦДНj)·cos(ШДНj); (48)

cos(γДНj) = sin(ЦДНj) (49)

19) Определяют разность хода лучей с направления диаграммы направленности антенн на j-м шаге автосопровождения между антеннами №i (Аi) и опорной антенной № 0 (А0) по формуле:

ΔRi0j = Li0·cos(∠Аi-0-ДНj)=

= Li0·[cos(αi0)·cos(αДНj) + cos(βi0)·cos(βДНj) + cos(γi0)·cos(γДНj)] (50)

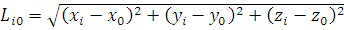

Здесь Li0 – расстояние между фазовыми центрами антенн Аi и А0, cos(αi0), cos(βi0), cos(γДНj) – направляющие косинусы векторов от опорной антенны А0 к антенне Аi, рассчитываются по формулам:

(51)

(51)

cos(αi0) = (xi – x0)/Li0; (52)

cos(βi0) = (yi – y0)/Li0; (53)

cos(γi0) = (zi – z0)/Li0; (54)

где (xi, yi, zi) и (x0, y0, z0) – координаты фазовых центров антенн Аi и А0 в местной системе координат (см. фиг.3).

20) Определяют Дtсi0j – оценку сдвига по времени прихода радиосигнала между антеннами Аi и А0 по формуле:

Дtсi0j = ΔRi0j/c, (55)

где c – скорость света в свободном пространстве.

21) Заменяют на регистрах предложенного устройства фазирования и автосопровождения ЦАР цифровые сигналы сдвига по времени прихода радиосигнала между антеннами Аi и А0 со значениями Дtсi0j-1 на сформированные на j-м шаге автосопровождения цифровые сигналы со значениями Дtсi0j для работы УФА на (j+1)-м шаге автосопровождения.

Поскольку значения сигналов рассогласования из-за неточного, но синфазного наведения на антеннах, находящихся по разные стороны относительно фазового центра решётки, будут иметь противоположный знак, то при вычитании абсолютные значения этих сигналов будут складываться, увеличивая значение результирующего сигнала рассогласования.

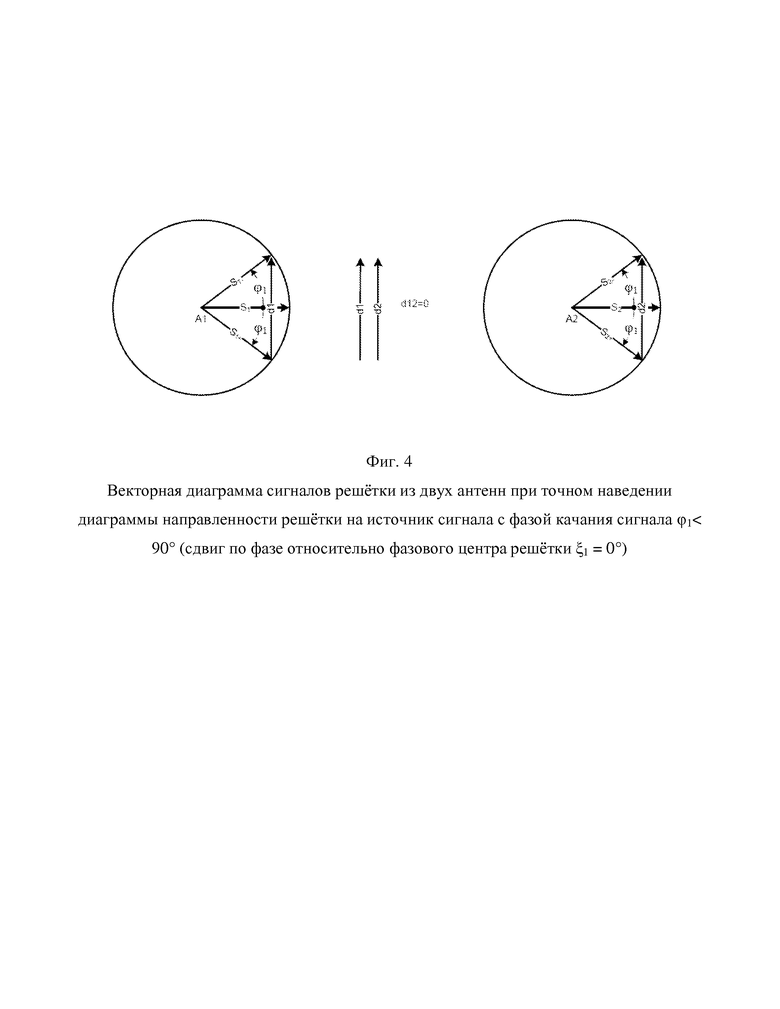

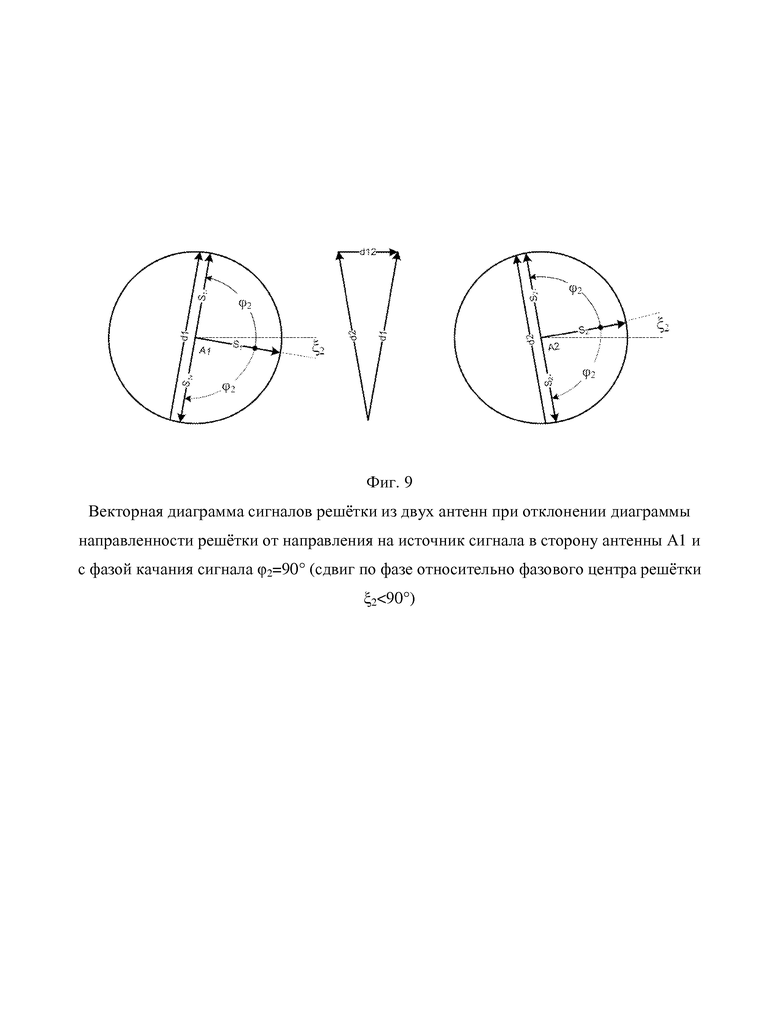

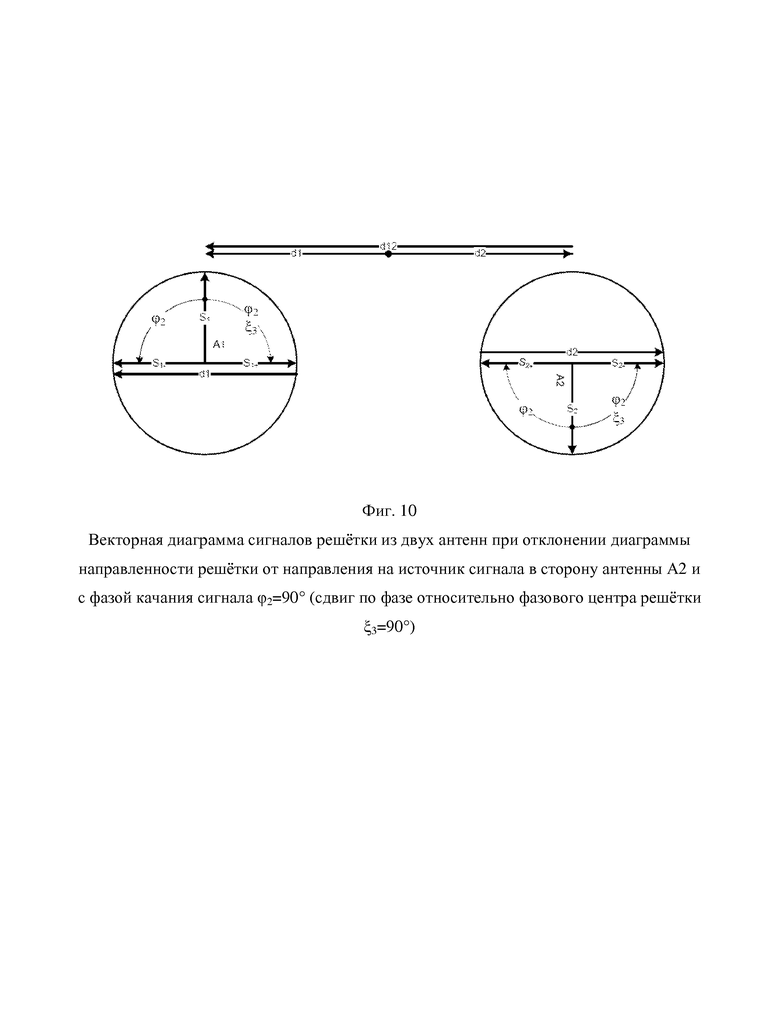

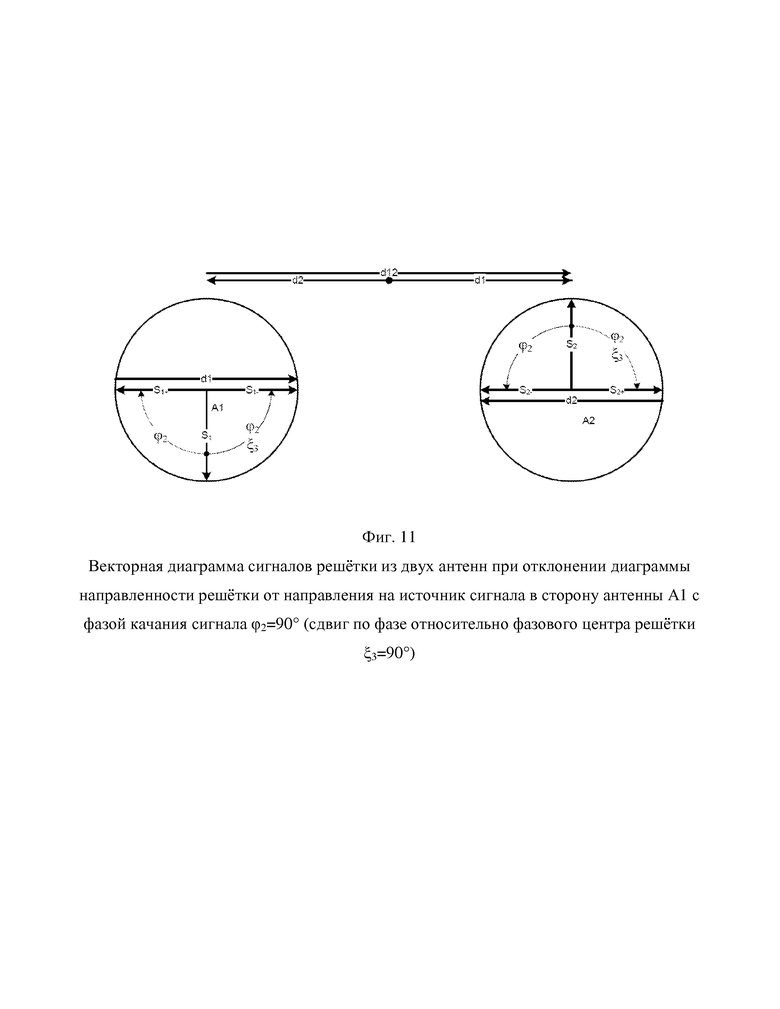

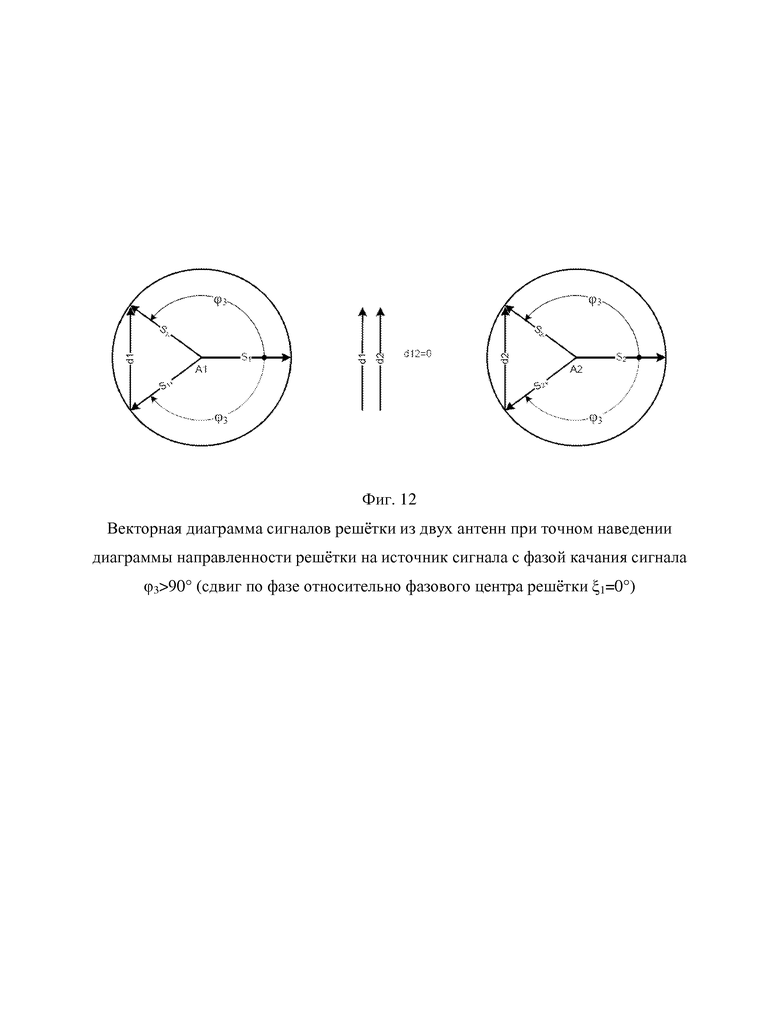

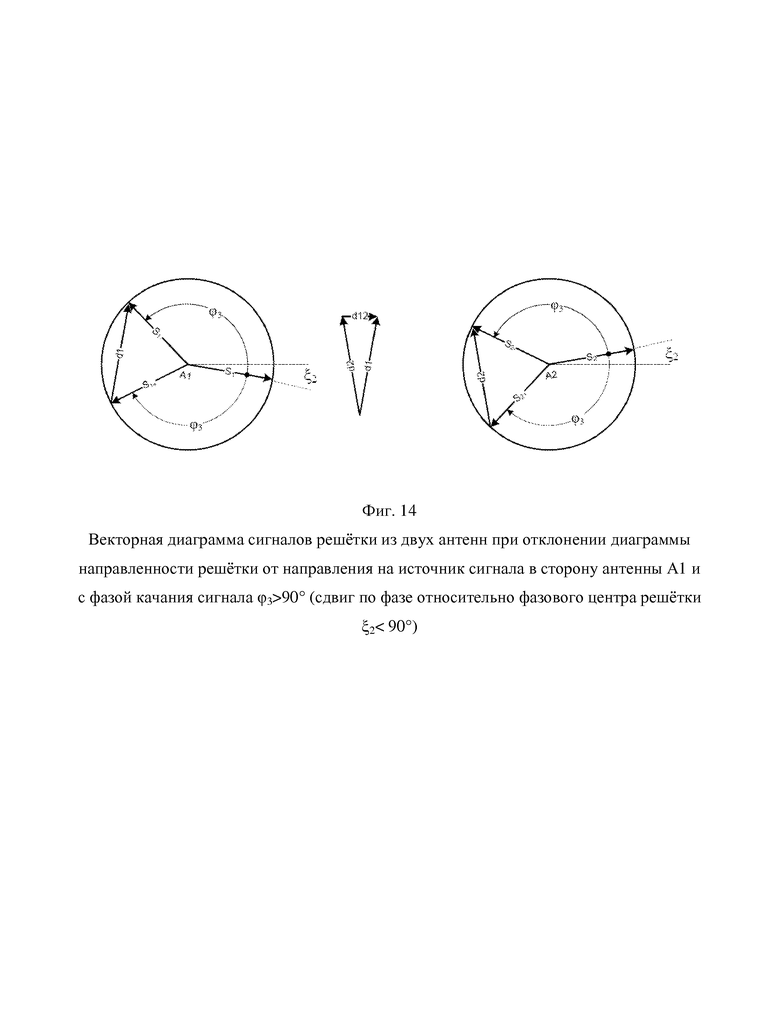

Сущность предлагаемого равносигнально-разностного метода автосопровождения в цифровой антенной решётке поясняется векторными диаграммами на фиг. 4-14 для гармоник принимаемых сигналов.

Допустим, осуществляется приём гармонического сигнала S решёткой из двух антенн А1 и А2. В информационном тракте антенна А1 принимает сигнал S1, а антенна А2 – сигнал S2. В тракте автосопровождения сигнал от источника принимают с упреждением и с запаздыванием относительно информационного тракта на некоторый интервал времени отклонения Дtоткл.

При точном наведении обеих антенн на источник сигнала сдвиг по фазе относительно фазового центра решётки принимаемых антеннами А1 и А2 сигналов S1 и S2 будет равен нулю и при времени отклонения Дtоткл взятия отсчётов в каналах автосопровождения относительно информационного канала таком, что сдвиг по фазе сигналов в каналах автосопровождения |ц1|< 90°, векторная диаграмма сигналов на антеннах А1 и А2 будет иметь вид, представленный на фиг. 4. Здесь d1 – вектор разности сигнала S1-, принятого антенной А1 по каналу автосопровождения с упреждением на время Дtоткл относительно сигнала S1, принятого антенной А1 в информационном тракте, и сигнала S1+, принятого антенной А1 по каналу автосопровождения с отставанием на время Дtоткл относительно сигнала S1, принятого антенной А1 в информационном тракте. Аналогичное значение имеет вектор d2 разности соответствующих сигналов S2- и S2+, принятых в канале с опережением и с отставанием в тракте автосопровождения антенны А2. Очевидно, что нулевое отклонение диаграмм направленности антенн от направления на источник сигнала для разностных сигналов отклонения по времени взятия отсчётов является равносигнальным, разностные сигналы d1 и d2 равны между собой, а их разность d12 = d1 – d2, являющаяся сигналом наведения антенн, равна нулю.

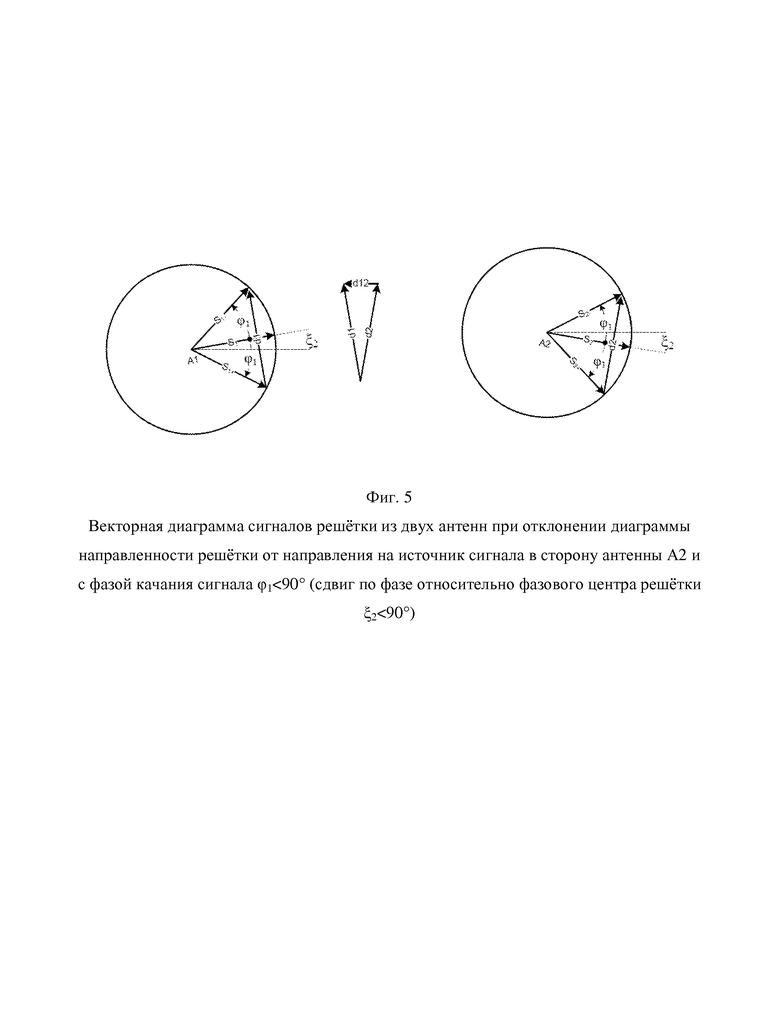

При том же времени отклонения взятия отсчётов сигналов Дtоткл в трактах автосопровождения антенн А1 и А2 и при некотором отклонении диаграммы направленности решётки от направления на источник сигнала в сторону антенны А2, приводящем к сдвигу фазы принимаемого сигнала в информационном канале антенны А1 на угол + ξ2 , а в антенне А2 на угол – ξ2 относительно фазового центра решётки, где ξ2< 90°, имеем векторную диаграмму сигналов на фиг. 5, а при таком же отклонении диаграммы направленности решётки в сторону антенны А1 имеем векторную диаграмму сигналов на фиг. 6. В этих случаях вычитание разностных сигналов d1 и d2 формирует уже ненулевой сигнал наведения антенн d12, знак которого зависит от направления отклонения диаграммы направленности решётки.

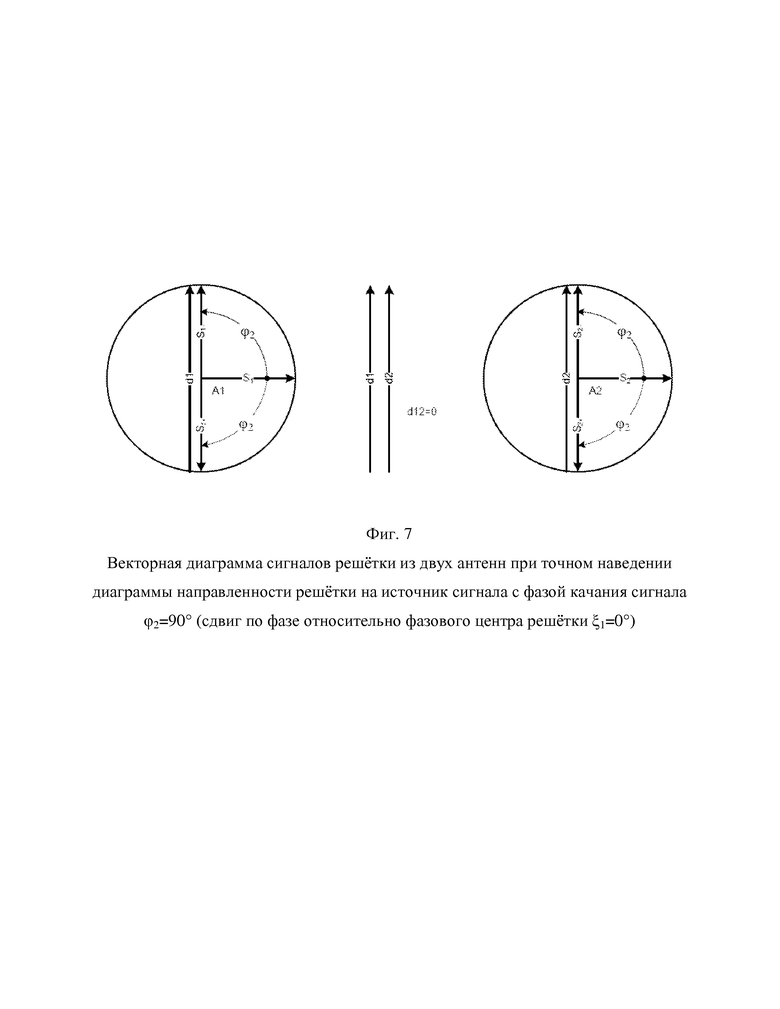

Величина сигнала наведения антенн d12 при одном и том же отклонении диаграммы направленности решётки ξ2 от источника сигнала определяется временем отклонения взятия отсчётов сигналов Дtоткл в трактах автосопровождения антенн А1 и А2 и достигает максимума при таком значении времени отклонения Дtоткл , когда сдвиг по фазе сигналов в каналах автосопровождения |ц2| = 90°, как показано на фиг. 7, 8 и 9.

Максимум максиморум сигнала наведения антенн d12 достигает учетверённого значения принимаемого сигнала одной антенной S (без учёта ослабления диаграммой направленности парциальной антенны), когда это отклонение диаграммы направленности решётки приведёт к сдвигу фазы принимаемого сигнала в информационном канале антенн А1 и А2 относительно фазового центра решётки на угол ξ3 = 90°, как это показано на фиг. 10 и 11. Этот гипотетический случай, представляющий чисто теоретический интерес, определяет динамический диапазон сигнала наведения антенн в предлагаемом равносигнально-разностном методе, а именно |d12|maxmax=4|S|.

На фиг. 12, 13 и 14 представлены векторные диаграммы сигналов антенн в случае, когда время отклонения взятия отсчётов сигналов Дtоткл в трактах автосопровождения имеет такое значение, что сдвиг по фазе сигналов в каналах автосопровождения относительно информационного канала 90°<|ц3|<180°. Видим, что при превышении сдвигом фазы относительно фазового центра решётки в каналах автосопровождения значения 90° величина сигнала наведения антенн d12 начинает уменьшаться, обращаясь в ноль при сдвиге в 180°. Это позволяет дать следующую рекомендацию по выбору величины времени отклонения взятия отсчётов сигналов Дtоткл в трактах автосопровождения.

Время отклонения взятия отсчётов сигналов Дtоткл в трактах автосопровождения следует выбирать таким образом, чтобы гармоники сигнала в средней части спектра fс для каналов автосопровождения имели сдвиг по фазе относительно соответствующих гармоник в средней части спектра информационного канала примерно на ± 90°, то есть исходя из условия 2·р·fс·Дtоткл = р/2. Тогда векторные диаграммы для гармоник в средней части спектра принимаемого широкополосного сигнала будут иметь вид, представленный на фиг. 7-9, векторные диаграммы для гармоник в нижней части спектра принимаемого широкополосного сигнала будут иметь вид, представленный на фиг. 4-6, наконец, векторные диаграммы для гармоник в верхней части спектра принимаемого широкополосного сигнала будут иметь вид, представленный на фиг. 12-14.

Важно, что при таком выборе времени отклонения Дtоткл результирующие разностные сигналы от всех гармоник спектра принимаемого радиосигнала имеют одинаковую полярность и суммируются по абсолютной величине при формировании результирующего сигнала наведения антенн по предлагаемому равносигнально-разностному методу.

Принадлежность антенны к ближней или дальней, левой или правой части антенного поля относительно фазового центра решётки, используемую в вычислениях по формулам (25)÷(32), (36)÷(43), определяют следующим образом.

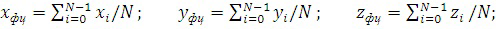

1) Определяют координаты фазового центра цифровой антенной решётки по формулам

(56)

(56)

Здесь N – количество антенн в решётке антенного поля; (xi, yi, zi) – координаты фазового центра антенны Аi в местной системе координат (см. фиг.3).

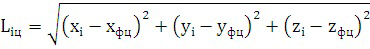

2) Определяют расстояние от фазового цента (ФЦ) ЦАР до каждойантенны Аi:

(57)

(57)

3) Определяют направляющие косинусы векторов из фазового центра ЦАР на каждую антенну Аi в местной системе координат (фиг. 15):

cos(αiц) = (xi – xфц)/Liц; (58)

cos(βiц) = (yi – yфц)/Liц; (59)

cos(γiц) = (zi – zфц)/Liц; (60)

4) Определяют направляющие косинусы проекций на горизонтальную плоскость векторов из фазового центра ЦАР на каждую антенну Аi :

cos(αiцГ) = (xi – xфц)/LiцГ = (xi – xфц)/(Liц · sin(γiц)) = cos(αiц)/sin(γiц); (61)

cos(βiцГ) = (yi – yфц)/ LiцГ = (yi – yфц)/ (Liц · cos(γiц)) = cos(βiц)/sin(γiц); (62)

5) Определяют направляющие косинусы проекции на горизонтальную плоскость вектора диаграммы направленности отдельной антенны в текущий момент времени:

cos(αДНГj) = sin(ШДНj); (63)

cos(βДНГj) = cos(ШДНj); (64)

6) В горизонтальной плоскости для каждой антенны определяют косинус разности азимутов направления на антенну и текущего направления диаграммы направленности антенны:

cos[∠(азимут ДНj – азимутАi )] = cos(αiцГ)·cos(αДНГj) + cos(βiцГ)·cos(βДНГj)=

= cos(αiц)/sin(γiц)·sin(ШДНj)+ cos(βiц)/sin(γiц)·cos(ШДНj); (65)

7) Определяют условие «ближе» – «дальше» для каждой антенны в текущий момент времени:

если cos(∠(азимут ДНj – азимут Аi)) > 0, то Аi ближе к КА, чем ФЦ; (66)

если cos(∠(азимут ДНj – азимут Аi)) < 0, то Аi дальше от КА, чем ФЦ. (67)

8) В горизонтальной плоскости для каждой антенны определяют синус разности азимутов направления на антенну и текущего направления диаграммы направленности антенны:

sin[∠(азимут ДНj – азимут Аi)] = – cos{∠[(азимут ДН j+р/2) – азимут Аi]} =

= – { cos(αiц)/sin(γiц)·sin(ШДНj+р/2)+ cos(βiц)/sin(γiц)· cos(ШДНj+р/2)} =

= –cos(αiц)/sin(γiц)·cos(ШДНj) + cos(βiц)/sin(γiц)· sin(ШДНj) (68)

9) Определяют условие «справа» – «слева» для каждой антенны в текущий момент времени:

Если sin(∠(азимут ДНj– азимут Аi)) > 0, то Аi левее, чем ФЦ; (69)

Если sin(∠(азимут ДНj – азимут Аi)) < 0, то Аi правее, чем ФЦ. (70)

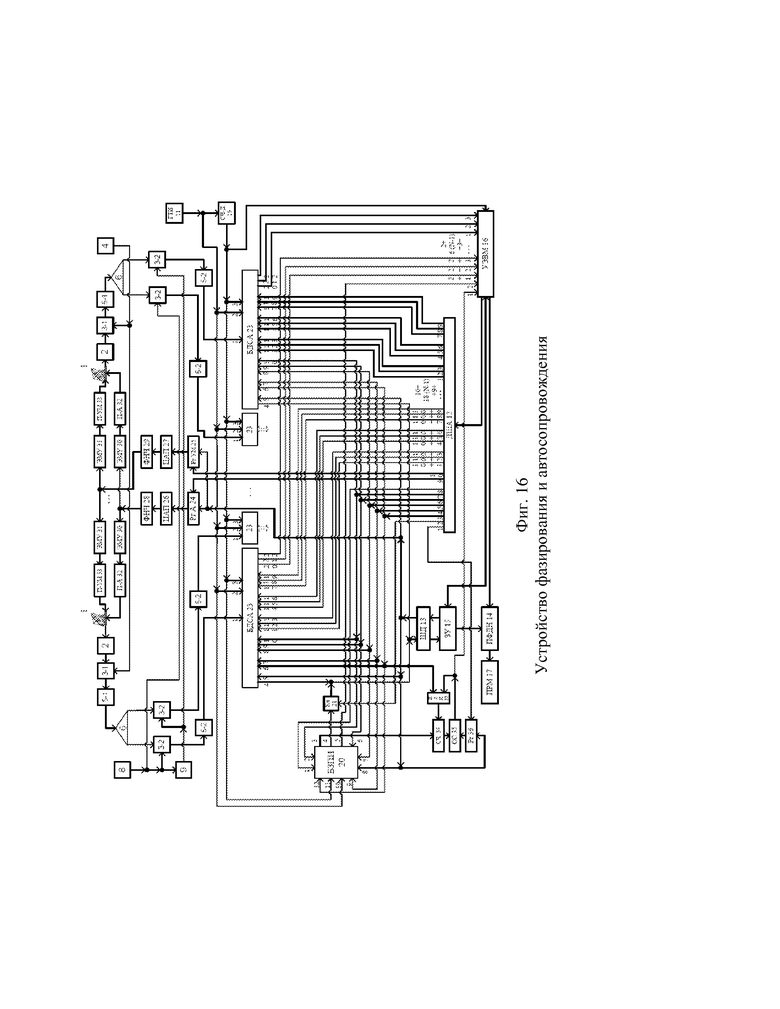

Предложено устройство фазирования и автосопровождения неэквидистантной цифровой антенной решётки приёма широкополосных сигналов, содержащее совокупность трактов приёма сигналов от антенн и автосопровождения антенн, являющихся частью антенной решётки.

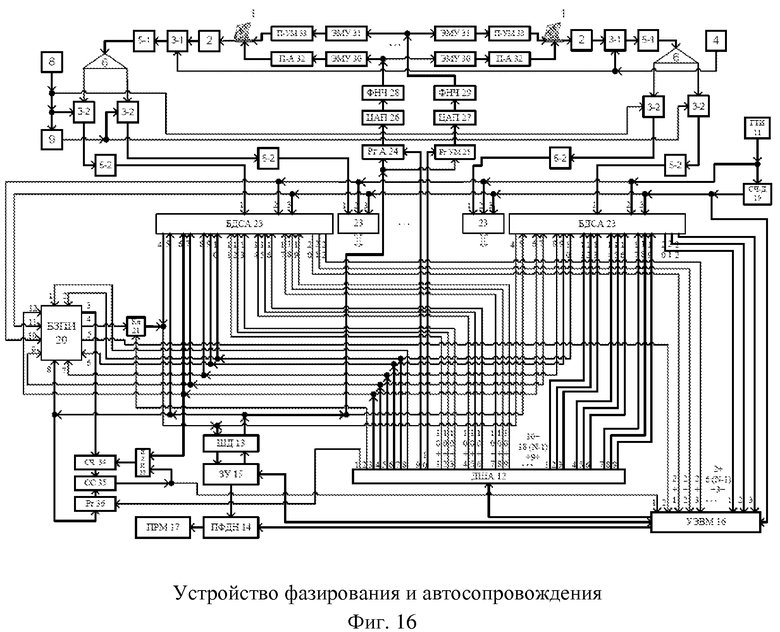

Схема предложенного устройства фазирования и равносигнально-разностного автосопровождения неэквидистантной цифровой антенной решётки приёма широкополосных сигналов приведена на фиг. 16, где: 1 – приёмная антенна; 2 – входной малошумящий усилитель (МШУ) и фидер до смесителя; 3-1 – смеситель первой промежуточной частоты (ПЧ-1); 3-2 – смеситель второй промежуточной частоты (ПЧ-2); 4 – первый гетеродин; 5-1 – усилитель ПЧ-1с полосовым фильтром (УПЧ-ПФ-1); 5-2 – усилитель ПЧ-2 с полосовым фильтром (УПЧ-ПФ-2); 6 – делитель; 8 – второй гетеродин; 9 – постоянный фазовращатель на 90°; 11 – генератор тактовых импульсов (ГТИ); 12 – дешифратор адресного сигнала; 13 – шина данных; 14 – процессор формирования диаграммы направленности (ПФДН); 15 – запоминающее устройство (ЗУ); 16 – управляющая ЭВМ (УЭВМ); 17 – приёмник. В этом предложенном устройстве фазирования и автосопровождения устранены (см. фиг. 1) синхронные фазовые детекторы – 7, функции устройства управления возложены на управляющую ЭВМ (УЭВМ) – 16 и введены: смесители ПЧ-2 – 3-2, усилители с фильтрами УПЧ-ПФ-2 – 5-2, счётчик-делитель – 19; блок задержки последовательности импульсов (БЗПИ) – 20; ключ сигнала индекса – 21; блоки дискретизации сигнала антенны (БДСА) – 23; регистр сигнала наведения антенны по азимуту – 24; регистр сигнала наведения антенны по углу места - 25; цифро-аналоговый преобразователь сигнала наведения по азимуту – 26; цифро-аналоговый преобразователь сигнала наведения по углу места – 27; фильтр нижних частот сигнала наведения по азимуту – 28; фильтр нижних частот сигнала наведения по углу места – 29; электромашинные усилители наведения по азимуту – 30; электромашинные усилители наведения по углу места – 31; приводы наведения по азимуту – 32; приводы наведения по углу места – 33; счётчик периода автосопровождения – 34; схема сравнения периода автосопровождения – 35; регистр сигнала периода автосопровождения 36, схема ИЛИ 37.

Выход каждой антенны 1 соединён с входом соответствующего МШУ 2, выход каждого МШУ 2 соединён через фидер с сигнальным входом соответствующего смесителя 3-1, гетеродинный вход которого соединён с выходом первого гетеродина 4, выход каждого смесителя 3-1 соединён с входом соответствующего УПЧ-ПФ-1 5-1, выход которого соединён с входом соответствующего делителя 6, первый выход каждого делителя 6 соединён с сигнальным входом первого, а второй выход делителя соединён с сигнальным входом второго из соответствующей пары смесителей 3-2, причём гетеродинный вход каждого первого в соответствующей паре смесителя 3-2 соединён с выходом второго гетеродина 8, а гетеродинный вход каждого второго в соответствующей паре смесителя 3-2 соединён с выходом постоянного фазовращателя на 90° 9, вход которого соединён с выходом второго гетеродина 8, выход каждого смесителя 3-2 с сигнальным входом 1 соответствующего блока дискретизации сигнала антенны (БДСА) 23.

Выход ГТИ 11 соединён со счётным входом счётчика-делителя 19, с входом импульсов фазирования 10 блока задержки последовательности импульсов БЗПИ 20 и с входом импульсов фазирования 2 каждого блока дискретизации сигнала антенны (БДСА) 23; выход счётчика-делителя 19 соединён с входом синхронизации управляющей ЭВМ 16, с входом 11 импульсов дискретизации блока задержки последовательности импульсов БЗПИ 20 и с входом импульсов дискретизации 3 каждого блока дискретизации сигнала антенны БДСА 23. Выход ключа 21 и выход 4 каждого БДСА соединён с входом ввода данных шины данных 13.

Первая адресная шина УЭВМ 16 соединена с входом дешифратора 12. Шина адреса, данных и управления УЭВМ 16 соединена с шиной адреса, данных и управления запоминающего устройства ЗУ 15. Выход управления УЭВМ 16 соединён с входом управления процессора формирования диаграммы направленности ПФДН 14. Вход данных ПФДН 14 соединён с первым выходом данных ЗУ 15, выход данных ПФДН 14 соединён с входом данных приёмника 17. Второй выход данных ЗУ 15 соединён с входом вывода данных шины 13, выход ввода данных которой соединён с входом данных ЗУ 15. Выход вывода данных шины данных 13 соединён с входом 8 шины ввода данных БЗПИ 20, с входом данных 5 каждого БДСА 23, с входом данных регистра сигнала периода автосопровождения 36, с входом данных регистра сигнала наведения антенн по азимуту 24 и с входом данных регистра сигнала наведения антенн по углу места 25.

Первый выход дешифратора адреса (ДША) 12 соединён с управляющим входом регистра сигнала периода автосопровождения 36; второй выход ДША 12 соединён с управляющим входом ключа 21; третий выход ДША 12 соединён с входом 12 сигнала начала сеанса БЗПИ 20, со вторым входом схемы ИЛИ 37 и с входом 6 сигнала начала сеанса каждого БДСА 23; 4-й выход ДША 12 соединён с входом 9 сигнала конца сеанса БЗПИ 20 и с входом 7 сигнала конца сеанса каждого БДСА 23; 5-й выход ДША 12 соединён с входом 7 сигнала ввода кода периода дискретизации БЗПИ 20 и с входом 8 сигнала ввода кода периода дискретизации каждого БДСА 23; 6-й выход ДША 12 соединён с входом 6 сигнала ввода кода задержки АЦП БЗПИ 20 и с входом 9 сигнала ввода кода задержки АЦП каждого БДСА 23; 7-й выход ДША 12 соединён с входом 2 сигнала ввода кода времени запрета импульса БЗПИ 20 и с входом 10 сигнала ввода кода времени запрета импульса каждого БДСА 23; 8-й выход ДША 12 соединён с входом 1 сигнала ввода кода задержки БЗПИ 20; 9-й выход ДША 12 соединён с управляющим входом регистра сигнала наведения антенн по азимуту 24; 10-й выход ДША 12 соединён с управляющим входом регистра сигнала наведения антенн по углу места 25; выход [10+18·i+9·(j–1)+1] ДША 12 соединён с входом 11 сигнала вывода цифрового сигнала номера отсчёта информационного канала j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1; выход [10+18·i+9·(j–1)+2] ДША 12 соединён с входом 12 сигнала вывода цифрового сигнала отсчёта информационного канала j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1; выход [10+18·i+9·(j–1)+3] ДША 12 соединён с входом 13 сигнала ввода кода задержки информационного канала j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1; выход [10+18·i+9·(j–1)+4] ДША 12 соединён с входом 14 сигнала вывода цифрового сигнала номера отсчёта канала автосопровождения с опережением j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1; выход [10+18·i+9·(j–1)+5] ДША 12 соединён с входом 15 сигнала вывода цифрового сигнала отсчёта канала автосопровождения с опережением j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1; выход [10+18·i+9·(j–1)+6] ДША 12 соединён с входом 16 сигнала ввода кода задержки канала автосопровождения с опережением j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1; выход [10+18·i+9·(j–1)+7] ДША 12 соединён с входом 17 сигнала вывода цифрового сигнала номера отсчёта канала автосопровождения с отставанием j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1; выход [10+18·i+9·(j–1)+8] ДША 12 соединён с входом 18 сигнала вывода цифрового сигнала отсчёта канала автосопровождения с отставанием j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1; выход [10+18·i+9·(j–1)+9] ДША 12 соединён с входом 19 сигнала ввода кода задержки канала автосопровождения с отставанием j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1.

Выход 3 задержанных импульсов дискретизации в БЗПИ 20 соединён со счётным входом счётчика периода автосопровождения 34, выход 4 сигнала номера отсчёта БЗПИ 20 соединён с входом данных ключа 21, выход 5 сигнала прерывания отсчёта БЗПИ 20 соединён со 2-м входом прерывания УЭВМ 16.

Выход счётчика периода автосопровождения 34 соединён с первым входом схемы сравнения периода автосопровождения 35, второй вход которой соединён с выходом регистра сигнала периода автосопровождения 36, а выход соединён с первым входом схемы ИЛИ 37 и с первым входом прерывания УЭВМ 16. Выход схемы ИЛИ 37 соединён с входом обнуления счётчика периода автосопровождения 34.

Выход 20 сигнала прерывания отсчёта информационного канала j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, соединён с входом[2+6·i+3·(j–1)+1] прерывания УЭВМ 16; выход 21 сигнала прерывания отсчёта канала автосопровождения с опережением j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, соединён с входом [2+6·i+3·(j–1)+2] прерывания УЭВМ 16; выход 22 сигнала прерывания отсчёта канала автосопровождения с отставанием j-го БДСА i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, соединён с входом [2+6·i+3·(j–1)+3] прерывания УЭВМ 16.

Выход регистра сигнала наведения антенн по азимуту 24 соединён с входом цифро-аналогового преобразователя (ЦАП) 26, выход которого соединён с входом фильтра низких частот ФНЧ 28. Выход регистра сигнала наведения антенн по углу места 25 соединён с входом ЦАП 27, выход которого соединён со ФНЧ 29. Выход ФНЧ 28 соединён с входом каждого электромашинного усилителя канала азимута ЭМУ 30. Выход ФНЧ 29 соединён с входом каждого электромашинного усилителя канала угла места ЭМУ 31. Выход каждого электромашинного усилителя канала азимута ЭМУ 30 соединён с входом привода по азимуту 32 соответствующей антенны 1. Выход каждого электромашинного усилителя канала угла места ЭМУ 31 соединён с входом привода по углу места 33 соответствующей антенны 1.

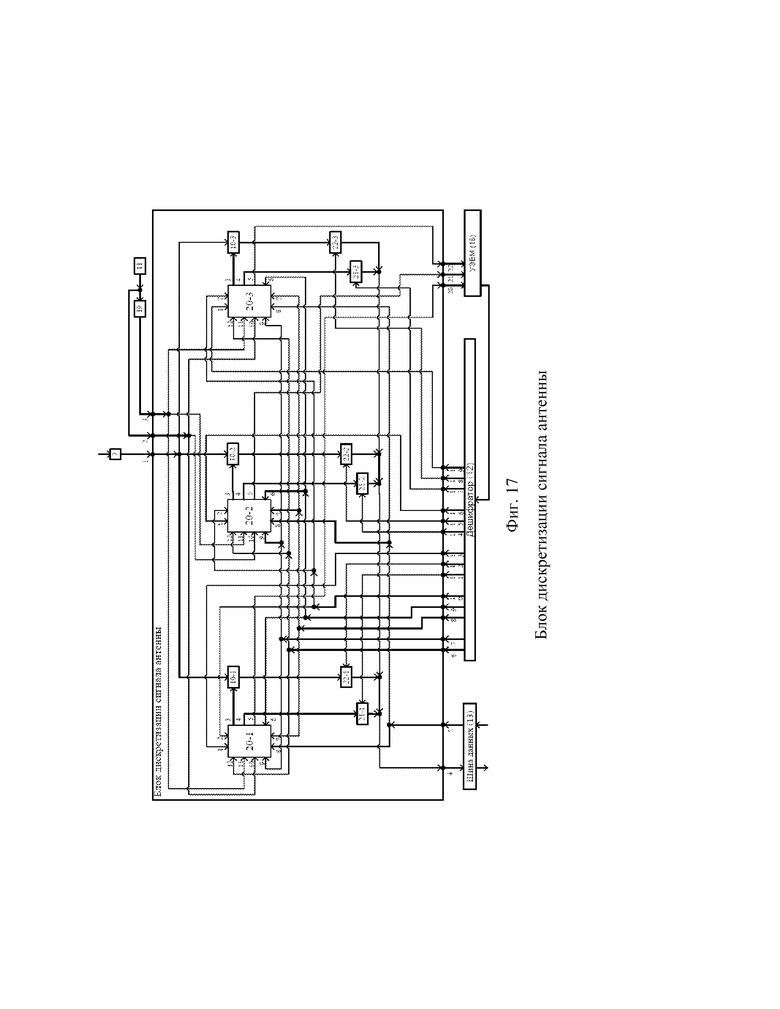

Схема блока дискретизации сигнала антенны 23 представлена на фиг. 17, где три канала дискретизации (информационный канал и два канала автосопровождения с дискретизацией с опережением и с отставанием) содержат три аналого-цифровых преобразователя 10-1, 10-2 и 10-3 по одному на каждый канал дискретизации, три блока задержки последовательности импульсов (БЗПИ) – 20-1, 20-2, 20-3 по одному на каждый канал дискретизации, три ключа сигнала индекса 21-1, 21-2, 21-3 по одному в каждом канале дискретизации и три ключа сигнала отсчёта 22-1, 22-2, 22-3 по одному в каждом канале дискретизации, причём сигнальный вход 1 БДСА 23 соединён с сигнальным входом каждого АЦП 10-1, 10-2, 10-3. Вход импульсов фазирования 2 в БДСА 23 соединён с входом импульсов фазирования 10 каждого БЗПИ 20-1, 20-2, 20-3. Вход импульсов дискретизации 3 в БДСА 23 соединён с входом 11 импульсов дискретизации каждого БЗПИ 20-1, 20-2, 20-3.

Выход 3 задержанных импульсов дискретизации каждого БЗПИ 20-1, 20-2, 20-3 соединён с входом импульсов дискретизации АЦП 10-1, 10-2, 10-3 соответствующего канала дискретизации БДСА. В каждом канале дискретизации выход соответствующего АЦП 10-1, 10-2 , 10-3 соединён с входом данных соответствующего ключа сигнала отсчёта 22-1, 22-2, 22-3, причём выход каждого из этих ключей соединён с выходом данных 4 БДСА.

В каждом БЗПИ 20-1, 20-2, 20-3 выход 4 сигнала номера отсчёта соединён с входом данных соответствующего ключа сигнала индекса 21-1, 21-2, 21-3, причём выход каждого из этих ключей соединён с выходом данных 4 БДСА.

Выход 5 сигнала прерывания отсчёта информационного канала БЗПИ 20-1 соединён с выходом 20 сигнала прерывания отсчёта информационного канала БДСА 23.

Выход 5 сигнала прерывания отсчёта канала автосопровождения с опережением БЗПИ 20-2 соединён с выходом 21 сигнала прерывания отсчёта канала автосопровождения с опережением БДСА 23.

Выход 5 сигнала прерывания отсчёта канала автосопровождения с отставанием БЗПИ 20-3 соединён с выходом 22 сигнала прерывания отсчёта канала автосопровождения с отставанием БДСА 23.

Вход данных 5 БДСА 23 соединён с входом 8 шины ввода данных каждого БЗПИ 20-1, 20-2, 20-3. Вход 6 сигнала начала сеанса БДСА 23 соединён с входом 12 сигнала начала сеанса БЗПИ 20-1, 20-2 и 20-3. Вход 7 сигнала конца сеанса БДСА 23 соединён с входом 9 сигнала конца сеанса БЗПИ 20-1, 20-2 и 20-3. Вход 8 сигнала ввода кода периода дискретизации БДСА 23 соединён с входом 7 сигнала ввода кода периода дискретизации БЗПИ 20-1, 20-2, 20-3. Вход 9 сигнала ввода кода задержки АЦП в БДСА 23 соединён с входом 6 сигнала ввода кода задержки АЦП в БЗПИ 20-1, 20-2, 20-3. Вход 10 сигнала ввода кода времени запрета импульса БДСА 23 соединён с входом 2 сигнала ввода кода времени запрета импульса БЗПИ 20-1, 20-2, 20-3.

Вход 11 сигнала вывода цифрового сигнала номера отсчёта информационного канала БДСА 23 соединён с управляющим входом ключа 21-1. Вход 12 сигнала вывода цифрового сигнала отсчёта информационного канала БДСА 23 соединён с управляющим входом ключа 22-1. Вход 13 сигнала ввода кода задержки информационного канала БДСА 23 соединён с входом 1 сигнала ввода кода задержки БЗПИ 20-1.

Вход 14 сигнала вывода цифрового сигнала номера отсчёта канала автосопровождения с опережением БДСА 23 соединён с управляющим входом ключа 21-2. Вход 15 сигнала вывода цифрового сигнала отсчёта канала автосопровождения с опережением БДСА 23 соединён с управляющим входом ключа 22-2. Вход 16 сигнала ввода кода задержки канала автосопровождения с опережением БДСА 23 соединён с входом 1 сигнала ввода кода задержки БЗПИ 20-2.

Вход 17 сигнала вывода цифрового сигнала номера отсчёта канала автосопровождения с отставанием БДСА 23 соединён с управляющим входом ключа 21-3. Вход 18 сигнала вывода цифрового сигнала отсчёта канала автосопровождения с отставанием БДСА 23 соединён с управляющим входом ключа 22-3. Вход 19 сигнала ввода кода задержки канала автосопровождения с отставанием БДСА 23 соединён с входом 1 сигнала ввода кода задержки БЗПИ 20-3.

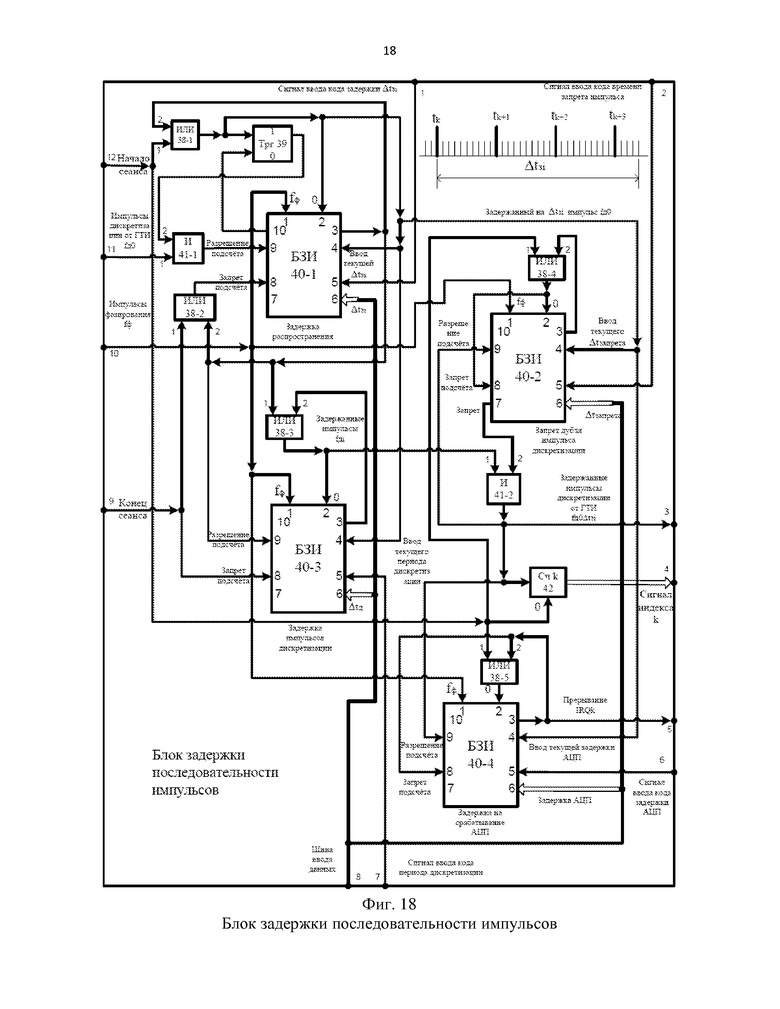

Схема блока задержки последовательности импульсов (БЗПИ) представлена на фиг. 18, где 38-1, 38-2, 38-3, 38-4, 38-5 – схемы ИЛИ, 39– триггер, 41-1, 41-2 – схемы И, 40-1, 40-2, 40-3, 40-4 – блоки задержки импульса, 42 – счётчик. Вход 1 сигнала ввода кода задержки БЗПИ соединён с входом 5 сигнала ввода новой задержки блока задержки импульсов (БЗИ) 40-1. Вход 2 сигнала ввода кода времени запрета импульса БЗПИ соединён с входом 5 сигнала ввода новой задержки БЗИ 40-2. Вход 6 сигнала ввода кода задержки АЦП в БЗПИ соединён с входом 5 сигнала ввода новой задержки БЗИ 40-4. Вход 7 сигнала ввода кода периода дискретизации БЗПИ соединён с входом 5 сигнала ввода новой задержки БЗИ 40-3. Вход 8 шины ввода данных БЗПИ соединён с входом 6 сигнала кода новой задержки блоков БЗИ 40-1, 40-2, 40-3, 40-4. Вход 9 сигнала конца сеанса БЗПИ соединён с входом 8 запрета подсчёта блока БЗИ 40-3, используемого для задержки импульсов дискретизации, и с первым входом схемы ИЛИ 38-2. Вход 10 импульсов фазирования БЗПИ соединён с входом 1 импульсов фазирования блоков БЗИ 40-1, 40-2, 40-3, 40-4. Вход 11 импульсов дискретизации БЗПИ соединён с первым входом схемы И 41-1. Вход 12 сигнала начала сеанса БЗПИ соединён с входом обнуления счётчика 42, с первыми входами схем ИЛИ 38-4, 38-5 и с первым входом схемы ИЛИ 38-1, выход которой соединён с входом импульса обнуления 2 БЗИ 40-1, с входом 4 сигнала ввода кода текущей задержки БЗИ 40-1, БЗИ 40-2, БЗИ 40-3, БЗИ 40-4 и с единичным входом триггера 39, единичный выход которого соединён со вторым входом схемы И 41-1, выход которой, в свою очередь, соединён с входом 9 входного импульса БЗИ 40-1. Выход 3 задержанного импульса БЗИ 40-1 соединён со вторым входом схемы ИЛИ 38-1, со вторым входом схемы ИЛИ 38-2, с первым входом схемы ИЛИ 38-3 и с входом 9 входного импульса БЗИ 40-3.

Выход 10 состояния разрешения подсчёта БЗИ 40-1 соединён с нулевым входом триггера 39. Выход схемы ИЛИ 38-2 соединён с входом 8 запрета подсчёта БЗИ 40-1. Выход 3 задержанного импульса БЗИ 40-3 соединён со вторым входом схемы ИЛИ 38-3, выход которой соединён с входом 2 импульса обнуления БЗИ 40-3 и с первым входом схемы И 41-2. Выход 3 задержанного импульса БЗИ 40-2 соединён со вторым входом схемы ИЛИ 38-4. Выход схемы ИЛИ 38-4 соединён с входом 2 импульса обнуления БЗИ 40-2 и с входом 8 запрета подсчёта БЗИ 40-2. Выход 7 состояния запрета подсчёта БЗИ 40-2 соединён со вторым входом схемы И 41-2, выход которой соединён со счётным входом счётчика 42, с входом 9 входного импульса БЗИ 40-2, с входом 9 входного импульса БЗИ 40-4 и с выходом 3 задержанных импульсов дискретизации блока БЗПИ. Выход 3 задержанного импульса БЗИ 40-4 соединён со вторым входом схемы ИЛИ 38-5, с входом 8 запрета подсчёта БЗИ 40-4 и с выходом 5 сигнала прерывания индекса БЗПИ. Выход схемы ИЛИ 38-5 соединён с входом 2 импульса обнуления БЗИ 40-4. Выход счётчика 42 соединён с выходом 4 сигнала индекса БЗПИ.

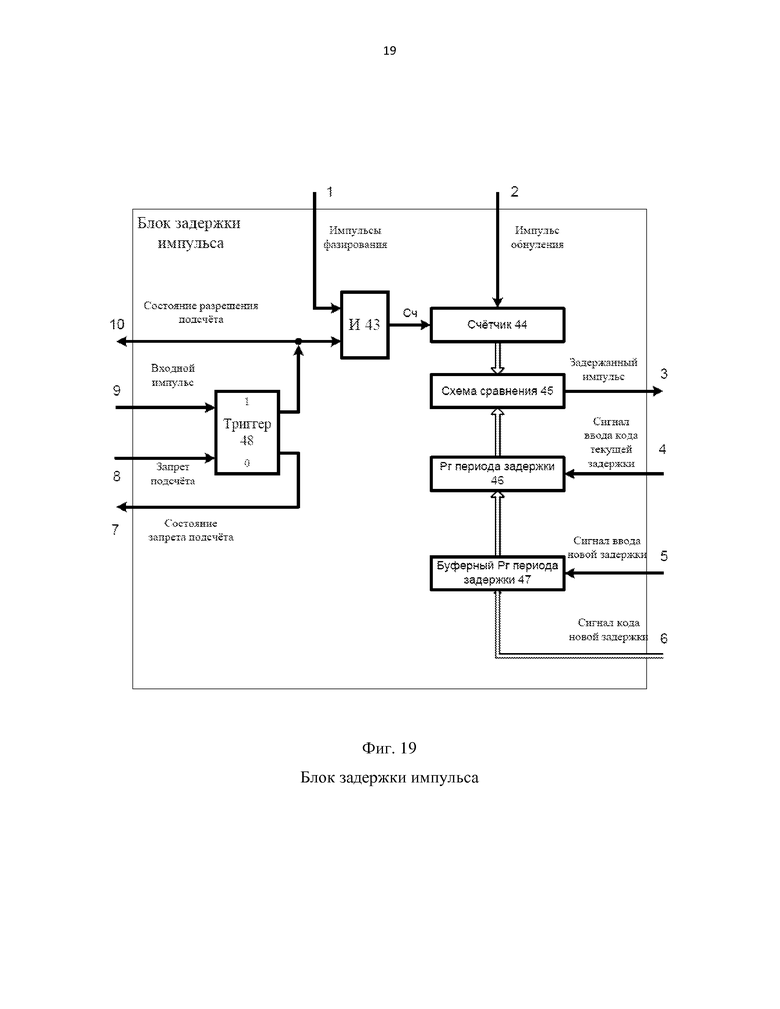

Схема блока задержки импульса (БЗИ) представлена на фиг. 19, где 43 – схема И, 44 – счётчик, 45 – схема сравнения, 46 – регистр периода задержки, 47 – буферный регистр периода задержки, 48 – триггер, причём вход 1 импульсов фазирования БЗИ соединён с первым входом схемы И 43, вход 2 импульса обнуления БЗИ соединён с входом обнуления счётчика 44, вход 4 сигнала ввода кода текущей задержки БЗИ соединён с управляющим входом регистра периода задержки 46, вход 5 сигнала ввода кода новой задержки БЗИ соединён с управляющим входом буферного регистра периода задержки 47, вход 6 сигнала кода новой задержки БЗИ соединён с входом данных буферного регистра периода задержки 47, вход 8 запрета подсчёта соединён с нулевым входом триггера 48, вход 9 входного импульса БЗИ соединён с единичным входом триггера 48, единичный выход триггера 48 соединён со вторым входом схемы И 43 и с выходом 10 состояния разрешения подсчёта БЗИ, нулевой выход триггера 48 соединён с выходом 7 состояния запрета подсчёта БЗИ, выход схемы И 43 соединён со счётным входом счётчика 44, выход которого соединён с первым входом схемы сравнения 45, выход регистра периода задержки 46 соединён со вторым входом схемы сравнения 45, выход которой соединён с выходом 3 задержанного импульса БЗИ.

При осуществлении предложенного способа и работе предложенного устройства перед началом сеанса связи с КА антенны 1 решётки (см. фиг. 16) наводят по целеуказаниям на точку небесной сферы с заданным углом места и азимутом, соответствующим началу зоны радиовидимости КА.

Далее, УЭВМ 16 вводит в блоки предложенного устройства цифровые сигналы, соответствующие значениям исходных данных для проведения сеанса связи с КА в следующем, например, порядке: формирует на своей шине адреса, данных и управления цифровой сигнал со значением адреса ячейки, где хранят цифровой сигнал со значением периода дискретизации Дtд. Под воздействием этого адресного сигнала запоминающее устройство ЗУ 15 формирует на своём втором выходе данных цифровой сигнал со значением периода дискретизации Дtд, который поступает на вход вывода данных шины 13, с выхода вывода данных которой цифровой сигнал со значением периода дискретизации Дtд поступает на вход 8 шины ввода данных блока задержки последовательности импульсов БЗПИ 20, на вход данных 5 j-го блока дискретизации сигнала антенны БДСА 23 i-й антенны, j=1, 2; i=0, 1, … , N – 1, в каждом блоке БДСА на вход 8 БЗПИ 20-1, 20-2, 20-3 (см. фиг 17) и далее на вход 6 сигнала кода новой задержки блока задержки импульса БЗИ 40-3 (см. фиг. 18), с которого поступает на вход данных буферного регистра периода задержки 47 (см. фиг. 19).

Далее УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением 5, который поступает на вход дешифратора 12, с 5-го выхода которого единичный управляющий сигнал поступает на вход 7 блока задержки последовательности импульсов БЗПИ 20 (см. фиг. 16), на вход 8 j-го блока дискретизации сигнала антенны БДСА 23 i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, в каждом блоке БДСА на вход 7 БЗПИ 20-1, 20-2, 20-3 (см. фиг 17) и далее на вход 5 сигнала ввода новой задержки блока задержки импульса БЗИ 40-3 (см. фиг. 18), с которого поступает (см. фиг. 19) на управляющий вход буферного регистра периода задержки 47. Под воздействием единичного управляющего сигнала на своём управляющем входе буферный регистр периода задержки 47 вводит со своего входа данных и запоминает цифровой сигнал со значением периода дискретизации Дtд.

Далее УЭВМ 16 формирует на своей шине адреса, данных и управления цифровой сигнал со значением адреса ячейки, где хранят цифровой сигнал со значением задержки АЦП ДtАЦП. Под воздействием этого адресного сигнала запоминающее устройство ЗУ 15 формирует на своём втором выходе данных цифровой сигнал со значением задержки АЦП ДtАЦП, который поступает на вход вывода данных шины 13, с выхода вывода данных которой цифровой сигнал со значением задержки АЦП ДtАЦП поступает на вход 8 шины ввода данных блока задержки последовательности импульсов БЗПИ 20, на вход данных 5 j-го блока дискретизации сигнала антенны БДСА 23 i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, в каждом блоке БДСА на вход 8 шины ввода данных БЗПИ 20-1, 20-2, 20-3 (см. фиг. 17) и далее на вход 6 сигнала кода новой задержки блока задержки импульса БЗИ 40-4 (см. фиг. 18), с которого поступает на вход данных буферного регистра периода задержки 47 (см. фиг. 19).

Далее УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением 6, который поступает на вход дешифратора 12, с 6-го выхода которого единичный управляющий сигнал поступает на вход 6 блока задержки последовательности импульсов БЗПИ 20 (см. фиг. 16), на вход 9 j-го БДСА 23 i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, в каждом блоке БДСА на вход 6 БЗПИ 20-1, 20-2, 20-3 (см. фиг. 17) и далее на вход 5 блока задержки импульса БЗИ 40-4 (см. фиг. 18), с которого поступает (см. фиг. 19) на управляющий вход буферного регистра периода задержки 47. Под воздействием единичного управляющего сигнала на своём управляющем входе буферный регистр периода задержки 47 вводит со своего входа данных и запоминает цифровой сигнал со значением задержки АЦП ДtАЦП.

Далее УЭВМ 16 формирует на своей шине адреса, данных и управления цифровой сигнал со значением адреса ячейки, где хранят цифровой сигнал со значением времени запрета импульса Дtзапрета. Под воздействием этого адресного сигнала запоминающее устройство ЗУ 15 формирует на своём втором выходе данных цифровой сигнал со значением времени запрета импульса Дtзапрета, который поступает на вход вывода данных шины 13, с выхода вывода данных которой цифровой сигнал со значением времени запрета импульса Дtзапрета поступает на вход 8 шины ввода данных блока задержки последовательности импульсов БЗПИ 20, на вход данных 5 j-го БДСА 23 i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, в каждом блоке БДСА на вход 8 БЗПИ 20-1, 20-2, 20-3 (см. фиг. 17) и далее на вход 6 блока задержки импульса БЗИ 40-2 (см. фиг. 18), с которого поступает на вход данных буферного регистра периода задержки 47 (см. фиг. 19).

Далее УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением 7, который поступает на вход дешифратора 12, с 7-го выхода которого единичный управляющий сигнал поступает на вход 2 блока задержки последовательности импульсов БЗПИ 20 (см. фиг. 16), на вход 10 j-го БДСА 23 i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, в каждом блоке БДСА на вход 2 БЗПИ 20-1, 20-2, 20-3 (см. фиг. 17) и далее на вход 5 блока задержки импульса БЗИ 40-2 (см. фиг. 18), с которого поступает (см. фиг. 19) на управляющий вход буферного регистра периода задержки 47. Под воздействием единичного управляющего сигнала на своём управляющем входе буферный регистр периода задержки 47 вводит со своего входа данных и запоминает цифровой сигнал со значением времени запрета импульса Дtзапрета.

Далее УЭВМ 16 формирует на своей шине адреса, данных и управления цифровой сигнал со значением адреса ячейки, где хранят цифровой сигнал со значением задержки времени начала обработки отсчётов одного фронта волны в информационных каналах ДtzобрИ. Под воздействием этого адресного сигнала запоминающее устройство ЗУ 15 формирует на своём втором выходе данных цифровой сигнал со значением задержки времени начала обработки отсчётов одного фронта волны в информационных каналах ДtzобрИ, который поступает на вход вывода данных шины 13, с выхода вывода данных которой цифровой сигнал со значением ДtzобрИ поступает на вход 8 блока задержки последовательности импульсов БЗПИ 20 и далее на вход 6 блока задержки импульса БЗИ 40-1 (см. фиг. 18), с которого поступает на вход данных буферного регистра периода задержки 47 (см. фиг. 19).

Далее УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением 8, который поступает на вход дешифратора 12, с 8-го выхода которого единичный управляющий сигнал поступает на вход 1 блока задержки последовательности импульсов БЗПИ 20 (см. фиг. 16) и далее на вход 5 блока задержки импульса БЗИ 40-1 (см. фиг. 18), с которого поступает (см. фиг. 19) на управляющий вход буферного регистра периода задержки 47. Под воздействием единичного управляющего сигнала на своём управляющем входе буферный регистр периода задержки 47 вводит со своего входа данных и запоминает цифровой сигнал со значением задержки времени начала обработки отсчётов одного фронта волны в информационных каналах ДtzобрИ.

Далее УЭВМ 16 формирует на своей шине адреса, данных и управления цифровой сигнал со значением адреса ячейки, где хранят цифровой сигнал со значением MдАС количества периодов дискретизации Дtд в периоде времени обработки отсчётов каналах автосопровождения TАС. Под воздействием этого адресного сигнала запоминающее устройство ЗУ 15 формирует на своём втором выходе данных цифровой сигнал со значением MдАС, который поступает на вход вывода данных шины 13, с выхода вывода данных которой цифровой сигнал со значением MдАС поступает на вход данных регистра сигнала периода автосопровождения 36 (см. фиг. 16).

Далее УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением 1, который поступает на вход дешифратора 12, с 1-го выхода которого единичный управляющий сигнал поступает на управляющий вход регистра сигнала периода автосопровождения 36 (см. фиг. 16). Под воздействием единичного управляющего сигнала на своём управляющем входе буферный регистра сигнала периода автосопровождения 36 вводит со своего входа данных и запоминает цифровой сигнал со значением периода времени обработки отсчётов каналах автосопровождения в периодах дискретизации MдАС.

Кроме перечисленных сигналов перед началом сеанса связи с КА в УФА вводят цифровые сигналы времени задержки импульса дискретизации в цифровом информационном канале и обоих каналах автосопровождения каждого БДСА, значения которых рассчитывают в управляющей ЭВМ 16 по формулам (1), (3), (4), (45) ÷ (53) на момент начала зоны радиовидимости КА для соответствующих углов места и азимута. Цифровые сигналы со значениями рассчитанных начальных задержек Дtzi0, Дtzi0АС1 и Дtzi0АС2 помещают в соответствующие ячейки ЗУ 15.

После этого для каждого j-го БДСА 23 каждой i-й антенны, j=1, 2; i=0, 1, … , N – 1, последовательно выполняют серию следующих шагов.

Шаг 1: УЭВМ 16 формирует на своей шине адреса, данных и управления цифровой сигнал со значением адреса ячейки, где хранят цифровой сигнал со значением времени задержки импульса дискретизации Дtzi0 в информационном канале i-й антенны. Под воздействием этого адресного сигнала запоминающее устройство ЗУ 15 формирует на своём втором выходе данных цифровой сигнал с исходным значением времени задержки импульса дискретизации Дtzi0 в цифровом информационном канале i-й антенны, который поступает на вход вывода данных шины 13, с выхода вывода данных которой цифровой сигнал со значением времени задержки импульса дискретизации в информационном канале i-й антенны, поступает на вход данных 5 j-го БДСА 23 i-й антенны, в блоке БДСА на вход 8 шины ввода данных БЗПИ 20-1, 20-2, 20-3 (см. фиг. 17) и далее на вход 6 сигнала кода новой задержки блока задержки импульса БЗИ 40-1 (см. фиг. 18), с которого поступает на вход данных буферного регистра периода задержки 47 (см. фиг. 19).

Шаг 2: УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением [10+18·i+9·(j–1)+3], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+3]-го выхода которого единичный управляющий сигнал поступает на вход 13 j-го БДСА 23 i-й антенны, в блоке БДСА на вход 1 БЗПИ 20-1, (см. фиг. 17) и далее на вход 5 блока задержки импульса БЗИ 40-1 (см. фиг. 18), с которого поступает (см. фиг. 19) на управляющий вход буферного регистра периода задержки 47. Под воздействием единичного управляющего сигнала на своём управляющем входе буферный регистр периода задержки 47 вводит со своего входа данных и запоминает цифровой сигнал с исходным значением времени задержки импульса дискретизации Дtzi0 в информационном канале i-й антенны.

Шаг 3: УЭВМ 16 формирует на своей шине адреса, данных и управления цифровой сигнал со значением адреса ячейки, где хранят цифровой сигнал со значением времени задержки импульса дискретизации Дtzi0АС1 в канале автосопровождения с опережением i-й антенны. Под воздействием этого адресного сигнала запоминающее устройство ЗУ 15 формирует на своём втором выходе данных цифровой сигнал с исходным значением времени задержки импульса дискретизации Дtzi0АС1 в канале автосопровождения с опережением i-й антенны, который поступает на вход вывода данных шины 13, с выхода вывода данных которой цифровой сигнал со значением времени задержки импульса дискретизации в канала автосопровождения с опережением i-й антенны, поступает на вход данных 5 j-го блока дискретизации сигнала антенны БДСА 23 i-й антенны, в блоке БДСА на вход 8 шины ввода данных БЗПИ 20-1, 20-2, 20-3 (см. фиг. 17) и далее на вход 6 сигнала кода новой задержки блока задержки импульса БЗИ 40-1 (см. фиг. 18), с которого поступает на вход данных буферного регистра периода задержки 47 (см. фиг. 19).

Шаг 4: УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением [10+18·i+9·(j–1)+6], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+6]-го выхода которого единичный управляющий сигнал поступает на вход 16 j-го БДСА 23 i-й антенны, в блоке БДСА на вход 1 БЗПИ 20-2, (см. фиг. 17) и далее на вход 5 блока задержки импульса БЗИ 40-1 (см. фиг. 18), с которого поступает (см. фиг. 19) на управляющий вход буферного регистра периода задержки 47. Под воздействием единичного управляющего сигнала на своём управляющем входе буферный регистр периода задержки 47 вводит со своего входа данных и запоминает цифровой сигнал с исходным значением времени задержки импульса дискретизации Дtzi0АС1 в канале автосопровождения с опережением i-й антенны.

Шаг 5: УЭВМ 16 формирует на своей шине адреса, данных и управления цифровой сигнал со значением адреса ячейки, где хранят цифровой сигнал со значением времени задержки импульса дискретизации Дtzi0АС2 в канале автосопровождения с отставанием i-й антенны. Под воздействием этого адресного сигнала запоминающее устройство ЗУ 15 формирует на своём втором выходе данных цифровой сигнал с исходным значением времени задержки импульса дискретизации Дtzi0АС2 в канале автосопровождения с отставанием i-й антенны, который поступает на вход вывода данных шины 13, с выхода вывода данных которой цифровой сигнал со значением времени задержки импульса дискретизации в канала автосопровождения с отставанием i-й антенны поступает на вход данных 5 j-го БДСА 23 i-й антенны, в блоке БДСА поступает на вход 8 шины ввода данных БЗПИ 20-1, 20-2, 20-3 (см. фиг. 17) и далее на вход 6 сигнала кода новой задержки блока задержки импульса БЗИ 40-1 (см. фиг. 18), с которого поступает на вход данных буферного регистра периода задержки 47 (см. фиг. 19).

Шаг 6: УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением [10+18·i+9·(j–1)+9], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+9]-го выхода которого единичный управляющий сигнал поступает на вход 19 j-го БДСА 23 i-й антенны, в блоке БДСА на вход 1 БЗПИ 20-3, (см. фиг. 17) и далее на вход 5 блока задержки импульса БЗИ 40-1 (см. фиг. 18), с которого поступает (см. фиг. 19) на управляющий вход буферного регистра периода задержки 47. Под воздействием единичного управляющего сигнала на своём управляющем входе буферный регистр периода задержки 47 вводит со своего входа данных и запоминает цифровой сигнал с исходным значением времени задержки импульса дискретизации Дtzi0АС2 в канале автосопровождения с отставанием i-й антенны.

По завершении ввода цифровых сигналов со значениями исходных данных непосредственно перед началом сеанса связи в начале зоны радиовидимости КА во все блоки БЗПИ выдают сигнал начала сеанса. Для этого УЭВМ 16 формирует на своей первой адресной шине цифровой сигнал со значением 3, который поступает на вход дешифратора 12, с 3-го выхода которого единичный управляющий сигнал начала сеанса поступает на второй вход схемы ИЛИ 37, через неё на вход обнуления счётчика 34 и устанавливает в нём цифровой сигнал с нулевым значением, кроме того данный единичный управляющий сигнал начала сеанса поступает на вход 12 блока задержки последовательности импульсов БЗПИ 20 (см. фиг. 16), на вход 6 каждого j-го БДСА 23 в тракте каждой i-й антенны, j = 1, 2; i = 0, 1, … , N – 1, в каждом блоке БДСА на вход 12 БЗПИ 20-1, 20-2, 20-3 (см. фиг. 17) и в каждом БЗПИ на первый вход схем ИЛИ 38-1, 38-4, 38-5 и на вход обнуления счётчика 42, устанавливая в нём нулевое значение сигнала индекса k (см. фиг. 18). Единичный управляющий сигнал с выхода схемы ИЛИ 38-1 поступает на единичный вход триггера 39 и переводит его в единичное состояние. С выходов схем ИЛИ 38-1, 38-4, 38-5 единичный управляющий сигнал поступает на вход обнуления 2 БЗИ 40-1, 40-3, 40-2, 40-4 и в каждом БЗИ поступает на вход обнуления счётчика 44 (см. фиг. 19) и устанавливает в нём цифровой сигнал с нулевым значением. Кроме этого, с выхода схемы ИЛИ 38-1 единичный управляющий сигнал поступает на вход 4 сигнала ввода кода текущей задержки БЗИ 40-1, 40-2, 40-3, 40-4 (см. фиг. 18) и в каждом БЗИ поступает на управляющий вход регистра периода задержки 46 (см. фиг. 19) и вводит в него цифровой сигнал с текущим значением периода задержки с выхода буферного регистра периода задержки 47, в который этот сигнал был введён ранее из УЭВМ 16. Помимо этого, с выхода схемы ИЛИ 38-4 единичный управляющий сигнал поступает на вход 8 запрета подсчёта БЗИ 40-2 (см. фиг. 18) и далее на нулевой вход триггера 48 (см. фиг. 19), устанавливая его в нулевое состояние, после чего единичный сигнал с нулевого выхода триггера 48 поступает на выход 7 состояния запрета подсчёта БЗИ 40-2 и далее на второй вход схемы И 41-2.

Таким образом, под воздействием сигнала начала сеанса в УФА заканчивают подготовительные операции и начинают операции по фазированию сигналов от разных антенн и по автосопровождению КА.

Также как и в прототипе, на антенны 1 решётки падает фронт волны радиосигнала со сдвигом для антенны №i, i=0, 1, … , N–1, на время разности хода лучей Дtio относительно опорной антенны № 0. Принятый антенной сигнал усиливают в соответствующем МШУ 2, понижают по частоте до первой промежуточной частоты с использованием первого гетеродина 4 и смесителя 3-1, усиливают и ограничивают по полосе частот с использованием УПЧ-ПФ 5-1, разветвляют на два сигнала делителем 6 и далее, в отличие от прототипа, формируют квадратурные сигналы на второй промежуточной полосе с помощью смесителей 3-2, второго гетеродина 8 и постоянного фазовращателя на 90° 9.

На 1-м блоке дискретизации сигнала антенны БДСА 23 i-й антенны, i = 0, 1, … , N–1, под воздействием импульсов фазирования с частотой следования fф от ГТИ 11, поступающих на 2-й вход БДСА, и импульсов дискретизации с выхода счётчика-делителя 19 с частотой следования fд, поступающих на 3-й вход БДСА, в соответствии с выражением (7) формируют цифровые отсчёты синусной квадратуры, принятого сигнала в информационном канале Sik в моменты времени tik = tГk + Дtzik= tУФАik+ Дtп; в соответствии с выражением (9) формируют отсчёты Sik– синусной квадратуры принятого сигнала в канале автосопровождения с опережением в моменты времени tikАС1 = tГk + ДtzikАС1 = tГk + Дtzik – Дtоткл= tУФАik + Дtп – Дtоткл; в соответствии с выражением (11) формируют отсчёты Sik+ синусной квадратуры принятого сигнала в канале автосопровождения с отставанием в моменты времени tikАС2 = tГk + ДtzikАС2 = tГk + Дtzik + Дtоткл= tУФАik + Дtп + Дtоткл.

На 2-ом блоке дискретизации сигнала антенны БДСА 23 i-й антенны, i = 0, 1, … , N–1, под воздействием импульсов фазирования с частотой следования fф от ГТИ 11, поступающих на 2-й вход БДСА, и импульсов дискретизации с выхода счётчика-делителя 19 с частотой следования fд, поступающих на 3-й вход БДСА, в соответствии с выражением (8) формируют цифровые отсчёты косинусной квадратуры, принятого сигнала в информационном канале S90ik в моменты времени tik = tГk + Дtzik= tУФАik+ Дtп; в соответствии с выражением (10) формируют отсчёты S90ik– косинусной квадратуры принятого сигнала в канале автосопровождения с опережением в моменты времени tikАС1 = tГk + ДtzikАС1 = tГk + Дtzik – Дtоткл= tУФАik + Дtп – Дtоткл; в соответствии с выражением (12) формируют отсчёты S90ik+ косинусной квадратуры принятого сигнала в канале автосопровождения с отставанием в моменты времени tikАС2 = tГk + ДtzikАС2 = tГk + Дtzik + Дtоткл= tУФАik + Дtп + Дtоткл.

Для этого в одном из трёх блоков задержки последовательности импульсов БЗПИ, входящих в состав БДСА, например 20-1 (см. фиг. 17), под воздействием импульсов фазирования, поступающих на вход 10 блока 20-1 с входа 2 БДСА и импульсов дискретизации, поступающих на вход 11 блока 20-1 с входа 3 БДСА, формируют последовательность импульсов дискретизации, задержанную на интервал времени Дtzik, и подают импульсы дискретизации этой задержанной последовательности на вход импульсов дискретизации АЦП 10-1, на сигнальный вход которого подают принимаемый i-й антенной сигнал синусной квадратуры для 1-го БДСА и сигнал косинусной квадратуры для 2-го БДСА с сигнального входа 1 БДСА. Дискретный сигнал отсчёта с выхода АЦП 10-1 подают на вход данных ключа сигнала отсчёта 22-1.

Параллельно с выхода 4 БЗПИ 20-1 на вход данных ключа 21-1 подают сигнал индекса отсчёта со значением k, а с выхода 5 БЗПИ 20-1 на выход 20 БДСА подают сигнал прерывания, который далее подают на [2+6·i+3·(j–1)+1]-й вход сигнала прерывания о готовности отсчёта информационного канала УЭВМ 16 для j-го БДСА, j=1, 2; i = 0, 1, … , N–1.

Под воздействием сигнала прерывания о готовности отсчёта на своём [2+6·i+3·(j–1)+1]-м входе сигнала прерывания о готовности отсчёта УЭВМ 16 формирует на своей первой адресной шине сигнал со значением [10+18·i+9·(j–1)+1], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+1]-го выхода которого единичный управляющий сигнал поступает на 11-й вход j-го БДСА23 i-й антенны (см. фиг. 16) и далее на управляющий вход ключа 21-1 (см. фиг. 17). Под воздействием единичного управляющего сигнала ключ 21-1 пропускает сигнал индекса отсчёта со значением k на выход данных 4 j-го БДСА i-й антенны и далее на вход ввода данных шины данных 13 (см. фиг. 16), с выхода ввода данных которой сигнал индекса отсчёта со значением k от j-го БДСА i-й антенны поступает на вход данных ЗУ 15, где под воздействием адресного сигнала, подаваемого с шины адреса, данных и управления УЭВМ 16 на адресную шину ЗУ 15, этот дискретный сигнал записывают в ячейке текущего индекса отсчёта информационного канала i-й антенны.

Далее, УЭВМ 16 формирует на своей первой адресной шине сигнал со значением [10+18·i+9·(j–1)+2], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+2]-го выхода которого единичный управляющий сигнал поступает на 12-й вход j-го БДСА 23 i-й антенны (см. фиг. 16) и далее на управляющий вход ключа 22-1 (см. фиг. 17). Под воздействием единичного управляющего сигнала ключ 22-1 пропускает дискретный сигнал отсчёта информационного канала на выход данных 4 j-го БДСА i-й антенны и далее на вход ввода данных шины данных 13, с выхода ввода данных которой дискретный сигнал отсчёта информационного канала j-го БДСА i-й антенны поступает на вход данных ЗУ 15 (см. фиг. 16), где под воздействием адресного сигнала, подаваемого с шины адреса, данных и управления УЭВМ 16 на адресную шину ЗУ 15, этот дискретный сигнал записывают в ячейке индексированного массива i-й антенны с текущим индексом k отсчёта информационного канала.

Аналогично формируют и записывают в ЗУ 15 отсчёты Sik– синусной квадратуры принятого сигнала, отсчёты S90ik– косинусной квадратуры сигнала и их индексы в канале автосопровождения с опережением.

Для этого в одном из оставшихся двух блоков задержки последовательности импульсов БЗПИ, входящих в состав j-го БДСА i-й антенны, j=1, 2; i = 0, 1, … , N–1, например 20-2 (см. фиг. 17), под воздействием импульсов фазирования, поступающих на вход 10 блока 20-2 с входа 2 j-го БДСА i-й антенны и импульсов дискретизации, поступающих на вход 11 блока 20-2 с входа 3 j-го БДСА i-й антенны, формируют последовательность импульсов дискретизации, задержанную на интервал времени (Дtzik – Дtоткл), и подают импульсы дискретизации этой задержанной последовательности на вход импульсов дискретизации АЦП 10-2, на сигнальный вход которого подаётся принимаемый i-й антенной сигнал с сигнального входа 1 j-го БДСА i-й антенны. Дискретный сигнал отсчёта с выхода АЦП 10-2 подаётся на вход данных ключа сигнала отсчёта канала автосопровождения с опережением 22-2.

Параллельно с выхода 4 БЗПИ 20-2 на вход данных ключа 21-2 подаётся сигнал индекса отсчёта канала автосопровождения с опережением со значением k, а с выхода 5 БЗПИ 20-2 на выход 21 j-го БДСА i-й антенны подаётся сигнал прерывания, который далее подаётся на [2+6·i+3·(j–1)+2]-й вход сигнала прерывания о готовности отсчёта канала автосопровождения с опережением УЭВМ 16 (см. фиг. 16).

Под воздействием сигнала прерывания о готовности отсчёта канала автосопровождения с опережением на своём [2+6·i+3·(j–1)+2]-м входе сигнала прерывания о готовности отсчёта канала автосопровождения с опережением УЭВМ 16 формирует на своей первой адресной шине сигнал со значением [10+18·i+9·(j–1)+4], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+4]-го выхода которого единичный управляющий сигнал поступает на 14-й вход j-го БДСА 23 i-й антенны и далее на управляющий вход ключа 21-2 (см. фиг. 17). Под воздействием единичного управляющего сигнала ключ 21-2 пропускает сигнал индекса отсчёта канала автосопровождения с опережением со значением k на выход данных 4 j-го БДСА i-й антенны и далее на вход ввода данных шины данных 13, с выхода ввода данных которой сигнал индекса отсчёта со значением k от j-го БДСА i-й антенны поступает на вход данных ЗУ 15, где под воздействием адресного сигнала, подаваемого с шины адреса, данных и управления УЭВМ 16 на адресную шину ЗУ 15, тот дискретный сигнал записывают в ячейке текущего индекса отсчёта канала автосопровождения с опережением i-й антенны.

Далее, УЭВМ 16 формирует на своей первой адресной шине сигнал со значением [10+18·i+9·(j–1)+5], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+5]-го выхода которого единичный управляющий сигнал поступает на 15-й вход j-го БДСА 23 i-й антенны (см. фиг. 16) и далее на управляющий вход ключа 22-2 (см. фиг. 17) . Под воздействием единичного управляющего сигнала ключ 22-2 пропускает дискретный сигнал отсчёта канала автосопровождения с опережением на выход данных 4 j-го БДСА i-й антенны и далее на вход ввода данных шины данных 13, с выхода ввода данных которой дискретный сигнал отсчёта канала автосопровождения с опережением j-го БДСА i-й антенны поступает на вход данных ЗУ 15, где под воздействием адресного сигнала, подаваемого с шины адреса, данных и управления УЭВМ 16 на адресную шину ЗУ 15, этот дискретный сигнал записывают в ячейке индексированного массива i-й антенны с текущим индексом k отсчёта канала автосопровождения с опережением.

Аналогично формируют и записывают в ЗУ 15 отсчёты Sik+ синусной квадратуры принятого сигнала, отсчёты S90ik+ косинусной квадратуры принятого сигнала и их индексы в канале автосопровождения с отставанием.

Для этого в оставшемся блоке задержки последовательности импульсов БЗПИ, входящем в состав j-го БДСА i-й антенны, например 20-3 (см. фиг. 17), под воздействием импульсов фазирования, поступающих на вход 10 блока 20-3 с входа 2 j-го БДСА i-й антенны и импульсов дискретизации, поступающих на вход 11 блока 20-3 с входа 3 j-го БДСА i-й антенны, формируют последовательность импульсов дискретизации, задержанную на интервал времени (Дtzik + Дtоткл), и подают импульсы дискретизации этой задержанной последовательности на вход импульсов дискретизации АЦП 10-3, на сигнальный вход которого подаётся принимаемый i-й антенной сигнал с сигнального входа 1 j-го БДСА i-й антенны. Дискретный сигнал отсчёта с выхода АЦП 10-3 подаётся на вход данных ключа сигнала отсчёта канала автосопровождения с отставанием 22-3.

Параллельно с выхода 4 БЗПИ 20-3 на вход данных ключа 21-3 подаётся сигнал индекса отсчёта канала автосопровождения с отставанием со значением k, а с выхода 5 БЗПИ 20-3 на выход 22 j-го БДСА i-й антенны подаётся сигнал прерывания, который далее подаётся на [2+6·i+3·(j–1)+3]-й вход сигнала прерывания о готовности отсчёта канала автосопровождения с отставанием УЭВМ 16 (см. фиг. 16).

Под воздействием сигнала прерывания о готовности отсчёта канала автосопровождения с отставанием на своём [2+6·i+3·(j–1)+3]-м входе сигнала прерывания о готовности отсчёта канала автосопровождения с отставанием УЭВМ 16 формирует на своей первой адресной шине сигнал со значением [10+18·i+9·(j–1)+7], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+7]-го выхода которого единичный управляющий сигнал поступает на 17-й вход j-го БДСА 23 i-й антенны и далее на управляющий вход ключа 21-3 (см. фиг. 17). Под воздействием единичного управляющего сигнала ключ 21-3 пропускает сигнал индекса отсчёта канала автосопровождения с отставанием со значением k на выход данных 4 от j-го БДСА i-й антенны и далее на вход ввода данных шины данных 13, с выхода ввода данных которой сигнал индекса отсчёта со значением k j-го БДСА i-й антенны поступает на вход данных ЗУ 15, где под воздействием адресного сигнала, подаваемого с шины адреса, данных и управления УЭВМ 16 на адресную шину ЗУ 15, этот дискретный сигнал записывают в ячейке текущего индекса отсчёта канала автосопровождения с отставанием i-й антенны (см. фиг. 16).

Далее, УЭВМ 16 формирует на своей первой адресной шине сигнал со значением [10+18·i+9·(j–1)+8], который поступает на вход дешифратора 12, с [10+18·i+9·(j–1)+8]-го выхода которого единичный управляющий сигнал поступает на 18-й вход j-го БДСА 23 i-й антенны и далее на управляющий вход ключа 22-3 (см. фиг.17). Под воздействием единичного управляющего сигнала ключ 22-3 пропускает дискретный сигнал отсчёта канала автосопровождения с отставанием на выход данных 4 j-го БДСА i-й антенны и далее на вход ввода данных шины данных 13, с выхода ввода данных которой дискретный сигнал отсчёта канала автосопровождения с отставанием j-го БДСА i-й антенны поступает на вход данных ЗУ 15, где под воздействием адресного сигнала, подаваемого с шины адреса, данных и управления УЭВМ 16 на адресную шину ЗУ 15, этот дискретный сигнал записывают в ячейке индексированного массива i-й антенны с текущим индексом k отсчёта канала автосопровождения с отставанием (см. фиг. 16).

Параллельно на выходе 3 задержанных импульсов в блоке задержки последовательности импульсов БЗПИ 20 под воздействием импульсов фазирования с частотой следования fф от ГТИ 11, поступающих на 10-й вход БЗПИ 20, и импульсов дискретизации с выхода счётчика-делителя 19 с частотой следования fд , поступающих на 11-й вход БЗПИ 20, формируют последовательность импульсов, задержанную относительно импульсов дискретизации с выхода счётчика-делителя 19 на время задержки начала обработки отсчётов одного фронта волны в информационных каналах ДtzобрИ , выбранное в соответствии с выражением (17), и подают импульсы этой задержанной последовательности на счётный вход счётчика 34.

Параллельно с выхода 4 БЗПИ 20 на вход данных ключа 21 подают сигнал индекса импульса с очередным значением k, а с выхода 5 сигнала прерывания БЗПИ 20 подают сигнал прерывания на 2-й вход сигнала прерывания УЭВМ 16.

Под воздействием сигнала прерывания на своём 2-м входе сигнала прерывания о готовности отсчёта УЭВМ 16 формирует на своей первой адресной шине сигнал со значением 2, который поступает на вход дешифратора 12, со 2-го выхода которого единичный управляющий сигнал поступает на управляющий вход ключа 21. Под воздействием единичного управляющего сигнала ключ 21 пропускает сигнал индекса отсчёта со значением k на вход ввода данных шины данных 13, с выхода ввода данных которой сигнал индекса отсчёта со значением k поступает на вход данных ЗУ 15, где под воздействием адресного сигнала, подаваемого с шины адреса, данных и управления УЭВМ 16 на адресную шину ЗУ 15, этот дискретный сигнал записывают в ячейке текущего индекса суммарного информационного отсчёта антенной решётки.