Атомные электростанции являются сложными системами, которые могут иметь множество сенсоров, контролирующих параметры процессов, такие как, например, температура, давление, поток и нейтронный поток, и системы управления, выдающие команды на контроллеры, логические схемы защиты или системы приведения в действие защиты. Среда атомной электростанции подчиняется многообразным процедурам регулирования, предусматривающим обязательные жесткие меры по обеспечению безопасности. Например, меры по обеспечению безопасности включают в себя объединение разнообразных механизмов, разделение на оборудование защиты (обеспечения безопасности) и оборудование не для обеспечения безопасности, аппаратное резервирование и т.д. Как правило, для каждой измеренной характеристики или параметра сигналы от трех - четырех независимых сенсоров собираются во время эксплуатации электростанции. Сигналы обрабатываются и используются, чтобы контролировать работу, проверять корректность функционирования связанных механизмов и обнаруживать аномалии процесса. Модуль логики приоритетов (PLM) является логическим компонентом, помещаемым между системами инициирования защиты и/или управления и множеством исполнительных устройств, связанных с системами защиты и/или управления. PLM получает команды обеспечения защиты и/или не относящееся к защите команды и принимает решение (делает выбор) между ними, реагируя на противоречивые инструкции, путем выбора сигнала приоритетной команды из множества команд приведения в действие устройств.

Сущность изобретения

В варианте осуществления в системе управления ядерным процессом раскрыт модуль логики приоритетов (PLM). Модуль логики приоритетов содержит множество входных портов, каждый входной порт ассоциирован с одним из множества приоритетов, множество выходных портов и порт выбора тестового режима, ассоциированный с сигналом выбора тестового режима. Сигнал выбора тестового режима выбирает один из нормального режима или тестового режима, причем каждый режим ассоциирован с согласованием сигналов, принимаемых входными портами, с сигналами, посылаемыми выходными портами. Модуль логики приоритетов дополнительно содержит конфигурируемую схему логики приоритетов, причем схема логики приоритетов отображает один из входных портов на один из выходных портов.

В варианте осуществления в системе управления ядерным процессом раскрыт модуль логики приоритетов. Модуль логики приоритетов содержит множество входных портов и выходной порт, предварительно программируемую схему логики приоритетов, причем схема логики приоритетов отображает один из входных портов на выходной порт, и схему запрета программируемости, связанную со схемой логики приоритетов, причем схема запрета программируемости деактивирует функцию программирования схемы логики приоритетов.

В варианте осуществления раскрыт способ тестирования. Способ содержит выбор тестового режима из сигнала выбора тестового режима и прием множества входных сигналов, причем каждый входной сигнал является сигналом класса 1Е, ассоциированным с приоритетом. Способ дополнительно содержит формирование по меньшей мере одного выходного сигнала из входных сигналов, формирование выходного сигнала из самого низкоприоритетного входного сигнала, формирование тестового выходного сигнала из входных сигналов, посылку выходного сигнала на исполнительное устройство и посылку тестового выходного сигнала на устройство тестирования.

Эти и другие признаки будут более ясно понятны из следующего подробного описания, во взаимосвязи с иллюстрирующими чертежами и формулой изобретения.

Краткое описание чертежей

Для более полного понимания настоящего раскрытия ссылка далее делается на нижеследующее краткое описание, в связи с сопровождающими чертежами и подробным описанием, в котором сходные ссылочные позиции представляют сходные части.

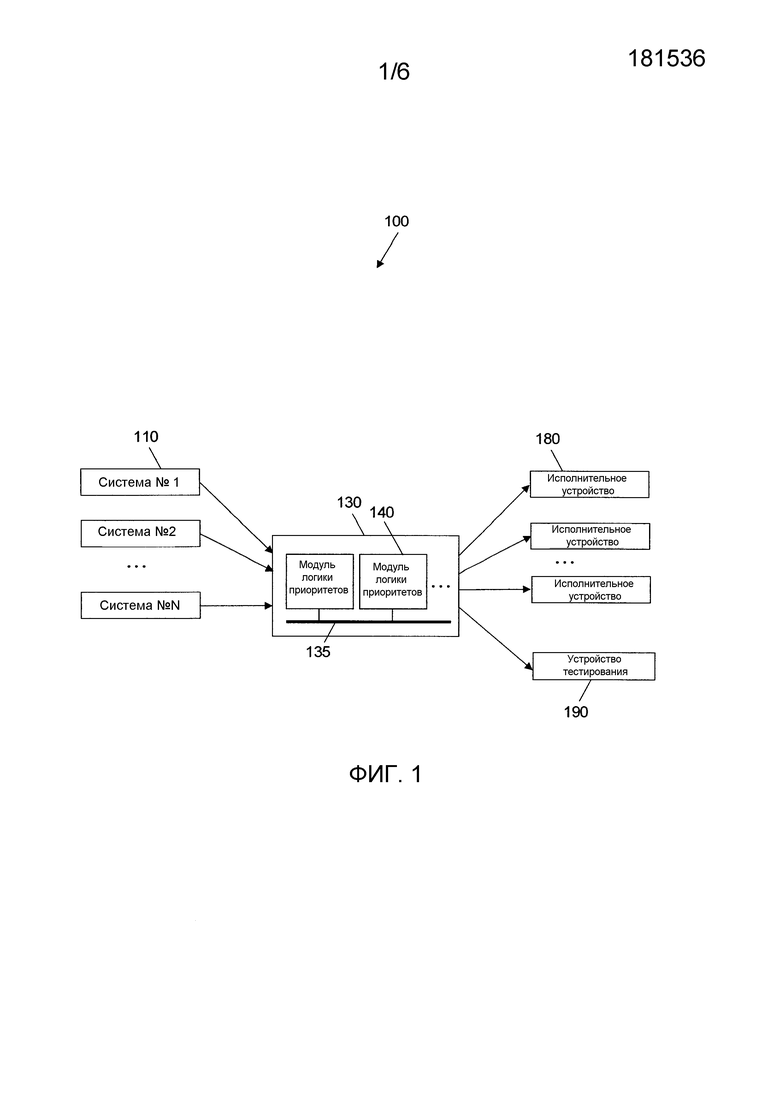

Фиг.1 - блок-схема системы управления процессом согласно варианту осуществления раскрытия.

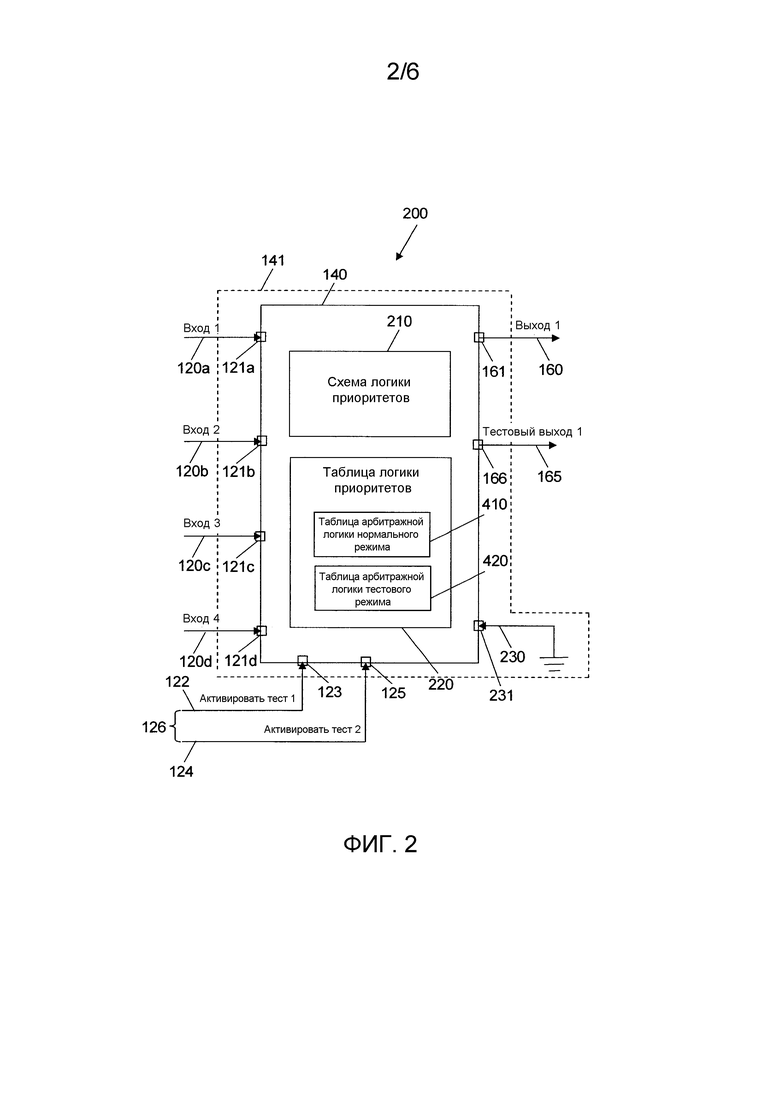

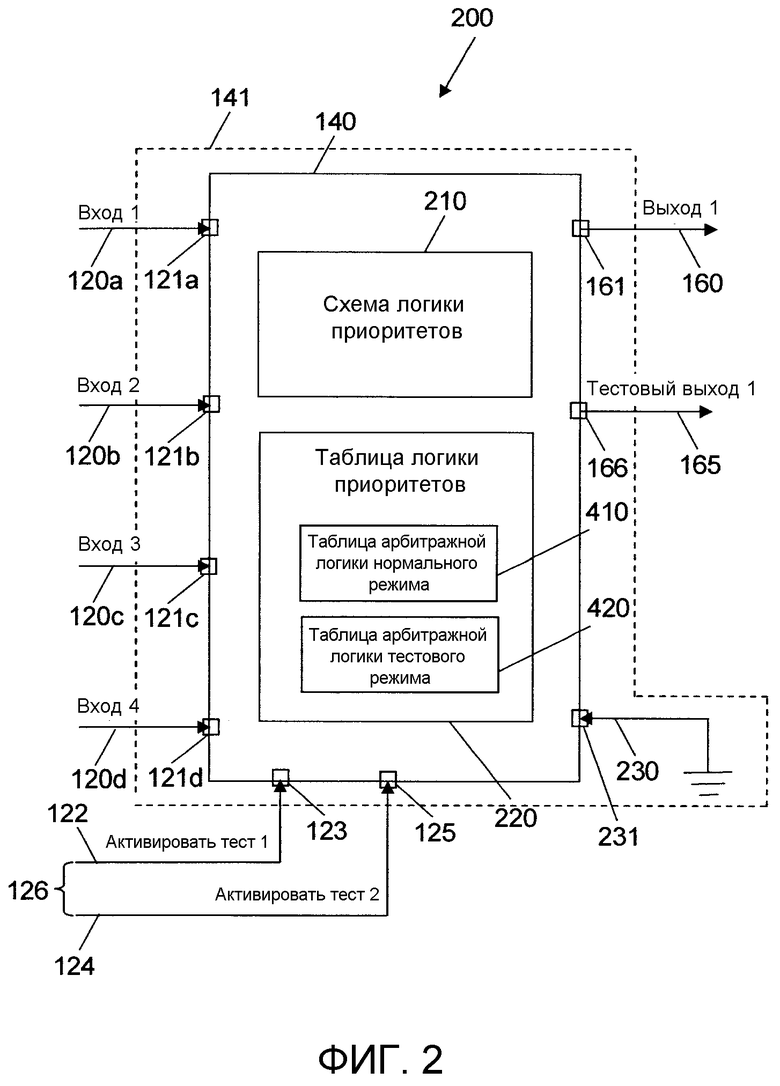

Фиг.2 - блок-схема архитектуры модуля логики приоритетов (PLM) согласно варианту осуществления раскрытия.

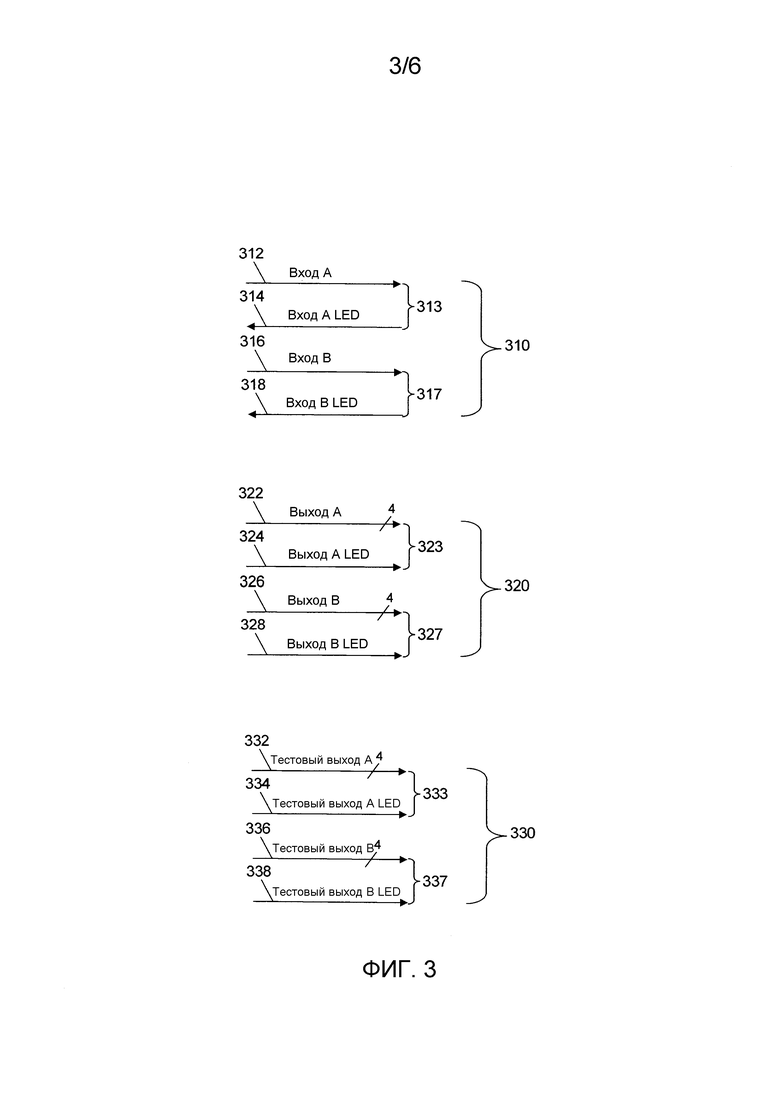

Фиг.3 иллюстрирует структуру входа/выхода согласно варианту осуществления раскрытия.

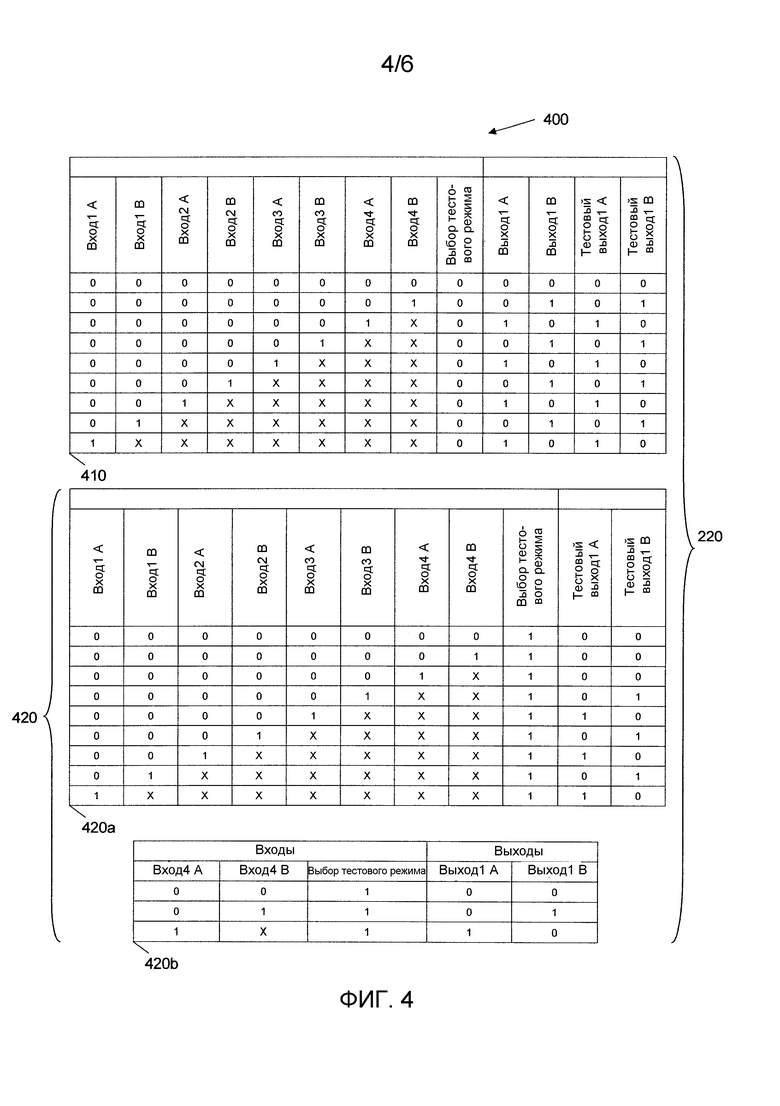

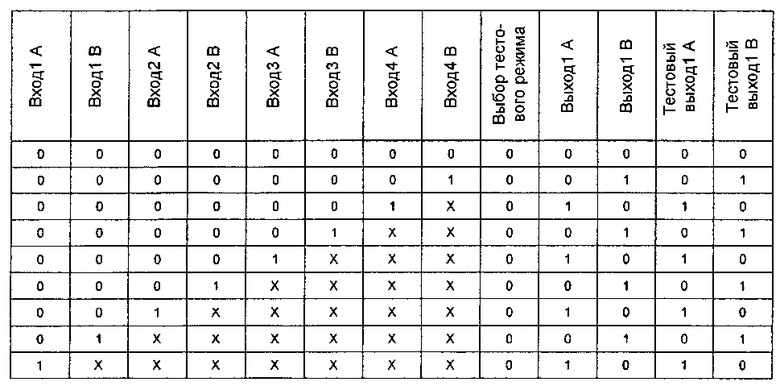

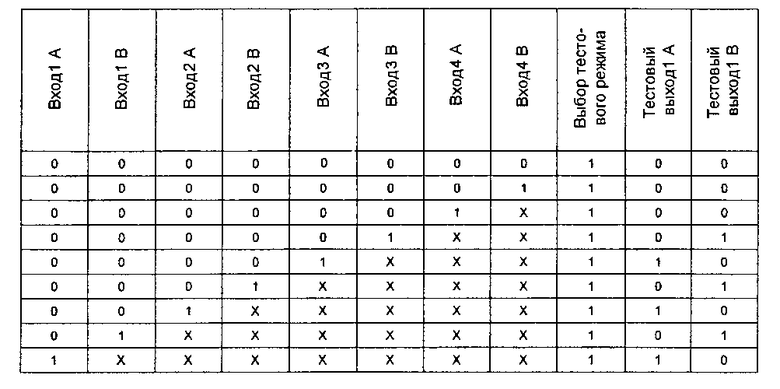

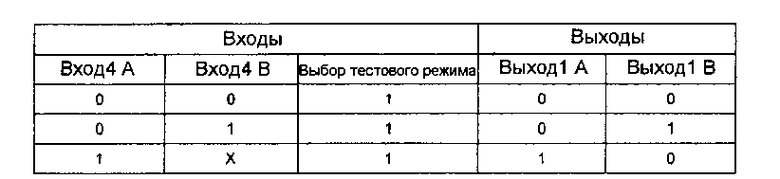

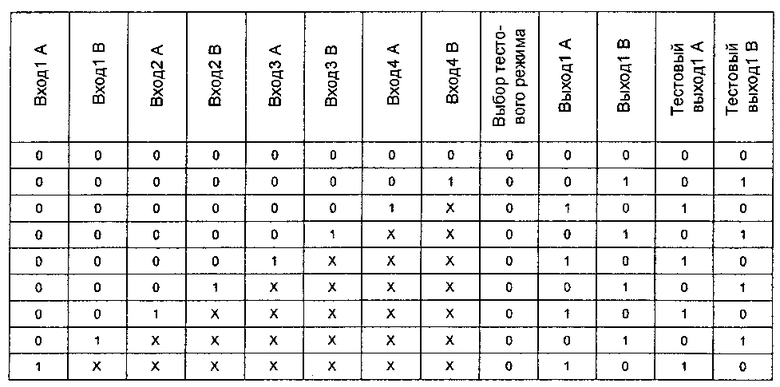

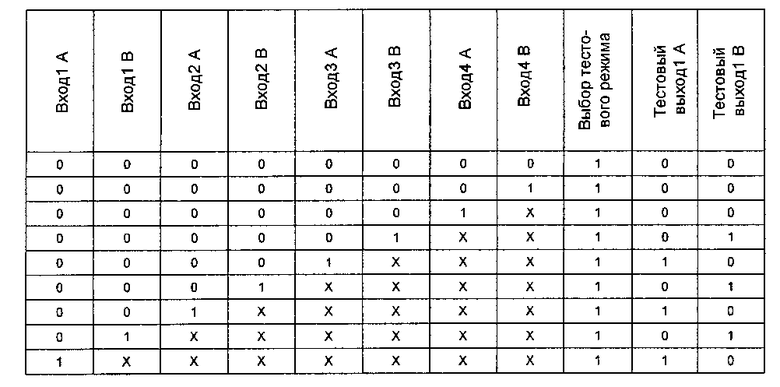

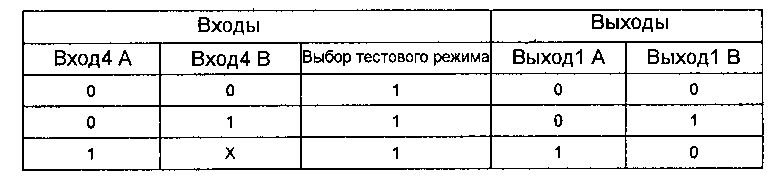

Фиг.4 иллюстрирует функциональное поведение логики приоритетов согласно варианту осуществления раскрытия.

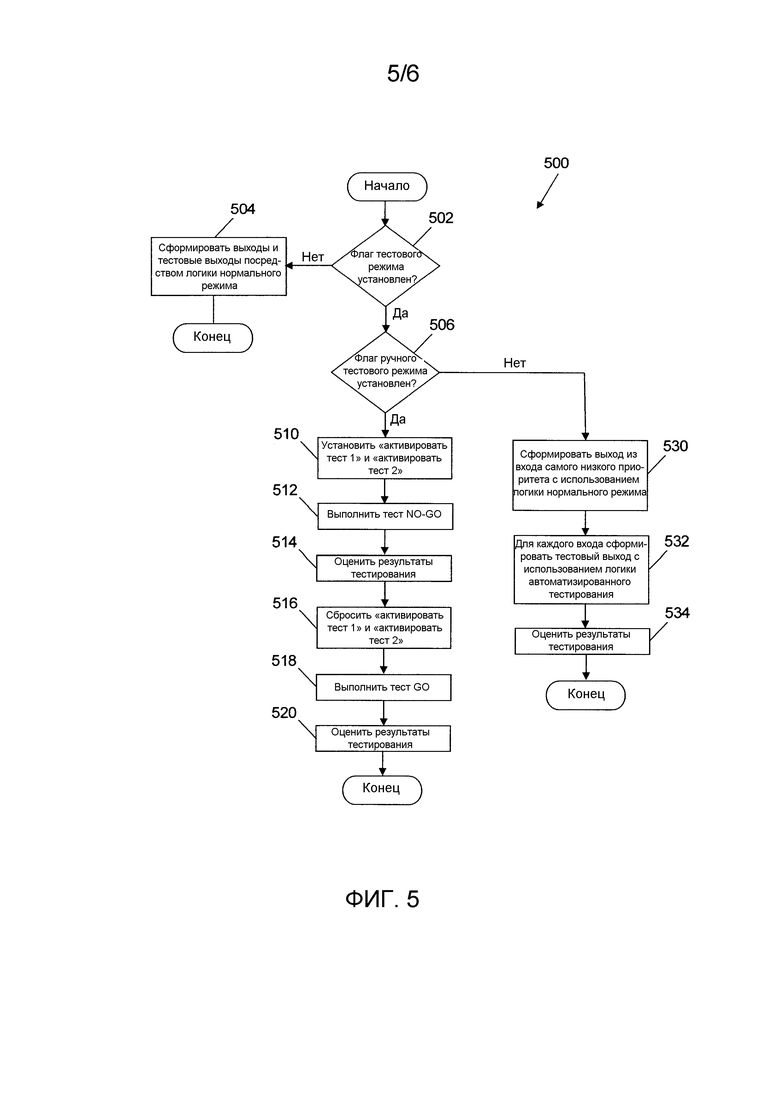

Фиг.5 - блок-схема способа тестирования согласно варианту осуществления раскрытия.

Фиг.6 иллюстрирует примерную компьютерную систему согласно варианту осуществления раскрытия.

Подробное описание

Следует понимать с самого начала, что хотя ниже представлено иллюстративное выполнение одного или более вариантов осуществления, раскрытые системы и способы могут быть осуществлены с использованием любого числа способов, как известных в настоящее время, так и еще не существующих. Раскрытие никоим образом не должно быть ограничено иллюстративными реализациями, чертежами и методами, проиллюстрированными ниже, но может быть изменено в объеме приложенных пунктов формулы изобретения совместно с их полным объемом эквивалентов.

Раскрыт модуль логики приоритетов (PLM), реализованный с использованием сложного устройства программируемой логики (CPLD) для использования в высоконадежных автоматизированных приложениях управления процессом. Модуль логики приоритетов может использоваться, в варианте осуществления, в системе управления ядерным процессом класса 1Е. Модуль логики приоритетов принимает множество входов и на основе логики присвоения приоритетов генерирует единственный выход управления из входов. Например, на основе четырех различных входов модуль логики приоритетов либо сигнализирует активацию соленоида, либо сигнализирует деактивацию соленоида. Входы могут содержать один или более входов ручного переопределения и один или более входов автоматизированного управления процессом. Модуль логики приоритетов дополнительно принимает вход тестового режима, который может перевести модуль логики приоритетов в тестовый режим работы.

Реализация модуля логики приоритетов в сложном устройстве программируемой логики способствует сокращению затрат на сертификацию, ассоциированных с изменением логики приоритетов. Логика приоритетов может отличаться в зависимости от определенной обеспечиваемой функции управления. Например, логика приоритета для управления стержнями управления реактора может отличаться от логики приоритета для управления клапаном хладагента. Если две различных логических функции были реализованы в первой специализированной интегральной схеме (ASIC) и второй специализированной интегральной схеме, может быть необходимым выполнять полное независимое тестирование сертификации на обеих специализированных интегральных схемах. Такое тестирование сертификации может быть очень дорогостоящим и трудоемким и может повлечь за собой физические тесты, такие как радиационный тест, экологический тест, сейсмический тест, тест на кондуктивную эмиссию, тест на излученную эмиссию и другие. Поскольку тот же самый элемент аппаратных средств, заданное сложное устройство программируемой логики, может использоваться, чтобы реализовать различную логику приоритетов, путем повторного программирования, реализованный на CPLD модуль логики приоритетов может быть сертифицирован однажды, и различное программирование функциональности логики приоритетов может поддерживаться документом намного менее дорогого и трудоемкого анализа влияния изменения.

В варианте осуществления модуль логики приоритетов останавливает попытки повторного программирования или нелицензионного выпуска модуля логики программирования в полевых условиях путем заземления тактового генератора программирования и компоновки модуля логики приоритетов внутри оболочки. Например, когда модуль логики приоритетов изготавливается и завершает свою сборку, заключительный этап может включать в себя заземление тактового генератора программирования и заключение в оболочку модуля логики приоритетов. Это поддерживает регулирующее ограничение, что модуль логики приоритетов для использования в ядерной среде класса 1E не является программируемым в полевых условиях. С другой стороны, модуль логики программирования, раскрываемый в настоящем изобретении, способствует упрощению перепрограммирования в производственной среде и/или исследовательской лабораторной среде. Например, модуль логики программирования может быстро и удобно перепрограммироваться разработчиками для развития проектирования программирования или проектирования логики в типовом цикле тестирования-пересмотра. Модуль логики программирования способствует считыванию идентификации логической версии, которая поддерживает инженерную разработку.

Приоритетный модуль логики поддерживает рабочий режим тестирования, который предусматривает непрерывное управление высоконадежного полевого устройства, например соленоида, при одновременном тестировании логики приоритетов. Например, в рабочем режиме тестирования низкоприоритетный вход может возбуждать выход, управляющий полевым устройством, в то время как три самых высокоприоритетных входа возбуждают тестовый выход в соответствии с логикой приоритетов, которая преобладает во время нормального рабочего режима.

Фиг.1 показывает вариант осуществления системы 100 управления процессом, содержащей множество входных систем 110, компонент 130 логики приоритетов, содержащий по меньшей мере один PLM 140, соединенный с базовой платой 135, по меньшей мере одно исполнительное устройство 180 и тестовое устройство 190. В варианте осуществления PLM 140 может содержать CPLD (сложное устройство с программируемой логикой), для которого программируемость может быть отключена. В другом варианте осуществления PLM 140 может содержать программируемую вентильную матрицу (FPGA), для которой программируемость может быть отключена. В варианте осуществления четыре PLM 140 могут быть соединены с базовой платой 135.

В варианте осуществления PLM 140 может быть сертифицирован для использования в системе управления ядерным процессом класса 1E, причем класс 1E определен как классификация безопасности электрооборудования и систем, которые являются существенными для быстрого выключения реактора. В варианте осуществления сертификация для использования в системе управления ядерным процессом класса 1E может включать в себя соответствие стандарту TR (Технические Результаты) 107330 EPRI (Научно-Исследовательский Институт Электронной Энергии). PLM 140 может работать в соответствии с множеством стандартов. Например, в некоторых вариантах осуществления PLM 140 может выполнять требования одного или более следующих стандартов: стандарт IEEE (Институт инженеров по электротехнике и радиоэлектронике) 1012 для проверки и утверждения программного обеспечения, Стандарт IEC (Международная электротехническая комиссия) 61513, IEC 60880, RG (Инструкции и руководство), NRC (Комиссия по ядерной регламентации) 1.180 и NRC DI&C-ISG (Промежуточное руководство для персонала систем цифрового оборудования и управления)-04.

Сертификация устройств управления для использования в системе управления ядерным процессом класса 1E может предусматривать один или больше из следующих тестов. Может выполняться радиационный тест, где PLM 140, соединенные с базовой платой 135, помещаются в камеру и облучаются гамма-лучами. Может выполняться экологический тест, где PLM 140 помещается в камеру и подвергается действию экстремальных температур и влажности. Может выполняться сейсмический тест, где PLM 140 закрепляется в тестовом зажимном приспособлении и встряхивается, чтобы моделировать пять больших землетрясений и одно очень большое землетрясение.

Тест на кондуктивные эмиссии может быть выполнен, когда PLM 140 работает таким образом, что провода, связанные с PLM 140, тестируются на шум, исходящий от них, который мог бы повлиять на другое оборудование. Тест на излученные эмиссии может быть проведен во время работы PLM 140. Может выполняться тест на кондуктивную восприимчивость, в котором шум вводится в провода, связанные с PLM 140, в то время как он работает, чтобы убедиться, может ли PLM 140 продолжать работать корректным образом при этом условии. Может выполняться тест на восприимчивость к излучению, в котором радиочастотный шум излучается в широком частотном диапазоне, в то время как PLM 140 работает, чтобы убедиться, может ли PLM 140 продолжать работать корректным образом при этом условии. Может выполняться тест на восприимчивость к излученному магнитному полю, в котором сильные магнитные поля создаются вокруг PLM 140, в то время как он работает, чтобы убедиться, может ли PLM 140 продолжать работать корректным образом при этом условии.

Может выполняться тест на электрические быстрые переходные скачки кольцевых волн, в котором большие пики напряжения или последовательность пиков напряжения вводятся в линии, соединенные с PLM 140, в то время как он работает, чтобы убедиться, может ли PLM 140 продолжать работать корректным образом при этом условии. Может выполняться тест на электростатический разряд, в котором большие электростатические заряды разряжаются на один из металлических элементов PLM 140 или в воздухе вблизи PLM 140, в то время как он работает, чтобы убедиться, может ли PLM 140 продолжать работать корректным образом при этом условии.

Понятно, что выполнение этих и других тестов может требовать значительного количества времени и финансовых средств. Нужно отметить, что как только данное сложное устройство с программируемой логикой успешно прошло идентифицированные выше тесты, ему не требуется повторять эти тесты просто потому, что запрограммированная логика сложного устройства с программируемой логикой изменилась. Когда программирование изменено, изменения PLM 140 могут поддерживаться просто документом анализа влияния изменения.

Компонент 130 логики приоритетов может принимать множество сигналов от входных систем 110 и может направлять множество сигналов в PLM 140. PLM 140 может формировать множество сигналов, используя логику нормального режима или логику тестового режима, и PLM 140 может направить сигналы в компонент 130 логики приоритетов. Компонент 130 логики приоритетов может послать по меньшей мере один из сигналов в по меньшей мере одно исполнительное устройство 180, и PLM 140 может послать один из сигналов в тестовое устройство 190. В варианте осуществления базовая плата 135 обеспечивает возможность соединения между входными системами 110 и PLM 140 и между PLM 140 и исполнительным(и) устройством(ами) 180. В варианте осуществления базовая плата 135 может обеспечить избыточные источники питания для использования одним или более PLM 140.

Фиг.2 показывает вариант осуществления архитектуры 200 PLM, содержащей PLM 140, оболочку 141, множество входов 120, выход 160 и тестовый выход 165. Каждый вход 120 связан с входным портом 121, выход 160 связан с выходным портом 161 и тестовый выход 165 связан с тестовым выходным портом 166. Архитектура 200 PLM также содержит выбор 126 тестового режима, содержащий сигнал 122 «активировать тест 1», ассоциированный с портом 123 сигнала «активировать тест 1», и сигнал 124 «активировать тест 2», ассоциированный с портом 125 сигнала «активировать тест 2». Архитектура 200 PLM также содержит логику 220 приоритетов, содержащую таблицу 410 арбитражной логики нормального режима и таблицу 420 арбитражной логики тестового режима. Архитектура 200 PLM также содержит тактовый вход 230 порта программирования, ассоциированный с портом 231 программирования. В варианте осуществления входы 120 могут содержать сигналы класса 1E, сформированные устройствами класса 1E.

В варианте осуществления оболочка 141 может содержать устройство, например корпус или кожух, который препятствует доступу к PLM 140. Каждый входной порт 121 может быть ассоциирован с приоритетом, например логикой, запрограммированной в PLM 140. Как используется здесь, термин "входной порт наивысшего приоритета" обозначает "входной порт, ассоциированный с наивысшим приоритетом", термин "входной порт второго по высоте приоритета" обозначает "входной порт, ассоциированный со вторым по высоте приоритетом", термин "входной порт третьего по высоте приоритета" обозначает "входной порт, ассоциированный с третьим по высоте приоритетом", термин "входной порт низшего приоритета" обозначает "входной порт, связанный с самым низким приоритетом" и т.д. PLM 140 может исполнять арбитражную схему, чтобы принимать арбитражное решение между входами 120, выбирая по меньшей мере один вход 120, чтобы сформировать выход 160 и тестовый выход 165, основываясь на приоритетах, ассоциированных с входными портами 121. Понятно, что приоритет среди входов и, следовательно, соотнесение термина "входной порт наивысшего приоритета", "входной порт второго по высоте приоритета" и т.д. с определенными входными портами 121 может изменяться на основе программирования PLM 140.

Логика приоритетов может быть изменена по множеству причин. Например, логика приоритетов может быть изменена, потому что стратегия управления и/или политика управления, связанная с конкретным полевым устройством, могут измениться. Альтернативно, логика приоритетов может быть изменена, потому что PLM 140 может быть предназначен для использования с другим полевым устройством. Как используется здесь, понятие изменения и/или перепрограммирования логики программирования PLM 140 включает в себя идею программирования первой логики приоритета в первый PLM 140 и программирования второй логики приоритета во второй PLM 140, причем как первый PLM 140, так и второй PLM 140 могут быть ранее незапрограммированными и/или быть в состоянии, в котором они были получены от изготовителя сложного устройства с программируемой логикой.

В варианте осуществления PLM 140 может содержать четыре входных порта 121a-d, каждый входной порт 121 конфигурирован, чтобы принимать вход 120. В примере, проиллюстрированном на фиг.2, входной порт 120a ('Вход 1' на чертеже) является сигналом, связанным с входным портом наивысшего приоритета, вход 120b ('Вход 2' на чертеже) является сигналом, связанным с входным портом второго по высоте приоритета, Вход 120c ('Вход 3' на чертеже) является сигналом, связанным с входным портом третьего по высоте приоритета, и Вход 120d ('Вход 4' на чертеже) является сигналом, связанным с входным портом низшего приоритета. PLM 140 может далее содержать выходной порт 161, конфигурированный для передачи выхода 160 ('Выход 1' на чертеже), и тестовый выходной порт 166, конфигурированный для передачи тестового выхода 165 ('Тестовый выход 1' на чертеже). В варианте осуществления, в тестовом режиме, PLM 140 может формировать выход 160 посредством логики нормального режима из входа 120d низшего приоритета и может формировать тестовый выход 165 из всех входов 120a-d с использованием тестовой логики. В варианте осуществления, в тестовом режиме, PLM 140 может формировать выход 160 и тестовый выход 165 с использованием таблицы 420 арбитражной логики тестового режима. В ручном тестовом режиме PLM 140 может сначала выполнить тест "NO-GO" (ничего), активизируя каждый вход 120 отдельно и формируя только тестовый выход 165. PLM 140 может затем выполнить тест "GO" (работать), активизируя каждый вход 120 отдельно и проверяя активацию исполнительных устройств 180, ассоциированных с соответствующими выходами 160.

В варианте осуществления приоритеты, ассоциированные с входными портами 121a-d, могут быть программируемыми в установке, где PLM 140 находится в собранном состоянии, но не программируется в полевой установке, например в энергетической установке или в технологической установке, где PLM 140 используется, чтобы управлять полевыми устройствами. PLM 140 может быть смонтирован, чтобы отключать опцию программируемости. Например, вывод тактового сигнала программирования PLM 140 может быть заземлен. В некоторых контекстах это может упоминаться как ингибитор (схема запрета) программируемости. Настоящее раскрытие предусматривает, что в других вариантах осуществления схема запрета программируемости может быть реализована с другими структурами и/или с использованием других методов. В среде сборки, однако, инженер или техник могут без труда повторно активировать функцию программируемости и повторно программировать логику установления приоритетов. Например, инженер может удалить оболочку, удалить заземление, соединенное с источником тактового сигнала программирования, например перемычку заземления или заземляющий провод, и затем повторно программировать PLM 140, например, используя стандартный кабель интерфейса. В полевой установке, однако, без специализированных инструментов оболочка может быть несъемной, и, следовательно, доступ для повторного программирования PLM 140 может оказаться невозможным. Альтернативно, оболочка может быть съемной в полевых условиях без специальных инструментов, но удаление оболочки может занять некоторое количество времени, которое не совместимо со скрытыми попытками несанкционированного вмешательства в PLM 140. Дополнительно без доступа к диаграммам схемотехники сложного устройства с программируемой логикой и/или без сложного технического знания того, как работает сложное устройство с программируемой логикой, персонал, работающий в полевой среде, не будет знать, как активировать деактивированную функцию программируемости PLM 140.

В варианте осуществления PLM 140 может быть конфигурирован, чтобы принять сигнал выбора 126 тестового режима, указывающий ручной тестовый режим, сигнал, включающий в себя сигнал «активировать тест 1» 122, и сигнал «активировать тест 2» 124. PLM 140 может дополнительно быть соединен с тактовым входом 230 порта программирования, который конфигурирован для тактирования порта 231 программирования, через который может программироваться PLM. В варианте осуществления тактовый вход 230 порта программирования может быть заземлен, чтобы отключить программируемость PLM 140. В варианте осуществления PLM 140 может содержать CPLD, содержащее порт группы совместных тестовых действий (JTAG), и тактовый вход 230 порта программирования может содержать сигнал TCK.

На фиг.3 показан вариант осуществления структуры входа/выхода. В варианте осуществления каждый вход 120 может содержать пару 310 входов, содержащую два сигнала: In A 313, содержащий вход А 312 и вход А LED 314, и In B 317, содержащий вход B 316 и вход B LED 318. Вход А LED 314 и вход B LED 318 может, каждый, содержать полупроводниковый источник света, включающий в себя светодиод (LED), указывающий, когда вход A 312 и/или вход B 316 является активным, соответственно. Вход А 312 и вход B 316 могут генерироваться посредством избыточных инструментальных средств, таких как, например, два независимых датчика. Выбор тестового режима 126 может содержать структуру, подобную паре 310 входов, причем «активировать тест 1» 122 и «активировать тест 2» 124 могут содержать ту же самую структуру, что и In A 313 и In B 317, соответственно.

В варианте осуществления PLM 140 может конфигурироваться, чтобы принимать четыре пары 310 входов. В варианте осуществления каждый выход 160 может содержать пару 320 выходов, содержащую два сигнала: Out A 323, содержащий выход А 322 и выход А LED 324, и Out B 327, содержащий выход B 326 и выход B LED 328, причем выход А LED 324 и выход B LED 328 могут, каждый, содержать LED сигнал, указывающий, когда соответствующие выходы являются активными. В варианте осуществления выход А 322 и выход B 326, каждый, включают в себя 4-битовые сигналы. Каждый тестовый выход 165 может содержать пару 330 тестовых выходов, включающую в себя два сигнала: тестовый Out А 333, включающий в себя тестовый выход А 332 и тестовый выход А LED 334, и тестовый Out B 337, включающий в себя тестовый выход B 336 и тестовый выход B LED 338, причем тестовый выход А LED 334 и тестовый выход B LED 338 могут, каждый, содержать LED сигнал, указывающий, когда соответствующие выходы являются активными. В варианте осуществления тестовый выход А 332 и тестовый выход B 336, каждый, включают в себя 4-битовый сигнал.

Фиг.4 иллюстрирует вариант осуществления функционального поведения PLM 140, представленный в таблице 400 функционального поведения. Таблица 400 функционального поведения включает в себя таблицу 410 арбитражной логики нормального способа, таблицу A 420a арбитражной логики тестового режима и таблицу B 420b арбитражной логики тестового режима, причем '1' указывает сигнал '1', '0' указывает сигнал '0' и 'x' указывает <безразлично>. Подразумевается, что в варианте осуществления функциональное поведение, представленное таблицей 400 функционального поведения, может быть реализовано множеством путей, например на языке описания аппаратного обеспечения (VHDL), который является функциональным по сути и не основан на таблице перекодировки.

В варианте осуществления функциональное поведение PLM 140 в нормальном режиме может быть представлено в таблице 410 арбитражной логики нормального режима. Например, выход PLM 140, реагирующий на входы PLM 140, может быть представлен таблицей 410 арбитражной логики нормального режима. Функциональное поведение PLM 140 относительно тестовых выходов 330 в тестовом режиме может быть представлено таблицей A 420a арбитражной логики тестового режима. Функциональное поведение PLM 140 относительно выходов 320 в тестовом режиме может быть представлено таблицей B 420b арбитражной логики тестового режима. Отметим, что в тестовом режиме выходы 320 зависят только от низкоприоритетных входов: входа 4A и входа 4B.

В варианте осуществления запись выбора тестового режима в таблице 400 функционального поведения может содержать «выбор тестового режима» 126 и может быть произведением сигнала «активировать тест 1» 122 и сигнала «активировать тест 2» 124. В варианте осуществления установка сигнала «активировать тест 1» 122 и «активировать тест 2» 124 на '1' может указывать на тестовый режим. В варианте осуществления (Вход1 A, Вход1 B) может указывать сигнал входа 120, ассоциированный с входным портом наивысшего приоритета, (Вход2 A, Вход2 B) может указывать сигнал входа 120, ассоциированный с входным портом второго по высоте приоритета, (Вход3 A, Вход3 B) может указывать на сигнал входа 120, ассоциированный с входным портом третьего по высоте приоритета, (Вход4 A, Вход4 B) может указывать на сигнал входа 120, ассоциированный с входным портом низшего приоритета, (Выход1 A, Выход1 B) может указывать выход 160 и (тестовый Выход1 A, Тестовый Выход1 B) может указывать тестовый выход 165.

Например, в нормальном режиме, если сигнал входа1 А есть '1', то PLM 140 может установить значение сигнала выхода1 А в '1', значение сигнала выхода1 B в '0', значение сигнала тестового выхода1 А в '1' и значение сигнала тестового выхода1 B в '0', независимо от значений других входов. В другом примере, в тестовом режиме, если сигнал входа4 А есть '1', PLM 140 может установить значение сигнала выхода1 А сигнал в '1', значение сигнала выхода1 B в '0' и значения сигнала тестового выхода1 А и сигнала тестового выхода1 B сигнал могут быть определены тремя входами более высокого приоритета. Понятно, что логика 220 приоритетов, представленная таблицами 410, 420a и 420b, может быть изменена путем перепрограммирования PLM 140. Далее понятно, что различные PLM 140, связанные с той же самой базовой платой 135 и/или тем же самым компонентом 130 логики приоритетов, могут быть запрограммированы с различной логикой приоритетов. Таким образом, различные PLM 140, связанные с той же самой базовой платой 135 и/или тем же самым компонентом 130 логики приоритетов, могут, каждый, осуществлять различную таблицу 400 функционального поведения.

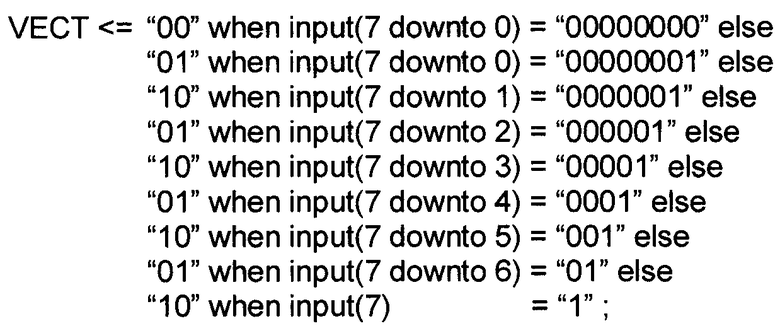

Как указано выше, описание на фиг.4 таблицы 400 функционального поведения является устройством для сформулированного выше и/или описывает поведение PLM 140 в примерном варианте осуществления и не подразумевает какой-либо конкретной реализации представленной функциональности. В варианте осуществления приоритетная логика, представленная концептуально в таблице 400 функционального поведения, может быть реализована в операторах VHDL, синтезирована и загружена в сложное устройство программируемой логики PLM 140. Например, в варианте осуществления логика приоритетов может быть осуществлена рядом операторов VHDL, которые напоминают структуры if-elsif-end (выбор (условный переход)-конец оператора) языков программирования.

Например, ROUT_VECT может определить двухбитовый вектор, который возбуждает два регулярных выхода: выход1 A и выход1 B, и TOUT_VECT может определить двухбитовый вектор, который возбуждает два тестовых выхода: тестовый выход1 A и тестовый выход1 B. Двухбитовый вектор VECT может определить промежуточное значение, которое может условно использоваться в определении ROUT_VECT и/или TOUT_VECT. VECT может быть определен в операторе VHDL, которое напоминает if-elsif-end структуры языков программирования, следующим образом:

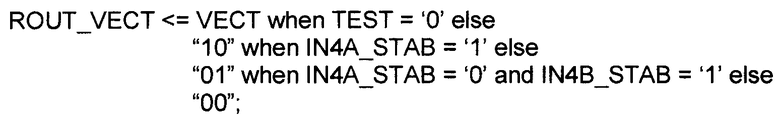

"input" (вход) может содержать вектор входов 120, например вход1 A, вход B, вход2 A, вход2 B, вход3 A, вход3 B, вход4 A и вход4 B. Двухбитовый вектор ROUT_VECT может быть определен в операторе VHDL, который напоминает if-elsif-end структуры языков программирования, следующим образом:

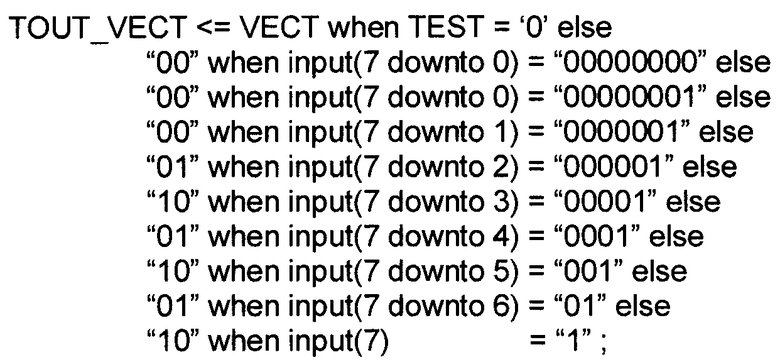

"TEST" (тест) может быть определен на основе выбора 126 тестового режима таким образом, что, когда тест не выбран, TEST имеет значение 0. "IN4A_STAB" может содержать вход4 A, и "IN4B_STAB" может содержать вход4 B из входов 120. Когда тестовый режим операции не выбран, вектору ROUT_VECT назначается значение, основанное на промежуточном значении VECT, и, следовательно, выход1 A и выход1 B возбуждаются в соответствии с логикой приоритетов нормального режима. Когда тестовый режим операции выбран, вектору ROUT_VECT назначается значение, основанное только на четвертом входе, входе низкого приоритета, и, следовательно, выход1 A и выход1 B возбуждаются входом низкого приоритета. Двухбитовый вектор TOUT_VECT может быть определен в операторе VHDL, который подобен if-elsif-end структурам языков программирования:

Когда тестовый режим операции не выбран, вектору TOUT_VECT назначается значение, основанное на промежуточном значении VECT, и, следовательно, тестовый выход1 A и тестовый выход1 B возбуждаются в соответствии с логикой приоритетов нормального режима. Когда тестовый режим операции выбран, вектору TOUT_VECT назначается значение, существенно подобное значениям VECT, за исключением того, что, когда вход1 A, вход1 B, вход2 A, вход2 B, вход3 A, и вход3 B все являются нулевыми значениями, тестовый выход1 A и тестовый выход1 B являются нулевыми значениями, несмотря на значения вход4 A и вход4 B.

Понятно, что приоритеты, которые определены фрагментами VHDL выше, могут быть легко пересмотрены, изменяя фрагменты VHDL, чтобы кодировать другие установления приоритетов и/или другие таблицы истинности. Кроме того, понятно, что фрагменты VHDL, приведенные выше, могут быть не полными и могут основываться на дополнительных операторах VHDL при практической реализации кодирования.

Фиг.5 иллюстрирует один вариант осуществления способа 500 тестирования, который может использоваться, чтобы проверить корректную операцию по меньшей мере одного компонента, содержащегося в системе 100 управления процессом. Например, способ 500 тестирования может быть осуществлен по меньшей мере частично в PLM 140. В варианте осуществления каждый PLM 140 в системе 100 управления процессом может осуществлять способ 500 тестирования независимо от других PLM 140 в системе 100 управления процессом.

Способ 500 тестирования может начаться в блоке 502, где способ может определить, установлен ли сигнал выбора тестового режима. В варианте осуществления сигнал выбора тестового режима включает в себя выбор 126 тестового режима. Способ 500 тестирования может перейти к блоку 506, если условие в блоке 502 удовлетворено, или к блоку 504, если условие в блоке 502 не удовлетворено. В блоке 504 способ 500 тестирования может сформировать по меньшей мере один выход 160 и тестовый выход 165 с использованием логики нормального режима, например, отображая входы на выходы с использованием таблицы 410 арбитражной логики нормального режима, и способ может завершиться. В блоке 506 способ 500 тестирования может определить, работает ли PLM 140 в ручном тестовом режиме. Способ 500 тестирования может перейти блоку 510, если условие в блоке 506 удовлетворено, и может перейти к блоку 530, если условие в блоке 506 не удовлетворено.

В блоке 510 способ может установить сигнал инициирования теста. В варианте осуществления установка сигнала инициирования теста может содержать установку сигнала «активировать тест 1» 122 и сигнала «активировать тест 2» 124 на '1'. Способ может затем перейти к блоку 512, чтобы выполнить тест NO-GO. В варианте осуществления тест NO-GO включает в себя посылку входа 120 к PLM 140, чтобы сформировать тестовый выход 165 и записать множество результатов тестирования. В варианте осуществления тест NO-GO может быть выполнен для всех входов 120, конфигурируя каждый вход 120, чтобы активировать исполнительное устройство 180, ассоциированное с входом 120. От блока 512 способ может перейти к блоку 514 и может оценить результаты тестирования из теста NO-GO. Способ может перейти к блоку 516 и сбросить сигнал активирования теста. В варианте осуществления сброс сигнала активирования теста может содержать установку сигнала «активировать тест 1» 122 и сигнала «активировать тест 2» 124 в '0'. Способ может перейти к блоку 518, выполнить тест GO и перейти к блоку 520. В варианте осуществления тест GO включает посылку входа 120 к PLM 140, чтобы сформировать выход 160 для исполнительного устройства 180, верификацию активации исполнительного устройства 180 и запись множества результатов тестирования. В блоке 520 способ 500 тестирования может оценить результаты тестирования из теста GO, и способ может быть завершен.

В блоке 530 способ 500 тестирования может формировать множество выходов из множества входов, используя логику тестирования. В варианте осуществления выход 160 может быть сформирован из входа 120, который ассоциирован с самым низким приоритетом. В варианте осуществления выход 160 может быть сформирован посредством таблицы B 420b арбитражной логики тестового режима. Способ может перейти к блоку 532, чтобы сформировать тестовый выход 165 для каждого входа 120 и записать множество результатов тестирования. В варианте осуществления тестовый выход 165 может быть сформирован посредством таблицы А 420а арбитражной логики тестового режима. Способ может перейти к блоку 534, может оценить результаты тестирования, и способ может быть завершен.

Фиг.6 иллюстрирует компьютерную систему 600, подходящую для реализации одного или более вариантов осуществления, раскрытых здесь. Компьютерная система 600 содержит процессор 682 (который может упоминаться как центральный процессорный блок или CPU), который осуществляет связь с устройствами памяти, включая вторичное хранилище 684, постоянное ЗУ (ROM) 686, память произвольного доступа (RAM) 688, устройства 690 ввода/вывода (I/O) и устройства 692 подключения к сети. Процессор 682 может быть осуществлен как одна или более микросхем CPU.

Понятно, что путем программирования и/или загрузки исполняемых инструкций на компьютерную систему 600 по меньшей мере одно из CPU 682, RAM 688 и ROM 686 изменяется, преобразовывая компьютерную систему 600 частично в конкретную машину или устройство, имеющее новую функциональность, раскрываемую в настоящем описании. Для электронной техники и техники программирования существенно, что функциональность, которая может быть реализована путем загрузки исполняемого программного обеспечения в компьютер, может быть преобразована в аппаратную реализацию хорошо известными правилами проектирования. Решения относительно реализации концепции в программном обеспечении или в аппаратных средствах, как правило, зависят от соображений стабильности конструкции и ряда блоков, которые будут производиться, а не вопросов, связанных с переходом от области программного обеспечения в область аппаратных средств. В принципе, конструкция, которая подвергается частому изменению, может предпочтительно осуществляться в программном обеспечении, потому что повторное преобразование в аппаратных средствах является более дорогостоящим, чем повторное преобразование в программном обеспечении. В принципе, конструкция, которая стабильна, которая будет производиться в большом объеме, может быть предпочтительной для реализации в аппаратных средствах, например, на специализированной интегральной схеме (ASIC), потому что для массового производства выполнение в аппаратных средствах может быть менее дорогостоящим, чем выполнение в программном обеспечении. Часто конструкция может разрабатываться и тестироваться в форме программного обеспечения и позже преобразовываться, по известным правилам проектирования, в эквивалентное выполнение в аппаратных средствах на специализированной интегральной схеме, которая реализует аппаратными средствами инструкции программного обеспечения. Подобно тому, как машина, управляемая новой ASIC, является конкретной машиной или устройством, компьютер, который был запрограммирован и/или загружен исполняемыми инструкциями, может рассматриваться как конкретная машина или устройство.

Вторичное хранилище 684, как правило, состоит из одного или более дисководов или лентопротяжных механизмов и используется для энергонезависимого хранения данных и как устройство хранения данных переполнения, если RAM 688 не является достаточно большой, чтобы содержать все рабочие данные. Вторичное хранилище 684 может использоваться для хранения программ, которые загружаются в RAM 688, когда такие программы выбираются для исполнения. ROM 686 используется, чтобы хранить инструкции и, возможно, данные, которые считываются во время выполнения программы. ROM 686 является энергонезависимым устройством памяти, которое обычно имеет малый объем памяти относительно большего объема памяти вторичного хранилища 684. RAM 688 используется, чтобы хранить изменчивые данные и, возможно, хранить инструкции. Доступ к ROM 686 и RAM 688 обычно является более быстрым, чем к вторичному хранилищу 684. Вторичное хранилище 684, RAM 688 и/или ROM 686 могут упоминаться в некоторых контекстах как некратковременные хранилища и/или некратковременные считываемые компьютером носители данных.

Устройства 690 ввода/вывода могут включать в себя принтеры, видеомониторы, жидкокристаллические дисплеи (LCD), дисплеи c сенсорным экраном, клавиатуры, клавишные панели, переключатели, диски, мыши, шаровые манипуляторы (трекболы), устройства распознавания голоса, устройства считывания с карт, считыватели перфоленты или другие известные устройства ввода.

Устройства 692 подключения к сети могут принимать форму модемов, банков модемов, карт Ethernet, интерфейсных плат универсальной последовательной шины (USB), последовательных интерфейсов, карт кольцевой сети с маркерным доступом, карт интерфейса передачи данных по волоконно-оптической сети (FDDI), карт беспроводной локальной сети (WLAN), карт радио приемопередатчика, таких как CDMA (множественный доступ с кодовым разделением), GSM (глобальная система мобильной связи), LTE (долгосрочное развитие), WiMAX (общемировая совместимость широкополосного беспроводного доступа) и/или другие карты радио приемопередатчика протокола радиоинтерфейса и другие известные сетевые устройства. Эти устройства 692 подключения к сети позволяют процессору 682 осуществлять связь с Интернетом или одним или более Интранетом. При таком соединении с сетью процессор 682 может получать информацию от сети или может выводить информацию в сеть в ходе выполнения вышеописанных этапов способа. Такая информация, которая часто представляется как последовательность инструкций для выполнения с использованием процессора 682, может быть получена из сети и выведена в сеть, например, в форме компьютерного сигнала данных, воплощенного в несущей волне.

Такая информация, которая может включать в себя данные или инструкции, которые должны выполняться, например, с использованием процессора 682, может быть получена из сети и выведена в сеть, например, в форме компьютерного видеосигнала данных или сигнала, воплощенного в несущей волне. Сигнал базовой полосы или сигнал, воплощенный в несущей волне, сформированной устройствами 692 подключения к сети, может распространяться в или на поверхности электрических проводников, в коаксиальных кабелях, в волноводах, в оптическом волноводе, например оптическом волокне, или в воздушном пространстве или свободном пространстве. Информация, содержащаяся в сигнале базовой полосы, или сигнале, включенном в несущую волну, может быть упорядочена согласно различным последовательностям, как может быть желательно для обработки или для формирования информации, или передачи или приема информации. Сигнал базовой полосы или сигнал, включенный в несущую волну, или другие типы сигналов, в настоящее время используемых, или тех, которые будут разработаны в будущем, могут генерироваться согласно разным методам, хорошо известным специалистам в данной области техники. Сигнал базовой полосы и/или сигнал, включенный в несущую волну, могут упоминаться в некоторых контекстах как переходный (кратковременный) сигнал.

Процессор 682 выполняет инструкции, коды, компьютерные программы, скрипты, к которым он получает доступ с жесткого диска, дискеты, оптического диска (эти различные, основанные на дисках системы могут рассматриваться как вторичное хранение 684), ROM 686, RAM 688 или устройства 692 подключения к сети. В то время как показан только один процессор 682, может иметься множество процессоров. Таким образом, хотя инструкции могут обсуждаться как выполняемые процессором, инструкции могут выполняться одновременно, последовательно, иным образом одним или несколькими процессорами. Инструкции, коды, компьютерные программы, скрипты и/или данные, к которым можно получить доступ от вторичного хранилища 684, например, жестких дисков, дискет, оптических дисков и/или других устройств, ROM 686 и/или RAM 688, могут упоминаться в некоторых контекстах как некратковременные инструкции и/или некратковременная информация.

В варианте осуществления компьютерная система 600 может содержать два или более компьютеров, осуществляющих связь друг с другом, которые взаимодействуют для выполнения задачи. Например, но не в качестве ограничения, приложение может быть разделено таким способом, чтобы позволить одновременную и/или параллельную обработку инструкций приложения. Альтернативно, данные, обрабатываемые приложением, могут быть разделены таким способом, чтобы позволять одновременную и/или параллельную обработку различных частей набора данных двумя или более компьютерами. В варианте осуществления программное обеспечение визуализации может использоваться компьютерной системой 600, чтобы обеспечить функциональность ряда серверов, которая непосредственно не связана с числом компьютеров в компьютерной системе 600. Например, виртуализация программного обеспечения может обеспечить двадцать виртуальных серверов на четырех физических компьютерах. В варианте осуществления функциональность, раскрытая выше, может быть обеспечена путем исполнения приложения и/или приложений в «облачной» вычислительной среде. Облачные вычисления могут содержать обеспечение вычислительных услуг через сетевое соединение с использованием динамически масштабируемых вычислительных ресурсов. Облачное вычисление может поддерживаться, по меньшей мере, частично, программным обеспечением виртуализации. Облачная вычислительная среда может быть установлена предприятием и/или может быть взята внаем по принципу «по необходимости» у поставщика третьей стороны. Некоторые облачные вычислительные среды могут содержать облачные вычислительные ресурсы, принадлежащие и управляемые предприятием, а также облачные вычислительные ресурсы, нанятые и/или арендованные у поставщика третьей стороны.

В варианте осуществления некоторая или вся функциональность, раскрытая выше, может предоставляться как компьютерный программный продукт. Компьютерный программный продукт может содержать один или более считываемых компьютером носителей данных, имеющих используемый компьютером программный код, воплощенный на них, реализующий функциональность, раскрытую выше. Компьютерный программный продукт может содержать данные, структуры данных, файлы, исполняемые инструкции и другую информацию. Компьютерный программный продукт может быть воплощен в съемных компьютерных носителях данных и/или несъемных компьютерных носителях данных. Съемный считываемый компьютером носитель данных может содержать, без ограничения, перфоленту, магнитную ленту, магнитный диск, оптический диск, твердотельную микросхему памяти, например аналоговую магнитную ленту, компакт-диск, CD-ROM диски, дискеты, флэшки, цифровые карты, мультимедийные карты и другие. Компьютерный программный продукт может быть пригодным для загрузки, компьютерной системой 600, по меньшей мере, части содержания компьютерного программного продукта во вторичное хранилище 684, ROM 686, RAM 688 и/или другую энергонезависимую память и энергозависимую память компьютерной системы 600. Процессор 682 может обрабатывать исполняемые инструкции и/или данные, частично путем непосредственного доступа к компьютерному программному продукту, например путем считывания с диска CD-ROM, вставленного в периферийный дисковод компьютерной системы 600. Компьютерный программный продукт может содержать инструкции, которые способствуют загрузке и/или копированию данных, структур данных, файлов и/или исполняемых инструкций во вторичное хранилище 684, ROM 686, RAM 688 и/или другую энергонезависимую память и энергозависимую память компьютерной системы 600.

Хотя несколько вариантов осуществления были обеспечены в настоящем раскрытии, понятно, что раскрытые системы и способы могут быть воплощены во многих других определенных формах без отклонения от сущности или объема настоящего раскрытия. Представленные примеры следует рассматривать как иллюстративные, а не как ограничивающие, и не предполагается ограничение приведенными выше деталями. Например, различные элементы или компоненты могут быть объединены или встроены в другую систему, или определенные опции могут быть опущены или не реализованы.

Кроме того, методы, системы, подсистемы и способы, описанные и проиллюстрированные в различных вариантах осуществления как дискретные или отдельные, могут быть объединены или интегрированы с другими системами, модулями, методами или способами без отклонения от объема настоящего раскрытия. Другие элементы, показанные или обсужденные как непосредственно связанные или осуществляющие связь друг с другом, могут быть связаны косвенно или осуществлять связь через некоторый интерфейс, устройство или промежуточный компонент электрически, механически или иным образом. Другие примеры изменений, подстановок и модификаций являются понятными для специалистов в данной области техники и могут быть выполнены без отклонения от сущности и объема, раскрытых здесь.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИКА ИНТЕРФЕЙСА ДЛЯ МНОГОЯДЕРНОЙ "СИСТЕМЫ НА КРИСТАЛЛЕ" (SoC) | 2010 |

|

RU2470350C2 |

| СИСТЕМА УПРАВЛЕНИЯ ТЕСТИРОВАНИЕМ ПРОГРАММНОГО ОБЕСПЕЧЕНИЯ | 2021 |

|

RU2774659C1 |

| УСТРОЙСТВО ДЛЯ БЫСТРОГО ДЕТЕКТИРОВАНИЯ ИНФЕКЦИОННЫХ АГЕНТОВ | 2012 |

|

RU2600812C2 |

| СПОСОБ И УСТРОЙСТВО ТЕСТИРОВАНИЯ МНОГОПОРТОВОГО МАССИВА ПАМЯТИ НА СКОРОСТИ | 2007 |

|

RU2408093C2 |

| ЭЛЕКТРОННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1998 |

|

RU2216796C2 |

| СИСТЕМА СВЯЗИ | 1991 |

|

RU2117405C1 |

| УСТРОЙСТВО И СПОСОБ ТЕСТИРОВАНИЯ СТАНДАРТНОГО ФУНКЦИОНАЛЬНОГО БЛОКА В ИНТЕГРАЛЬНОЙ СХЕМЕ С ИСПОЛЬЗОВАНИЕМ JTAG | 1996 |

|

RU2198411C2 |

| УПРАВЛЕНИЕ КОЛЕБАНИЯМИ ИНИЦИАТОРА ВВОДА/ВЫВОДА ПРИ ПЕРЕДАЧЕ | 2014 |

|

RU2644536C2 |

| УСТРОЙСТВО ДЛЯ ИНИЦИИРОВАНИЯ ЭЛЕКТРИЧЕСКИХ НАГРУЗОК, СПОСОБ ИНИЦИИРОВАНИЯ ЭЛЕКТРИЧЕСКИХ НАГРУЗОК ПО ИСТЕЧЕНИИ ПРЕДВАРИТЕЛЬНО УСТАНОВЛЕННЫХ ВРЕМЕННЫХ ЗАДЕРЖЕК И ДИСТАНЦИОННОЕ ЭЛЕКТРИЧЕСКОЕ УСТРОЙСТВО ЗАДЕРЖКИ ДЛЯ ИНИЦИИРОВАНИЯ ЭЛЕКТРИЧЕСКОЙ НАГРУЗКИ | 1990 |

|

RU2077699C1 |

| Комплекс тестирования встроенного программного обеспечения электронных устройств | 2022 |

|

RU2783906C1 |

Изобретение относится к области систем управления ядерным процессом. Техническим результатом является повышение эффективности тестирования модуля логики приоритетов. В системе управления ядерным процессом обеспечен модуль логики приоритетов (PLM). Модуль логики приоритетов содержит множество входных портов, каждый входной порт ассоциирован с одним из множества приоритетов, множество выходных портов и порт выбора тестового режима, ассоциированный с сигналом выбора тестового режима. Сигнал выбора тестового режима выбирает один из нормального режима или тестового режима, каждый режим ассоциирован с согласованием сигналов, принимаемых входными портами, с сигналами, посылаемыми выходными портами. Модуль логики приоритетов дополнительно содержит конфигурируемую схему логики приоритетов, причем схема логики приоритетов отображает один из входных портов на один из выходных портов. 4 н. и 12 з.п. ф-лы, 6 ил.

1. Модуль логики приоритетов (PLM) в системе управления ядерным процессом, содержащий:

множество входных портов, причем каждый входной порт ассоциирован с одним из множества приоритетов, при этом упомянутое множество входных портов содержит четыре входных порта, каждый из которых сконфигурирован с возможностью принимать пару входов, ассоциированную с приоритетом;

множество выходных портов, причем упомянутое множество выходных портов содержит один выходной порт, сконфигурированный с возможностью отправлять одну пару выходов на исполнительное устройство, и один тестовый выходной порт, сконфигурированный с возможностью отправлять одну пару тестовых выходов на тестовое устройство;

порт выбора тестового режима, ассоциированный с сигналом выбора тестового режима, причем сигнал выбора тестового режима выбирает один из нормального режима и тестового режима, при этом каждый режим ассоциирован с согласованием сигналов, принимаемых входными портами, с сигналами, отправляемыми выходными портами;

конфигурируемую логику приоритетов, причем схема логики приоритетов отображает один из входных портов на один из выходных портов,

при этом модуль логики приоритетов сертифицирован для использования в системе управления ядерным процессом класса 1Е, причем входные порты сконфигурированы с возможностью принимать сигналы класса 1Е, содержащие множество пар входов, и причем выходные порты конфигурированы с возможностью отправлять сигналы, содержащие множество пар выходов,

при этом (Вход1 А, Вход1 В) является парой входов, ассоциированной с входным портом наивысшего приоритета, (Вход2 А, Вход2 В) является парой входов, ассоциированной с входным портом второго по высоте приоритета, (Вход3 А, Вход3 В) является парой входов, ассоциированной с входным портом третьего по высоте приоритета, (Вход4 А, Вход4 В) является парой входов, ассоциированной с входным портом четвертого по высоте приоритета, выбор тестового режима является сигналом, установленным в ′0′, (Выход1 А, Выход1 В) является парой выходов, (Тестовый Выход1 А, Тестовый Выход1 В) является парой тестовых выходов, причем эти пара выходов и пара тестовых выходов формируются из упомянутых пар входов, при этом следующая таблица представляет функциональное поведение логики приоритетов:

где ′1′ указывает сигнал ′1′, ′0′ указывает сигнал ′0′ и ′x′ указывает <безразлично>.

2. Модуль логики приоритетов по п. 1, причем модуль логики приоритетов содержит сложное устройство с программируемой логикой (CPLD).

3. Модуль логики приоритетов по п. 1, в котором логика приоритетов является компонентом в пределах модуля логики приоритетов, причем конфигурирование логики приоритетов включает в себя изменение по меньшей мере одного логического компонента.

4. Модуль логики приоритетов по п. 1, в котором логика приоритетов является конфигурируемой во время изготовления.

5. Модуль логики приоритетов по п. 1, причем модуль логики приоритетов является непрограммируемым в полевых условиях.

6. Модуль логики приоритетов по п. 1, причем модуль логики приоритетов дополнительно содержит тестовый выходной порт.

7. Модуль логики приоритетов по п. 1, причем модуль логики приоритетов сконфигурирован с возможностью отправлять по меньшей мере один выходной сигнал, сформированный из входного сигнала, принятого входным портом, ассоциированным с самым низким приоритетом.

8. Модуль логики приоритетов (PLM) в системе управления ядерным процессом, содержащий:

множество входных портов, причем каждый входной порт ассоциирован с одним из множества приоритетов, при этом упомянутое множество входных портов содержит четыре входных порта, каждый из которых сконфигурирован с возможностью принимать пару входов, ассоциированную с приоритетом;

множество выходных портов, причем упомянутое множество выходных портов содержит один выходной порт, сконфигурированный с возможностью отправлять одну пару выходов на исполнительное устройство, и один тестовый выходной порт, сконфигурированный с возможностью отправлять одну пару тестовых выходов на тестовое устройство;

порт выбора тестового режима, ассоциированный с сигналом выбора тестового режима, причем сигнал выбора тестового режима выбирает один из нормального режима и тестового режима, при этом каждый режим ассоциирован с согласованием сигналов, принимаемых входными портами, с сигналами, отправляемыми выходными портами;

конфигурируемую логику приоритетов, причем схема логики приоритетов соотносит один из входных портов с одним из выходных портов,

при этом модуль логики приоритетов сертифицирован для использования в системе управления ядерным процессом класса 1Е, причем входные порты сконфигурированы с возможностью принимать сигналы класса 1Е, содержащие множество пар входов, и причем выходные порты конфигурированы с возможностью отправлять сигналы, содержащие множество пар выходов,

причем (Вход1 А, Вход1 В) является парой входов, ассоциированной с входным портом наивысшего приоритета, (Вход2 А, Вход2 В) является парой входов, ассоциированной с входным портом второго по высоте приоритета, (Вход3 А, Вход3 В) является парой входов, ассоциированной с входным портом третьего по высоте приоритета, (Вход4 А, Вход4 В) является парой входов, ассоциированной с входным портом четвертого по высоте приоритета, выбор тестового режима является сигналом, установленным в ′1′, (Выход1 А, Выход1 В) является парой выходов, (Тестовый Выход1 А, Тестовый Выход1 В) является парой тестовых выходов, причем эти пара выходов и пара тестовых выходов формируются из упомянутых пар входов, при этом следующие таблицы представляют функциональное поведение логики приоритетов:

где ′1′ указывает сигнал ′1′, ′0′ указывает сигнал ′0′ и ′x′ указывает <безразлично>.

9. Модуль логики приоритетов по п. 8, причем модуль логики приоритетов содержит сложное устройство с программируемой логикой (CPLD).

10. Модуль логики приоритетов по п. 8, в котором логика приоритетов является компонентом в пределах модуля логики приоритетов, причем конфигурирование логики приоритетов включает в себя изменение по меньшей мере одного логического компонента.

11. Модуль логики приоритетов по п. 8, в котором логика приоритетов является конфигурируемой во время изготовления.

12. Модуль логики приоритетов по п. 8, причем модуль логики приоритетов не является программируемым в полевых условиях.

13. Модуль логики приоритетов по п. 8, причем модуль логики приоритетов дополнительно содержит тестовый выходной порт.

14. Модуль логики приоритетов по п. 8, причем модуль логики приоритетов конфигурирован с возможностью отправлять по меньшей мере один выходной сигнал, сформированный из входного сигнала, принятого входным портом, ассоциированным с самым низким приоритетом.

15. Способ тестирования, содержащий этапы, на которых:

выбирают тестовый режим из сигнала выбора тестового режима;

принимают множество входных сигналов, причем каждый входной сигнал является сигналом класса 1Е, ассоциированным с приоритетом;

формируют по меньшей мере один выходной сигнал из входных сигналов;

формируют выходной сигнал из входного сигнала самого низкого приоритета;

формируют тестовый выходной сигнал из входных сигналов;

отправляют выходной сигнал на исполнительное устройство; и

отправляют тестовый выходной сигнал на устройство тестирования; и

конфигурируют арбитражную логику,

причем способ осуществляется модулем логики приоритетов (PLM), при этом сигнал выбора тестового режима указывает нормальный режим или тестовый режим, причем входные сигналы содержат множество пар входов, выходной сигнал содержит пару выходов и тестовый выходной сигнал содержит пару тестовых выходов;

причем (Вход1 А, Вход1 В) является парой входов, ассоциированной с входным портом наивысшего приоритета, (Вход2 А, Вход2 В) является парой входов, ассоциированной с входным портом второго по высоте приоритета, (Вход3 А, Вход3 В) является парой входов, ассоциированной с входным портом третьего по высоте приоритета, (Вход4 А, Вход4 В) является парой входов, ассоциированной с входным портом четвертого по высоте приоритета, выбор тестового режима является сигналом, установленным в ′0′, (Выход1 А, Выход1 В) является парой выходов, (Тестовый Выход1 А, Тестовый Выход1 В) является парой тестовых выходов, причем эти пара выходов и пара тестовых выходов формируются из упомянутых пар входов, при этом следующая таблица представляет функциональное поведение логики приоритетов:

где ′1′ указывает сигнал ′1′, ′0′ указывает сигнал ′0′ и ′x′ указывает <безразлично>.

16. Способ тестирования, содержащий этапы, на которых:

выбирают тестовый режим из сигнала выбора тестового режима;

принимают множество входных сигналов, причем каждый входной сигнал является сигналом класса 1Е, ассоциированным с приоритетом;

формируют по меньшей мере один выходной сигнал из входных сигналов;

формируют выходной сигнал из входного сигнала самого низкого приоритета;

формируют тестовый выходной сигнал из входных сигналов;

отправляют выходной сигнал на исполнительное устройство; и

отправляют тестовый выходной сигнал на устройство тестирования; и

конфигурируют арбитражную логику,

причем способ осуществляется модулем логики приоритетов (PLM), при этом сигнал выбора тестового режима указывает нормальный режим или тестовый режим, причем входные сигналы содержат множество пар входов, выходной сигнал содержит пару выходов и тестовый выходной сигнал содержит пару тестовых выходов,

причем (Вход1 А, Вход1 В) является парой входов, ассоциированной с входным портом наивысшего приоритета, (Вход2 А, Вход2 В) является парой входов, ассоциированной с входным портом второго по высоте приоритета, (Вход3 А, Вход3 В) является парой входов, ассоциированной с входным портом третьего по высоте приоритета, (Вход4 А, Вход4 В) является парой входов, ассоциированной с входным портом четвертого по высоте приоритета, выбор тестового режима является сигналом, установленным в ′1′, (Выход1 А, Выход1 В) является парой выходов, (Тестовый Выход1 А, Тестовый Выход1 В) является парой тестовых выходов, причем эти пара выходов и пара тестовых выходов формируются из упомянутых пар входов, при этом следующие таблицы представляют функциональное поведение логики приоритетов:

при этом функциональное поведение пары выходов представлено в следующей таблице:

где ′1′ указывает сигнал ′1′, ′0′ указывает сигнал ′0′ и ′x′ указывает <безразлично>.

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| US 7084660 B1, 01.08.2006 | |||

| US 6324676 B1, 27.11.2001 | |||

| US 7093168 B2, 15.08.2006 | |||

| ЭФФЕКТИВНОЕ ИСПРАВЛЕНИЕ ПРОГРАММ | 2005 |

|

RU2377637C2 |

Авторы

Даты

2016-08-27—Публикация

2011-11-10—Подача