Изобретение относится к области аналоговой микроэлектроники и может быть использовано в структуре аналого-цифровых интерфейсов и IP-модулей систем автоматики, связи и телекоммуникаций, допускающих работу в условиях высоких температур.

В современной микросхемотехнике находит широкое применение архитектура ОУ на основе входного дифференциального каскада, токовые выходы которого связаны выходным промежуточным каскадом, реализуемым по схеме так называемого «перегнутого» каскода [1-14]. Данное схемотехническое решение используется во многих серийных российских и зарубежных ОУ, в т.ч. на полевых и биполярных транзисторах.

Ближайшим прототипом является операционный усилитель, представленный в патенте US 6762646, fig. 3, 2004 г. Он содержит (фиг. 1) первый 1 и второй 2 входы, входной дифференциальный каскад 3, первый 4 и второй 5 транзисторы входного дифференциального каскада 3, статический режим которых устанавливается по токовому входу 6 первым 7 источником опорного тока, связанным с первой 8 шиной источника питания, первый 9 токовый выход входного дифференциального каскада 3, связанный со второй 10 шиной источника питания через второй 11 источник опорного тока и подключенный к истоку первого 12 выходного полевого транзистора, второй 13 токовый выход входного дифференциального каскада 3, соединенный со второй 10 шиной источника питания через третий 14 источник опорного тока и подключенный к истоку второго 15 выходного полевого транзистора, затвор которого связан с затвором первого 12 выходного полевого транзистора, токовое зеркало 16, вход которого соединен со стоком первого 12 выходного полевого транзистора, а выход подключен к стоку второго 15 выходного полевого транзистора, причем неинвертирующий токовый выход 17 токового зеркала 16 согласован с первой 8 шиной источника питания.

Существенный недостаток ОУ-прототипа состоит в том, что его схема не реализуется в рамках разрабатываемых научно-исследовательскими организациями Союзного государства арсенид-галлиевых технологических процессов [15], допускающих изготовление микросхем только на p-n-p биполярных и полевых JFet транзисторов с n-каналом. Кроме этого, известная схема не обеспечивает по токовому выходу Вых.i работу в режиме класса АВ - его максимальный выходной ток не превышает статическое значение токов второго 11 и третьего 14 источников опорного тока.

Основная задача предполагаемого изобретения состоит в создании схемы арсенид-галлиевого операционного усилителя на p-n-p биполярных и nJFet полевых транзисторах, работающего по выходу в режиме класса АВ при сравнительно низкоомных сопротивлениях нагрузки (Rн до 2 кОм).

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем первый 1 и второй 2 входы, входной дифференциальный каскад 3, первый 4 и второй 5 транзисторы входного дифференциального каскада 3, статический режим которых устанавливается по токовому входу 6 первым 7 источником опорного тока, связанным с первой 8 шиной источника питания, первый 9 токовый выход входного дифференциального каскада 3, связанный со второй 10 шиной источника питания через второй 11 источник опорного тока и подключенный к истоку первого 12 выходного полевого транзистора, второй 13 токовый выход входного дифференциального каскада 3, соединенный со второй 10 шиной источника питания через третий 14 источник опорного тока и подключенный к истоку второго 15 выходного полевого транзистора, затвор которого связан с затвором первого 12 выходного полевого транзистора, токовое зеркало 16, вход которого соединен со стоком первого 12 выходного полевого транзистора, а выход подключен к стоку второго 15 выходного полевого транзистора, причем неинвертирующий токовый выход 17 токового зеркала 16 согласован с первой 8 шиной источника питания, предусмотрены новые элементы и связи - первый 4 и второй 5 транзисторы входного дифференциального каскада 3 выполнены в виде арсенид-галлиевых p-n-p транзисторов, токовое зеркало 16 реализовано на первом 18 и втором 19 арсенид-галлиевых биполярных транзисторах, эмиттеры которых подключены к неинвертирующему токовому выходу 17 токового зеркала 16, база первого 18 арсенид-галлиевого биполярного транзистора соединена с базой второго 19 арсенид-галлиевого биполярного транзистора и подключена к коллектору первого 18 арсенид-галлиевого биполярного транзистора, который является входом токового зеркала 16, выход токового зеркала 16 соединен с базой первого 20 выходного биполярного транзистора, коллектор которого подключен ко второй 10 шине источника питания, а эмиттер соединен с неинвертирующим токовым выходом 17 токового зеркала 16, подключен к базе второго 21 выходного биполярного транзистора и через токостабилизирующий двухполюсник 22 связан с первой 8 шиной источника питания, коллектор второго 21 выходного биполярного транзистора соединен со второй 10 шиной источника питания, а эмиттер связан с потенциальным выходом устройства 23 и истоком выходного 24 полевого транзистора с управляющим p-n переходом, затвор которого соединен со входом токового зеркала 16, а сток подключен к первой 8 шине источника питания, причем затворы первого 12 и второго 15 выходных полевых транзисторов связаны со второй 10 шиной источника питания.

На чертеже фиг. 1 показана схема ОУ - прототипа.

На чертеже фиг. 2 представлена схема заявляемого ОУ на арсенид-галлиевых p-n-p биполярных и nJFet полевых транзисторах в соответствии с п. 1 формулы изобретения.

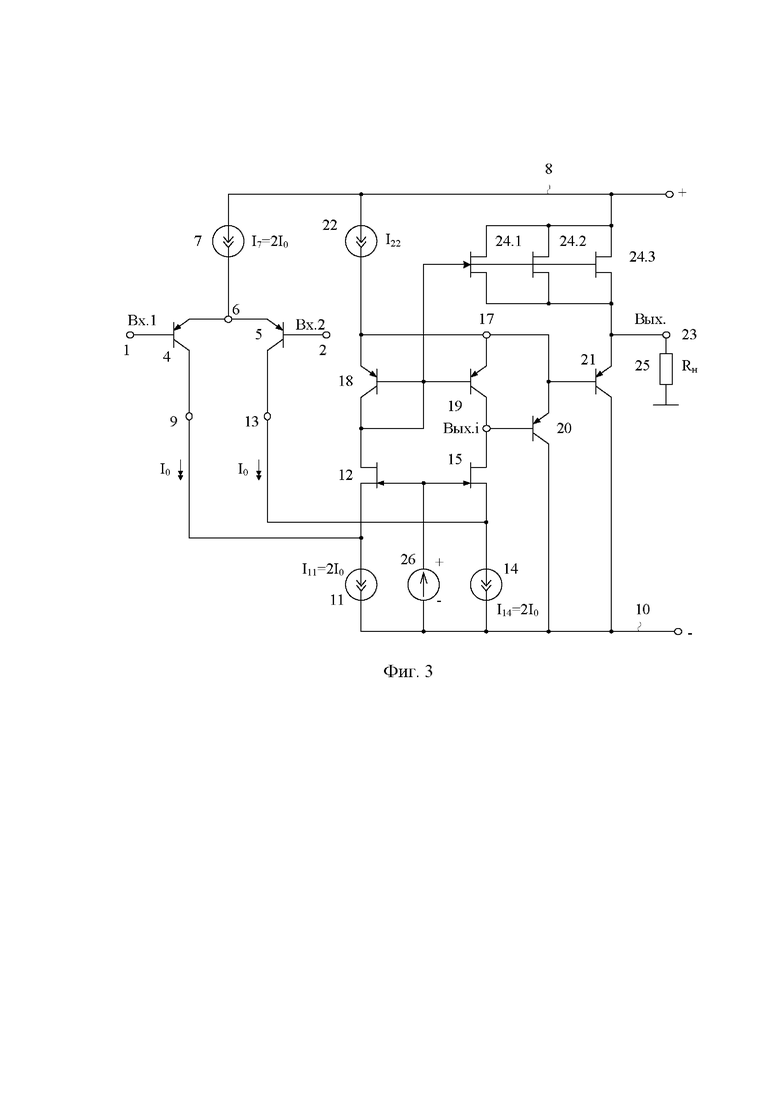

На чертеже фиг. 3 приведена схема заявляемого ОУ в соответствии с п. 2 формулы изобретения.

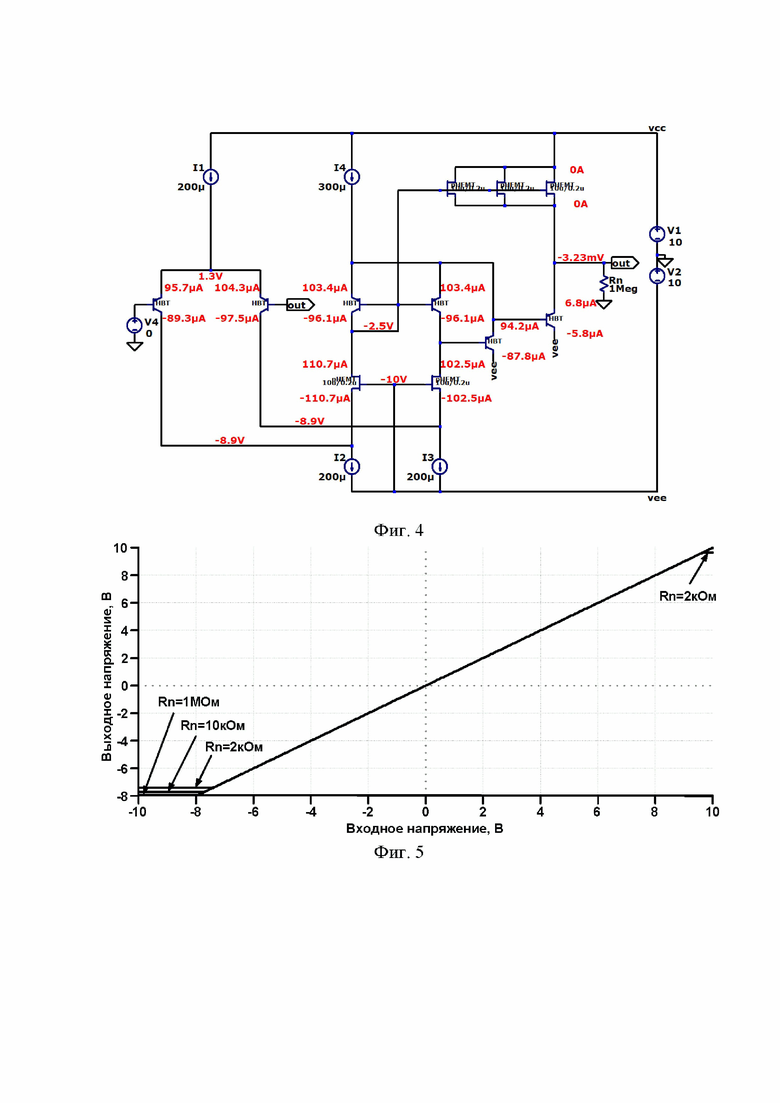

На чертеже фиг. 4 показан статический режим ОУ фиг. 2 в среде LTSpice на GaAs транзисторах при 27°С, источниках опорного тока I1=I2=I3=200мкА, I4=300мкА, Rn=1МОм, напряжениях на шинах питания V1=V2=±10В.

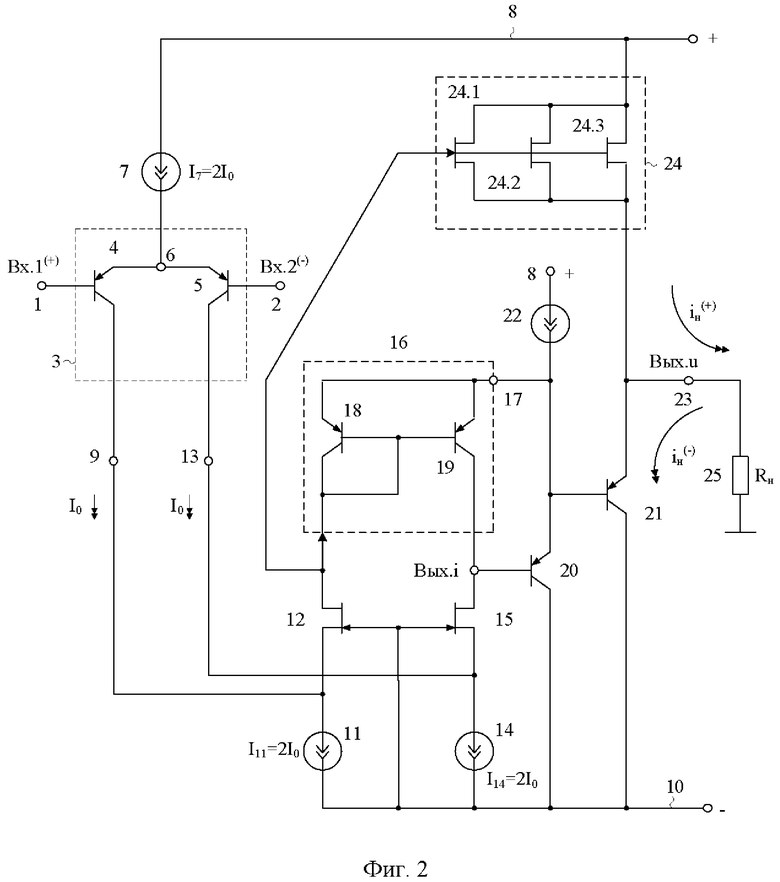

На чертеже фиг. 5 представлена амплитудная характеристика ОУ фиг. 4 при 100% отрицательной обратной связи и разных сопротивлениях нагрузки Rn.

На чертеже фиг. 6 показаны варианты практической реализации первого 7, второго 11, третьего 14 источников опорного тока, а также токостабилизирующего двухполюсника 22, которые могут выполняться на полевых арсенид-галлиевых транзисторах в соответствии с одной из схем включения фиг. 6а, фиг. 6б, фиг. 6в.

Источник опорного тока на чертеже фиг. 6а имеет узлы подключения 27, 28 в схему ОУ и содержит полевой транзистор 29 и резистор 30. Схема на чертеже фиг. 6б имеет узлы подключения 31, 32, а также полевые транзисторы 33, 34. Аналогично, схема на чертеже фиг. 6в может включаться как двухполюсник с узлами 35 и 36 в схему ОУ. Она содержит полевые транзисторы 37 и 38.

На чертеже фиг. 7 приведена логарифмическая амплитудно-частотная характеристика по напряжению ОУ фиг. 4.

Арсенид-галлиевый операционный усилитель фиг. 2 содержит первый 1 и второй 2 входы, входной дифференциальный каскад 3, первый 4 и второй 5 транзисторы входного дифференциального каскада 3, статический режим которых устанавливается по токовому входу 6 первым 7 источником опорного тока, связанным с первой 8 шиной источника питания, первый 9 токовый выход входного дифференциального каскада 3, связанный со второй 10 шиной источника питания через второй 11 источник опорного тока и подключенный к истоку первого 12 выходного полевого транзистора, второй 13 токовый выход входного дифференциального каскада 3, соединенный со второй 10 шиной источника питания через третий 14 источник опорного тока и подключенный к истоку второго 15 выходного полевого транзистора, затвор которого связан с затвором первого 12 выходного полевого транзистора, токовое зеркало 16, вход которого соединен со стоком первого 12 выходного полевого транзистора, а выход подключен к стоку второго 15 выходного полевого транзистора, причем неинвертирующий токовый выход 17 токового зеркала 16 согласован с первой 8 шиной источника питания. Первый 4 и второй 5 транзисторы входного дифференциального каскада 3 выполнены в виде арсенид-галлиевых p-n-p транзисторов, токовое зеркало 16 реализовано на первом 18 и втором 19 арсенид-галлиевых биполярных транзисторах, эмиттеры которых подключены к неинвертирующему токовому выходу 17 токового зеркала 16, база первого 18 арсенид-галлиевого биполярного транзистора соединена с базой второго 19 арсенид-галлиевого биполярного транзистора и подключена к коллектору первого 18 арсенид-галлиевого биполярного транзистора, который является входом токового зеркала 16, выход токового зеркала 16 соединен с базой первого 20 выходного биполярного транзистора, коллектор которого подключен ко второй 10 шине источника питания, а эмиттер соединен с неинвертирующим токовым выходом 17 токового зеркала 16, подключен к базе второго 21 выходного биполярного транзистора и через токостабилизирующий двухполюсник 22 связан с первой 8 шиной источника питания, коллектор второго 21 выходного биполярного транзистора соединен со второй 10 шиной источника питания, а эмиттер связан с потенциальным выходом устройства 23 и истоком выходного 24 полевого транзистора с управляющим p-n переходом, затвор которого соединен со входом токового зеркала 16, а сток подключен к первой 8 шине источника питания, причем затворы первого 12 и второго 15 выходных полевых транзисторов связаны со второй 10 шиной источника питания.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, затворы первого 12 и второго 15 выходных полевых транзисторов связаны со второй 10 шиной источника питания через дополнительную цепь смещения потенциалов 26.

Рассмотрим работу ОУ на чертеже фиг. 2.

Статический режим в ОУ фиг.2 устанавливается первым 7, вторым 11, третьи 14 источниками опорного тока и токостабилизирующим двухполюсником 22, которые реализуются на полевых арсенид-галлиевых транзисторах в соответствии с одной из схем включения, показанной на чертеже фиг. 6.

Двухтактный режим работы заявляемого ОУ обеспечивается для положительного тока в нагрузке 25 параллельно включенными арсенид-галлиевыми полевыми транзисторами 24.1, 24.2 и 24.3. На практике вместо параллельного включения этих активных элементов может применяться существенное увеличение ширины канала выходного 24 полевого транзистора с управляющим p-n переходом. Ток в нагрузке отрицательного направления обеспечивается первым 20 и вторым 21 выходными GaAs биполярными транзисторами. Его максимальные численные значения находятся по формуле:

где I14 - статический ток третьего 14 источника опорного тока, β20β21 - коэффициенты усиления по току базы первого 20 и второго 21 выходных биполярных транзисторов.

Результаты компьютерного моделирования ОУ фиг. 2 (фиг. 4), представленные на чертеже фиг. 5, подтверждают работоспособность предлагаемой схемы с выходным каскадом в режиме класса АВ при сопротивлениях нагрузки 2-10 кОм.

Амплитудно-частотная характеристика схемы ОУ фиг. 4 показана на чертеже фиг. 7.

В некоторых случаях первый 7, второй 11, третий 14 источники опорного тока и токостабилизирующий двухполюсник 22 могут выполняться на арсенид-галлиевых биполярных транзисторах, а в качестве второго 11 и третьего 14 источников опорного тока допускается применение токостабилизирующих резисторов.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом и может использоваться для построения высокотемпературных микросхем на GaAs, а также на других широкозонных полупроводниках (GaN, SiC).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6762646, fig, 3, 2004 г.

2. Патентная заявка US 2004/0090268, fig. 5в, 2004 г.

3. Патент US 5952882, fig. 2, fig. 4, 1999 г.

4. Патент US 6717474, fig. 4, 2004 г.

5. Патентная заявка US 2005/0001682, fig. 3, 2005 г.

6. Патент US 6084475, fig. 2, 2000 г.

7. Патент US 6300831, fig. 1, fig. 2, 2001 г.

8. Патент EP 1227580, fig. 1, fig. 3, 2002 г.

9. Патент US 5580325, fig. 3, fig. 13, 2003 г.

10. Патент US 6714076, fig. 1, 2004 г.

11. Патент US 6218900, fig. 2, fig.3, fig. 4, 2001 г.

12. Патент US 5424681, fig. 1, fig. 4, 1995 г.

13. Патент US 5477190, fig. 4, 1995 г.

14. Патент US 6236270, fig. 2, 2001 г.

15. Унифицированные схемотехнические решения аналоговых арсенид-галлиевых микросхем / Дворников О.В., Павлючик А.А., Прокопенко Н.Н., Чеховский В.А., Кунц А.В., Чумаков В.Е. // Известия вузов. Электроника. 2022. Т. 27. № 4. С. 475-488. DOI: https://doi.org/10.24151/1561-5405-2022-27-4-475-488.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

Изобретение относится к области аналоговой микроэлектроники. Технический результат: создание арсенид-галлиевого операционного усилителя на p-n-p биполярных и nJFet полевых транзисторах, работающего по выходу в режиме класса АВ при сравнительно низкоомных сопротивлениях нагрузки. Для этого предложен арсенид-галлиевый операционный усилитель, в котором первый (4) и второй (5) транзисторы входного дифференциального каскада (3) выполнены в виде арсенид-галлиевых p-n-p транзисторов, токовое зеркало (16) реализовано на первом (18) и втором (19) арсенид-галлиевых биполярных транзисторах, эмиттеры которых подключены к неинвертирующему токовому выходу (17) токового зеркала (16), база первого (18) арсенид-галлиевого биполярного транзистора соединена с базой второго (19) арсенид-галлиевого биполярного транзистора и подключена к коллектору первого (18) арсенид-галлиевого биполярного транзистора, который является входом токового зеркала (16), выход токового зеркала (16) соединен с базой первого (20) выходного биполярного транзистора. 1 з.п. ф-лы, 7 ил.

1. Арсенид-галлиевый операционный усилитель, содержащий первый (1) и второй (2) входы, входной дифференциальный каскад (3), первый (4) и второй (5) транзисторы входного дифференциального каскада (3), статический режим которых устанавливается по токовому входу (6) первым (7) источником опорного тока, связанным с первой (8) шиной источника питания, первый (9) токовый выход входного дифференциального каскада (3), связанный со второй (10) шиной источника питания через второй (11) источник опорного тока и подключенный к истоку первого (12) выходного полевого транзистора, второй (13) токовый выход входного дифференциального каскада (3), соединенный со второй (10) шиной источника питания через третий (14) источник опорного тока и подключенный к истоку второго (15) выходного полевого транзистора, затвор которого связан с затвором первого (12) выходного полевого транзистора, токовое зеркало (16), вход которого соединен со стоком первого (12) выходного полевого транзистора, а выход подключен к стоку второго (15) выходного полевого транзистора, причем неинвертирующий токовый выход (17) токового зеркала (16) согласован с первой (8) шиной источника питания, отличающийся тем, что первый (4) и второй (5) транзисторы входного дифференциального каскада (3) выполнены в виде арсенид-галлиевых p-n-p транзисторов, токовое зеркало (16) реализовано на первом (18) и втором (19) арсенид-галлиевых биполярных транзисторах, эмиттеры которых подключены к неинвертирующему токовому выходу (17) токового зеркала (16), база первого (18) арсенид-галлиевого биполярного транзистора соединена с базой второго (19) арсенид-галлиевого биполярного транзистора и подключена к коллектору первого (18) арсенид-галлиевого биполярного транзистора, который является входом токового зеркала (16), выход токового зеркала (16) соединен с базой первого (20) выходного биполярного транзистора, коллектор которого подключен ко второй (10) шине источника питания, а эмиттер соединен с неинвертирующим токовым выходом (17) токового зеркала (16), подключен к базе второго (21) выходного биполярного транзистора и через токостабилизирующий двухполюсник (22) связан с первой (8) шиной источника питания, коллектор второго (21) выходного биполярного транзистора соединен со второй (10) шиной источника питания, а эмиттер связан с потенциальным выходом устройства (23) и истоком выходного (24) полевого транзистора с управляющим p-n переходом, затвор которого соединен со входом токового зеркала (16), а сток подключен к первой (8) шине источника питания, причем затворы первого (12) и второго (15) выходных полевых транзисторов связаны со второй (10) шиной источника питания.

2. Арсенид-галлиевый операционный усилитель по п.1, отличающийся тем, что затворы первого (12) и второго (15) выходных полевых транзисторов связаны со второй (10) шиной источника питания через дополнительную цепь смещения потенциалов (26).

| US 6762646 B1, 13.07.2004 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2439778C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2411641C1 |

| US 6501333 B1, 31.12.2002. | |||

Авторы

Даты

2024-02-06—Публикация

2023-11-02—Подача