Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известен логический модуль (патент РФ 2542920, кл. G06F 7/57, 2015 г.), который содержит четыре мажоритарных элемента, четыре входа, выход и реализующий простые симметричные булевые функции от трех аргументов при соответствующих настройках.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического модуля, относятся ограниченные функциональные возможности, обусловленные тем, что он не реализует самодвойственные и бесповторные булевые функции, зависящие от трех аргументов.

Известен логический модуль (патент РФ 2398265, кл. G06F 7/57, 2010 г.), который содержит два мажоритарных элемента, элемент И, элемент ИЛИ, пять входов, выход и реализующий простые симметричные булевые функции от трех аргументов при соответствующих настройках.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического модуля, относятся ограниченные функциональные возможности, обусловленные тем, что он не реализует самодвойственные и бесповторные булевые функции, зависящие от трех аргументов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, логический модуль (патент РФ 2303282, кл. G06F 7/00, 2007 г.), предназначенный для реализации простых симметричных булевых функций, зависящих от трех аргументов, содержащий семь входов, выход, двенадцать элементов И, шесть элементов НЕ, шесть элементов ИЛИ.

К причине, препятствующей достижению указанного ниже технического результата при использовании известного логического модуля, относятся ограниченные функциональные возможности, обусловленные тем, что он не реализует самодвойственные и бесповторные булевые функции, зависящие от трех аргументов.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации простых симметричных функций, самодвойственных и бесповторных булевых функций, зависящих от трех аргументов.

Указанный технический результат при осуществлении изобретения достигается тем, что в устройство обработки логической информации, предназначенное для реализации симметричных, самодвойственных и бесповторных булевых функций, зависящих от трех аргументов, содержащее пять входов устройства, выход устройства, два элемента И, элемент ИЛИ, два элемента НЕ, причем первый вход устройства соединен с первым входом первого элемента И и первым входом второго элемента И, второй вход устройства соединен с входом первого элемента НЕ, введены дополнительно мультиплексор с тремя адресными входами и восемью информационными входами, элемент РАВНОЗНАЧНОСТЬ, второй выход устройства, причем первый вход устройства соединен с вторым и пятым информационными входами мультиплексора, первым входом элемента РАВНОЗНАЧНОСТЬ и первым входом элемента ИЛИ, второй вход устройства соединен с четвертым информационным входом мультиплексора, вторым входом второго элемента И, вторым входом элемента РАВНОЗНАЧНОСТЬ и вторым входом элемента ИЛИ, выход элемента НЕ соединен с вторым входом первого элемента И, выход первого элемента И соединен с первым информационным входом мультиплексора и через второй элемент НЕ с седьмым информационным входом мультиплексора, выход второго элемента И соединен с третьим информационным входом мультиплексора, выход элемента РАВНОЗНАЧНОСТЬ соединен с шестым информационным входом мультиплексора, выход элемента ИЛИ соединен с восьмым информационным входом мультиплексора, третий вход устройства соединен с первым адресным входом мультиплексора, четвертый вход устройства соединен с вторым адресным входом мультиплексора, пятый вход устройства соединен с третьим адресным входом мультиплексора, прямой выход мультиплексора соединен с первым выходом устройства, инверсный выход мультиплексора соединен с вторым выходом устройства.

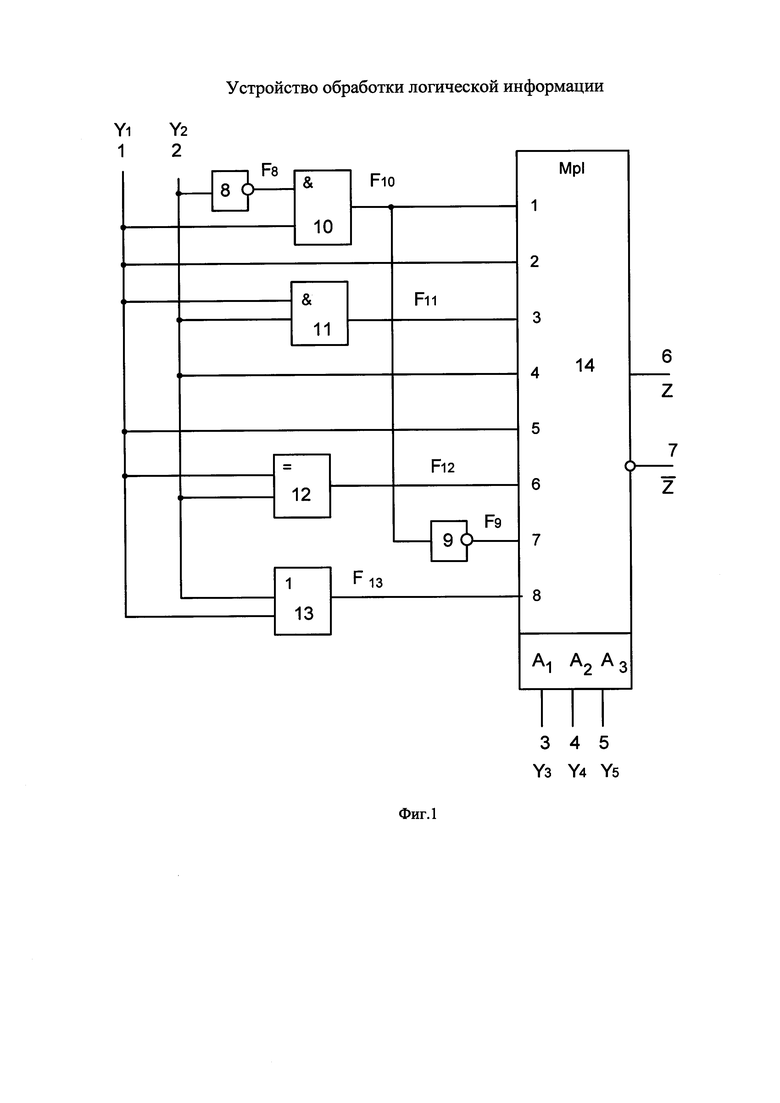

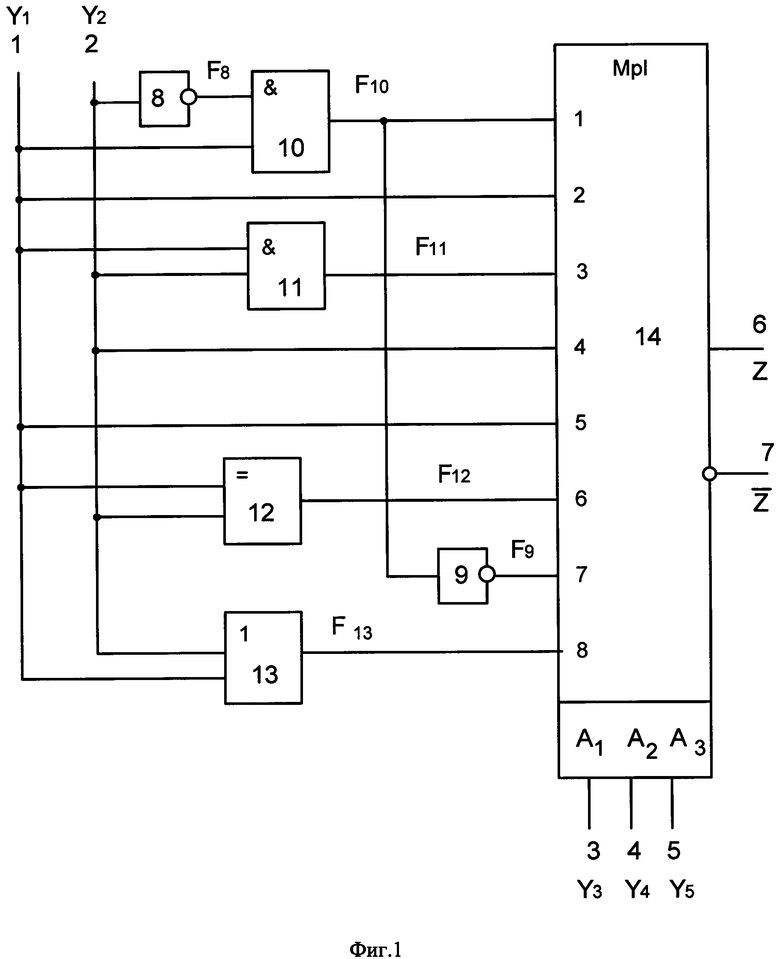

На чертеже представлена схема устройства обработки логической информации, которое содержит пять входов устройства 1,2,3,4,5, выходы устройства 6 и 7, два элемента НЕ 8, 9, два элемента И 10,11, элемент РАВНОЗНАЧНОСТЬ 12, элемент ИЛИ 13, мультиплексор 14, причем первый вход устройства 1 соединен с первым входом первого элемента И 10 и первым входом второго элемента И 11, с вторым и пятым информационными входами мультиплексора 14, первым входом элемента РАВНОЗНАЧНОСТЬ 12 и первым входом элемента ИЛИ 13, второй вход устройства 2 соединен с входом первого элемента НЕ 8, с четвертым информационным входом мультиплексора 14, вторым входом второго элемента И 11, вторым входом элемента РАВНОЗНАЧНОСТЬ 12 и вторым входом элемента ИЛИ 13, выход элемента НЕ 8 соединен с вторым входом первого элемента И 10, выход первого элемента И 10 соединен с первым информационным входом мультиплексора 14 и через второй элемент НЕ 9 с седьмым информационным входом мультиплексора 14, выход второго элемента И 11 соединен с третьим информационным входом мультиплексора 14, выход элемента РАВНОЗНАЧНОСТЬ 12 соединен с шестым информационным входом мультиплексора 14, выход элемента ИЛИ 13 соединен с восьмым информационным входом мультиплексора 14, третий вход устройства 3 соединен с первым адресным входом мультиплексора 14, четвертый вход устройства 4 соединен с вторым адресным входом мультиплексора 14, пятый вход устройства 5 соединен с третьим адресным входом мультиплексора 14, прямой выход мультиплексора 14 соединен с первым выходом 6 устройства, инверсный выход мультиплексора 14 соединен с вторым выходом 7 устройства.

Работа устройства обработки логической информации осуществляется следующим образом.

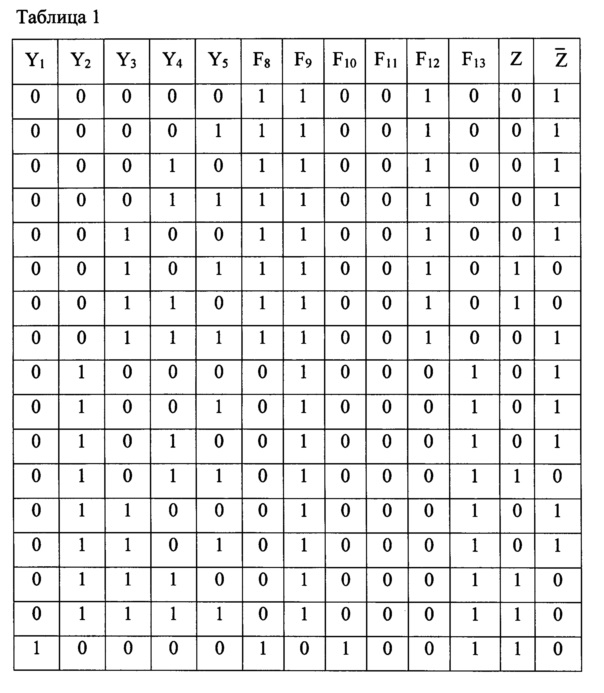

В зависимости от значений входных сигналов Y1, Y2, Y3, Y4, Y5, на входах 1, 2, 3, 4, 5 устройства, на выходах его элементов, на прямом выходе 6 устройства (Z) и на инверсном выходе 7  реализуются булевые функции, приведенные в табл. 1

реализуются булевые функции, приведенные в табл. 1

Устройство реализует следующие булевые функции от трех аргументов (X1, X2, X3):

- симметричные булевые функции (C1, C2, C3);

- самодвойственные булевые функции (S1, S2, S3, S4, S5, S6);

- бесповторные булевые функции (B1, B2, B3, B4).

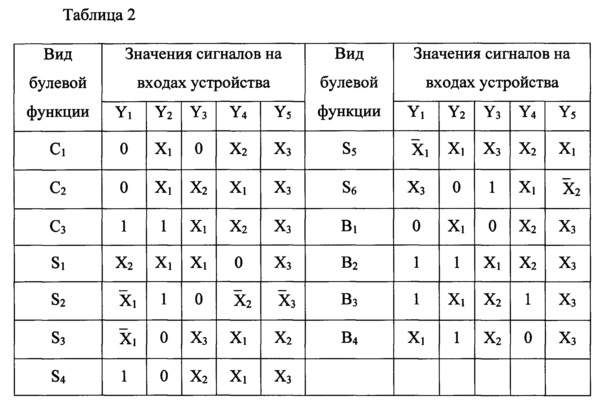

Для реализации заданных булевых функций необходимо на входы 1, 2, 3, 4, 5 устройства подать настроечные сигналы из множества  в соответствии с таблицей настроек и видом реализуемой булевой функцией. Значения настроечных сигналов приведены в табл. 2. На инверсном выходе 7 реализуется обратная булевая функция.

в соответствии с таблицей настроек и видом реализуемой булевой функцией. Значения настроечных сигналов приведены в табл. 2. На инверсном выходе 7 реализуется обратная булевая функция.

Сравнение характеристик прототипа и заявляемого устройства показывает, что заявленное устройство имеет более широкие функциональные возможности, т.к. реализует не только симметричные булевые функции, но и самодвойственные и бесповторные булевые функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 2015 |

|

RU2610678C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2610247C1 |

| НАСТРАИВАЕМЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 2016 |

|

RU2626343C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2015 |

|

RU2609743C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2016 |

|

RU2626345C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2015 |

|

RU2618899C1 |

| ФОРМИРОВАТЕЛЬ СИММЕТРИЧНЫХ БУЛЕВЫХ ФУНКЦИЙ | 2016 |

|

RU2616890C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2015 |

|

RU2609744C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2015 |

|

RU2602331C1 |

| МАЖОРИТАРНЫЙ МОДУЛЬ "ТРИ ИЗ ПЯТИ" | 2016 |

|

RU2628117C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики и функциональных узлов систем управления. Технический результат заключается в расширении функциональных возможностей за счет обеспечения реализации простых симметричных функций, самодвойственных и бесповторных булевых функций, зависящих от трех аргументов. Устройство обработки логической информации содержит пять входов устройства 1,2,3,4,5, выходы устройства 6 и 7, два элемента НЕ 8, 9, два элемента И 10, 11, элемент РАВНОЗНАЧНОСТЬ 12, элемент ИЛИ 13, мультиплексор 14. 1 ил., 2 табл.

Устройство обработки логической информации, предназначенное для реализации симметричных, самодвойственных и бесповторных булевых функций, зависящих от трех аргументов, содержащее пять входов устройства, выход устройства, два элемента И, элемент ИЛИ, два элемента НЕ, причем первый вход устройства соединен с первым входом первого элемента И и первым входом второго элемента И, второй вход устройства соединен с входом первого элемента НЕ, отличающееся тем, что содержит мультиплексор с тремя адресными входами и восемью информационными входами, элемент РАВНОЗНАЧНОСТЬ, второй выход устройства, причем первый вход устройства соединен с вторым и пятым информационными входами мультиплексора, первым входом элемента РАВНОЗНАЧНОСТЬ и первым входом элемента ИЛИ, второй вход устройства соединен с четвертым информационным входом мультиплексора, вторым входом второго элемента И, вторым входом элемента РАВНОЗНАЧНОСТЬ и вторым входом элемента ИЛИ, выход элемента НЕ соединен с вторым входом первого элемента И, выход первого элемента И соединен с первым информационным входом мультиплексора и через второй элемент НЕ с седьмым информационным входом мультиплексора, выход второго элемента И соединен с третьим информационным входом мультиплексора, выход элемента РАВНОЗНАЧНОСТЬ соединен с шестым информационным входом мультиплексора, выход элемента ИЛИ соединен с восьмым информационным входом мультиплексора, третий вход устройства соединен с первым адресным входом мультиплексора, четвертый вход устройства соединен с вторым адресным входом мультиплексора, пятый вход устройства соединен с третьим адресным входом мультиплексора, прямой выход мультиплексора соединен с первым выходом устройства, инверсный выход мультиплексора соединен с вторым выходом устройства.

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2006 |

|

RU2303282C1 |

| Настраиваемое логическое устройство | 1987 |

|

SU1513440A1 |

| Приспособление для суммирования отрезков прямых линий | 1923 |

|

SU2010A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

Авторы

Даты

2017-02-14—Публикация

2015-11-30—Подача