Изобретение относится к радиоэлектронной технике и может быть использовано в системах передачи информации для определения соответствия (идентичности) кода принимаемого от передатчика, сигнала коду, хранящемуся в памяти приемника.

В общем случае (с точки зрения теории), коррелятор это устройство, способное вычислить корреляционную функцию между двумя процессами.

Использование корреляторов в системах цифровой связи, используемой для передачи информации для дискретных состояний лог. "Ноль" или лог. "единица" реализация корреляторов является классической, см. Варакин Л.Е. "Системы связи с шумоподобными сигналами, М, Радио и Связь", 1985, стр. 384.

Проблемой является техническая реализация корреляторов при использовании квазигармонических импульсов.

Известна теоретическая разработка для реализации подобного коррелятора, см. ИССЛЕДОВАНИЕ АКФ ШУМОПОДОБНЫХ СИГНАЛОВ С ИМПУЛЬСАМИ ГАРМОНИЧЕСКОЙ ФОРМЫ ПРИ ОГРАНИЧЕНИИ ШИРИНЫ СПЕКТРА. Малыгин И.В., Комиссарова А.В. В сборнике: СВЧ-техника и телекоммуникационные технологии, 25 Международная Крымская конференция, 2015.

Недостаток этой разработки: это только теория, а до практической реализации еще далеко.

Технической задачей изобретения является построение практической схемы коррелятора для квазигармонических импульсов, как указано на фиг. 1.

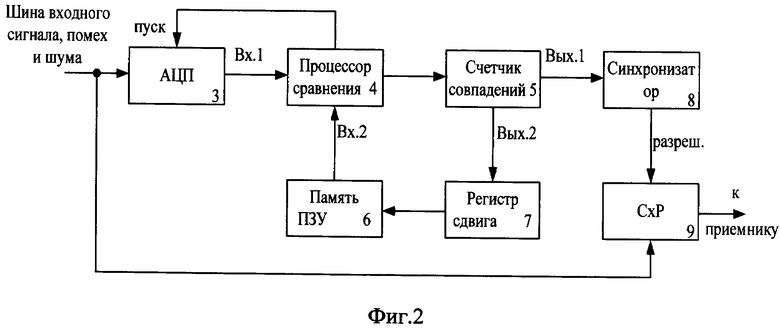

Технический результат достигается за счет построения структурной электрической схемы, показанной на фиг. 2.

Для решения поставленной задачи предлагается коррелятор, содержащий входную информационную шину с квазигармонической формой импульса, отличающийся тем, что содержит АЦП, процессор сравнения, счетчик совпадений, регистр сдвига, ПЗУ и синхронизатор со следующими соединениями.

Шина входного сигнала (смесь полезного сигнала, помех и шума) соединена с сигнальным вход АЦП, выходы которого соединены с первыми входами процессора сравнения, выход которого соединен с счетчиком совпадения, первый выход счетчика соединен с синхронизатором, выход которого соединен с схемой разрешения, а второй выход счетчика совпадений через регистр сдвига и через запоминающее устройство соединен с вторым входом процессора, второй вход которого соединен с входом запуска АЦП.

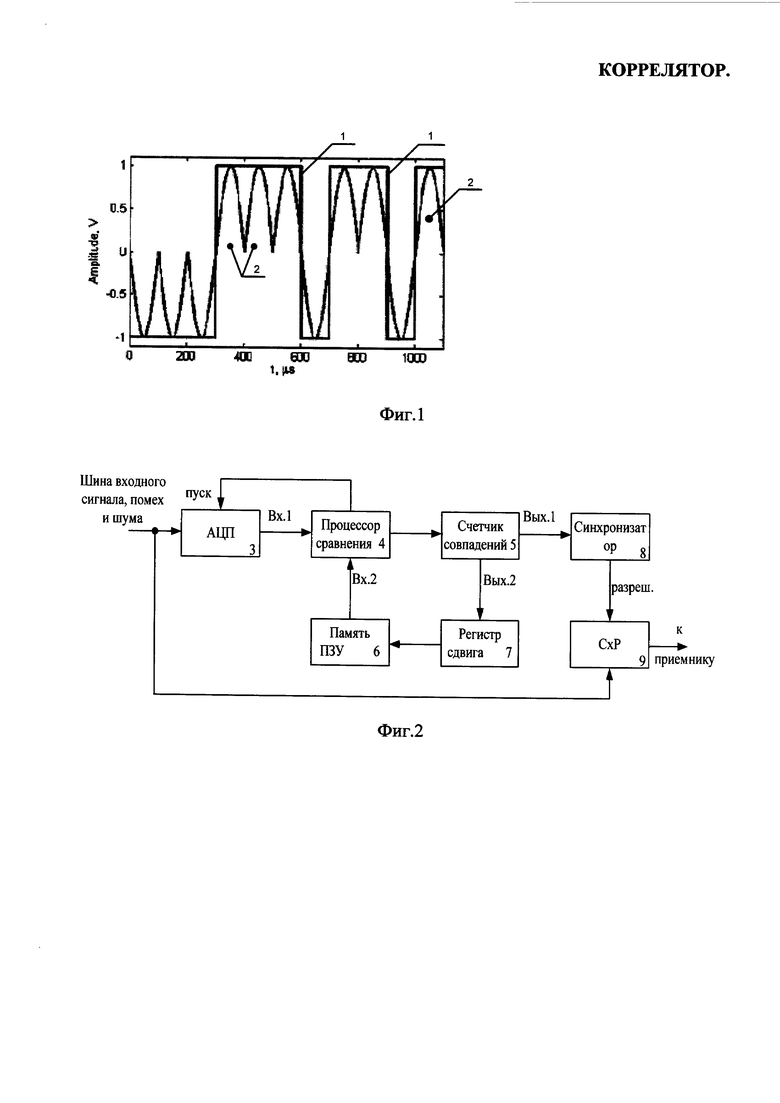

На фиг. 1 показаны диаграммы классических цифровых сигналов прямоугольной формы и квазигармонических (кода Баркера длиной 11 бит).

На фиг. 2 показана структурная электрическая схема предлагаемого коррелятора.

На фиг. 1 линиями 1 показана форма сигнала с прямоугольными импульсами, линиями 2-е квазигармоническими.

На фиг. 2 показано:

3 - АЦП

4 - процессор сравнения

5 - счетчик совпадений

6 - запоминающее устройство (ПЗУ)

7 - регистр сдвига

8 - синхронизатор

9 - схема разрешения прохождения сигналов (СхР)

Схема на фиг. 2 имеет следующие соединения.

Шина входного сигнала (смесь полезного сигнала, помех и шума) соединена с сигнальным вход АЦП 3, выходы которого соединены с первыми входами процессора сравнения 4, выход которого соединен с счетчиком совпадения 5, первый выход счетчика 5 соединен с синхронизатором 8, выход которого соединен с схемой разрешения 9, а второй выход счетчика совпадений 5 через регистр сдвига 7 и через запоминающее устройство 6 соединен с вторым входом процессора 4, второй вход которого соединен с входом запуска АЦП 3.

Коррелятор работает следующим образом.

Смесь полезного сигнала, помех и шума с выхода высокочастотной части приемника поступает на вход АЦП, где преобразуется в цифровую форму. Процессор сравнения, побитно, с необходимой тактовой частотой, проверяет соответствие принятого сигнала с исходным кодом, хранящимся в памяти устройства. При недостаточном числе совпадений, определяемом счетчиком совпадений по выходному сигналу процессора сравнения, регистр сдвига производит сдвиг кода в памяти вправо (или влево) на один такт, после чего процедура сравнения повторяется. Счетчик совпадений и регистр сдвига целесообразно реализовать на одной ПЛИС. Если число совпадений, в идеальном случае равное длине используемой псевдослучайной последовательности, достаточно, синхронизатор вырабатывает импульс синхронизации для начала приема полезной информации приемным устройством. Синхронизатор может быть реализован на основе микрокомпьютера. Отдельной микросхемы памяти не планируется, так как для этой цели может быть задействована и память процессора, и память на ПЛИС, и память микрокомпьютера. В данном случае описывается последовательная схема коррелятора, для ускорения процедуры корреляции также может быть применена параллельная схема, что потребует применения микросхем большей разрядности и вычислительной мощности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор полезного сигнала с обнаружением и классификацией помех | 2019 |

|

RU2716027C1 |

| Устройство для зондирования ионосферы | 1990 |

|

SU1742762A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| АЭРОЛОГИЧЕСКАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА С ЗАЩИЩЁННЫМ КАНАЛОМ СВЯЗИ | 2019 |

|

RU2738438C2 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| Приёмное устройство широкополосных сигналов | 2018 |

|

RU2691731C1 |

| Цифровой коррелятор | 1990 |

|

SU1824642A1 |

| УСТРОЙСТВО ДЛЯ ОДНОВРЕМЕННОГО ПРИЕМА СИГНАЛОВ РАЗЛИЧНЫХ СИСТЕМ СПУТНИКОВОЙ НАВИГАЦИИ | 2015 |

|

RU2611069C1 |

| Устройство для измерения электромагнитных параметров объемных экранов | 1983 |

|

SU1228150A1 |

Изобретение относится к радиоэлектронной технике и может быть использовано в системах передачи информации для определения идентичности кода принимаемого от передатчика сигнала коду, хранящемуся в памяти приемника. Техническим результатом является построение коррелятора для квазигармонических импульсов. Устройство содержит входную информационную шину входного сигнала, содержащего смесь полезного сигнала, помех и шума с квазигармонической формой импульса, АЦП, процессор сравнения, счетчик совпадений, регистр сдвига, ПЗУ, синхронизатор, схему разрешения. 2 ил.

Коррелятор, содержащий входную информационную шину входного сигнала, содержащего смесь полезного сигнала, помех и шума с квазигармонической формой импульса, отличающийся тем, что содержит АЦП, процессор сравнения, счетчик совпадений, регистр сдвига, ПЗУ, синхронизатор и схему разрешения со следующими соединениями: шина входного сигнала - смесь полезного сигнала, помех и шума - соединена с сигнальным входом АЦП и схемой разрешения, выходы АЦП соединены с первыми входами процессора сравнения, выход которого соединен со счетчиком совпадений, первый выход счетчика соединен с синхронизатором, выход которого соединен со схемой разрешения, а второй выход счетчика совпадений через регистр сдвига и через запоминающее устройство соединен со вторым входом процессора, второй вход которого соединен со входом запуска АЦП, выход схемы разрешения является выходом коррелятора.

| КОРРЕЛЯТОР | 1979 |

|

SU1840069A1 |

| КОРРЕЛЯТОР | 1987 |

|

SU1834544A1 |

| US 2003202569 A1, 30.10.2003 | |||

| US 2005135464 A1, 23.06.2005 | |||

| US 2014270017 A1, 18.09.2014. | |||

Авторы

Даты

2017-05-11—Публикация

2015-09-15—Подача