Изобретение относится к области измерительной и вычислительной техники и может быть использовано для измерения функции взаимной корреляции между двумя случайными процессами, задержанными один относительно другого.

Целью изобретения является повышение быстродействия.

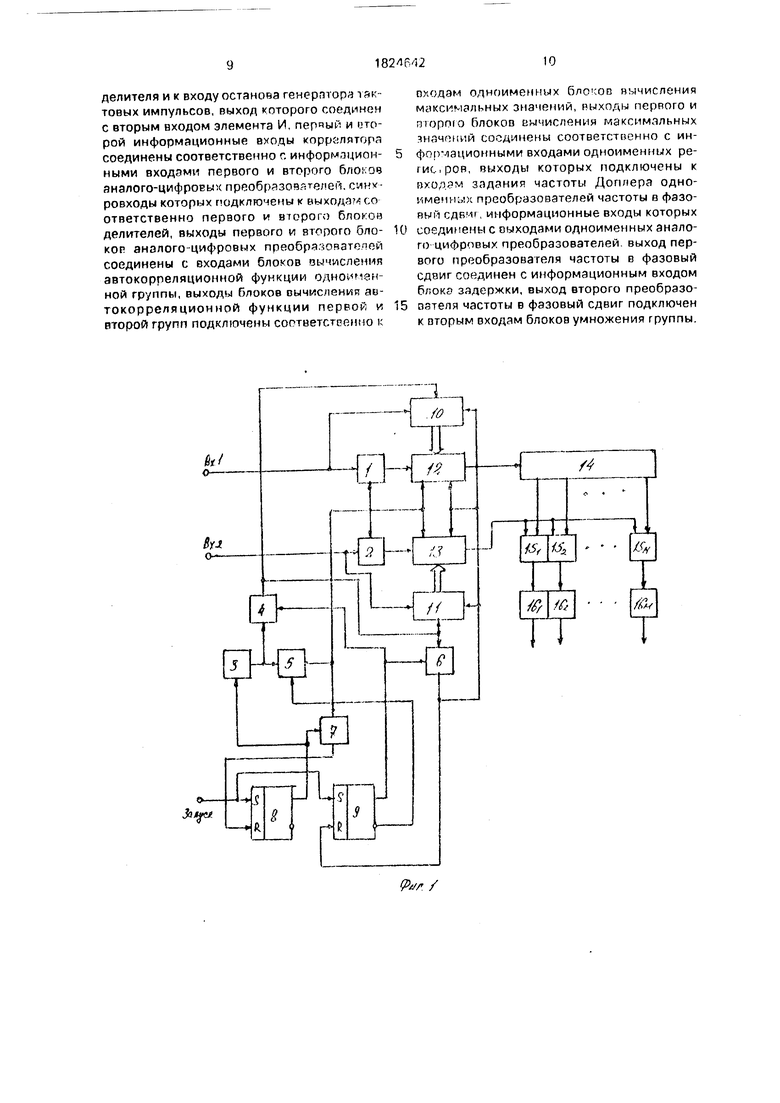

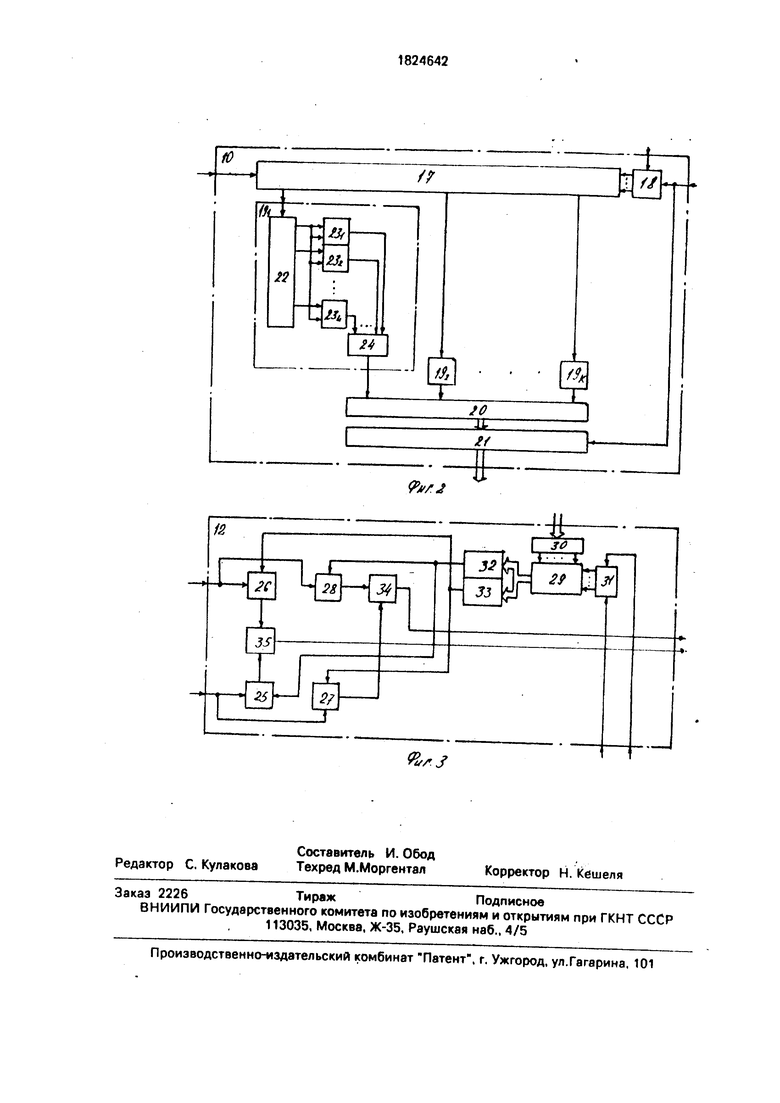

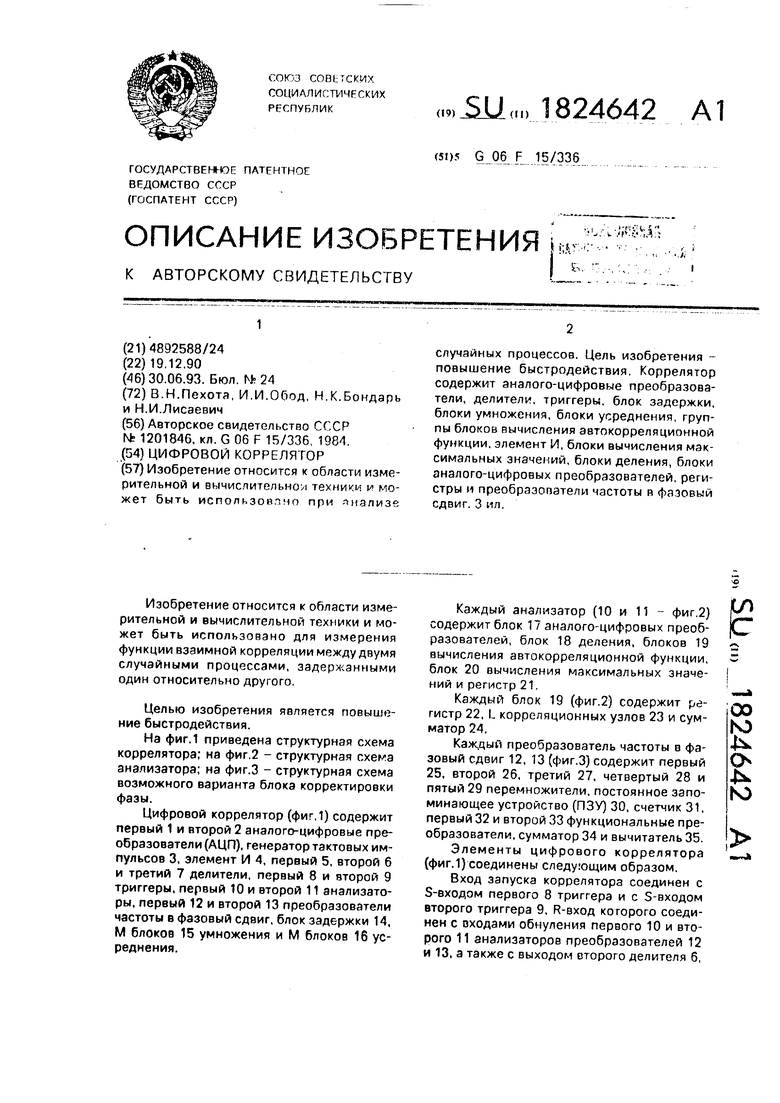

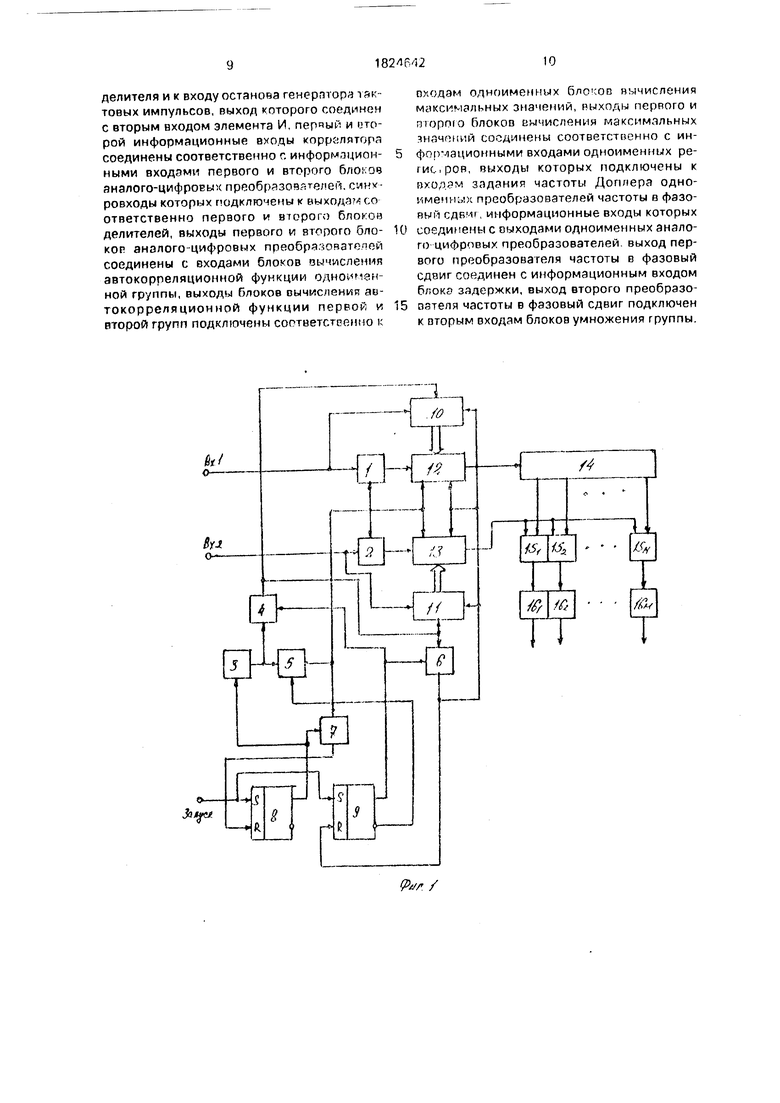

На фиг,1 приведена структурная схема коррелятора; на фиг.2 - структурная схема анализатора; на фиг.З - структурная схема возможного варианта блока корректировки фазы.

Цифровой коррелятор (фиг,1) содержит первый 1 и второй 2 аналого-цифровые преобразователи (АЦП), генератор тактовых импульсов 3, элемент И 4, первый 5, второй 6 и третий 7 делители, первый 8 и второй 9 триггеры, первый 10 и второй 11 анализаторы, первый 12 и второй 13 преобразователи частоты в фазовый сдвиг, блок задержки 14, М блоков 15 умножения и М блоков 16 усреднения.

Каждый анализатор (10 и 11 - фиг.2) содержит блок 17 аналого-цифровых преобразователей, блок 18 деления, блоков 19 вычисления автокорреляционной функции, блок 20 вычисления максимальных значений и регистр 21.

Каждый блок 19 (фиг.2) содержит регистр 22, L корреляционных узлов 23 и сумматор 24.

Каждый преобразователь частоты в фазовый сдвиг 12, 13 (фиг.З) содержит первый 25, второй 26, третий 27, четвертый 28 и пятый 29 перемножители, постоянное запоминающее устройство (ПЗУ) 30, счетчик 31, первый 32 и второй 33 функциональные преобразователи, сумматор 34 и вычитатель 35.

Элементы цифрового коррелятора (фиг.1) соединены следующим образом.

Вход запуска коррелятора соединен с S-входом первого 8 триггера и с S-входом второго триггера 9, R-вход которого соединен с входами обнуления первого 10 и второго 11 анализаторов преобразователей 12 и 13, а также с выходом второго делителя б,

е

оо ю -N о

Јь Ю

вход обнуления которого соединен с прямым выходом второго триггера и с вторым входом элемента И 4, первый вход которого соединен с выходом генератора тактовых импульсов 3 и с счетным входом первого делителя 5, вход обнуления которого соединен с инверсным выходом второго триггера 9, а выход - с тактовыми входами первого 1 и второго 2 АЦП, преобразователей 12 и 13 и с счетным входом третьего делителя 7, выход которого соединен с R-входом первого триггера 8, прямой выход которого соединен с входом обнуления третьего делителя 7 и с входом разрешения работы генератора тактовых импульсов 3, а первый вход корре- пчтсрз соединен с информационным входом первого АЦП 1 и с информационным пходом первого анализатора 10, счетный вход которого соединен с выходом элемента И 4, со счетным входом второго анализатора 11 и с счетным входом второго делителя б, а управляющие выходы - с управляющими входами преобразователя 12, информационный вход которого соединен с выходом АЦП 1, а информационный выход-с входом блока 14 задержки, выходы которого соединены с вторыми входами соответствующего блока 15, первые входы которых соединены с информационным выходом второго преобразователя 13, информационный вход которого соединен с выходом второго АЦП 2, а управляющие входы - с управляющими выходами второго анализатора 11, информационный вход которого соединен с входом второго АЦП 2 и с вторым входом корреля тора, выходы которого соединены с соотсет- ствующими выходами блоков 16 усреднения, выходы которых соединены с выходами соответствующих блоков 15 умно жения.

Цифровой коррелятор (фиг.1) работает следующим образом.

Процесс вычисления взаимной корреляционной функции осуществляется в дна цик- ла. В первом цикле осуществляется вычисление частот Доплера сигналов, поступающих на первый и второй входы, а во втором цикле вычисление взаимной корреляционной функции поступающих сигналов со скомпенсированной частотой Доплера.

При поступлении импульса запуска на вход запуска триггеры 8 и 9 устанавливается в единичное состояние. Установление триггера 8 в единичное состояние разрешает работу делителя 7 и генератора тактовых импульсов 3. Уст -зновление триггера 9 в еди ничное состояние разрешает работу делителя 6 и элемента И 4. Генератор тактовых импульсов 3 формирует на своем выходе

ИМПуЛЬСЫ ВЫСОКОЙ ЧЯ ПОШ Зт Л МПУЛЬСЫ

проходят через элемент И 4 и поступают на счетные входы первого 10 и второго 11 анализаторов и делителя 6. Входные сигналы, поступающие на входы коррелятора, проходятна информационные входы нерпою 10 и второго 11 анализаторов. В анализаторах 10 и 11 происходи вычисление частоты Доплера входных сигна/юь. По окончании первого цикла вычислении, т.е. при появлении импульса на выходе делителя 6,в анализаторах 10 и 11 осуществилось вычисление частоты Доплера поступающих сигналов, и е.е код появляется на управляющих выходах анализаторов.

При появлении импульса на выходе долителн 6 он поступает на входы иСнуленпя анализаторов 10 и 11, где обеспечивает перепись кода частоты Доплера в выходной регистр на входы обнуления преобразовато0 лей 12 и 13 и переключает триггер 9 в нулевое состояние.

Переключение триггера 9 в нулевое состояние запрещает работу делителя 6 и ЭЛР- меита И 4 и разрешает работу делителя 5.

5HP пыходе делителя 5 образуются импульсы тактовой чаи оты с частотой, определяемой частотой Котельникова. Импульсы с выхода делителя 5 послупзк-i на счетный вход делителя 7 и на тякюгие входы АЦП 1

0 и 2 и пргобразовэюлой 12 и ГЗ В АЦП по импульсам т-э - та осуществ/и ен .я преобразование входных янало ог.-4х емшанов гз цифровой код. Цифровые коды с пиходов АЦП 1 , 2 поступаю, на входы прообразов

5 телей 12 и 13, в которых по кодам управления с выходов анализа юров осуществляется коррекция фазы цифросых отсчетов так, что осуществляется коррекция фазы - компенсация частоты Доплера вход0 цых сигналов.

Таким образом, на выходе пр пбразооз- телей выходные сигналы не содержат частоты Доплера. Выходные сигналы преобразователя 12 поступают на входы

5 блока 14 задержки, имрющего М отводоз, где М - число вычисляемых ординат взаимной корреляционной функции. Цифровые отсчеты с выходом блока 14 задержки и с выходов преобразователя 13 перемножаютО ся в блоках 15. Выходные результаты перс множсния поступают на входы блоков усреднения 16, в которых и осуществляется накопление результатов перемножения. По окончании накопления, т.е. при появлении

5 импульса на выходе делителя 7 три герч8 устанавливается в нулевое состояние чем и заканчивается процесс работы коррелятора. Результаты вычисления взаимной корреляционной функции роботы прг этом хранятся о блокгтг О и not. tyna m на выход

коррелятора. Если необходима оценка раз ности доплеровских частот поступающих сигналов, то управляющие выходы анализаторов 10 и 11 подводятся до вычитателя (на фиг.1 не показан) и с его выходов и снима- ется разность доплеровских частот.

В дальнейшем работа цифрового коррелятора аналогична.

Рассмотрим работу отдельных элементов цифрового коррелятора. Анализатор 11 (фиг.2) работает следующим образом.

Математический алгоритм работы анализатора основан на следующем. Предположим, что сигнал, принимаемый приемником, можно записать в следующем виде

S(r) Soexp{l(ft t) + tp} + n(t).(1)

где (О (1 - )uJb - угловая частота, смеС

щенная за счет эффекта Доплера; v0 - ско- рость движения постановщика помех. So скорость распределения радиоволн, р - фаза, n(t)-аддитивная помеха в полосе пропускания приемника.

В случае монохроматического сигнала радиопомех уравнение (1) без n(t) дает следующую автокорреляционную функцию

R0(r)2T S(t)-S(t+r)dt

(l()}(2)

где 2Т - интервал интегрирования, г- время задержки, (х ) - комплексное сопряжение.

Для получения точного результата опре- делим фазовращательную автокорреляционную функцию R(r) следующим образом

R(r )- S S(t)ST(t+r)dr; (3)

5i(t+ г) S(M- г )ехр(- г да);(4) . (5)

где прогнозируемое вращение фазы при (t+r ).

6- прогнозируемая угловая частота в данный период.

Подставляя уравнения (1), (4) и (5) в (3). получаем:

R( г) - So2exp{l( о - о) г} «- N(r }, (6) где N( r) означает вклад шума n(t) в уравнение (2).

Как следует из (б).когда прогнозируемая угловая частота (ш ) не совпадает с действительными значениями, реальная часть изменяется со временем задержки г . Исследуя (о , мы можем найти истинную ft), когда реальная часть автокорреляционной функции остается константой So1 при любом времени задержки. Поскольку в реальных условиях существует шумовой эффект

5

10

15

20

25

0

с

0

5

0

5

N( г). то мы можем получить опшмотм ую оценку о) , максимизируя ср°дмо л nnrofop реляционную мощность RP ппр д -пенную для периода временигр п СЛРДУКЧЦ М виде

//Real R (r)|cl т tK -TR

«wax ft - at.(7)

Таким образом, в основе алгоритма функционирования заявленного устройства, т.е. анализатора, лежит выражение (7).

При поступлении импульсов на счетный вход анализатора они проходят на счетный вход блока 18 деления. На выходе каждого из делителей блока 18, за счет различного коэффициента деления, образуются чистоты квантования с различным периодом квантования.

Импульсы квантования с выходом делителей 18 поступают на свой канал обработки, который состоит из аналого-цифрового преобразователя блока 17 и блока 19. В каждом блоке 19 осуществляется вычисление автокорреляционной функции при различных дискретах дискретизации. В регистре

22осуществляется задержка цифровых отсчетов, а в корреляционных узлах 23 осуществляется перемножение поступающих отсчетов и накопление результатов пере- мнохсения. Выходные значения с выходов корреляционных узлов 23 поступают на сумматор 24, в котором и происходит вычисление, т.е. выделяется результат по выражению (7). L выбирается в соответствии с требуемым значением TR . Выходные коды с блоков 19 поступают на входы блока 20 определения максимума, который определяет код канала с максимальным значением кода. т.е. на выходе блока 20 вырабатывается код ординаты с максимальным выходным кодом, а я соответствии с выражением (7) этим определяется тот канал, в котором частота дискретизации наиболее точно совпала с (о . Этот канал, т.е. его код с выхода блока 20, по импульсу, поступающему на вход обнуления анализатора, переписывается в выходной регистр 21 и выдается на выход анализатора. Корреляционный узел

23реализуется на перемножителе и накопительном сумматоре. Устройство определения максимума может быть реализовано на устройствах сравнения, элементах И и ИЛИ.

Преобразователь 12 (13) (фиг.З) работает следующим образом.

Он может быть реализован по различным схемам. Одна из них и приведена на фиг.З. Она показана для того случая, когда имеется два квадратурных канала обработки. Если их нет (т.е. имеется только один

вход), то они могут быть реализовлны по схеме, приведенной в (4),

Таким образом, расквэдратурить каналы можно и после АЦП.

Работу преобразователя рассмотрим, когда имеются два квадратурных канала (фиг.5).

На управляющие входы преобразователя поступает код канала с максимальной подобранной частотой. Этот код поступает на адресные входы ПЗУ 30, в котором осуществляется преобразование входного кода частоты значение фазового сдвига. Для этого преобразования осуществлен табличный принцип преобразования, нашедший в настоящее время широкое применение. Код фазового сдвига с выхода ПЗУ 30 поступает на перемножитель 29, в котором происходит перемножение этого кода с постоянно возрастающим кодом счетчика 31.

Таким образом, на выходе перемножи теля 29 происходит вычисление фазового сдвига с постоянно возрастающим знамени ом по времени от начала преобразования. Этим и происходит устранение постоянно возрастающего сдвига фазы под действием частоты Доплера.

Известно (4), что это изменение фазы комплексного сигнала с цифровой форме можно осуществить путем умножения каждого выборочного значения А Aexp{J fk } АС ь JAS второго сигнала на комплексное число В -- Bexp{j Ар } Вс + JBS, определяющее величину изменения (поворота) фазы .

Поэтому эти операции выполняются одним и тем же комплексным умножителем, формирующим произведение

А6 + ABexp{j( Фь + Ар)} - (АсВс - ASBS) +J(ACB, + AsBc).

В соответствие с этим выражением а первом функциональном преобразователе 32 осуществляется вычисление cos Ay) , a в функциональном преобразователе СЗ осуществляется вычисление sin Ay . На выходах блока получаются результаты вычислений по указанному выражению. В дальнейшем работе блока аналогична.

Остальные элементы цифрового коррелятора по техническому построению не сложны и они описаны в существующей технической литературе. Синхронизация работы отдельных элементов коррелятора может быть осуществлена импульсами, имеющимися в корреляторе (при необходимости они могут быть задержаны элементами задержки).

Предлагаемое техническое решение направлено на улучшение конкретных технических характеристик цифровых корреляте ров.

В прототипе для вычисления взаимной корреляционной функции требуется провести К циклов. В заявленном же устройстве при полностью одинаковых функциях, как и в прототипе, необходимо провести всего два цикла.

Таким образом, быстродействие заявленного устройства по срэрнению с базовым объектом повышается R К/2 раз. Формула изобретения Цифровой коррелятор, содержащий генератор тактовых иммули.оя дна анэлого5 цифровых преобразователя, три делителя, первый триггер, блок задержки, блоки умножения и блоки усреднения, причем информационные входы первого и OTOpoio аналого-цифровых преобразователей япля0 ются одноименными информационными входами корреллтора, выходы блока задержки соединены с первыми входами блоков умножения, выходы которых подключены к входам блоков усреднения, выходы коюрых

5 являются выходами коррелятора, входом запуска которого является S-вход первого триггера, выход генератора тактовых импульсов подключен к первому входу первого делителя, выход которого соединен с тактоO вым входом первого аналого-цифрового преобразоватгля, о т л и ч а ю щ и и с я тем, что, с целью повышения быстродействия, в него введены две группы блоков вычисли ния автокорреляционной функции, элемент

5 И, два блока вычисления максимальных значений, два блока деления, два блока аналого-цифровых преобразователей, два регистра, два преобразователя частоты в фазовый сдвиг и второй триггер, S-вход ко0 торого соединен с входом запуска коррелятора, а прямой выход - с первым входом второго депителя и первым входом элемента И, второй вход которого подключен к вы- ходу генератора тактовых импульсов, а

5 выход соединен с первыми входами первого и второго блоков делителя и с вторым входом второго делителя, выход которого подключен к обнуляющим входам преобразователей частоты в фазовый сдви

0 и синхровходам регистров, к вторым входам блоков делителей и к R-входу второго триггера, инверсный выход которою соединен с вторым входом первого делителя, выход которого подключен к тактовым

5 входам второго аналого-цифрового преобразователя, преобразователей частоты в фазовый сдвиг и к первому входу третье о делителя, выход которого соединен с R вхо дом первого триггера, прямой выход кото рого подключен к второму входу третю;

делителя и к входу останова генератора тактовых импульсов, выход которого соединен с вторым входом элемента И, первый и «торой информационные входы коррелятора соединены соответственно г. информационными входами первого и второго блоков аналого-цифровых преобразователей. CMHV- ровходы которых подключены к выходам со ответственно первого и второго блоков делителей, выходы первого и второго блоков аналого-цифровых преобря оватолей соединены с входами блоков вычисления автокорреляционной функции одноиман- ной группы, выходы блоков вычислений автокорреляционной функции первой и второй групп подключены согтветстеежю к

0

5

входам одноименных блоков вычисления мг1ксимальных значений, выходы первого и пюрпго блоков вычисления максимальных значений соединены соответственно с информационными входами одноименных ре- гио.ров, выходы которых подключены к входам задания частоты Доплера одноименных преобразователей частоты в фазовый сдвиг, информационные входы которых соединены с выходами одноименных аналоге цифровых преобразователей, выход первого преобразователя частоты в фазовый сдвиг соединен с информационным входом блока задержки, выход второго преобразователя частоты в фазовый сдвиг подключен к вторым входам блоков умножения группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой автокоррелятор | 1990 |

|

SU1829042A1 |

| Цифровой коррелятор | 1990 |

|

SU1727132A1 |

| Цифровой коррелятор | 1990 |

|

SU1727133A1 |

| Цифровой коррелятор сигналов различной доплеровской частоты | 1988 |

|

SU1571612A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| Устройство для определения взаимной корреляционной функции | 1987 |

|

SU1444812A1 |

| Устройство для определения взаимной корреляционной функции | 1987 |

|

SU1427383A1 |

| Устройство для измерения динамических характеристик | 1983 |

|

SU1168902A1 |

| Устройство для определения взаимной корреляционной функции | 1986 |

|

SU1406602A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

Изобретение относится к области измерительной и вычислительно/t техники v может быть использовлчо при анализе случайных процессов. Цель изобретения - повышение быстродействия. Коррелятор содержит аналого-цифровые преобразователи, делители, триггеры, блок задержки, блоки умножения, блоки усреднения, группы блоков вычисления автокорреляционной функции, элемент И, блоки вычисления максимальных значений, блоки деления, блоки аналого-цифровых преобразователей, регистры и преобразователи частоты в фазовый сдвиг. 3 ил.

Аг/

„-,- .Я.i1э1

| Взаимокоррелятор | 1984 |

|

SU1201846A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1993-06-30—Публикация

1990-12-19—Подача