2420-153840RU/018

СКООРДИНИРОВАННЫЕ ОПЕРАЦИИ ЗАПИСИ ПО АДРЕСНОМУ КАНАЛУ ШИНЫ

РОДСТВЕННЫЕ ЗАЯВКИ

Настоящая заявка на патент испрашивает приоритет предварительной заявки № 60/776529, озаглавленной "Cooperative Writes Over Address Channel", поданной 24 февраля 2006, переданной правопреемнику и полностью включенной в настоящую заявку посредством ссылки.

Настоящая заявка на патент родственна следующим поданным одновременно с данной заявкам на патент США: "Auxiliary Writes Over Address Channel", которая имеет номер 060485 в реестре поверенного, передана правопреемнику, и полностью включена в настоящую заявку посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение в основном относится к системам обработки данных, и более конкретно, к системам и способам для выполнения скоординированных записей по адресному каналу шины.

УРОВЕНЬ ТЕХНИКИ

В сердце наиболее современных систем обработки данных находится межкомпонентное соединение, называемое шиной. Шина пересылает информацию между различными объектами обработки в системе. На сегодняшний день, большинство шинных архитектур является четко стандартизированным. Упомянутые стандартизированные шинные архитектуры обычно имеют независимые и раздельные каналы считывания, записи и адресные каналы.

Указанный тип шинной архитектуры часто находится в системах обработки данных с одним или несколькими универсальными процессорами, имеющими доступ к памяти. В таких системах память обеспечивает носитель данных, который хранит программы и данные, которые нужны процессорам для выполнения их функций. Процессор может производить считывание или запись в память посредством помещения адреса в адресном канале и посредством передачи соответствующего сигнала управления считыванием/записью. В зависимости от состояния управления считыванием/записью, процессор либо производит запись в память по каналу записи, либо производит считывание из памяти по каналу считывания. В упомянутых типах систем обработки данных, а также во многих других, желательно уменьшать время ожидания записи и увеличивать ширину полосы пропускания.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Раскрывается особенность системы обработки данных. Система обработки данных включает в себя приемное устройство, шину, имеющую первый, второй и третий каналы, и передающее устройство, конфигурированное, чтобы адресовать приемное устройство на первом канале и считывать полезную нагрузку из приемного устройства на втором канале, причем передающее устройство дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки в приемное устройство на первом канале и вторую часть полезной нагрузки в приемное устройство на третьем канале.

Раскрывается другая особенность системы обработки данных. Система обработки данных включает в себя приемное устройство, шину, имеющую первый, второй и третий каналы, средство для адресации приемного устройства на первом канале, средство для считывания полезной нагрузки из приемного устройства на втором канале и средство для записи первой части полезной нагрузки в приемное устройство на первом канале и второй части полезной нагрузки в приемное устройство на третьем канале.

Раскрывается способ передачи информации по шине между передающим устройством и приемным устройством. Шина включает в себя первый, второй и третий каналы. Способ включает в себя адресацию приемного устройства на первом канале, считывание полезной нагрузки из приемного устройства на втором канале и запись первой части полезной нагрузки в приемное устройство на первом канале и второй части полезной нагрузки в приемное устройство на третьем канале.

Раскрывается особенность устройства управления шиной. Устройство управления шиной включает в себя процессор и интерфейс шины, сконфигурированный, чтобы сопрягать процессор с шиной, имеющей первый, второй и третий каналы, причем интерфейс шины дополнительно конфигурируется, чтобы адресовать подчиненное устройство на первом канале, принимать полезную нагрузку из подчиненного устройства на втором канале, и записывать первую часть полезной нагрузки в подчиненное устройство на первом канале и вторую часть полезной нагрузки в подчиненное устройство на третьем канале.

Раскрывается другая особенность устройства управления шины. Устройство управления шины включает в себя процессор и средство для сопряжения процессора с шиной, имеющей первый, второй и третий каналы, причем средство для сопряжения процессора с шиной содержит средство для адресации подчиненного устройства на первом канале, средство для приема полезной нагрузки из подчиненного устройства на втором канале, и средство для записи первой части полезной нагрузки в подчиненное устройство на первом канале и второй части полезной нагрузки в подчиненное устройство на третьем канале.

Раскрывается особенность подчиненного устройства. Подчиненное устройство включает в себя память и интерфейс шины, конфигурированный, чтобы сопрягать память с шиной, имеющей первый, второй и третий каналы, причем интерфейс шины конфигурируется, чтобы принимать адрес и первую часть полезной нагрузки из устройства управления шины на первом канале, посылать полезную нагрузку в устройство управления шины на втором канале, и принимать вторую часть полезной нагрузки из устройства управления шины на третьем канале.

Раскрывается другая особенность подчиненного устройства. Подчиненное устройство включает в себя память и средство для сопряжения памяти с шиной, имеющей первый, второй и третий каналы, причем средство для сопряжения памяти с шиной содержит средство для приема адреса и первой части полезной нагрузки из устройства управления шиной на первом канале, средство для передачи полезной нагрузки в устройство управления шиной на втором канале, и средство для приема второй части полезной нагрузки из устройства управления шиной на третьем канале.

Понятно, что другие варианты осуществления настоящего изобретения станут очевидными для специалистов из следующего подробного описания, в котором различные варианты осуществления настоящего изобретения показаны и описаны путем иллюстрации. Как будет понятно, возможны другие различные варианты осуществления, и некоторые их детали могут иметь модификации в различных других отношениях, не отклоняясь от настоящего изобретения. Соответственно, чертежи и подробное описание должны рассматриваться как иллюстративные по характеру, а не как ограничивающие.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

В дальнейшем изобретение поясняется описанием конкретных вариантов его осуществления со ссылками на сопровождающие чертежи, на которых:

фиг.1 - упрощенная блок-схема, иллюстрирующая пример двух устройств в системе обработки данных, сообщающихся по шине;

фиг.2 - иллюстрация, показывающая информацию, передаваемую на адресном канале и канале записи шины в системе обработки данных фиг.1 с адресным каналом, обеспечивающим общий носитель для адресов и данных;

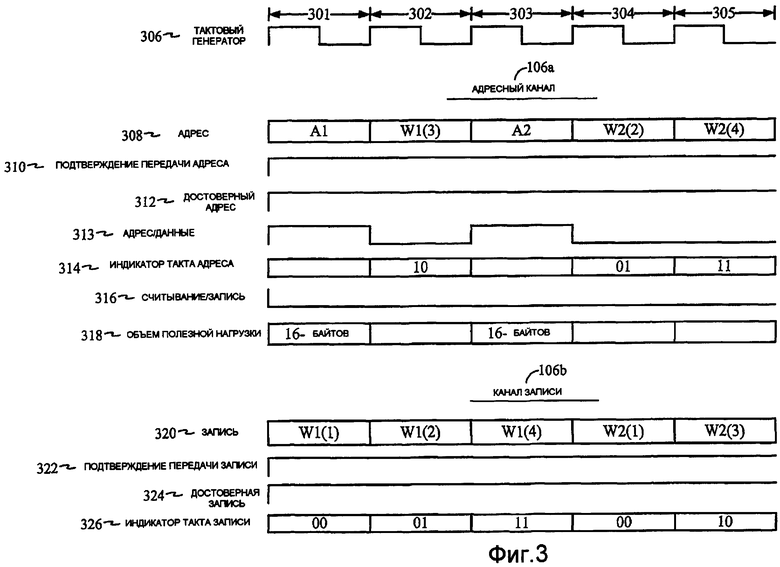

фиг.3 - диаграмма синхронизации, показывающая две операции записи по шине в системе обработки данных фиг.1;

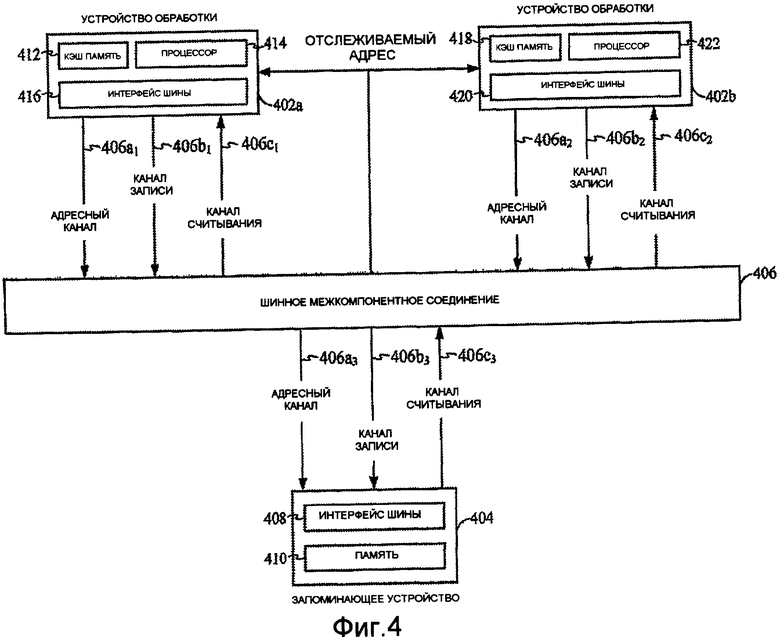

фиг.4 - упрощенная блок-схема, иллюстрирующая систему обработки данных с взаимным соответствием содержимого различных кэшей с двумя устройствами обработки в сообщении с совместно используемым ресурсом через шинное межкомпонентное соединение;

фиг.5 - иллюстрация, показывающая информацию, передаваемую на адресном канале и канале записи между одним устройством обработки и шинным межкомпонентным соединением в системе обработки данных с взаимным соответствием содержимого различных кэшей фиг.4;

фиг.6 - упрощенная блок-схема, иллюстрирующая пример двух устройств в системе обработки данных, сообщающихся по четырехканальной шине; и

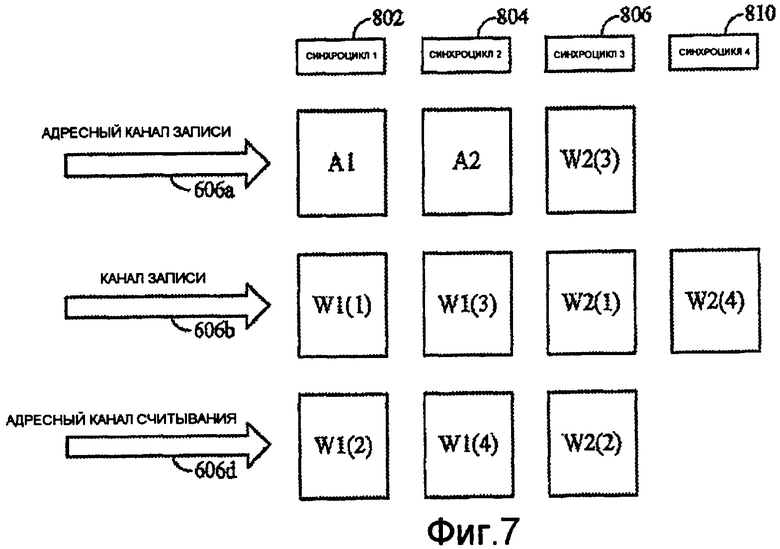

фиг.7 - иллюстрация, показывающая информацию, передаваемую на адресном канале и канале записи четырехканальной шины в системе обработки данных фиг.6 с адресными каналами считывания и записи, обеспечивающими общий носитель для адресов и данных.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Подробное описание, приведенное ниже с сопровождающими чертежами, дается как описание различных вариантов осуществления настоящего изобретения и не рассчитано представлять только варианты осуществления, в которых настоящее изобретение может осуществляться на практике. Подробное описание включает в себя специфические детали для цели обеспечения исчерпывающего понимания настоящего изобретения. Однако специалистам будет очевидно, что настоящее изобретение может осуществляться на практике без указанных специфических деталей. В некоторых примерах хорошо известные структуры и компоненты показаны в форме блок-схемы, чтобы избежать затуманивания концепций настоящего изобретения.

Фиг.1 - упрощенная блок-схема, иллюстрирующая пример двух устройств в системе обработки данных, сообщающихся по шине. Система 100 обработки данных может представлять собой совокупность устройств аппаратных средств, которые объединяются для выполнения одной или нескольких функций обработки. Обычные применения системы 100 обработки данных включают в себя: настольные компьютеры, портативные компьютеры, серверы, сотовые телефоны, карманные компьютеры (PDA), игровые приставки, пейджеры, модемы, аудиооборудование, медицинские устройства, автомобильные, видеооборудование, промышленное оборудование или любую другую машину или устройство, способное обрабатывать, искать и хранить информацию, но, не ограничиваясь ими.

Система 100 обработки данных показана с передающим устройством 102 в сообщении с приемным устройством 104 по шине 106. Шина 106 включает в себя три канала: адресный канал 106a, канал 106b записи и канал 106c считывания. «Канал» определяется как набор электрических проводников, используемых для переноса информации между двумя устройствами, и который имеет набор общих управляющих сигналов. В данном примере каждый канал имеет разрядность 32 бита. Обычно, шинное межкомпонентное соединение (не показано) используется, чтобы устанавливать тракт прямой связи между передающим устройством 102 и приемным устройством 104 по шине 106. Альтернативно, шина 106 может быть шиной специального назначения или любого другого типа подходящей шинной архитектуры.

Передающим устройством 102 может быть устройство управления шиной любого типа. В данном примере передающее устройство 102 включает в себя процессор 108 и интерфейс 110 шины. Процессор может быть процессором общего назначения, таким как микропроцессор, процессором специального назначения, таким как процессор цифровой обработки сигналов (DSP), специализированная интегральная схема (ASIC), контроллер прямого доступа к памяти (DMA), мостом, программируемым логическим устройством или любым другим объектом, который требует доступа к шине 106. Интерфейс 110 шины используется для запуска адресного канала и канала записи 106a, 106b, а также для обеспечения соответствующих управляющих сигналов. Интерфейс 110 шины также служит в качестве приемника для канала 106c считывания.

Приемным устройством 104 может быть подчиненное устройство любого типа. Приемным устройством 104 может быть оперативное запоминающее устройство, такое как SDRAM (синхронное динамическое ЗУПВ), DRAM (динамическое ЗУПВ) или RAM (запоминающее устройство с произвольной выборкой, ЗУПВ), или устройство длительного хранения данных такое как кэш-память, ROM (постоянное запоминающее устройство, ПЗУ), EPROM (стираемое программируемое постоянное запоминающее устройство), EEPROM (электрически стираемое программируемое постоянное запоминающее устройство), CD-ROM (постоянное запоминающее устройство на компакт-диске), DVD (цифровой многофункциональный диск), магнитный диск, регистры, жесткий диск, сменный диск, или любая другая форма носителя данных, известная в уровне техники, флэш-память, оптический компакт-диск многократной перезаписи и т.д. Альтернативно, приемное устройство 104 может быть мостом или любым другим устройством, способным отыскивать и хранить информацию. В указанном примере приемное устройство 104 включает в себя интерфейс 112 шины и память 114. Интерфейс 112 шины используется для запуска канала 106c считывания и соответствующих управляющих сигналов. Интерфейс 110 шины также служит в качестве приемника для адресного канала и канала записи 106a, 106b. Память 114 также может быть любым устройством, к содержанию которого можно получать произвольный доступ (то есть считывать и записывать).

В упомянутой шинной архитектуре передающее устройство 102 может производить считывание с приемного устройства 104 или запись на него. Когда передающее устройство 102 выполняет операцию записи, оно посылает адрес в приемное устройство 104 на адресном канале 106a с соответствующими управляющими сигналами. Полезная нагрузка может посылаться либо на адресном канале 106a, либо на канале 106b записи, либо на обоих. Под термином «полезная нагрузка» подразумеваются данные, ассоциированные с конкретной операцией считывания или записи. Когда передающее устройство выполняет операцию считывания, оно посылает адрес в приемное устройство 104 на адресном канале 106a с соответствующими управляющими сигналами. В ответ, приемное устройство 104 посылает полезную нагрузку в передающее устройство 102 на канале 106c считывания.

Теперь со ссылкой на Фиг.2 будут описаны две операции записи. Фиг.2 - иллюстрация, показывающая информацию, передаваемую на адресном канале и канале записи. В данном примере передающее устройство инициирует шины в системе обработки данных Фиг.1 с адресным каналом, обеспечивающим общий носитель для адресов и данных, две 16-байтовые операции записи.

На Фиг.2, на первом синхроцикле 202, передающее устройство инициирует первую 16-байтовую операцию записи, посылая 4-байтовый адрес A1 в приемное устройство на адресном канале 106a с соответствующими управляющими сигналами. Во время этого же синхроцикла 202, передающее устройство также посылает первые 4 байта первой полезной нагрузки W1(1) в приемное устройство на канале 106b записи.

Во втором синхроцикле 204, передающее устройство использует оба канала - адресный канал 106a и канал 106b записи, чтобы посылать данные. Передающее устройство посылает вторые 4 байта первой полезной нагрузки W1(2) на канале 106b записи и третьи 4 байта первой полезной нагрузки W1(3) на адресном канале 106a.

Передающее устройство инициирует следующую 16-байтовую операцию записи во время третьего синхроцикла 206, посылая 4-байтовый адрес A2 в приемное устройство на адресном канале 106a с соответствующими управляющими сигналами. Передающее устройство завершает передачу первой полезной нагрузки во время этого же синхроцикла следующей операции записи, посылая последние 4 байта W1(4)в приемное устройство на канале 106b записи.

Затем, чтобы послать вторую полезную нагрузку в приемное устройство, передающее устройство использует следующие два синхроцикла. В четвертом синхроцикле 208 передающее устройство посылает в приемное устройство первые 4 байта второй полезной нагрузки W2(1) на канале 106b записи и вторые 4 байта второй полезной нагрузки W2(2) на адресном канале 106a. В следующем синхроцикле 210, передающее устройство посылает в приемное устройство третьи 4 байта второй полезной нагрузки W2(3) на канале 106b записи и последние 4 байта второй полезной нагрузки W2(4) на адресном канале 106a.

Для поддержки передающей среды, для осуществления передачи адреса и данных могут быть использованы два типа управляющих сигналов. Первый управляющий сигнал, называемый сигнал "адрес/данные", используется на адресном канале 106a для индикации того, является ли передаваемая информация адресом или данными. В данном примере, когда обеспечивается сигнал "адрес/данные", передается адрес на адресном канале 106a. Наоборот, когда сигнал "адрес/данные" отменяется, на адресном канале 106a передаются данные.

Второй управляющий сигнал, называемый Индикатор такта, используется на обоих каналах - адресном канале 106a и канале 106b записи для индикации такта текущей передаваемой полезной нагрузки. Следует отметить, что Индикатор такта представляет собой нулевой индикатор, такой, что значение "0" показывает первый такт передаваемой полезной нагрузки. В приведенном примере каждая полезная нагрузка полностью передается перед передачей следующей полезной нагрузки, и, следовательно, нет необходимости в передаче сигналов для идентификации каждой полезной нагрузки. В альтернативных вариантах осуществления системы обработки данных, где полезные нагрузки передаются беспорядочно, или такты различных полезных нагрузок перемежаются, передача сигналов может включать в себя номера последовательности полезной нагрузки.

Теперь со ссылкой на Фиг.3 будет описан пример, иллюстрирующий, как могут быть использованы два управляющих сигнала. Протокол шины для адресного канала и канала записи 106a, 106b показан в таблице 1. Указанный протокол шины используется для иллюстрации изобретательских особенностей системы обработки данных, с пониманием того, что такие изобретательские особенности могут быть использованы с другими протоколами шины. Специалисты могут легко варьировать и/или добавлять сигналы в этот протокол в фактической реализации описанных здесь шинных архитектур.

Фиг.3 - диаграмма синхронизации, показывающая передачу управляющих сигналов для двух одинаковых 16-байтовых операций, описанных выше в связи с Фиг.2. Для синхронизации передачи информации между передающим устройством и приемным устройством может быть использован системный тактовый генератор 306. Системный тактовый генератор 306 показан с пятью синхроциклами, причем каждый синхроцикл пронумерован последовательно.

Операция записи может быть инициирована на адресном канале 106a передающим устройством во время первого синхроцикла 303. Указанная операция записи достигается посредством передачи адреса A1 для первой операции записи на 32-битовой среде адреса 308. Передающее устройство обеспечивает сигнал Достоверный адрес 312, показывающий, что на адресном канале 106a передается достоверная информация. Передающее устройство 102 также обеспечивает сигнал 313 Адрес/данные, показывающий, что информация, передаваемая на адресном канале 106a, является адресом. Передающее устройство 102 отменяет сигнал 316 Считывание/запись, о запросе операции записи. Сигнал 318 Объем полезной нагрузки может быть использован, чтобы показывать объем полезной нагрузки, который в данном случае составляет 16 байтов. Состояние индикатора 314 Такта адреса может игнорироваться во время пребывания адреса на адресном канале 106a.

Во время того же первого синхроцикла 301 передающее устройство использует среду 320 записи для передачи первых 4 байтов первой полезной нагрузки W1(1) и устанавливает индикатор 326 такта записи на значение "00". Передающее устройство также обеспечивает сигнал 324 Достоверная запись, показывающий, что на канале 106b записи передается достоверная информация.

В конце первого синхроцикла 301 передающее устройство проверяет, чтобы установленный сигнал 310 Подтверждение передачи адреса подтвердил успешную доставку адреса A1 по адресному каналу 106a в приемное устройство. Передающее устройство также проверяет, чтобы установленный сигнал 322 Подтверждение передачи записи подтвердил успешную доставку первых 4 байтов первой полезной нагрузки W1(1) по каналу 106b записи в приемное устройство.

На втором синхроцикле 302 передающее устройство использует среду 320 записи для передачи первых 4 байтов первой полезной нагрузки W1(2) и устанавливает индикатор 326 такта записи на значение "01". Передающее устройство также обеспечивает индикатор 324 Достоверная запись, чтобы показывать, что на канале 106b записи передается достоверная информация.

Во время того же второго синхроцикла 302 передающее устройство передает третьи 4 байта первой полезной нагрузки W1(3) в приемное устройство на среде 308 адреса и устанавливает индикатор 314 такта адреса на значение "10". Передающее устройство также обеспечивает сигнал 312 Достоверный адрес, показывающий, что на адресном канале передается достоверная информация, и отменяет сигнал 313 Адрес/данные, чтобы показывать, что информация, передаваемая на адресном канале 106a, представляет собой данные. Состояние сигнала 316 Считывание/запись и 318 Объем полезной нагрузки может игнорироваться во время пребывания данных на адресном канале 106a. На Фиг.3 сигналы 316 Считывание/запись и 318 Объем полезной нагрузки остаются неизменными, но могут устанавливаться в любое состояние.

В конце второго синхроцикла 302 передающее устройство проверяет, чтобы установленный сигнал 322 Подтверждение передачи записи подтвердил успешную доставку вторых 4 байтов первой полезной нагрузки W1(2) по каналу 106b записи в приемное устройство. Передающее устройство также проверяет, чтобы установленный сигнал 310 Подтверждение передачи адреса подтвердил успешную доставку третьих 4 байтов первой полезной нагрузки W1(3) по адресному каналу 106a в приемное устройство.

На третьем синхроцикле 303 передающее устройство использует среду 320 записи для передачи последних 4 байтов первой полезной нагрузки W1(4) и устанавливает индикатор 326 такта записи на значение "11". Передающее устройство также обеспечивает индикатор 324 Достоверная запись, показывающий, что на канале 106b записи передается достоверная информация.

Во время того же третьего синхроцикла 303, в качестве завершения первой операции записи, передающее устройство передает адрес A2 для второй 16-байтовой операции на среде 308 записи. Передающее устройство обеспечивает сигнал 312 Достоверный адрес, показывающий, что на адресном канале 106a передается достоверная информация. Передающее устройство 102 также обеспечивает сигнал 313 Адрес/данные показывать, что информация, передаваемая на адресном канале 106a, является адресом A2. Передающее устройство 102 отменяет сигнал 316 Считывание/запись, чтобы запрашивать операцию записи. Сигнал 318 Объем полезной нагрузки может быть использован, чтобы показывать объем полезной нагрузки, который в этом случае составляет 16 байтов. Состояние индикатора 314 Такта адреса может игнорироваться во время пребывания адреса на адресном канале 106a.

В конце третьего синхроцикла 303, передающее устройство проверяет, чтобы установленный сигнал 310 Подтверждение передачи адреса подтвердил успешную доставку адреса A2 по адресному каналу 106a в приемное устройство. Передающее устройство также проверяет, чтобы установленный сигнал 322 Подтверждение передачи записи подтвердил успешную доставку последних 4 байтов первой полезной нагрузки W1(4) по каналу 106b записи в приемное устройство.

Передающее устройство использует следующие два синхроцикла, чтобы посылать вторую полезную нагрузку в приемное устройство. На четвертом синхроцикле 304, передающее устройство посылает первые 4 байта второй полезной нагрузки W2(1) в приемное устройство, используя среду 320 записи, и устанавливает индикатор 326 такта записи на значение "00". Передающее устройство продолжает обеспечивать сигнал 324 Достоверная запись, показывающий, что на канале 106b записи передается достоверная информация.

Во время того же четвертого синхроцикла 304, передающее устройство передает вторые 4 байта второй полезной нагрузки W2(2) на среде 308 адреса и устанавливает индикатор 314 такта адреса на значение "01". Передающее устройство также обеспечивает сигнал 312 Достоверный адрес, показывающий, что на адресном канале 106a передается достоверная информация, и отменяет сигнал 313 Адрес/данные, чтобы показывать, что информация, передаваемая на адресном канале 106a, представляет собой данные. После этого, сигнал 316 Считывание/запись и 318 Объем полезной нагрузки может игнорироваться во время пребывания данных на адресном канале 106a.

В конце четвертого синхроцикла 304, передающее устройство проверяет, чтобы установленный сигнал 322 Подтверждение передачи записи подтвердил успешную доставку первых 4 байтов второй полезной нагрузки W2(1) по каналу 106b записи в приемное устройство. Передающее устройство также проверяет, чтобы установленный сигнал 310 Подтверждение передачи адреса подтвердил успешную доставку вторых 4 байтов второй полезной нагрузки W2(2) по адресному каналу 106a в приемное устройство.

На пятом синхроцикле 305, передающее устройство посылает третьи 4 байта второй полезной нагрузки W2(3) в приемное устройство, используя среду 320 записи, и устанавливает индикатор 326 такта записи на значение "10". Передающее устройство обеспечивает индикатор 324 Достоверная запись, показывающий, что на канале 106b записи передается достоверная информация.

Во время того же пятого синхроцикла 305, передающее устройство передает последние 4 байта второй полезной нагрузки W2(4) на среде 308 адреса и устанавливает индикатор 314 такта адреса на значение "11". Передающее устройство также обеспечивает сигнал 312 Достоверный адрес, показывающий, что на адресном канале 106a передается достоверная информация, и отменяет сигнал 313 Адрес/данные, чтобы показывать, что информация, передаваемая на адресном канале 106a, представляет собой данные. Состояние сигнала 316 Считывание/запись и 318 Объем полезной нагрузки может игнорироваться во время пребывания данных на адресном канале 106a.

В конце пятого синхроцикла 305, передающее устройство проверяет, чтобы установленный сигнал 322 Подтверждение передачи записи подтвердил успешную доставку третьих 4 байтов второй полезной нагрузки W2(3) по каналу 106b записи в приемное устройство. Передающее устройство также проверяет, чтобы установленный сигнал 310 Подтверждение передачи адреса подтвердил успешную доставку последних 4 байтов второй полезной нагрузки W2(4) по адресному каналу 106a в приемное устройство.

Уменьшение передачи сигналов может быть достигнуто посредством замены индикатора такта схемой неявной адресации. Пример такой схемы неявной адресации показан на Фиг.2. В данном примере схема неявной адресации требует, чтобы следующая 4-байтовая последовательность текущей полезной нагрузки передавалась на самом раннем доступном синхроцикле, с приоритетом канала 106b записи над адресным каналом 106a.

На Фиг.2 самым ранним синхроциклом доступным для передачи первых 4 байтов первой полезной нагрузки W1(1), является первый синхроцикл 202, и во время этого синхроцикла 202 является доступным канал 106b записи. Самым ранним синхроциклом, доступным для передачи вторых 4 байтов первой полезной нагрузки W1(2), является второй синхроцикл 204, и снова является доступным канал 106b записи. Второй синхроцикл 204 также является доступным для передачи третьих 4 байтов первой полезной нагрузки W1(3), но канал 106b записи не доступен. Таким образом, третьи 4 байта первой полезной нагрузки W1(3) передаются на адресном канале 106a. Самым ранним синхроциклом, доступным для передачи последних 4 байтов первой полезной нагрузки W1(4), является третий синхроцикл 206, и снова является доступным канал 106b записи.

Во время третьего синхроцикла 206 в приемное устройство передается адрес A2 для второй операции записи. Однако канал 106b записи является недоступным для передачи первых 4 байтов второй полезной нагрузки W2(1), так как он необходим во время третьего синхроцикла 206 для передачи последних 4 байтов первой полезной нагрузки W1(4). Самым ранним синхроциклом, доступным для передачи первых 4 байтов второй полезной нагрузки W2(1), является четвертый синхроцикл 208, и во время указанного синхроцикла 208 канал 106b записи доступен. Четвертый синхроцикл 208 также является доступным для передачи вторых 4 байтов второй полезной нагрузки W2(2), но канал 106b записи не доступен. Таким образом, вторые 4 байта второй полезной нагрузки W2(2) передаются на адресном канале 106a. Самым ранним синхроциклом, доступным для передачи последних 8 байтов второй полезной нагрузки W2(3), W2(4), является пятый синхроцикл 210. Третьи 4 байта второй полезной нагрузки W2(3) передаются на канале 106b записи, то есть, предпочтительном канале, и последние 4 байта второй полезной нагрузки W2(4) передаются на адресном канале 106a.

Использование адресного канала в качестве среды для передачи адресов и данных может применяться в различных условиях обработки. Например, указанный метод может быть использован для уменьшения количества времени, необходимого для процессора для сбора строки данных кэш-памяти из другого процессора в системе обработки данных с взаимным соответствием содержимого различных кэшей, обеспеченной аппаратными средствами. Теперь упомянутый пример будет описан со ссылкой на Фиг.4. На Фиг.4 показана система 400 обработки данных с взаимным соответствием содержимого различных кэшей с двумя устройствами обработки 402a, 402b в сообщении с совместно используемым ресурсом, таким как запоминающее устройство 404, через шинное межкомпонентное соединение 406. В приведенном примере, первое устройство 402a обработки производит считывание с запоминающего устройства 404 посредством помещения адреса на его адресном канале 406a1 с соответствующими управляющими сигналами. Адрес отправляется в запоминающее устройство 404 через шинное межкомпонентное соединение 406 на адресном канале 406a3 запоминающего устройства. В ответ шинное межкомпонентное соединение 408 отыскивает блок данных из памяти 410 и помещает его на канале 406c3 считывания памяти. Шинное межкомпонентное соединение 406 отправляет данные из запоминающего устройства 404a в первое устройство обработки по каналу 406c1 считывания первого устройства обработки. Сразу после приема первым устройством 402a обработки данные могут быть помещены в кэш-память 412, модифицированную процессором 414, и записаны обратно в запоминающее устройство 404 интерфейсом 416 шины. Операция записи может выполняться так же, как описано выше в связи с Фиг.2 и 3.

Взаимное соответствие содержимого различных кэшей относится к ситуации, где второе устройство 402b обработки по-существу пытается производить считывание с одного и того же адреса. Без механизма, гарантирующего взаимное соответствие содержимого различных кэшей, второе устройство 402b обработки могло бы принимать данные состояния из запоминающего устройства 404, если данные в кэш-памяти 412 первого устройства 402a обработки были модифицированы, но еще не записаны обратно в запоминающее устройство 404.

Для поддержания соответствия между кэш-памятью и основной памятью обычно используется процесс, называемый «отслеживание адресов». Отслеживание адресов представляет собой процесс, в котором устройство обработки, например, такое как второе устройство 402b обработки, выдает запрос считывания на снабженный кэшем адрес в запоминающем устройстве 404, не присутствующий в собственной кэш-памяти 418, что побуждает шинное межкомпонентное соединение 406 рассылать отслеживаемый адрес в другие устройства обработки в системе, перед тем как отправлять запрос считывания данных в запоминающее устройство 404. Если другое устройство обработки, такое как первое устройство 402a обработки, имеет запрошенные данные, хранимые в его кэш-памяти 412 в модифицированном состоянии, то оно будет записывать модифицированные данные обратно в запоминающее устройство 404. Одновременно, шинное межкомпонентное соединение 406 будет посылать модифицированные данные во второе устройство 402b обработки по каналу 406c2 считывания. Второе устройство 402 обработки будет помещать модифицированные данные в кэш-память 418 для использования процессором 422.

Фиг.5 - иллюстрация, показывающая информацию, передаваемую на адресном канале и канале записи 406a1, 406b1 между первым устройством 402a обработки и шинным межкомпонентным соединением 406. На Фиг.4 и 5 первое устройство 402a обработки записывает 32-байтовую полезную нагрузку из своей кэш-памяти 412 в запоминающее устройство 404 в ответ на отслеживаемый адрес, рассылаемый шинным межкомпонентным соединением 406. Операция записи выполняется посредством передачи 32-байтовой полезной нагрузки на шинное межкомпонентное соединение 406, используя оба канала адресный и записи 406a1, 406b1. На первом синхроцикле 502 первое устройство 402a обработки посылает отслеживаемый адрес A на шинное межкомпонентное соединение 406 на своем адресном канале 406a1 с соответствующими управляющими сигналами. Во время этого же синхроцикла 502 первые 4 байта полезной нагрузки W(1) посылаются первым устройством 402a обработки на шинное межкомпонентное соединение 406 на канале 106b1 записи.

Остаток полезной нагрузки посылается из первого устройства 402a обработки на шинное межкомпонентное соединение 406 на следующих четырех синхроциклах. Во втором синхроцикле 504 первое устройство 402a обработки посылает вторые 4 байта полезной нагрузки W(2) на канале 106b1 записи и третьи 4 байта полезной нагрузки W(3) на адресном канале 106a1. Четвертые 4 байта полезной нагрузки W(4), шестые 4 байта полезной нагрузки W(6) и последние 4 байта полезной нагрузки W(8) посылаются первым устройством 402a обработки на шинное межкомпонентное соединение 406 на канале 106b1 записи на следующих трех синхроциклах 506, 508, 510. Пятые 4 байта полезной нагрузки W(5) и седьмые 4 байта полезной нагрузки W(7) посылаются первым устройством 402a обработки на шинное межкомпонентное соединение 406 на адресном канале 106a1 на следующих двух синхроциклах 506, 508.

Шинное межкомпонентное соединение 406 может посылать 32-байтовую полезную нагрузку в запоминающее устройство 404 подобным образом, используя оба канала - адресный канал и канал записи 406a3, 406b3, чтобы посылать полезную нагрузку в 5-ти синхроциклах. Шинное межкомпонентное соединение 406 также посылает 32-байтовую полезную нагрузку во второе устройство 402b обработки на канале 406c2 считывания в 8 синхроциклах в ответ на первоначальный запрос считывания устройства 402b обработки. Передача 32-байтовой полезной нагрузки в запоминающее устройство 404 и во второе устройство 402b обработки может перекрывать или следовать после передачи полезной нагрузки между первым устройством 402a обработки и шинным межкомпонентным соединением 406.

Объяснение передачи управляющих сигналов, которое было подробно описано в связи с Фиг.3, не будет здесь повторяться за исключением того, что следует отметить, что индикатор такта для обоих каналов адресного и записи 406a1, 406b1 не должен распространяться на 3-битовый код, чтобы управлять 8-байтовой полезной нагрузкой.

Фиг.6 - упрощенная блок схема, иллюстрирующая пример двух устройств в системе 600 обработки данных, сообщающихся по четырехканальной шине. Для каждого канала считывания и записи обеспечивается отдельный независимый адресный канал. В указанном примере каждый канал имеет разрядность 32 бита, но на практике может иметь любую ширину, в зависимости от конкретного применения и ограничений общего замысла. Операция записи по четырехканальной шине может выполняться посредством передачи в приемное устройство 604 адреса на адресном канале 606a записи и данных на адресном канале 606a записи, канале 606b записи и/или адресном канале 606d считывания. Операция записи по четырехканальной шине может выполняться посредством передачи в приемное устройство 604 адреса на адресном канале 606d считывания. В ответ приемное устройство 604 посылает полезную нагрузку в передающее устройство 602 на канале 606c считывания.

Фиг.7 - иллюстрация, показывающая информацию, передаваемую на адресном канале записи, адресном канале считывания и канале записи между передающим устройством и приемным устройством по четырехканальной шине. На первом синхроцикле 702 передающее устройство инициирует первую 16-байтовую операцию записи, посылая 4-байтовый адрес A1 в приемное устройство на адресном канале 106a записи с соответствующими управляющими сигналами. Во время этого же синхроцикла 702 передающее устройство также передает первые 4 байта первой полезной нагрузки W1(1) на канале 106b записи и вторые 4 байта такой же полезной нагрузки W1(2) на адресном канале 606d считывания.

Во втором синхроцикле 704 остаток первой полезной нагрузки посылается передающим устройством в приемное устройство. Более конкретно, на втором синхроцикле 704, как завершающем первую операцию записи, передающее устройство передает третьи 4 байта первой полезной нагрузки W1(3) на канале 106b записи и последние 4 байта первой полезной нагрузки W1(4) на адресном канале 606d считывания. Во время того же синхроцикла 704 передающее устройство посылает адрес A2 для второй 16-байтовой операции записи в приемное устройство на адресном канале 606a записи.

Затем передающее устройство использует следующие два синхроцикла для передачи второй полезной нагрузки в приемное устройство. На третьем синхроцикле 706 передающее устройство посылает в приемное устройство первые 4 байта второй полезной нагрузки W2(1) на канале 606b записи, вторые 4 байта второй полезной нагрузки W2(2) на адресном канале 606d считывания и третьи 4 байта второй полезной нагрузки W2(3) на адресном канале 606a записи. На следующем синхроцикле 708 передающее устройство посылает последние 4 байта второй полезной нагрузки W2(4) на канале 606b записи в приемное устройство.

Различные иллюстративные логические блоки, модули и схемы, описанные в связи с раскрытыми здесь вариантами осуществления, могут быть выполнены или реализованы с процессором общего назначения, процессором цифровой обработки сигналов (DSP), со специализированной интегральной схемой (ASIC), программируемой вентильной матрицей (FPGA) или с другим программируемым логическим устройством, дискретным вентилем или транзисторной логикой, дискретными компонентами аппаратных средств или любой их комбинацией, рассчитанной для выполнения описанных здесь функций. Процессор общего назначения может представлять собой микропроцессор, но альтернативно, процессор может представлять собой известный процессор, контроллер, микроконтроллер или конечный автомат. Процессор также может быть выполнен в виде комбинации вычислительных устройств, например комбинации DSP процессора и микропроцессора, множества микропроцессоров, одного или нескольких микропроцессоров в сочетании с ядром DSP процессора, или в виде любой другой подобной конфигурации.

Этапы способа или алгоритм, описанные в связи с раскрытыми здесь вариантами осуществления, могут быть реализованы непосредственно в аппаратных средствах, в модуле программного обеспечения, выполняемого процессором, или в их комбинации. Модуль программного обеспечения может представлять собой запоминающее устройство с произвольной выборкой (RAM, ЗУПВ), флэш-память, постоянное запоминающее устройство (ROM, ПЗУ), стираемое программируемое постоянное запоминающее устройство (EPROM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), регистры, жесткий диск, сменный диск, постоянное запоминающее устройство на компакт-диске (CD-ROM) или любую другую форму носителя данных, известную в уровне техники. Носитель данных соединяется к процессору, так что процессор может считывать информацию с носителя данных или записывать на него. Альтернативно, носитель данных может быть интегральным с процессором. Процессор и носитель данных может находиться в схеме ASIC. Схема ASIC может находиться в передающем и/или приемном устройстве, или где-то в другом месте. Альтернативно, процессор и носитель данных могут находиться в дискретных компонентах в передающем и/или приемном устройстве, или где-то в другом месте.

Предыдущее описание раскрытых вариантов осуществления обеспечивается, чтобы дать возможность любому специалисту применить настоящее изобретение. Специалистам будут очевидны различные модификации упомянутых вариантов осуществления, и, основополагающие принципы, данные здесь, могут применяться к другим вариантам осуществления, не выходя за рамки и не отклоняясь от сущности настоящего изобретения. Таким образом, настоящее изобретение не должно ограничиваться показанными здесь вариантами осуществления, но должно соответствовать более широким рамкам, согласующимся с принципами и раскрытыми здесь элементами новизны.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСПОМОГАТЕЛЬНЫЕ ЗАПИСИ ПО КАНАЛУ АДРЕСА | 2007 |

|

RU2417414C2 |

| АРХИТЕКТУРА ПРОЦЕССОРА ВВОДА-ВЫВОДА, КОТОРЫЙ ОБЪЕДИНЯЕТ МОСТ МЕЖСОЕДИНЕНИЯ ПЕРВИЧНЫХ КОМПОНЕНТ | 1996 |

|

RU2157000C2 |

| СПОСОБ ОСУЩЕСТВЛЕНИЯ ДОСТУПА К ЦЕЛЕВОМУ ДИСКОВОМУ ЗАПОМИНАЮЩЕМУ УСТРОЙСТВУ, СИСТЕМА РАСШИРЕНИЯ ДИСКОВОЙ ЕМКОСТИ И ДИСКОВЫЙ МАССИВ | 2006 |

|

RU2399951C2 |

| Программируемые устройства для обработки запросов передачи данных памяти | 2016 |

|

RU2690751C2 |

| ШИННАЯ СИСТЕМА ОДНОКАНАЛЬНОЙ МНОГОСТАНЦИОННОЙ СВЯЗИ | 1994 |

|

RU2122234C1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Мультиплексный канал | 1978 |

|

SU723559A1 |

| ПОРТАТИВНОЕ УСТРОЙСТВО ХРАНЕНИЯ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ МНОЖЕСТВА ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2004 |

|

RU2325689C2 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

Изобретение относится к системам и способам обработки данных для передачи информации по шине в системе обработки данных. Техническим результатом является повышение быстродействия за счет уменьшения времени ожидания записи и увеличения ширины полосы пропускания. Система обработки данных включает в себя приемное устройство, шину, имеющую первый, второй и третий каналы, и передающее устройство, конфигурированное, таким образом, чтобы адресовать приемное устройство на первом канале и считывать полезную нагрузку из приемного устройства на втором канале, причем передающее устройство дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки в приемное устройство на первом канале и вторую часть полезной нагрузки в приемное устройство на третьем канале. 5 н. и 37 з.п. ф-лы, 7 ил., 2 табл.

1. Система обработки данных, содержащая:

приемное устройство;

шину, имеющую первый, второй и третий каналы; и

передающее устройство, конфигурированное, чтобы адресовать приемное устройство на первом канале и считывать данные из приемного устройства на втором канале, причем передающее устройство дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки в приемное устройство на первом канале и вторую часть полезной нагрузки в приемное устройство на третьем канале, причем первая часть полезной нагрузки и вторая часть полезной нагрузки являются последовательными частями полезной нагрузки, при этом, когда первый канал и третий канал одновременно доступны для записи соответствующей части полезной нагрузки, приоритет упорядочивания последовательных данных отдается третьему каналу по отношению к первому каналу.

2. Система обработки данных по п.1, в которой передающее устройство дополнительно конфигурируется, чтобы одновременно записывать первую и вторую части полезной нагрузки в приемное устройство.

3. Система обработки данных по п.1, в которой передающее устройство дополнительно конфигурируется, чтобы одновременно адресовать приемное устройство и записывать вторую часть полезной нагрузки в приемное устройство.

4. Система обработки данных по п.1, в которой передающее устройство дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки на первый адрес и вторую часть полезной нагрузки на первый адрес плюс смещение адреса первой части полезной нагрузки приемного устройства, причем передающее устройство дополнительно конфигурируется, чтобы посылать второй адрес в приемное устройство на первом канале одновременно с записью второй части полезной нагрузки в приемное устройство.

5. Система обработки данных по п.1, в которой передающее устройство содержит первое устройство обработки, а приемное устройство содержит шинное межкомпонентное соединение, причем система обработки данных дополнительно содержит второе устройство обработки, причем шинное межкомпонентное соединение конфигурируется, чтобы соединять первое и второе устройства обработки с совместно используемым ресурсом, и в которой первое устройство обработки дополнительно конфигурируется, чтобы записывать первую и вторую части полезной нагрузки на шинное межкомпонентное соединение в ответ на отслеживаемый адрес из второго устройства обработки.

6. Система обработки данных по п.1, в которой шина дополнительно содержит четвертый канал, причем передающее устройство дополнительно конфигурируется, чтобы адресовать приемное устройство на первом канале для операций записи, и адресовать приемное устройство на четвертом канале для операций считывания, и в которой передающее устройство дополнительно конфигурируется, чтобы записывать третью часть полезной нагрузки в приемное устройство на четвертом канале.

7. Система обработки данных по п.6, в которой передающее устройство дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки на первый адрес, записывать вторую часть полезной нагрузки на первый адрес плюс смещение адреса первой части полезной нагрузки и записывать третью часть полезной нагрузки на первый адрес плюс объединенное смещение адреса первой и второй части полезной нагрузки, причем передающее устройство дополнительно конфигурируется, чтобы посылать второй адрес в приемное устройство на первом канале одновременно с записью второй и третьей частей полезной нагрузки в приемное устройство.

8. Система обработки данных по п.1, в которой передающее устройство дополнительно конфигурируется, чтобы обеспечивать подачу управляющего сигнала в приемное устройство, показывающего, используется ли в настоящее время первый канал, чтобы адресовать приемное устройство, или чтобы записывать первую часть полезной нагрузки в приемное устройство.

9. Система обработки данных по п.1, в которой передающее устройство дополнительно конфигурируется, чтобы обеспечивать подачу управляющего сигнала на каждом из первого и третьего каналов в приемное устройство, причем каждый из управляющих сигналов идентифицирует часть полезной нагрузки, посылаемой на соответствующем ей канале.

10. Система обработки данных по п.1, в которой передающее устройство конфигурируется, чтобы неявно адресовать приемное устройство, причем следующая последовательная часть полезной нагрузки записывается на самом раннем доступном синхроцикле.

11. Система обработки данных по п.10, в которой каждая полезная нагрузка передается целиком до того, как передается следующая полезная нагрузка.

12. Система обработки данных, содержащая:

приемное устройство;

шину, имеющую первый, второй и третий каналы;

средство для адресации приемного устройства на первом канале:

средство для считывания данных из приемного устройства на втором канале; и

средство для записи первой части полезной нагрузки в приемное устройство на первом канале и второй части полезной нагрузки в приемное устройство на третьем канале, причем первая часть полезной нагрузки и вторая часть полезной нагрузки являются последовательными частями полезной нагрузки, при этом, когда первый канал и третий канал одновременно доступны для записи соответствующей части полезной нагрузки, приоритет упорядочивания последовательных данных отдается третьему каналу по отношению к первому каналу.

13. Способ обмена информацией между передающим устройством и приемным устройством по шине, причем шина содержит первый, второй и третий каналы, при этом способ содержит:

адресацию приемного устройства на первом канале;

считывание данных из приемного устройства на втором канале; и

запись первой части полезной нагрузки в приемное устройство на первом канале и второй части полезной нагрузки в приемное устройство на третьем канале, причем первая часть полезной нагрузки и вторая часть полезной нагрузки являются последовательными частями полезной нагрузки, при этом, когда первый канал и третий канал одновременно доступны для записи соответствующей части полезной нагрузки, приоритет упорядочивания последовательных данных отдается третьему каналу по отношению к первому каналу.

14. Способ по п.13, в котором первая и вторая части полезной нагрузки одновременно записываются в приемное устройство.

15. Способ по п.13, в котором приемное устройство адресуется одновременно с записью второй части полезной нагрузки в приемное устройство.

16. Способ по п.13, в котором первая часть полезной нагрузки записана на первый адрес и вторая часть полезной нагрузки записана на первый адрес плюс смещение адреса первой части полезной нагрузки, адресация приемного устройства дополнительно содержит передачу второго адреса в приемное устройство на первом канале одновременно с записью второй части полезной нагрузки в приемное устройство.

17. Способ по п.13, в котором передающее устройство содержит первое устройство обработки, и приемное устройство содержит шинное межкомпонентное соединение, причем система обработки данных дополнительно содержит второе устройство обработки, причем шинное межкомпонентное соединение конфигурируется, чтобы соединять первое и второе устройства обработки с совместно используемым ресурсом, и в котором первая и вторая части полезной нагрузки записываются на шинное межкомпонентное соединение в ответ на отслеживаемый адрес из второго устройства обработки.

18. Способ по п.13, в котором шина дополнительно содержит четвертый канал, причем адресация приемного устройства на первом канале осуществляется для операций записи, при этом способ дополнительно содержит адресацию приемного устройства на четвертом канале для операций считывания, и запись третьей части полезной нагрузки в приемное устройство на четвертом канале.

19. Способ по п.18, в котором первая часть полезной нагрузки записывается на первый адрес, вторая часть полезной нагрузки записывается на первый адрес плюс смещение адреса первой части полезной нагрузки и третья часть полезной нагрузки записывается на первый адрес плюс объединенное смещение адреса первой и второй части полезной нагрузки, при этом способ дополнительно содержит передачу второго адреса в приемное устройство на первом канале одновременно с записью второй и третьей частей полезной нагрузки в приемное устройство.

20. Способ по п.13, дополнительно содержащий обеспечение подачи управляющего сигнала в приемное устройство, показывающего, используется ли в настоящее время первый канал, чтобы адресовать приемное устройство, или чтобы записывать первую часть полезной нагрузки в приемное устройство.

21. Способ по п.13, дополнительно содержащий управляющий сигнал на каждом из первого и третьего каналов в приемное устройство, причем каждый из управляющих сигналов идентифицирует часть полезной нагрузки, посылаемой на соответствующем ей канале.

22. Способ по п.13, в котором передающее устройство конфигурируется, чтобы неявно адресовать приемное устройство, причем следующая последовательная часть полезной нагрузки записывается на самом раннем доступном синхроцикле.

23. Способ по п.22, в котором каждая полезная нагрузка передается целиком до того, как передается следующая полезная нагрузка.

24. Устройство управления шиной, содержащее:

процессор; и

интерфейс шины, конфигурированный, чтобы сопрягать процессор с шиной, имеющей первый, второй и третий каналы, причем интерфейс шины дополнительно конфигурируется, чтобы адресовать подчиненное устройство на первом канале, принимать данные из подчиненного устройства на втором канале, и записывать первую часть полезной нагрузки в подчиненное устройство на первом канале и вторую часть полезной нагрузки в подчиненное устройство на третьем канале, причем первая часть полезной нагрузки и вторая часть полезной нагрузки являются последовательными частями полезной нагрузки, при этом, когда первый канал и третий канал одновременно доступны для записи соответствующей части полезной нагрузки, приоритет упорядочивания последовательных данных отдается третьему каналу по отношению к первому каналу.

25. Устройство управления шиной по п.24, в котором интерфейс шины дополнительно конфигурируется, чтобы одновременно записывать первую и вторую части полезной нагрузки в подчиненное устройство.

26. Устройство управления шиной по п.24, в котором интерфейс шины дополнительно конфигурируется, чтобы одновременно адресовать подчиненное устройство и записывать вторую часть полезной нагрузки в подчиненное устройство.

27. Устройство управления шиной по п.24, в котором интерфейс шины дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки на первый адрес и вторую часть полезной нагрузки на первый адрес плюс смещение адреса первой части полезной нагрузки подчиненного устройства, причем интерфейс шины дополнительно конфигурируется, чтобы посылать второй адрес в подчиненное устройство на первом канале одновременно с записью второй части полезной нагрузки в подчиненное устройство.

28. Устройство управления шиной по п.24, в котором подчиненное устройство содержит шинное межкомпонентное соединение, конфигурированное, чтобы соединять устройство управления шиной и второе устройство управления шиной с совместно используемым ресурсом, и в котором устройство управления шиной дополнительно конфигурируется, чтобы записывать первую и вторую части полезной нагрузки в шинное межкомпонентное соединение в ответ на отслеживаемый адрес из второго устройства управления шиной.

29. Устройство управления шиной по п.24, в котором шина дополнительно содержит четвертый канал, причем интерфейс шины дополнительно конфигурируется, чтобы адресовать подчиненное устройство на первом канале для операций записи, и адресовать подчиненное устройство на четвертом канале для операций считывания, и в котором интерфейс шины дополнительно конфигурируется, чтобы записывать третью часть полезной нагрузки в подчиненное устройство на четвертом канале.

30. Устройство управления шиной по п.29, в котором интерфейс шины дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки на первый адрес, записывать вторую часть полезной нагрузки на первый адрес плюс смещение адреса первой части полезной нагрузки и записывать третью часть полезной нагрузки на первый адрес плюс объединенное смещение адреса первой и второй части полезной нагрузки, причем интерфейс шины дополнительно конфигурируется, чтобы посылать второй адрес в подчиненное устройство на первом канале одновременно с записью второй или третьей части полезной нагрузки в подчиненное устройство.

31. Устройство управления шиной по п.24, в котором интерфейс шины дополнительно конфигурируется, чтобы обеспечивать подачу управляющего сигнала на каждом из первого и третьего каналов в подчиненное устройство, причем каждый из управляющих сигналов идентифицирует часть полезной нагрузки, посылаемой на соответствующем ей канале.

32. Устройство управления шиной по п.24, в котором интерфейс шины дополнительно конфигурируется, чтобы неявно адресовать подчиненное устройство, причем следующая последовательная часть полезной нагрузки записывается на самом раннем доступном синхроцикле.

33. Устройство управления шиной по п.32, в котором каждая полезная нагрузка передается целиком до того, как передается следующая полезная нагрузка.

34. Запоминающее устройство, содержащее:

память; и

интерфейс шины, конфигурированный, чтобы сопрягать память с шиной, имеющей первый, второй и третий каналы, причем интерфейс шины конфигурируется, чтобы принимать адрес и первую часть полезной нагрузки из устройства управления шиной на первом канале, посылать данные в устройство управления шиной на втором канале, и принимать вторую часть полезной нагрузки из устройства управления шиной на третьем канале, причем первая часть полезной нагрузки и вторая часть полезной нагрузки являются последовательными частями полезной нагрузки, при этом, когда первый канал и третий канал одновременно доступны для записи соответствующей части полезной нагрузки, приоритет упорядочивания последовательных данных отдается третьему каналу по отношению к первому каналу.

35. Запоминающее устройство по п.34, в котором интерфейс шины дополнительно конфигурируется, чтобы одновременно принимать первую и вторую части полезной нагрузки.

36. Запоминающее устройство по п.34, в котором интерфейс шины дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки на первый адрес и вторую часть полезной нагрузки на первый адрес плюс смещение адреса первой части полезной нагрузки, причем интерфейс шины дополнительно конфигурируется, чтобы принимать второй адрес на первом канале одновременно со второй частью полезной нагрузки.

37. Запоминающее устройство по п.34, в котором шина дополнительно содержит четвертый канал, причем интерфейс шины дополнительно конфигурируется, чтобы принимать адрес на первом канале для операций записи, и принимать адрес на четвертом канале для операции считывания, и в котором интерфейс шины дополнительно конфигурируется, чтобы принимать третью часть полезной нагрузки из устройства управления шиной на четвертом канале.

38. Запоминающее устройство по п.37, в котором интерфейс шины дополнительно конфигурируется, чтобы записывать первую часть полезной нагрузки на первый адрес, записывать вторую часть полезной нагрузки на первый адрес плюс смещение адреса первой части полезной нагрузки и записывать третью часть полезной нагрузки на первый адрес плюс объединенное смещение адреса первой и второй части полезной нагрузки, причем интерфейс шины дополнительно конфигурируется, чтобы принимать второй адрес из устройства управления шиной на первом канале одновременно с приемом второй или третьей части полезной нагрузки.

39. Запоминающее устройство по п.34, в котором интерфейс шины дополнительно конфигурируется, чтобы принимать управляющий сигнал из устройства управления шиной, показывающий, используется ли в настоящее время первый канал, чтобы посылать адрес или первую часть полезной нагрузки.

40. Запоминающее устройство по п.34, в котором интерфейс шины дополнительно конфигурируется, чтобы принимать управляющий сигнал на каждом из первого и третьего каналов из устройства управления шиной, причем каждый из управляющих сигналов идентифицирует часть полезной нагрузки, посылаемой на соответствующем ей канале.

41. Запоминающее устройство по п.34, в котором интерфейс шины дополнительно конфигурируется, чтобы неявно адресовать устройство управления шиной, причем следующая последовательная часть полезной нагрузки принимается на самом раннем доступном синхроцикле.

42. Запоминающее устройство по п.41, в котором каждая полезная нагрузка принимается целиком до того, как передается следующая полезная нагрузка.

| US 5255376 А, 19.10.1993 | |||

| US 20050172063 A1, 04.08.2005 | |||

| US 5745707 A, 28.04.1998 | |||

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

Авторы

Даты

2010-11-27—Публикация

2007-02-23—Подача